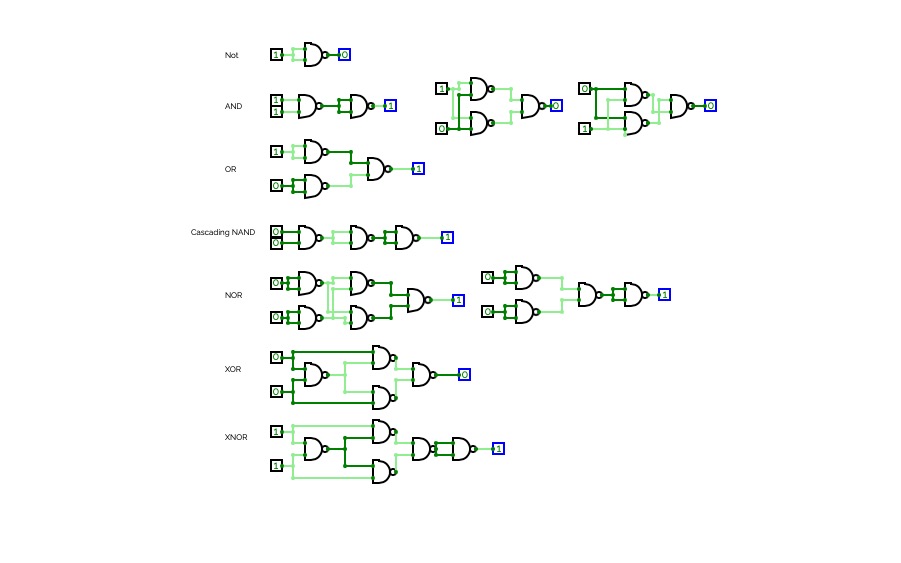

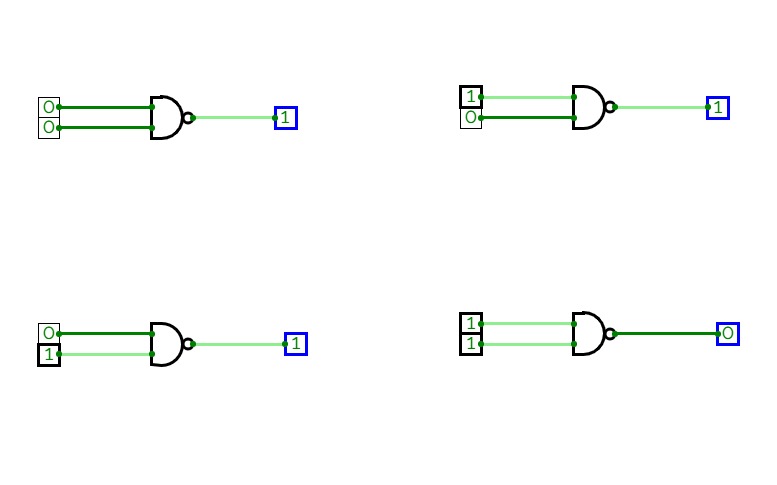

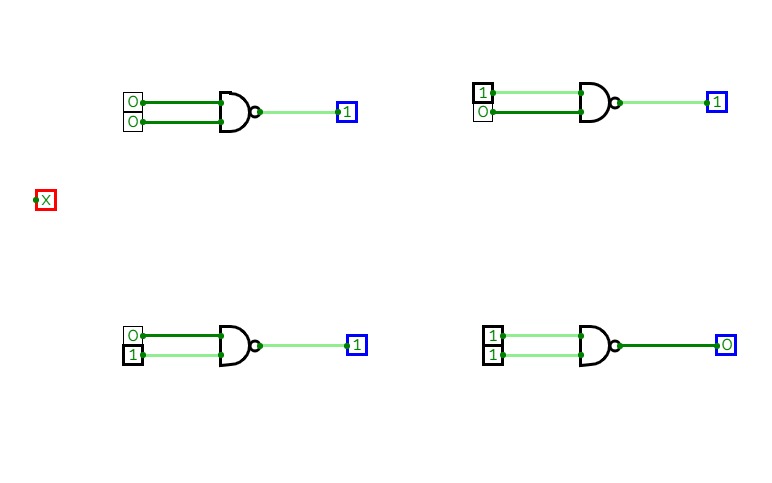

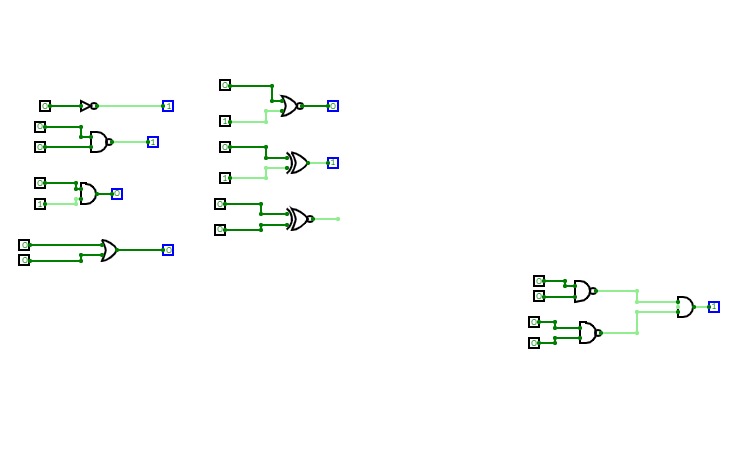

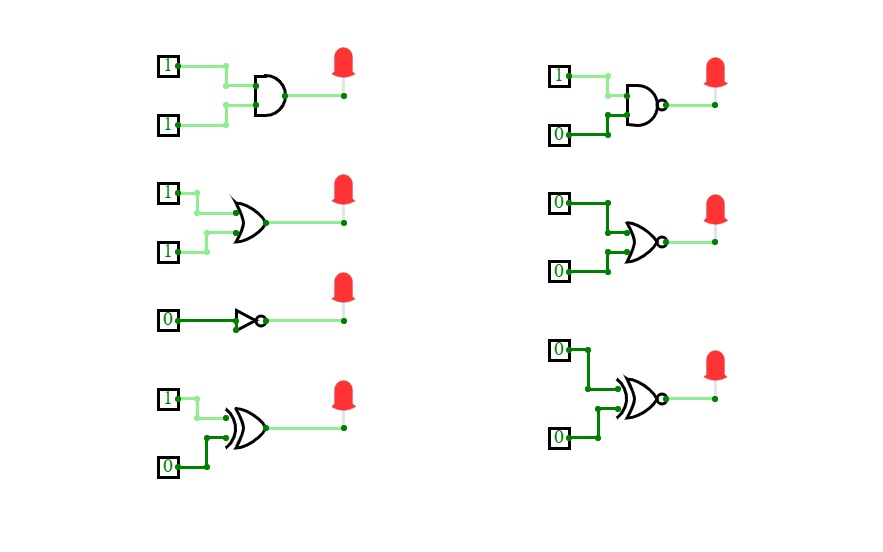

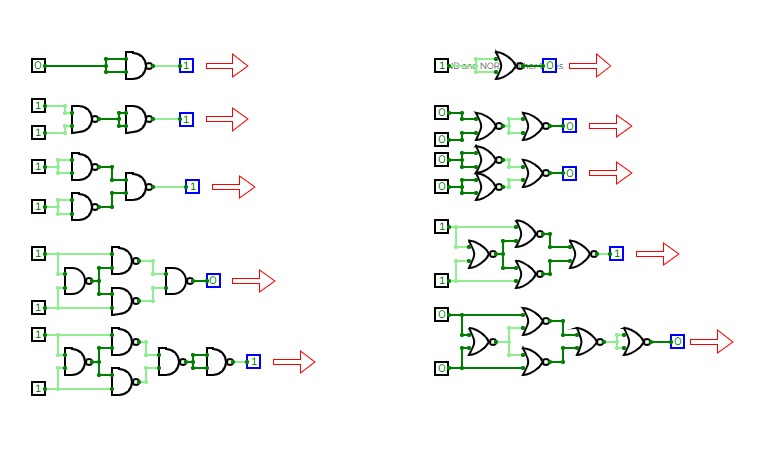

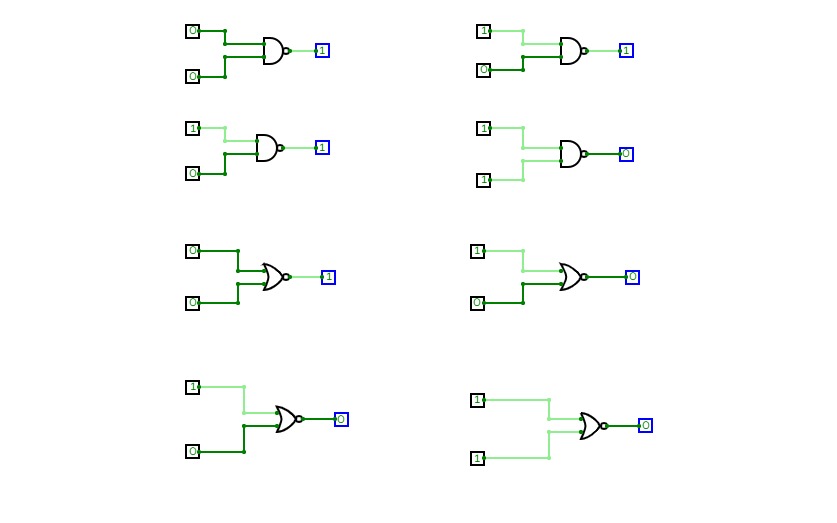

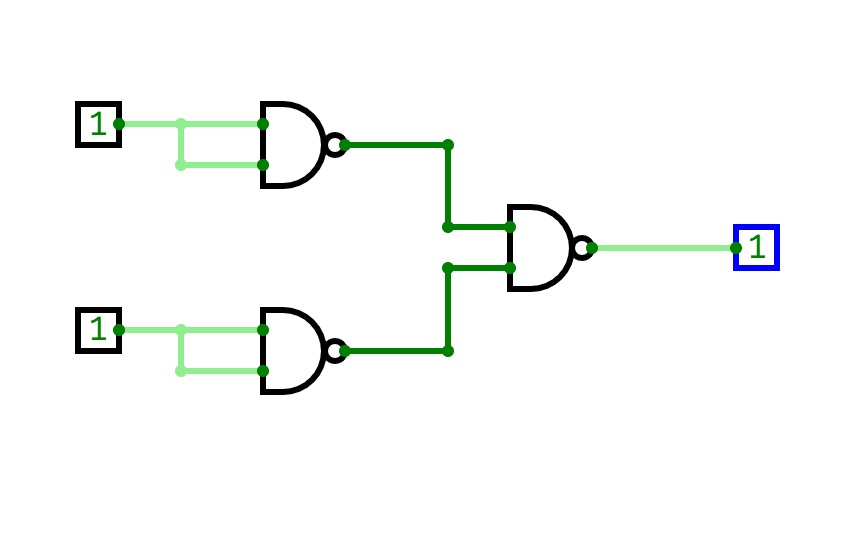

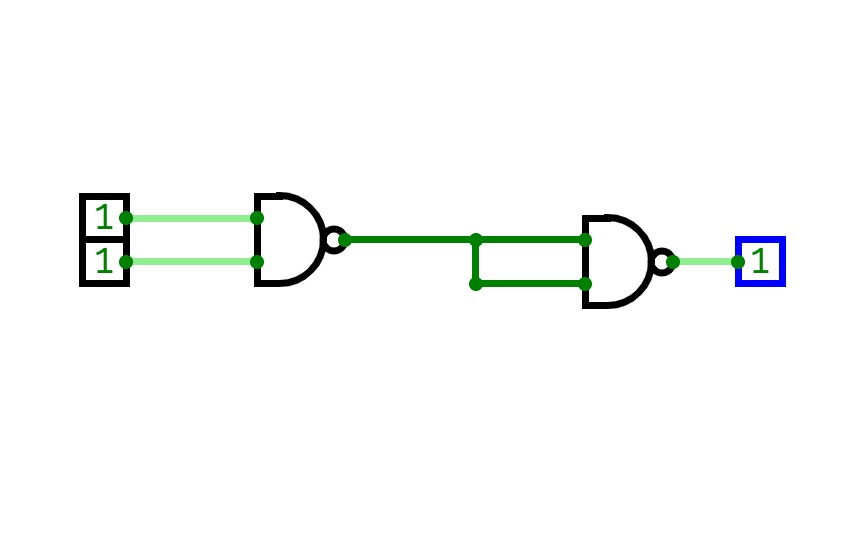

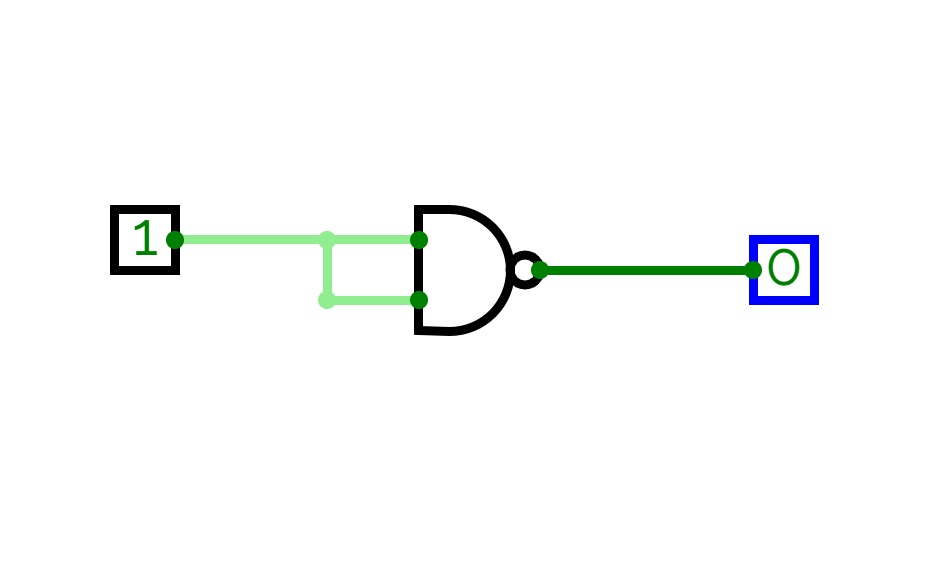

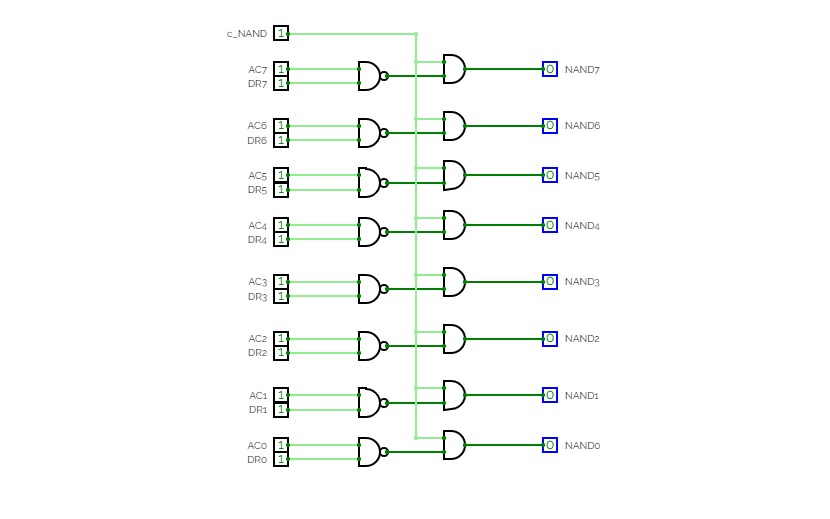

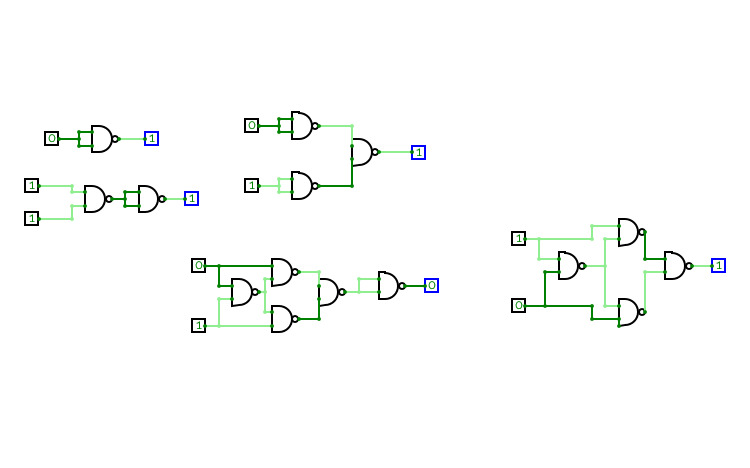

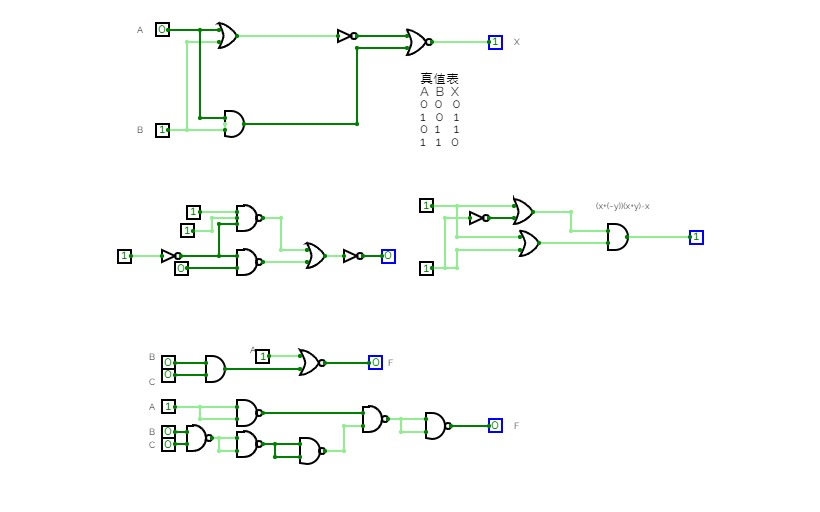

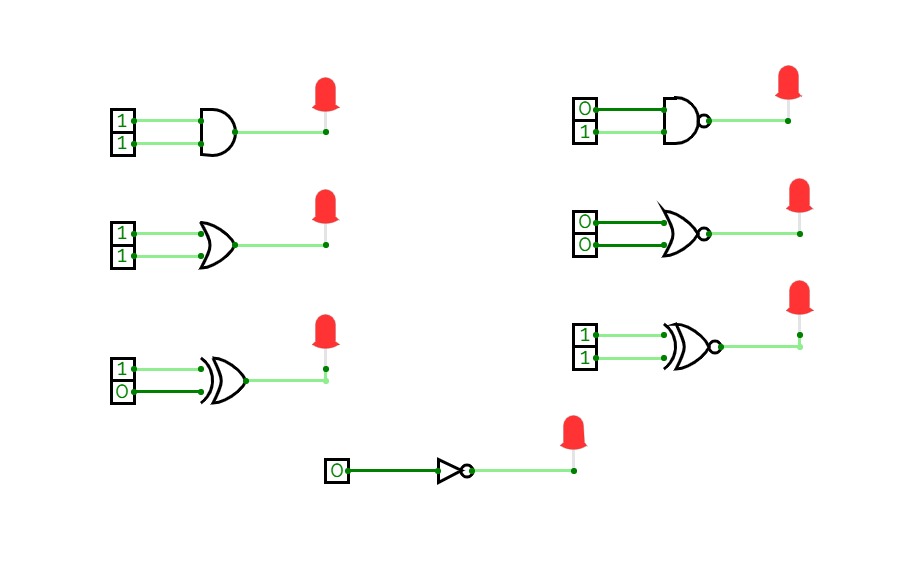

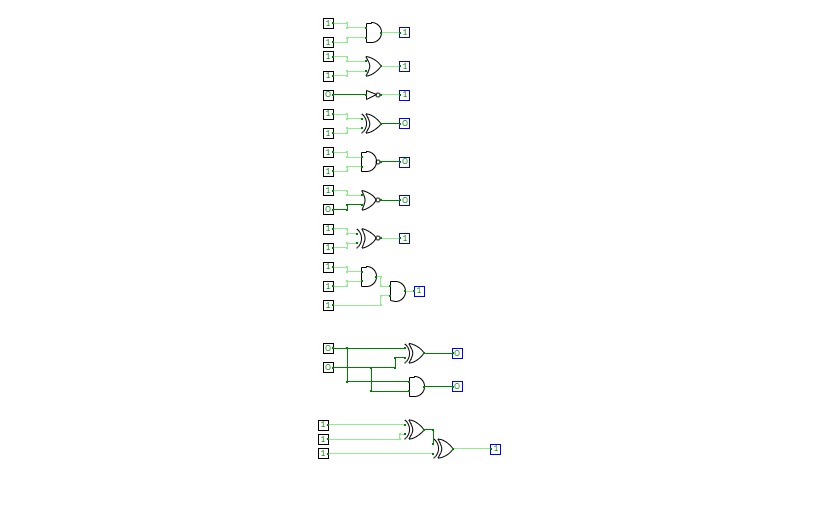

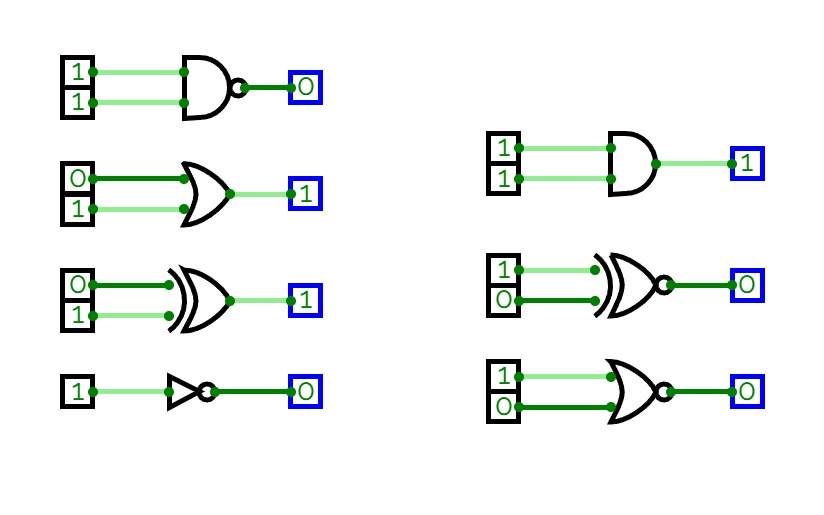

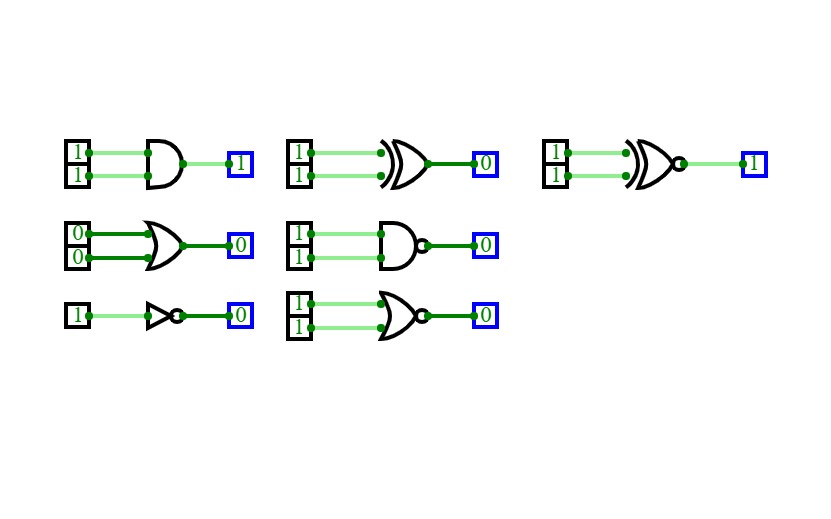

All possible functions with two arguments built using NAND gates

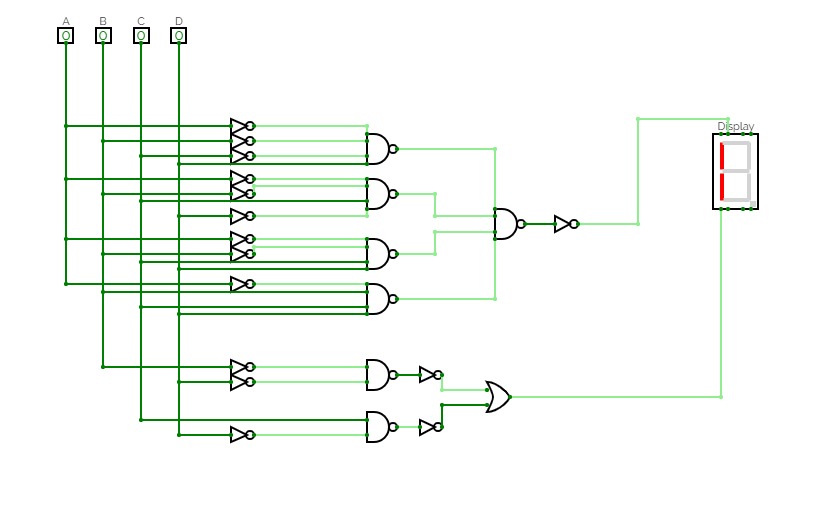

All possible functions with two arguments built using NAND gates7 Segment Decoder (Only NAND)

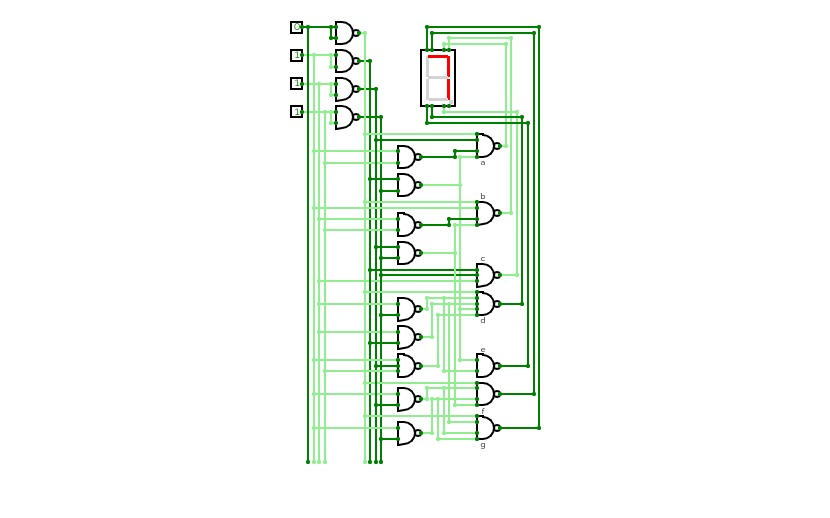

7 Segment Decoder (Only NAND)4-Bit 7-Segment Display using only NAND

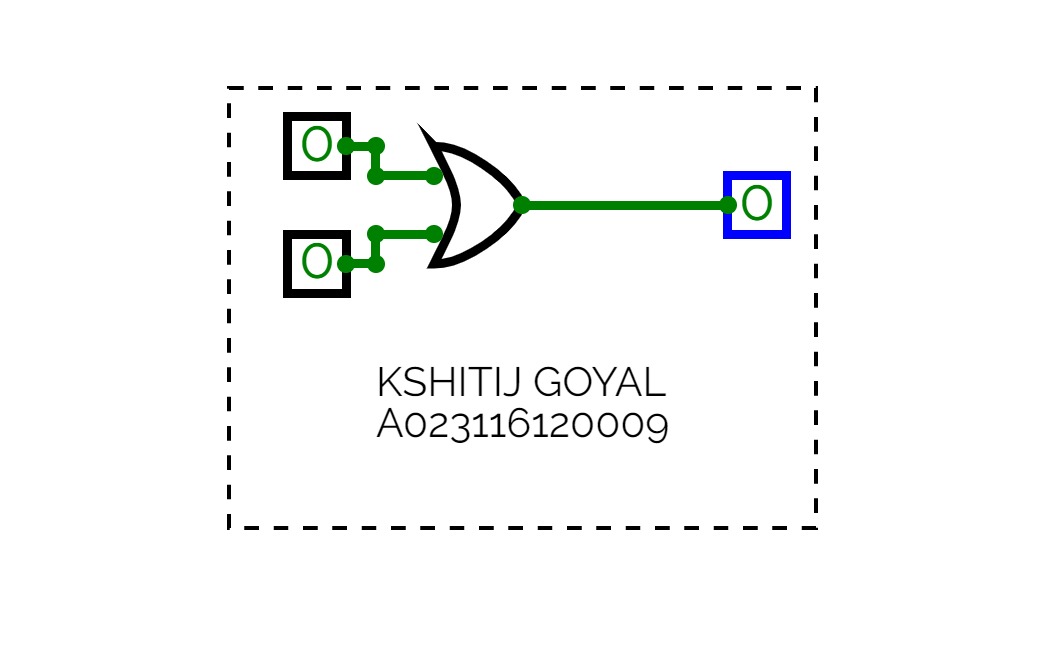

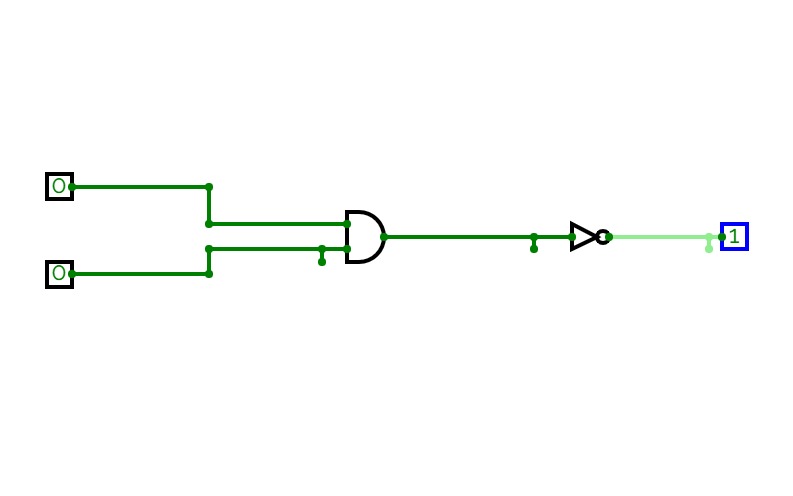

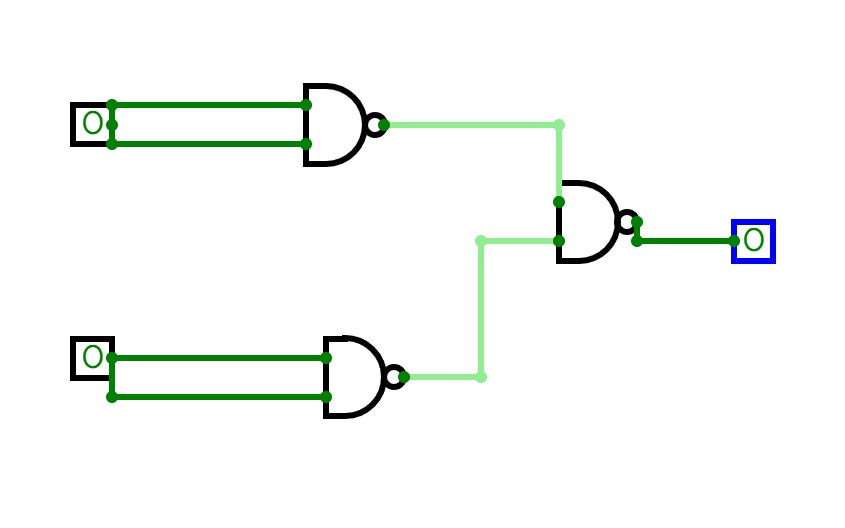

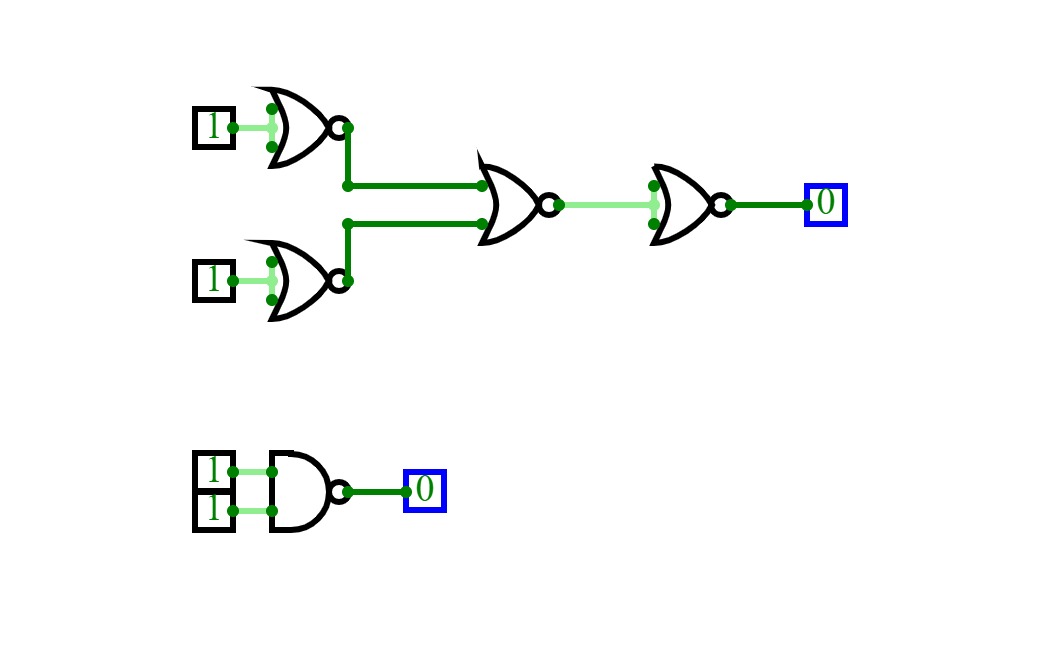

XNOR USING NAND GATES

XNOR USING NAND GATESaMISH Q1

aMISH Q1BCD NAND

BCD NANDBCH NAND

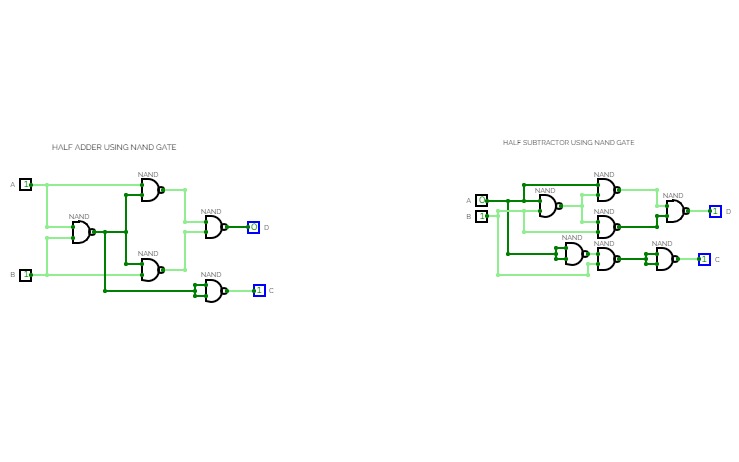

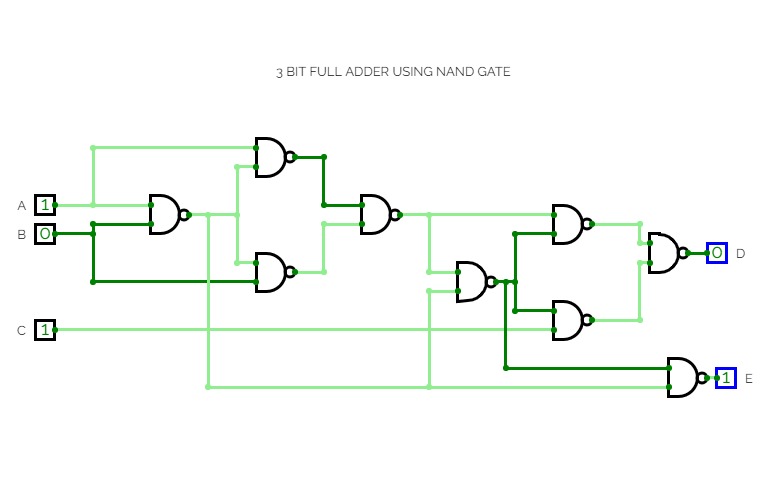

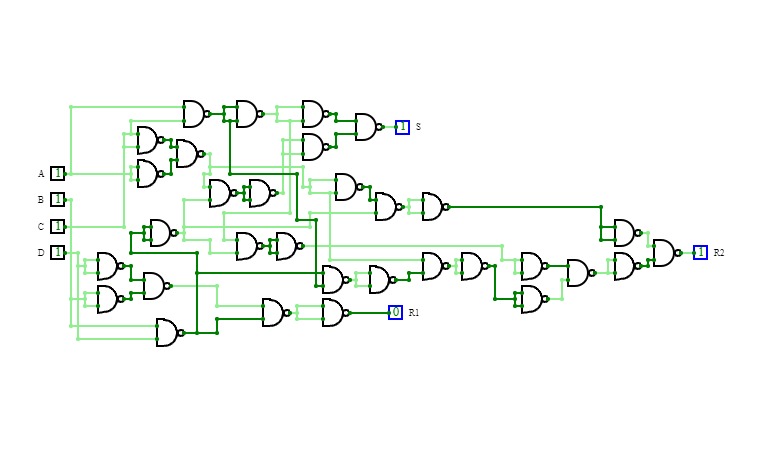

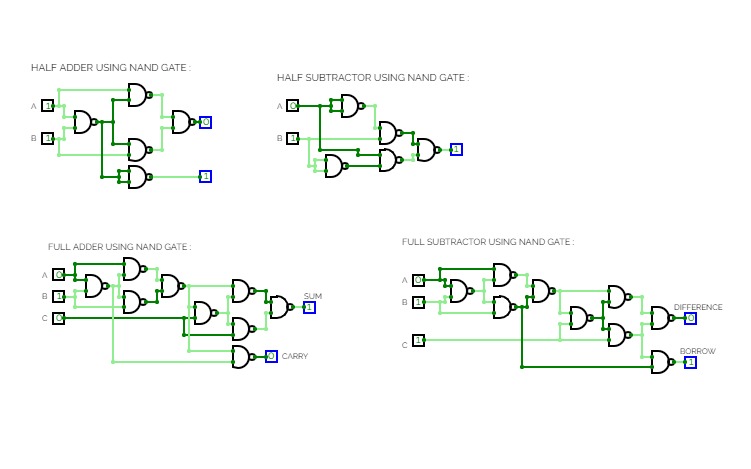

BCH NANDExperiment 1

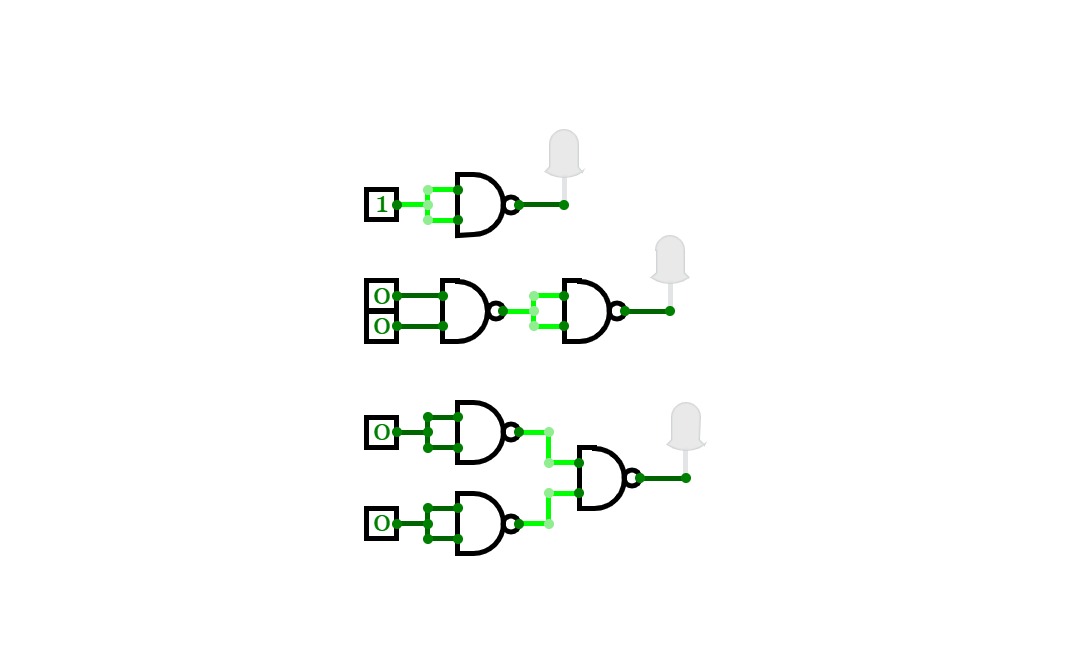

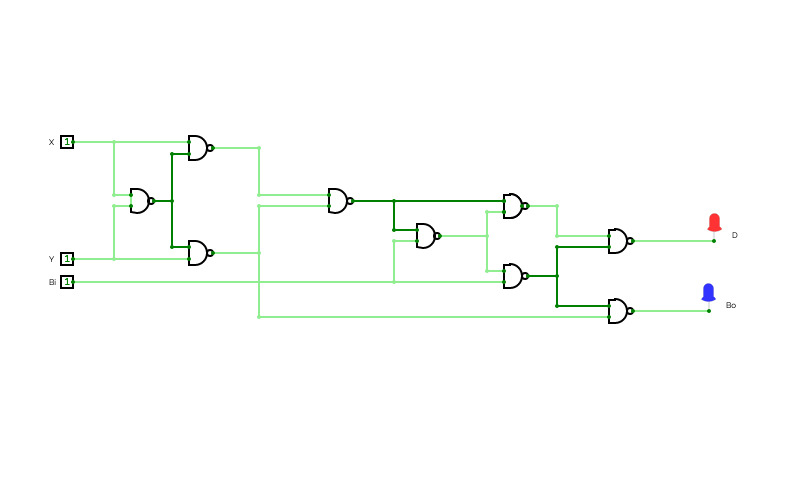

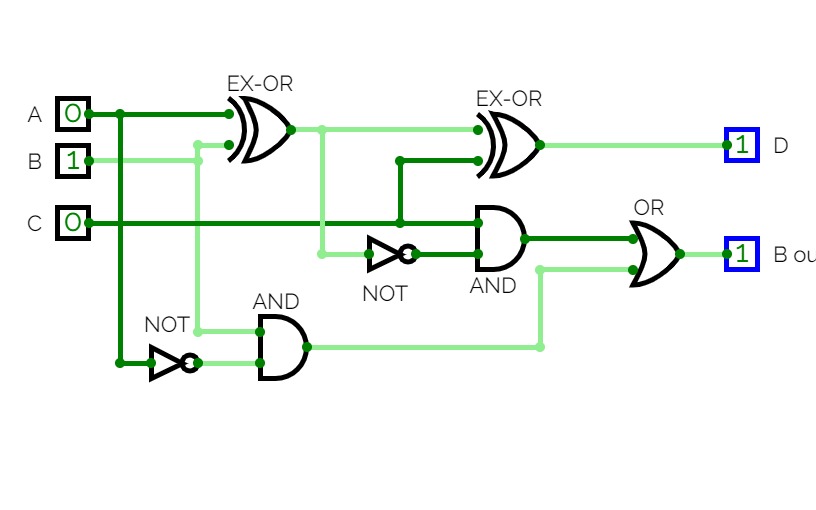

Experiment 1DL_CO_Full_Subtractor_NAND_2147033

DL_CO_Full_Subtractor_NAND_2147033Full Subtractor using NAND Gates

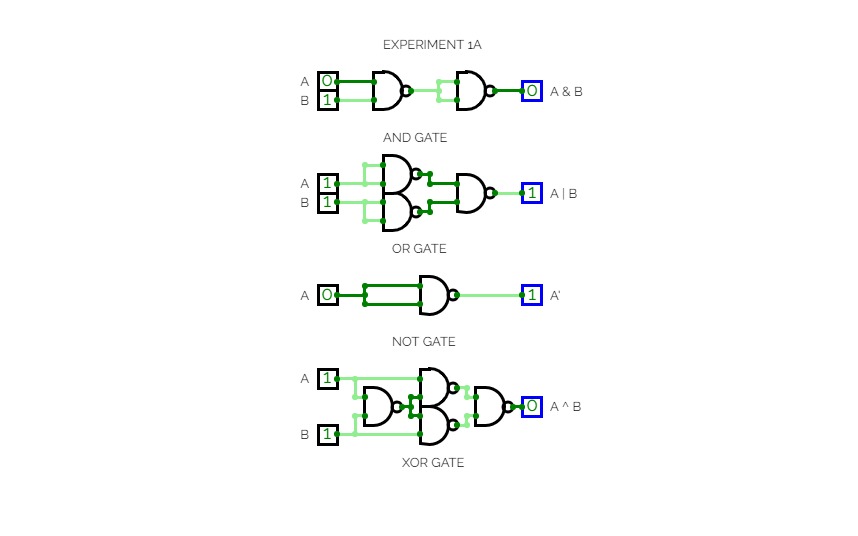

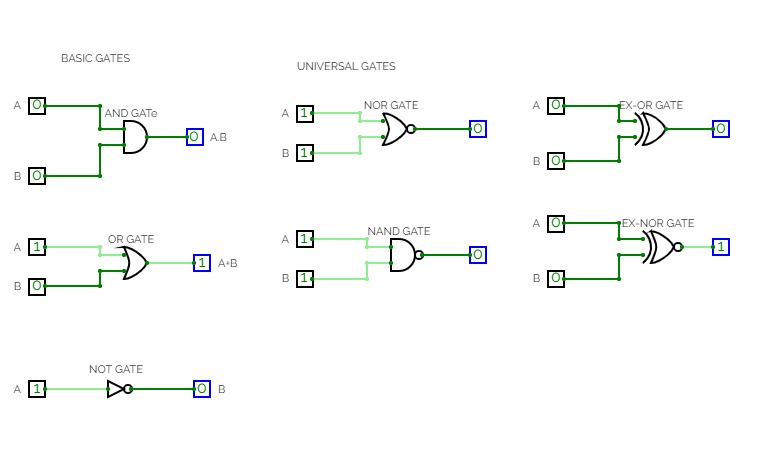

EXPERIMENT 1A

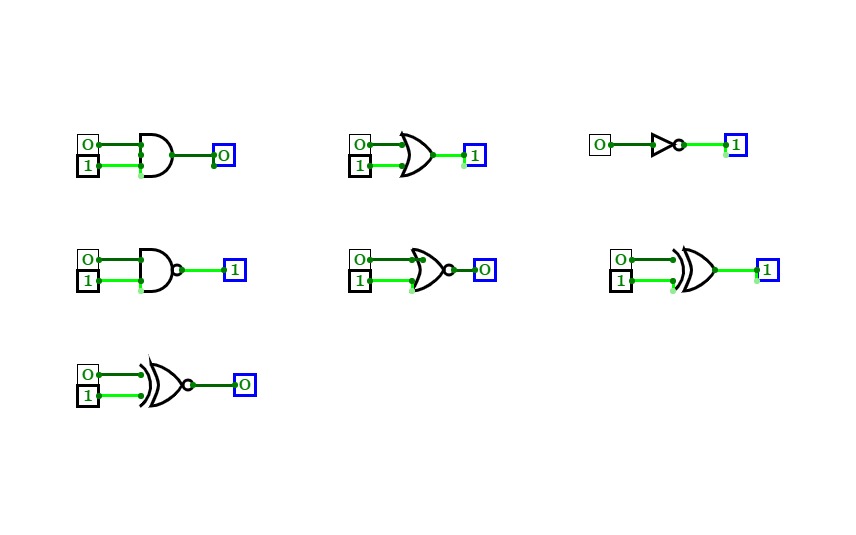

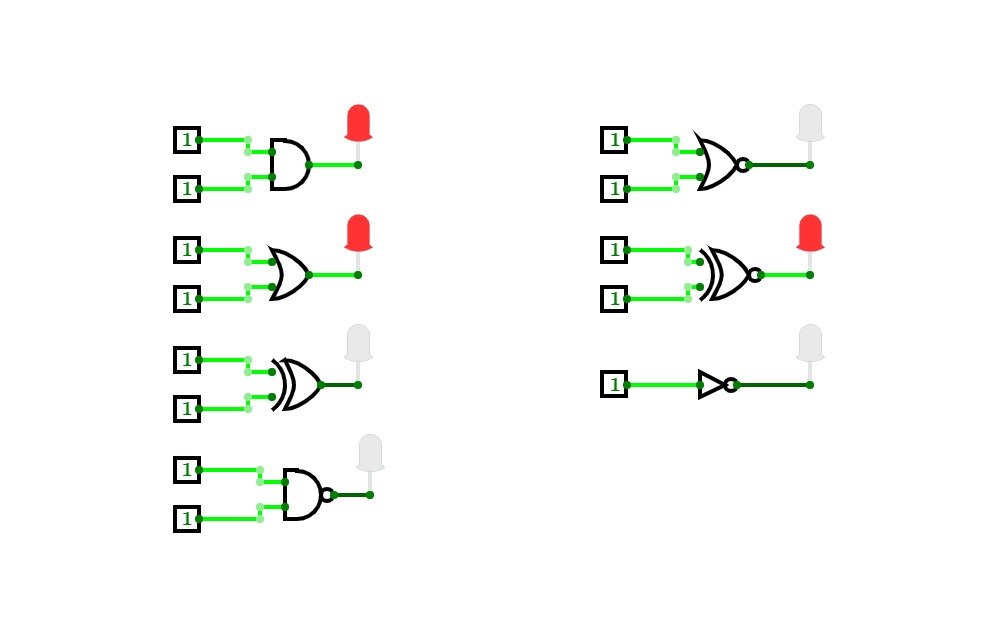

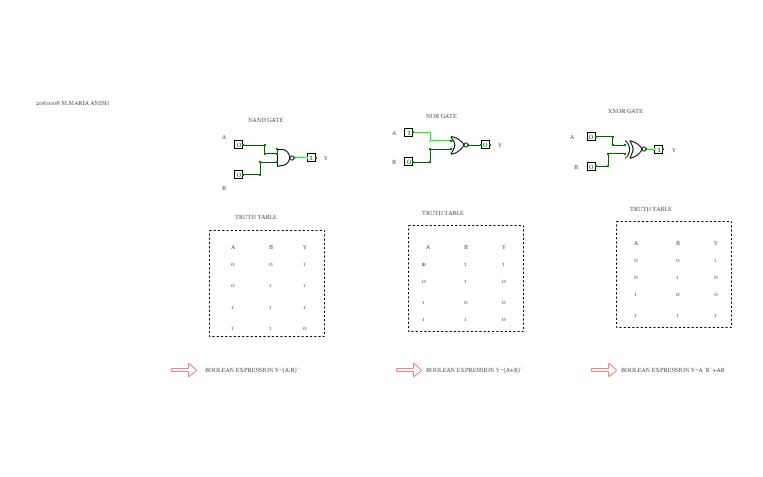

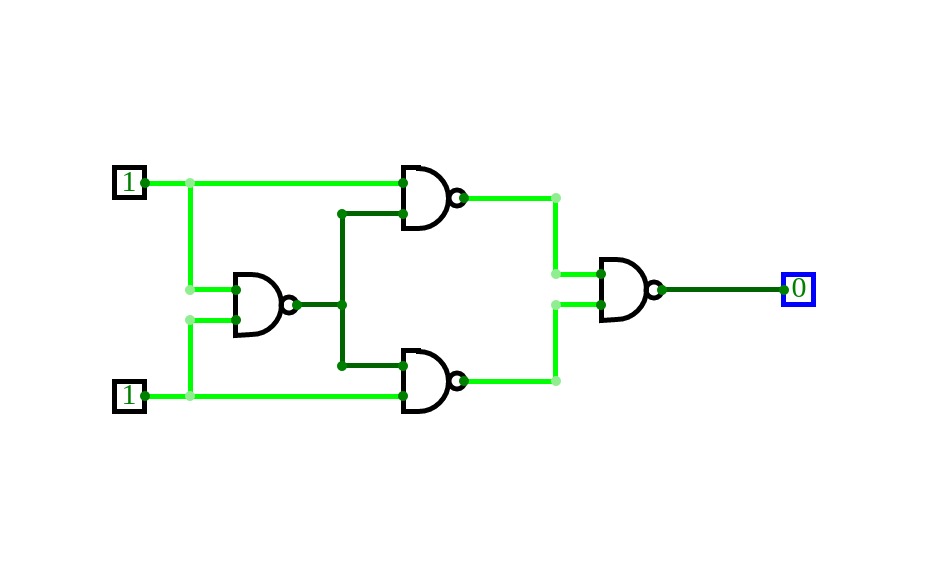

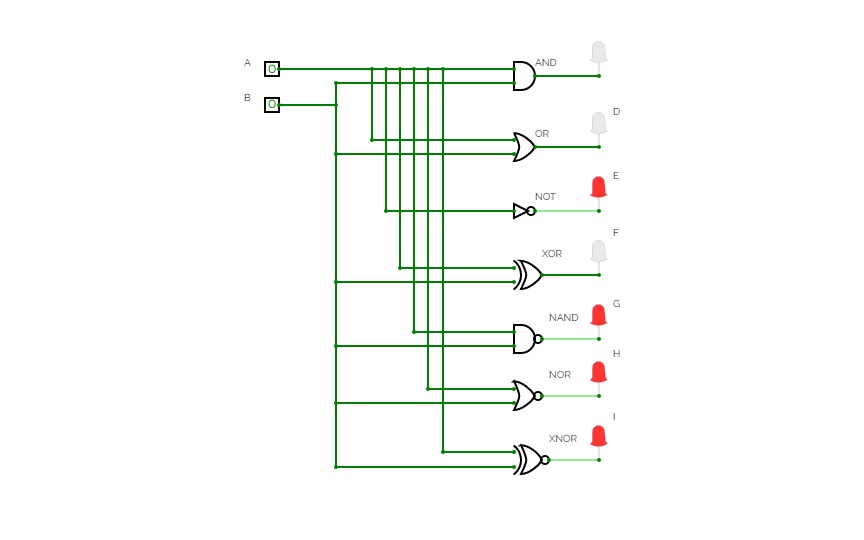

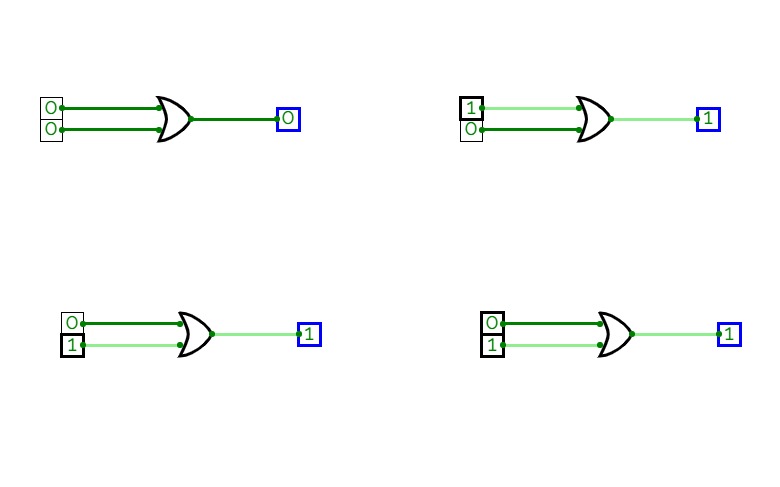

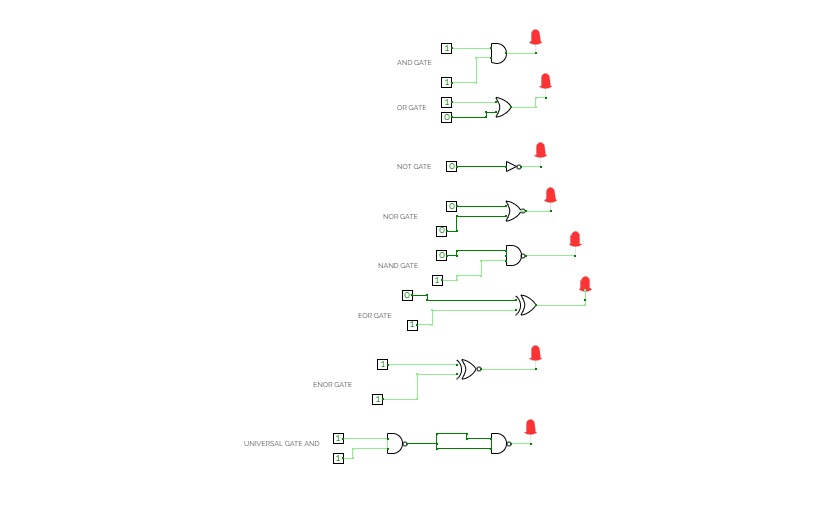

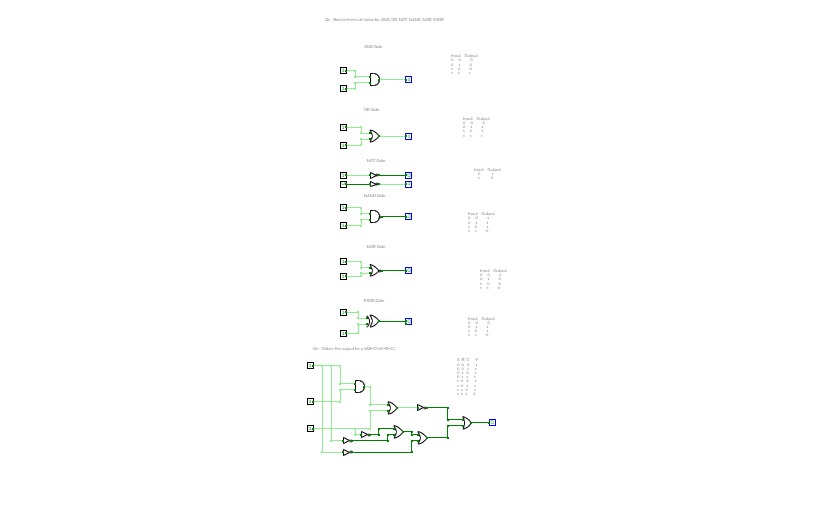

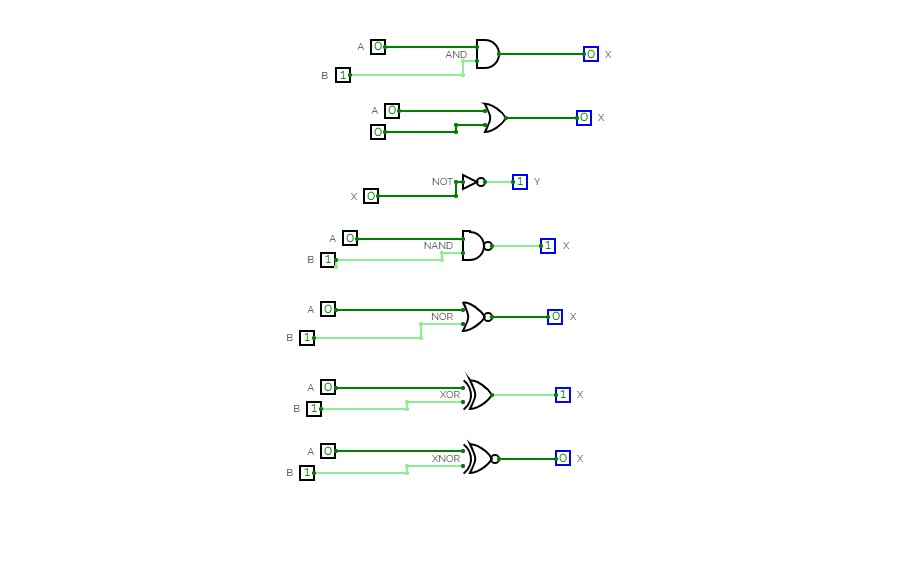

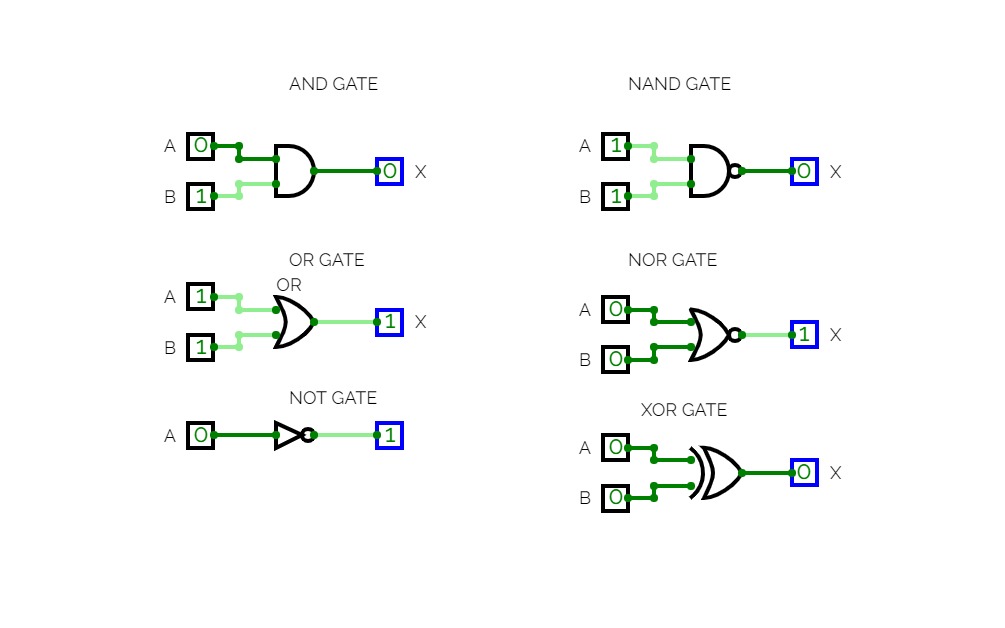

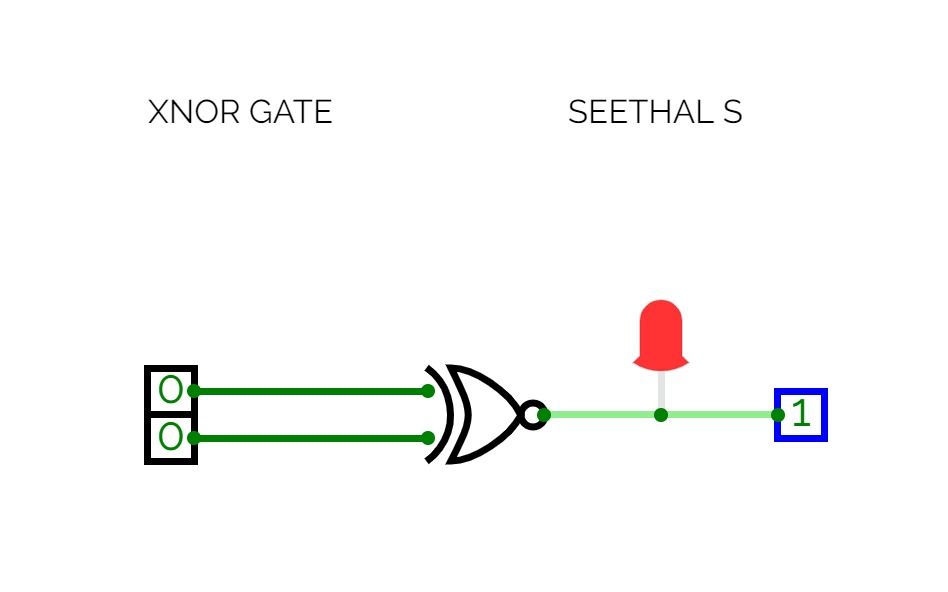

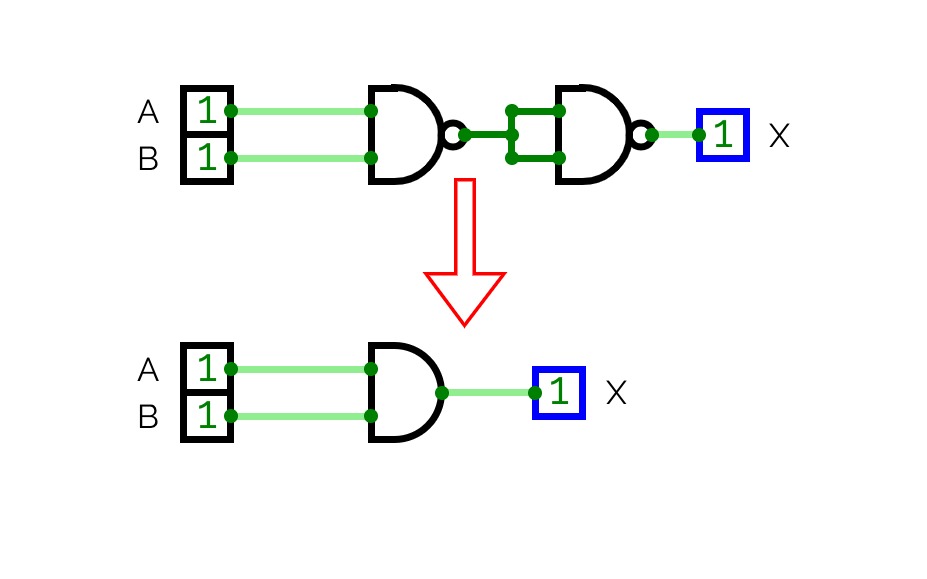

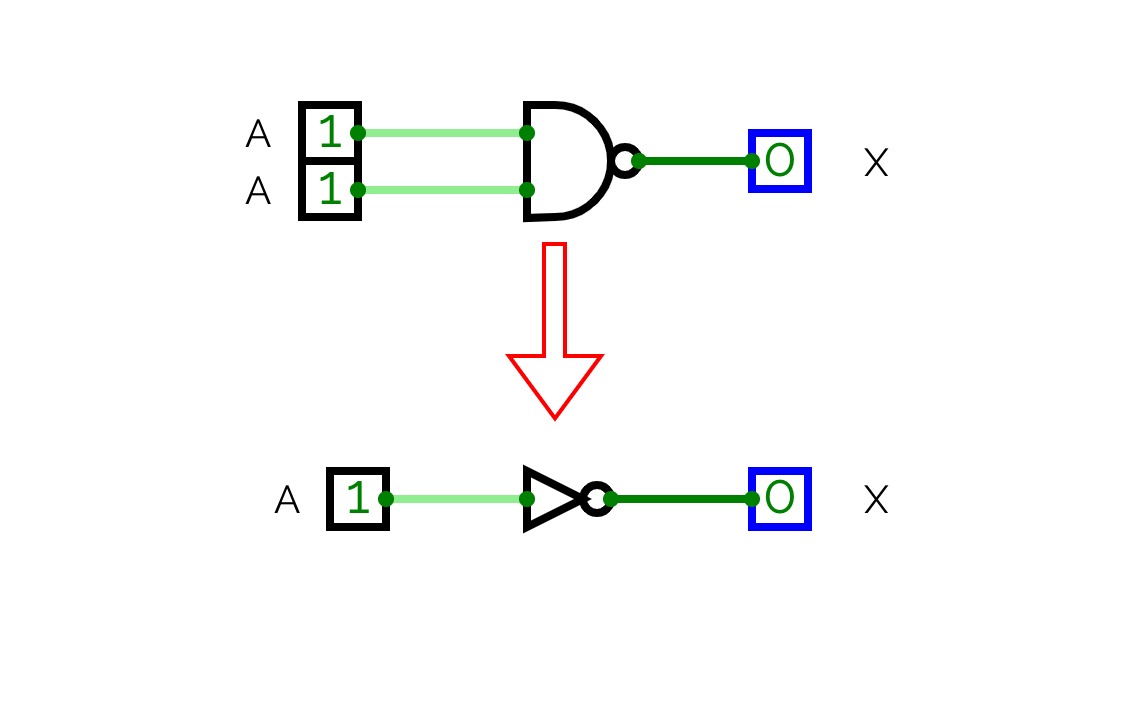

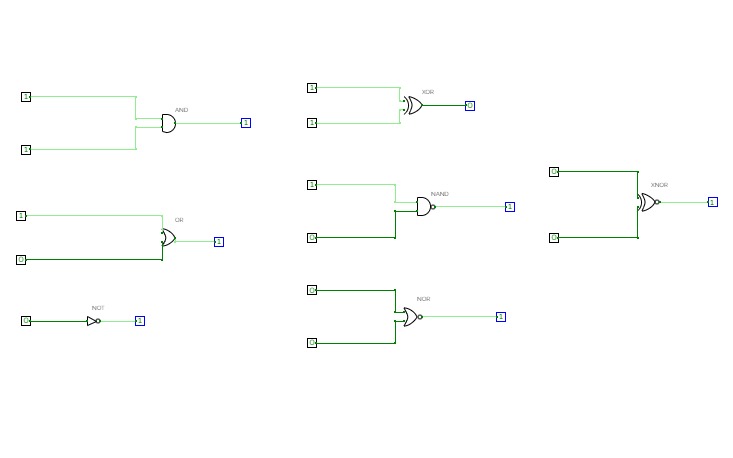

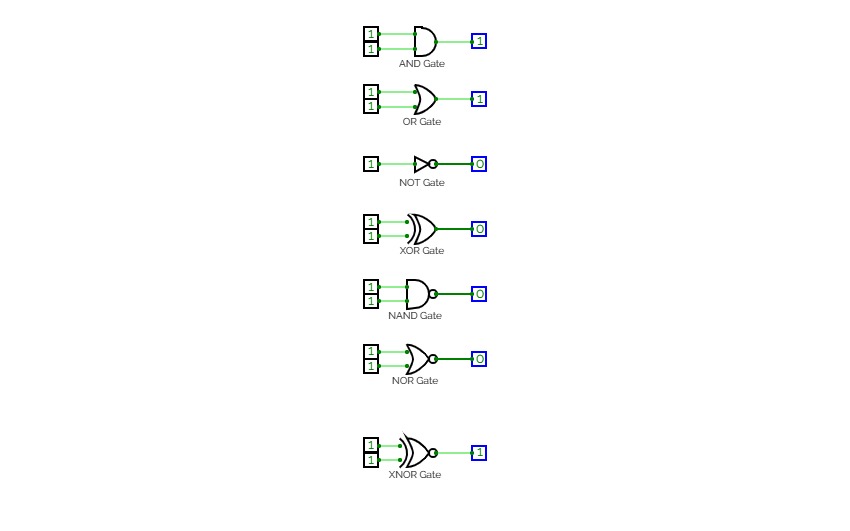

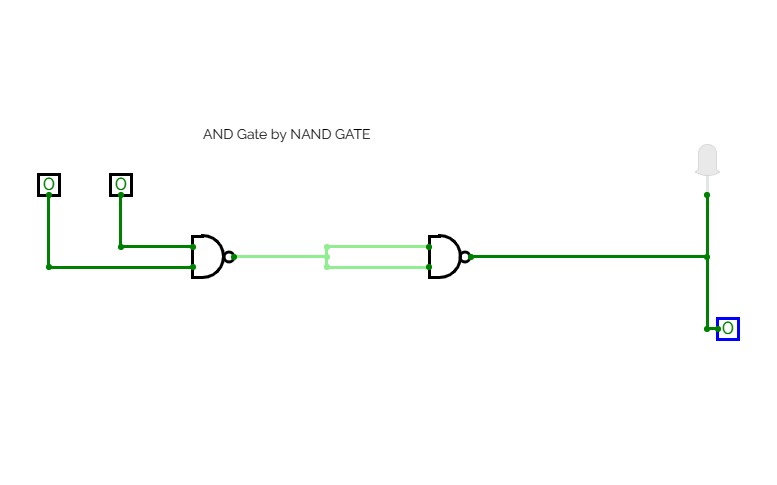

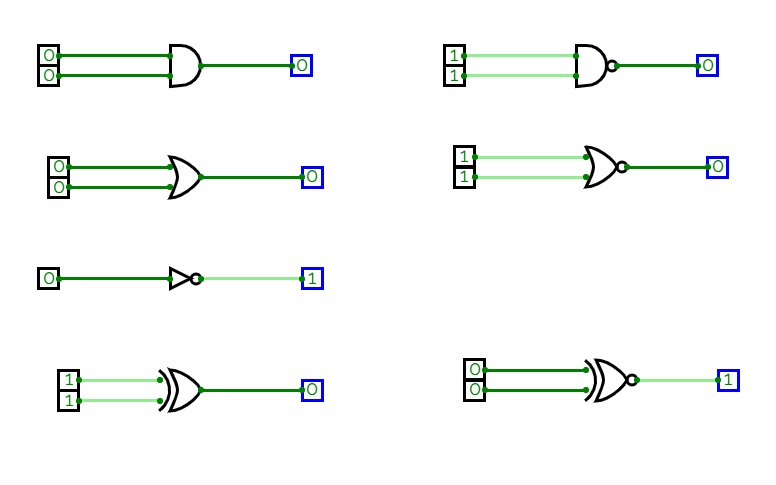

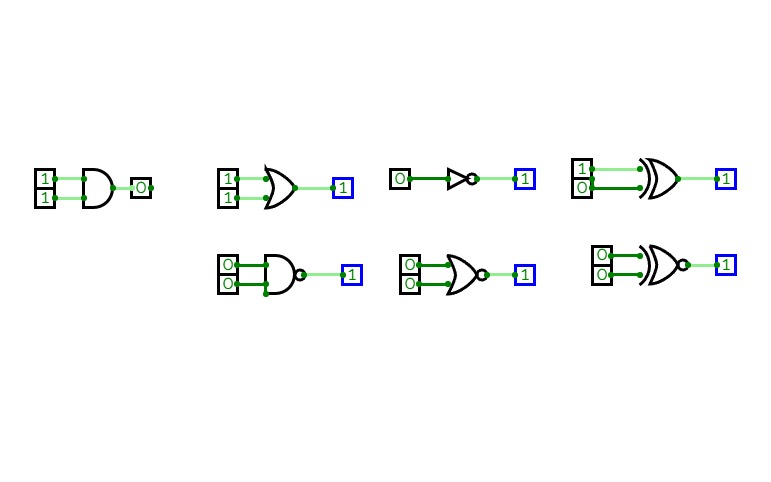

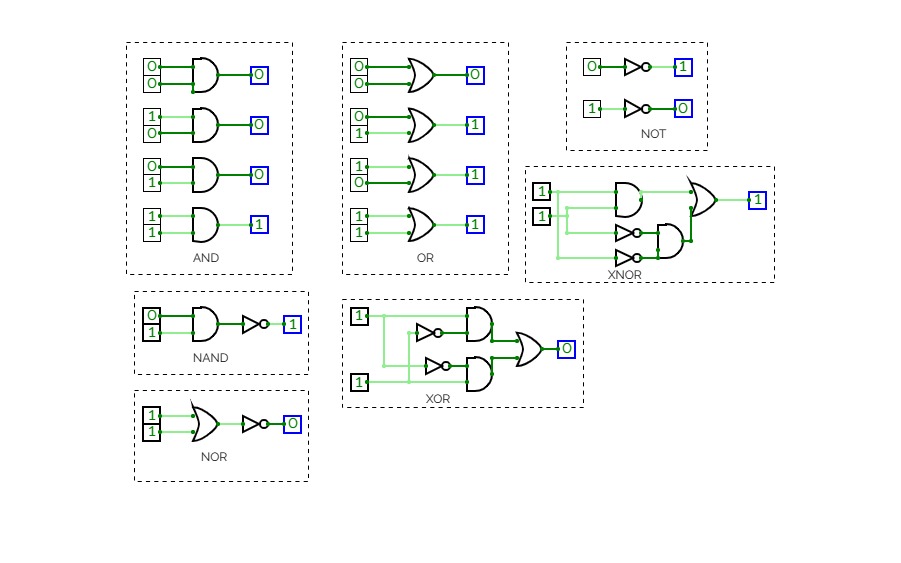

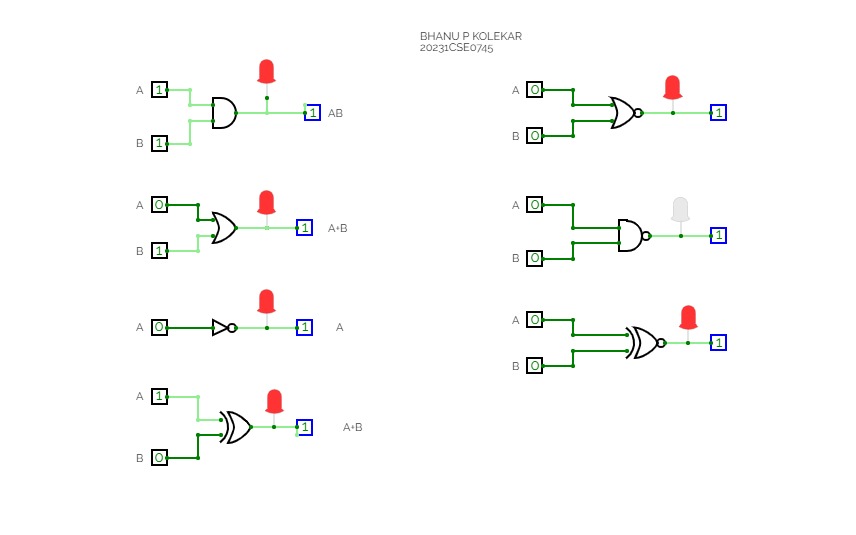

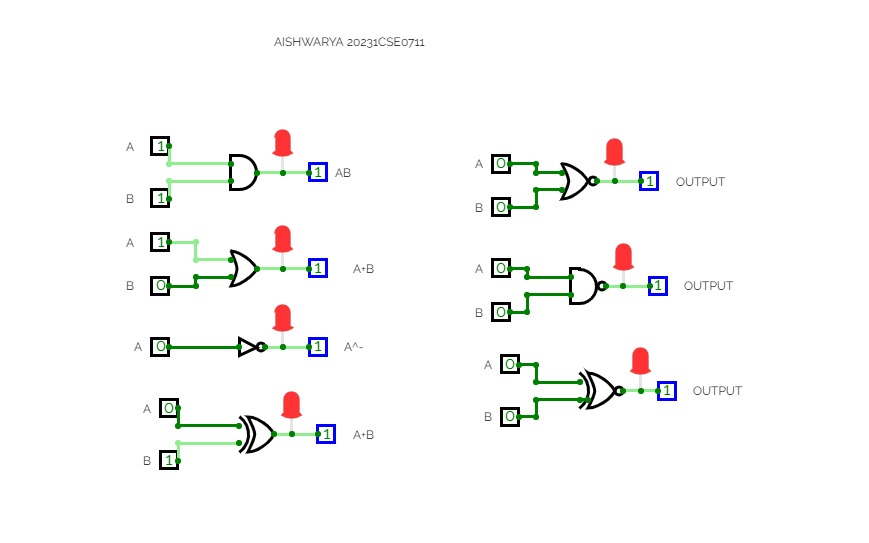

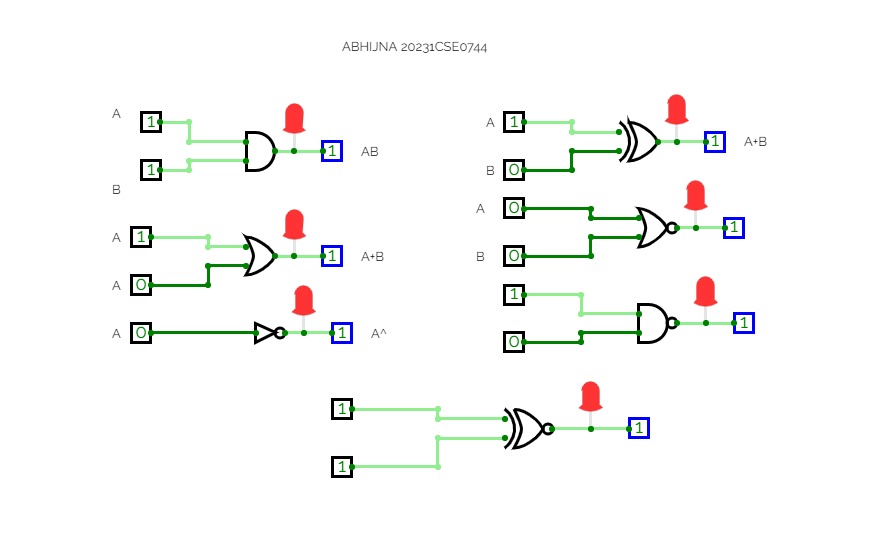

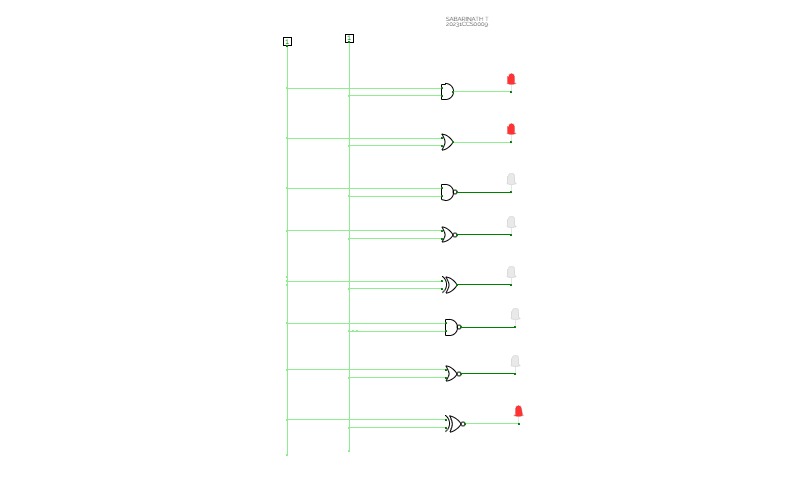

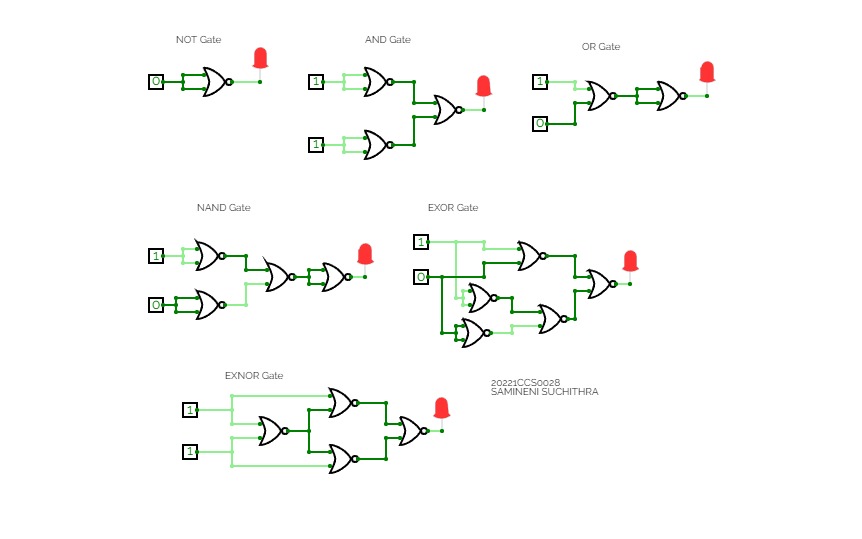

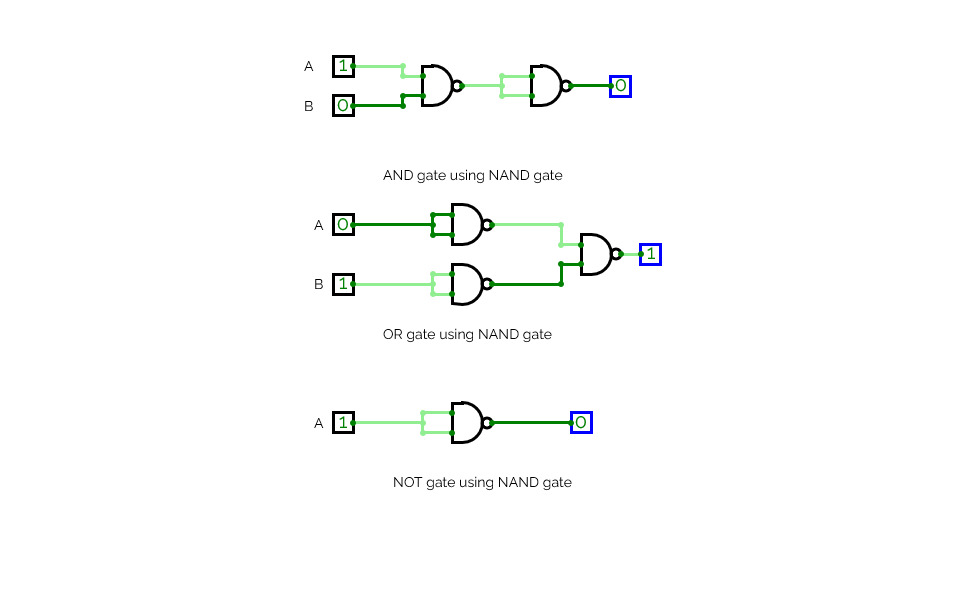

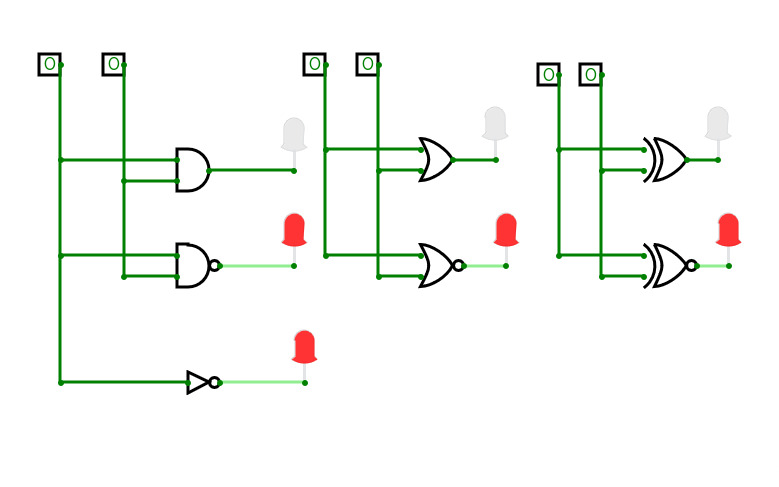

EXPERIMENT 1AConstruction of Basic Gates, i.e. AND, OR, NOT, XOR using Universal Gate NAND

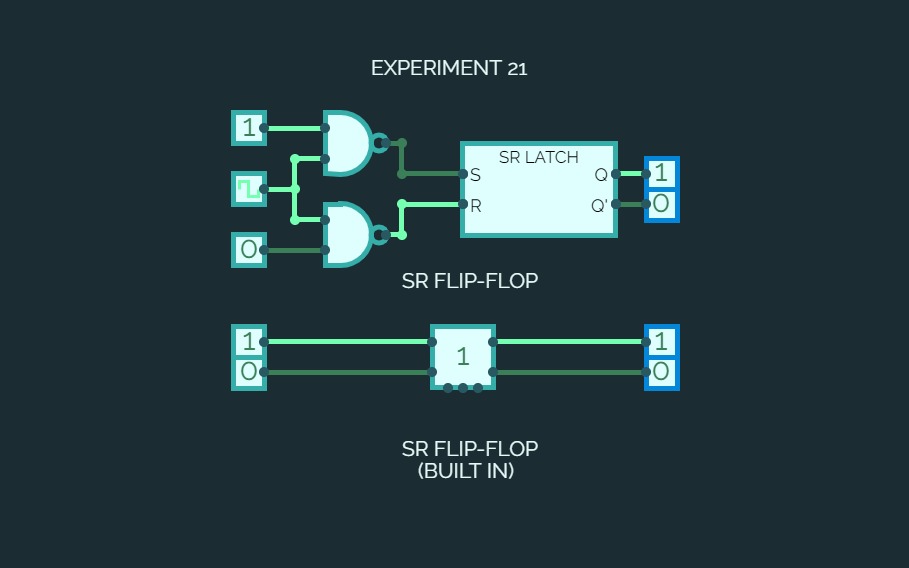

EXPERIMENT 21

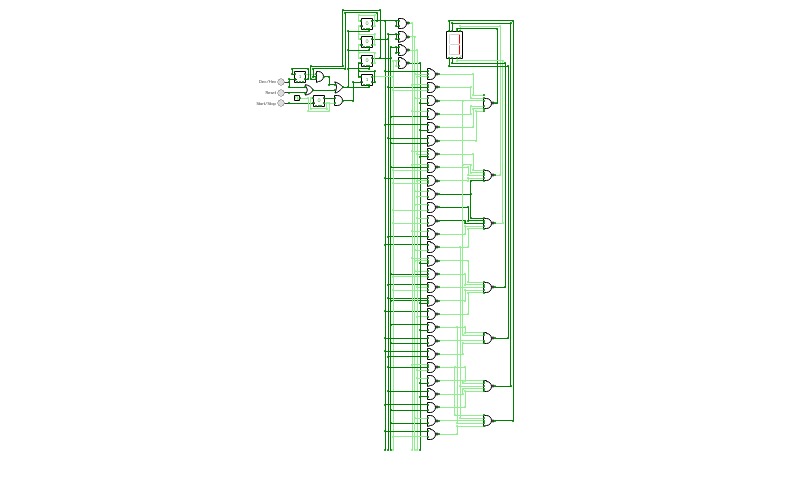

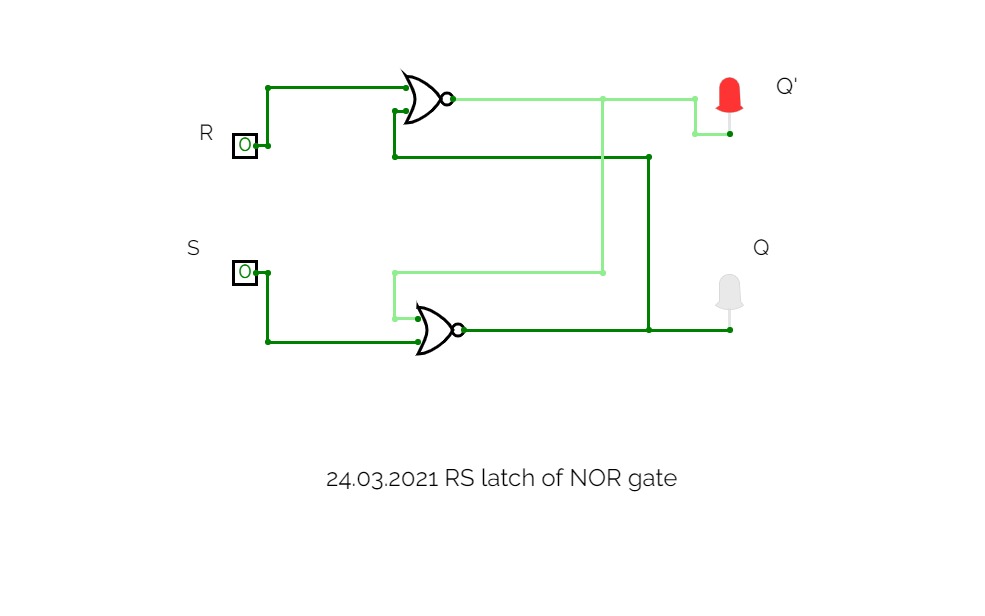

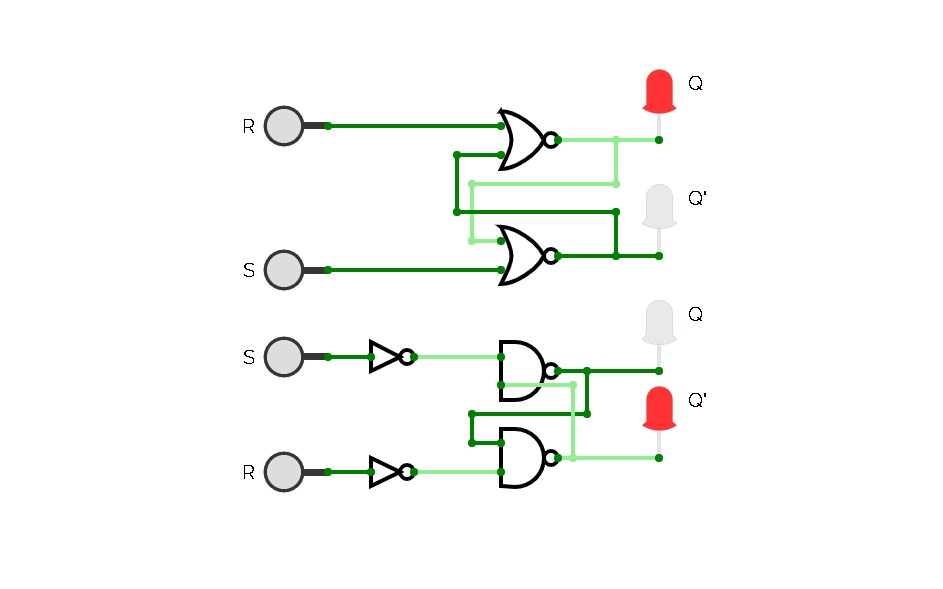

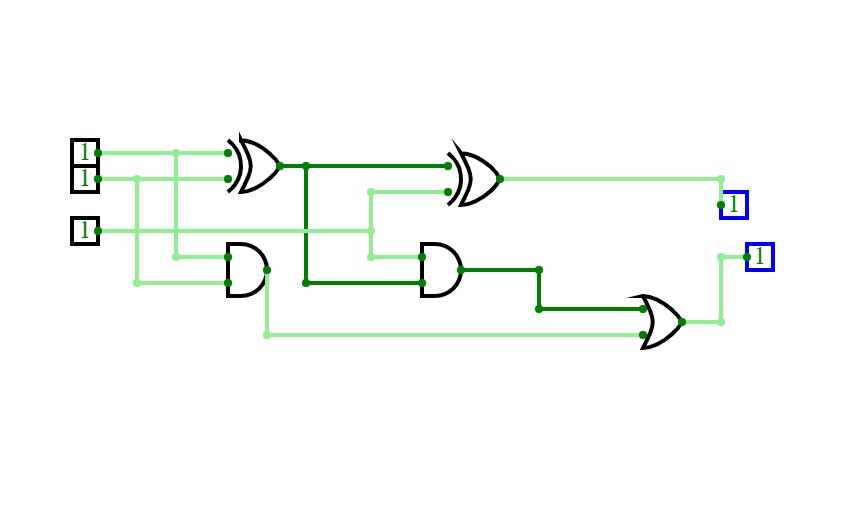

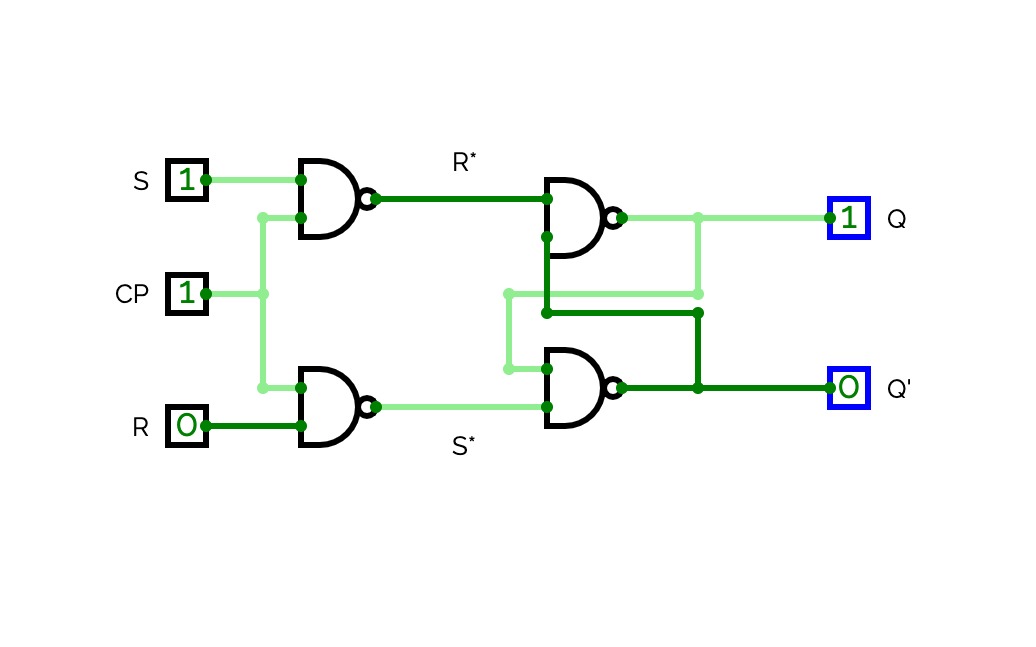

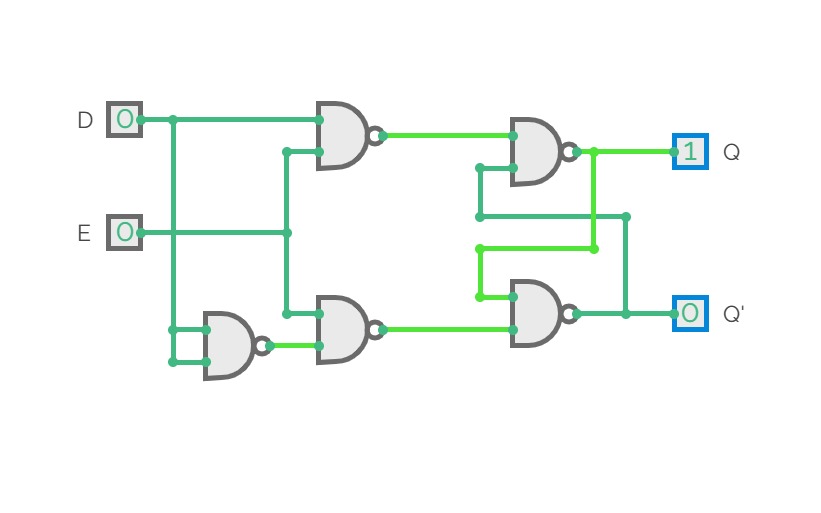

EXPERIMENT 21Implementation of SR FLIP-FLOP using SR-LATCH

Implementation of SR LATCH using NAND Gate

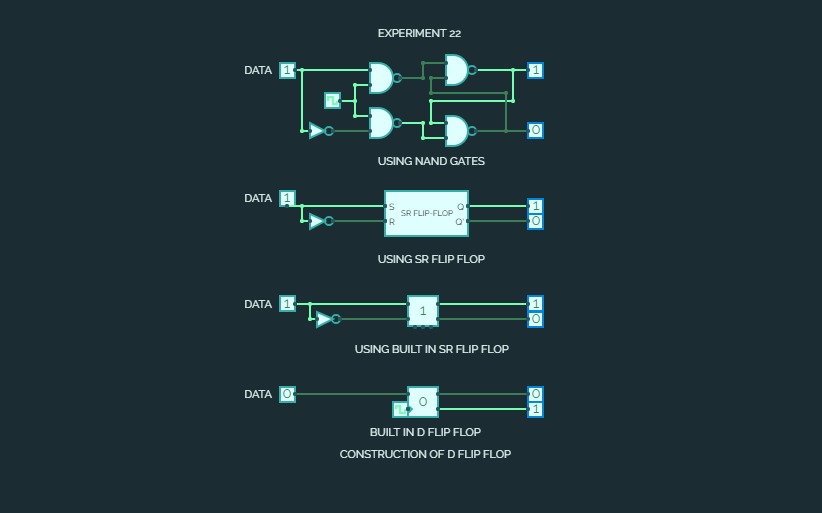

EXPERIMENT 22

EXPERIMENT 22Implementation of D FLIP-FLOP Using SR-Latch and NAND Gates

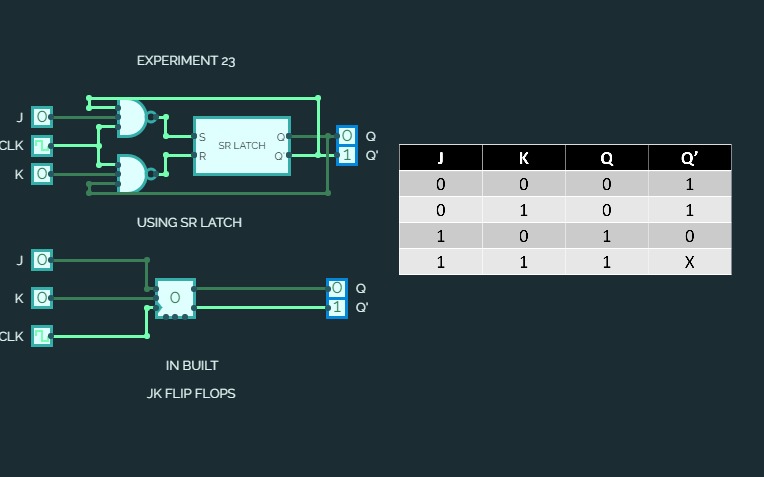

EXPERIMENT 23

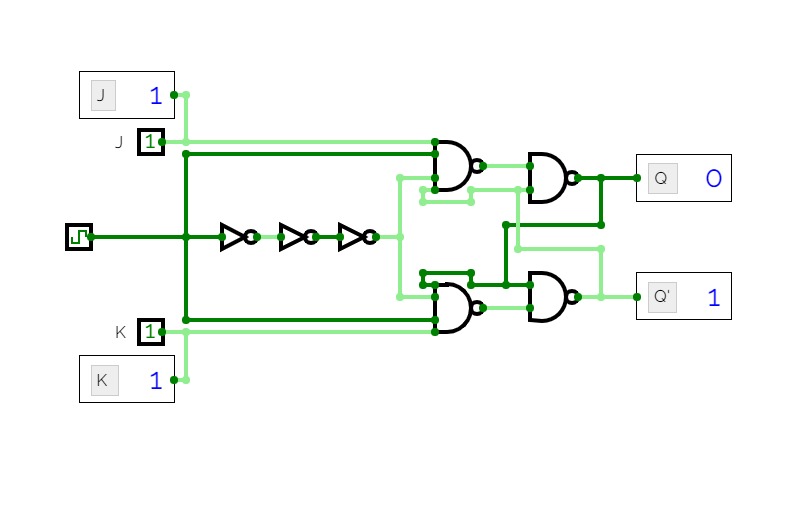

EXPERIMENT 23Implementation of JK FLIP FLOP

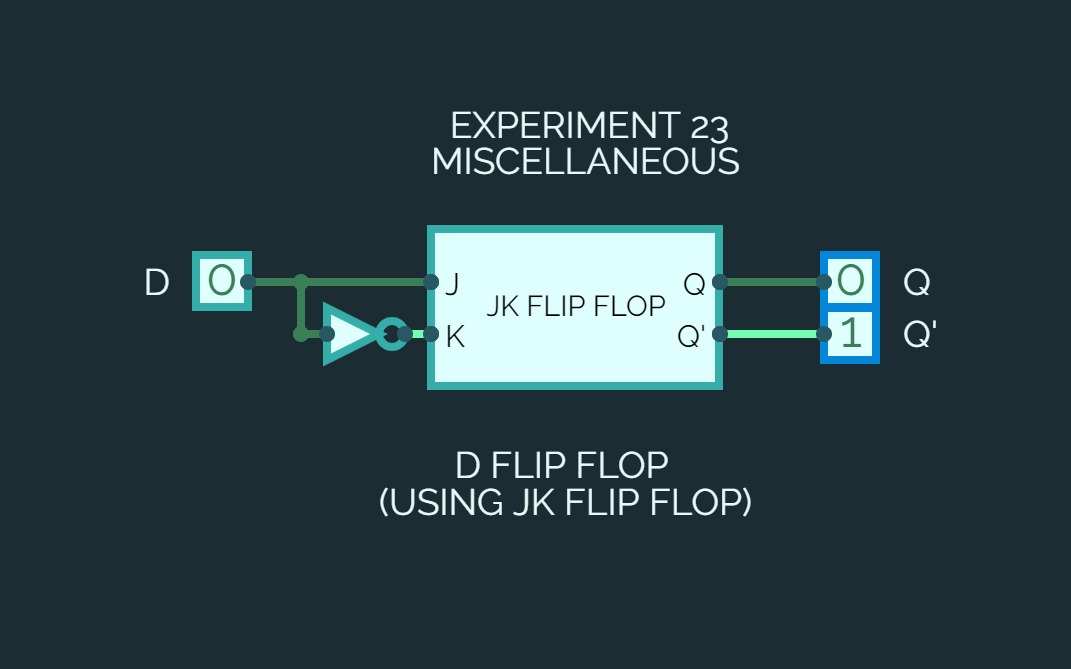

EXPERIMENT 23 MISC

EXPERIMENT 23 MISCImplementation of D FLIP-FLOP using JK FLIP-FLOP

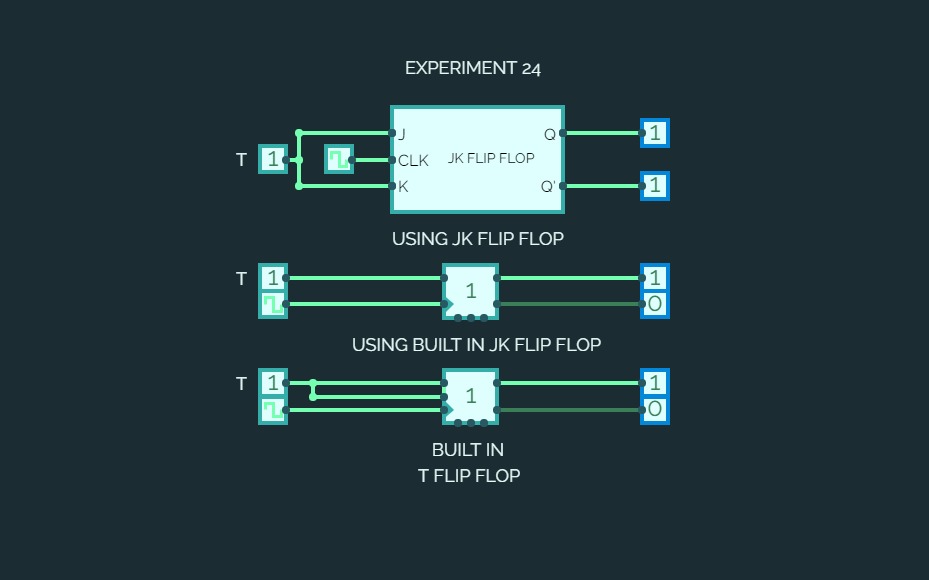

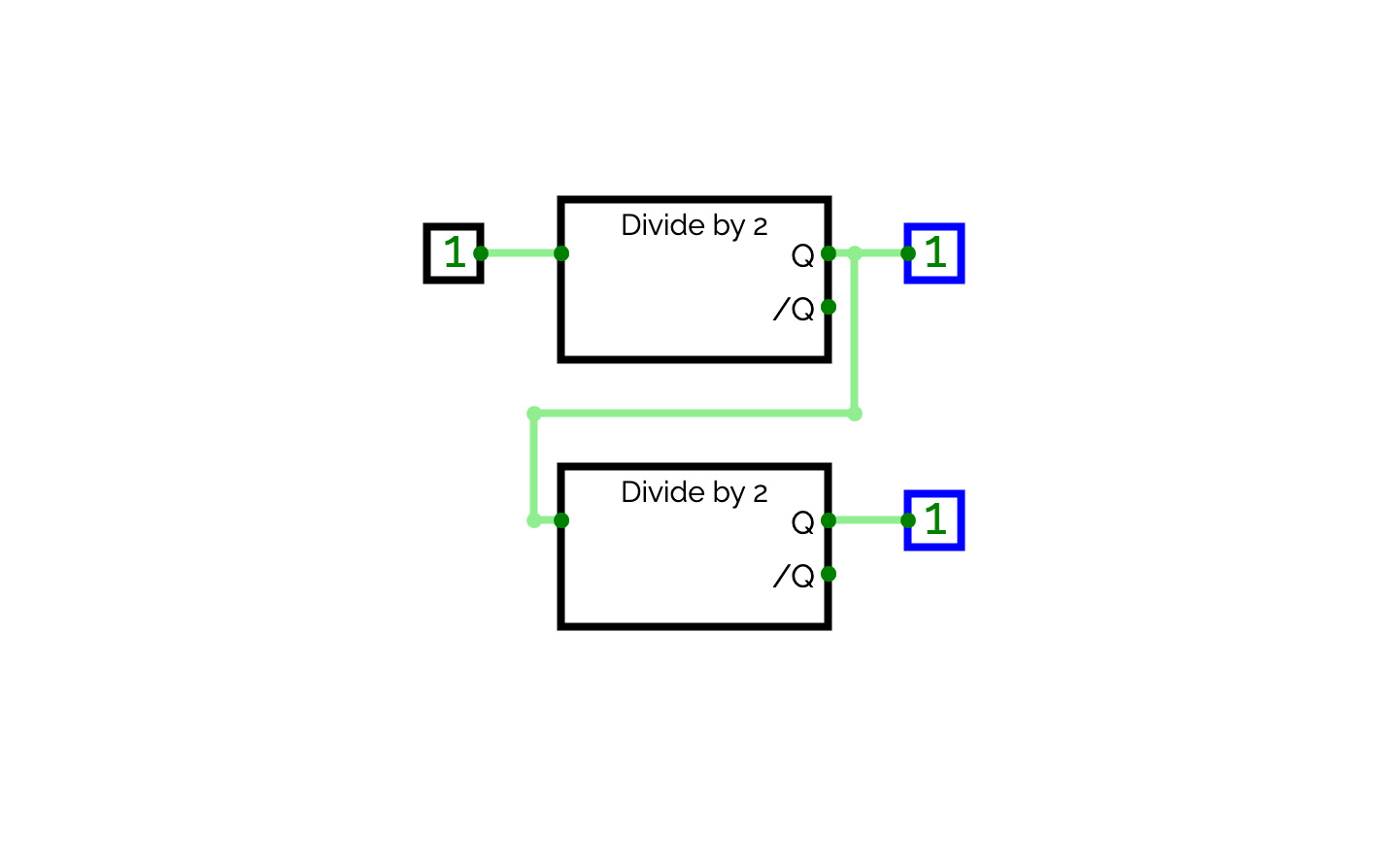

EXPERIMENT 24

EXPERIMENT 24Implementation of a T FLIP-FLOP using JK FLIP FLOP

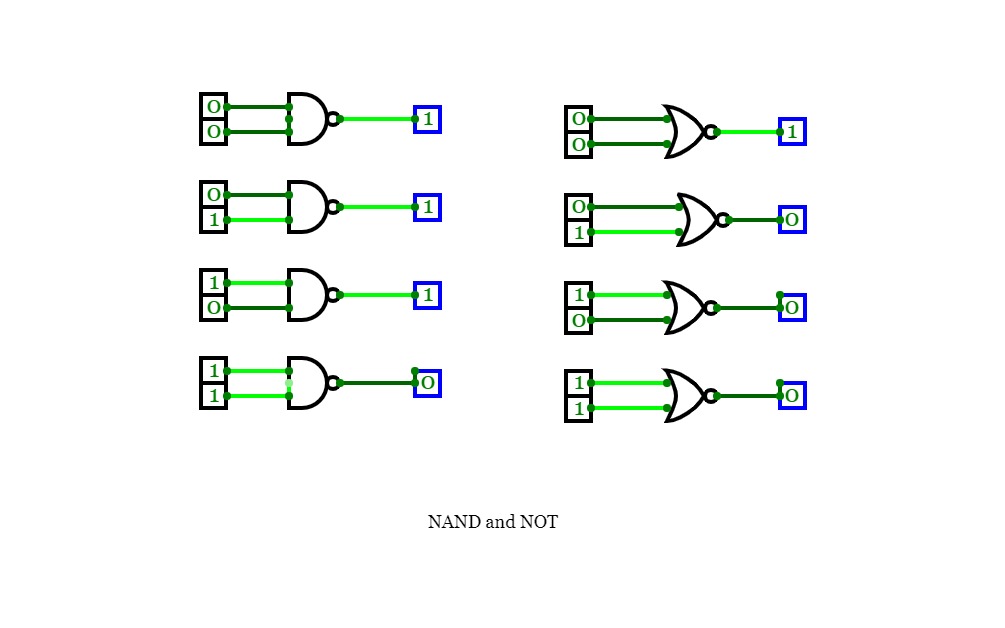

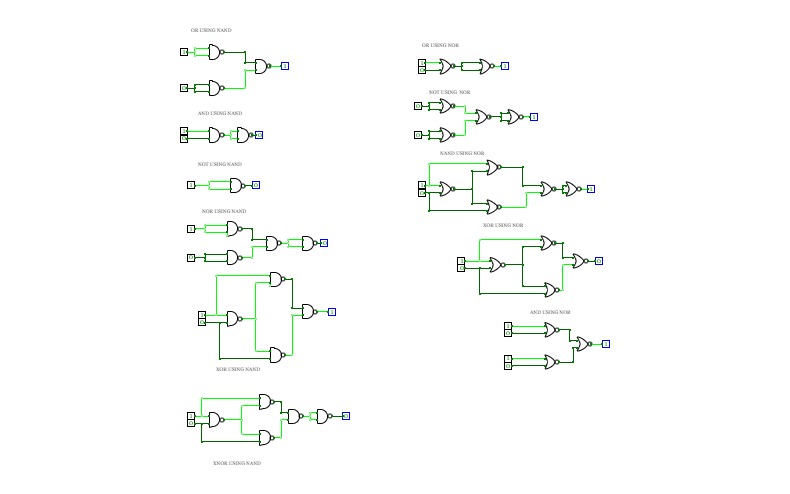

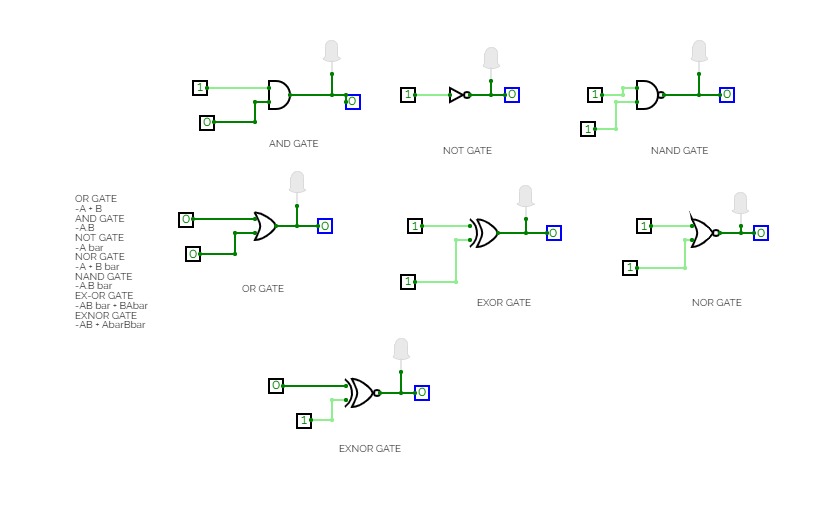

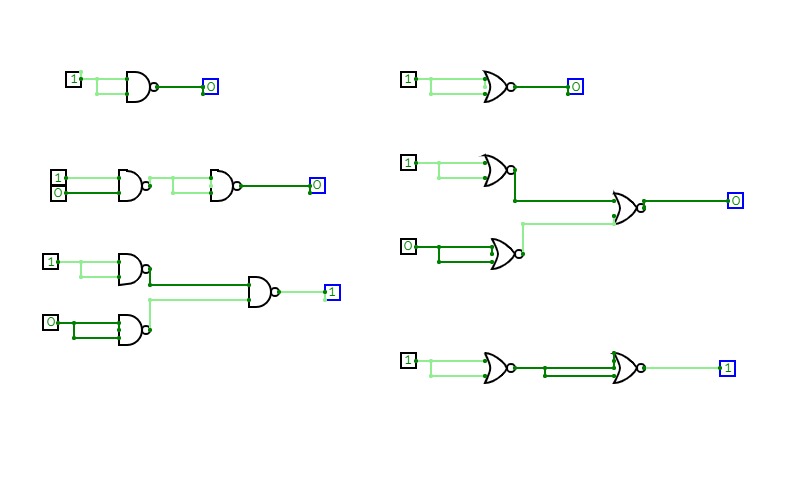

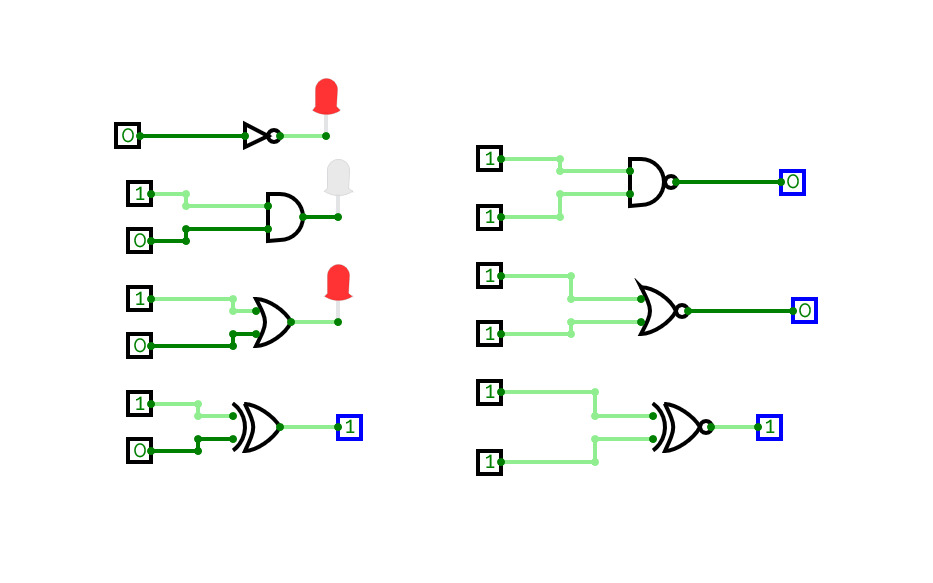

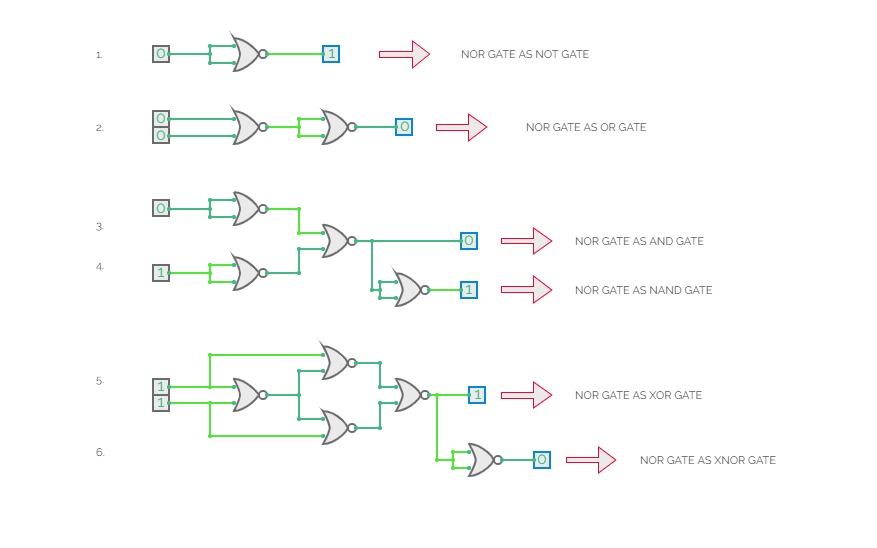

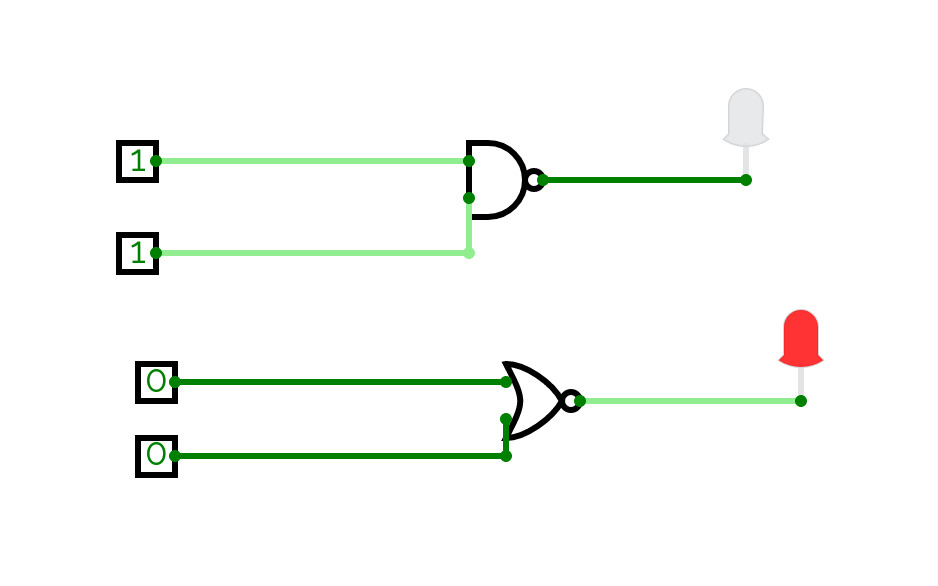

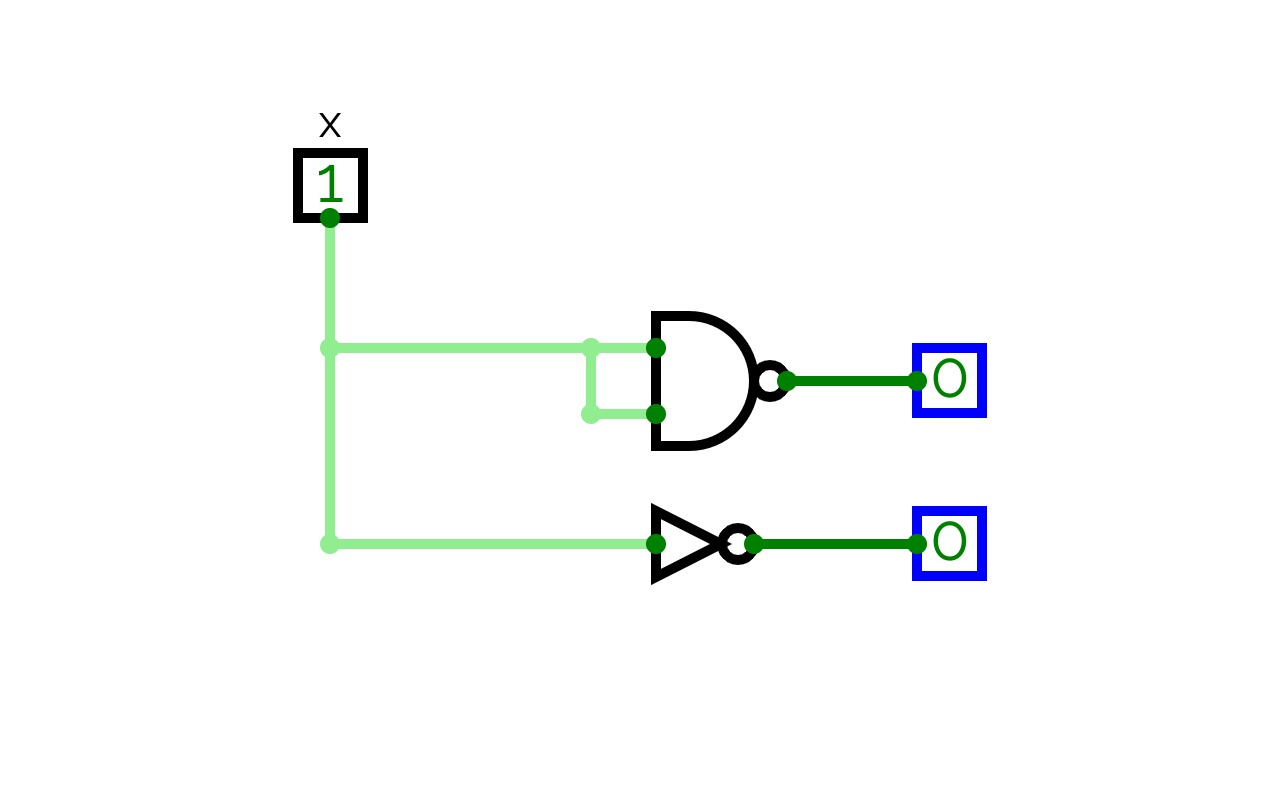

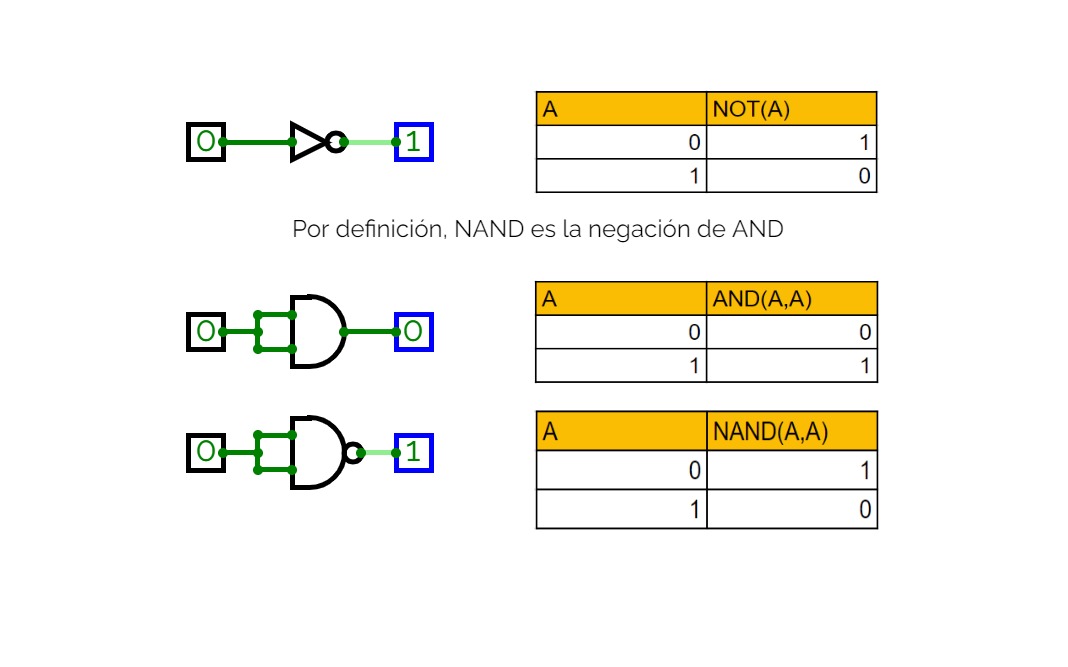

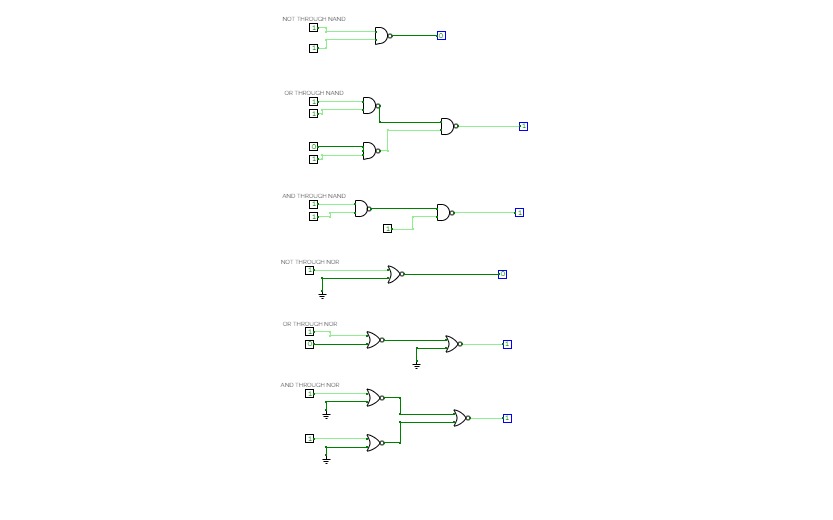

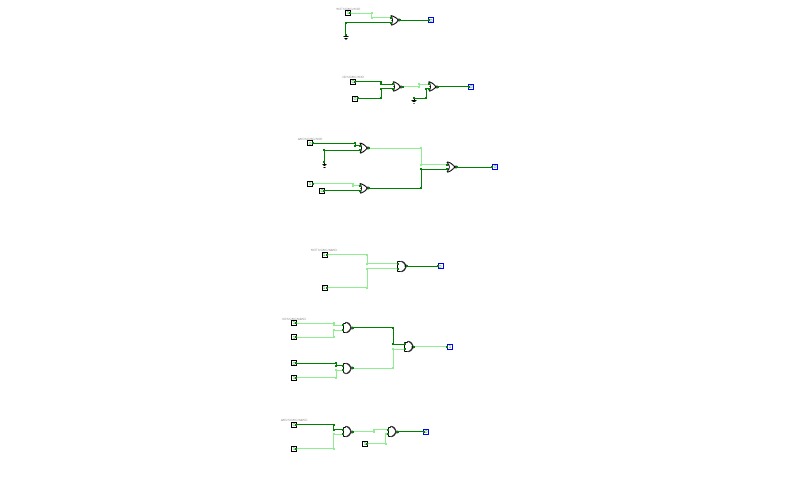

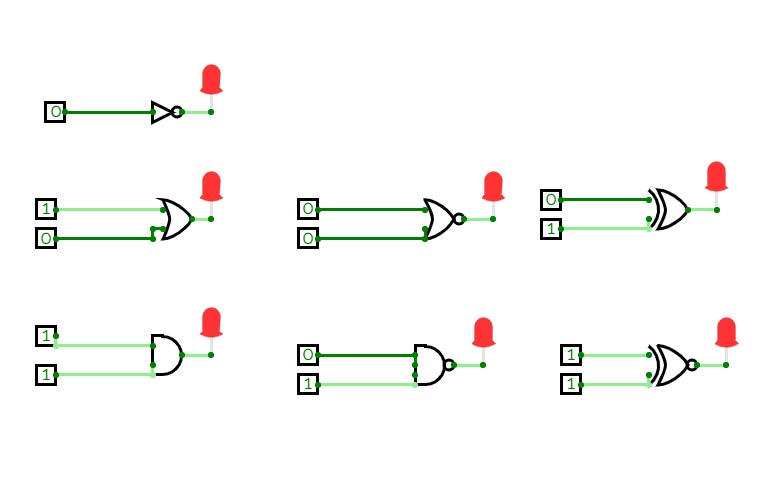

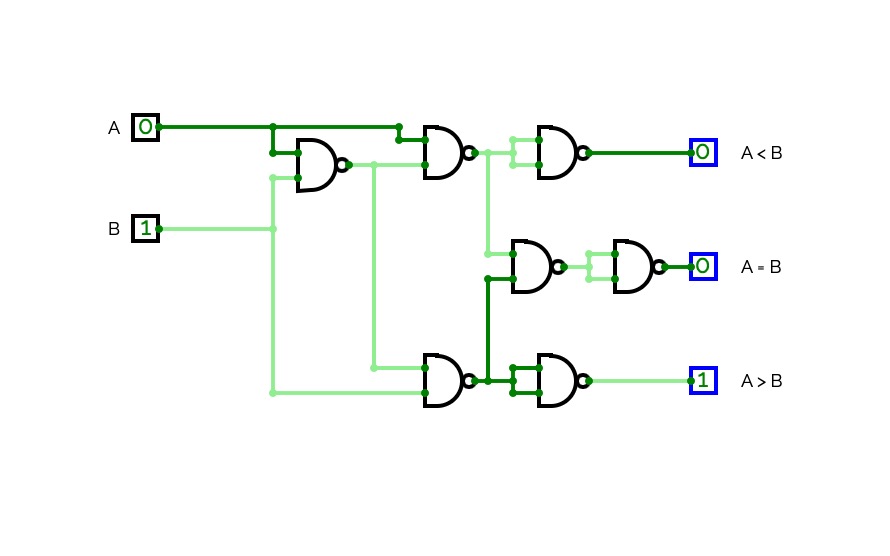

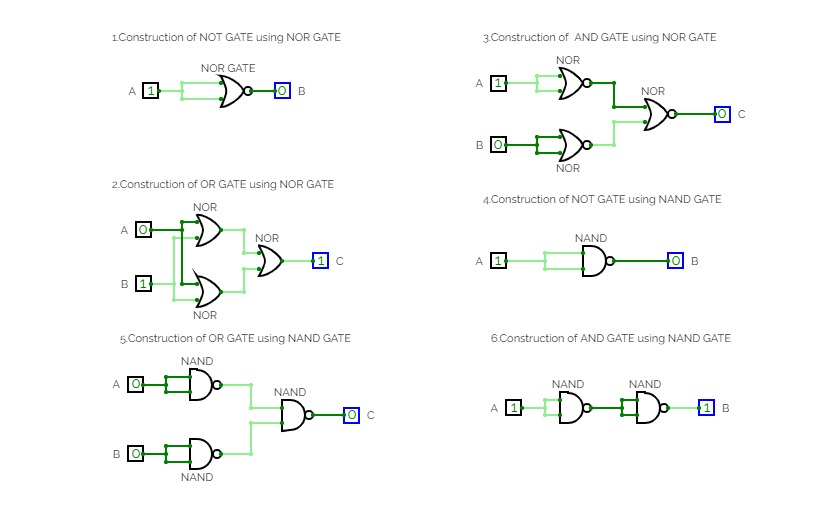

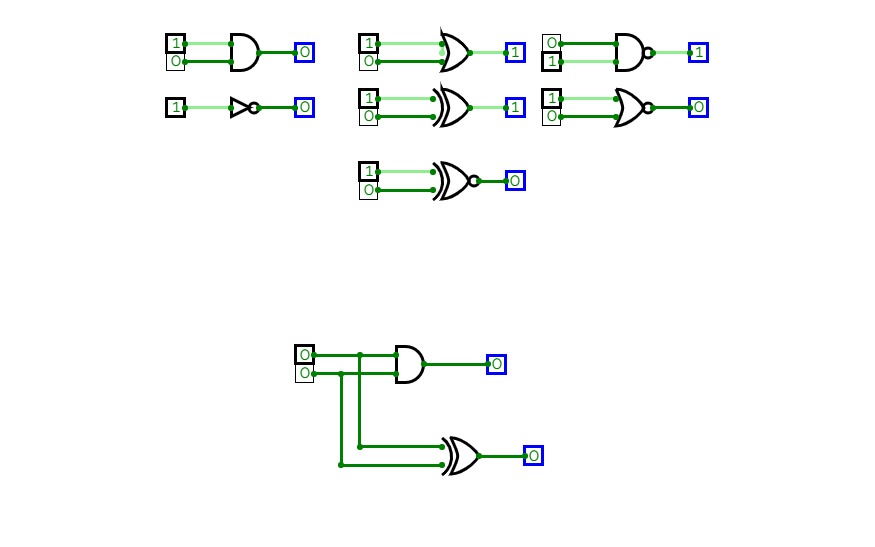

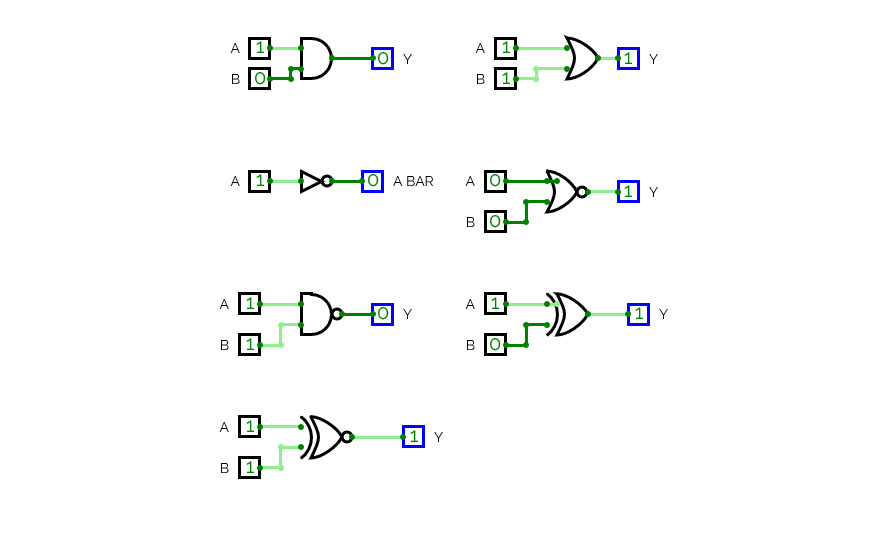

NAND and NOR as Other gates

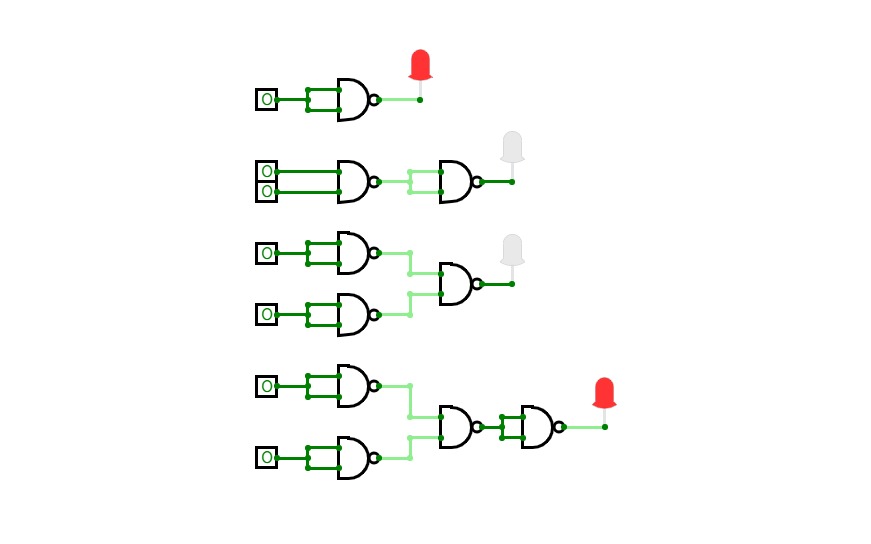

NAND and NOR as Other gatesEquivalencias a NAND de compuertas NOT, AND y OR para el trabajo Sumador de 4 bits con Compuertas Lógicas NAND.

Hecho por:

- Natalia Andrea Álvarez Hoyos

- Jean Carlo Montoya Castro

- Sebastián Valencia Zapata

- Alejandra Uribe Sierra

Estudiantes de la Universidad Nacional de Colombia. Semestre 2022-1. Asignatura Arquitectura de Computadores.

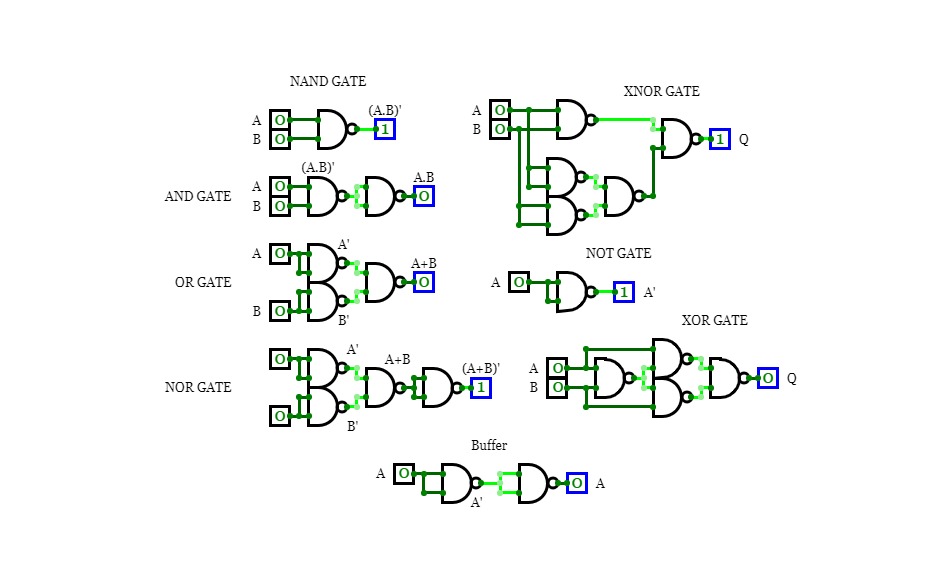

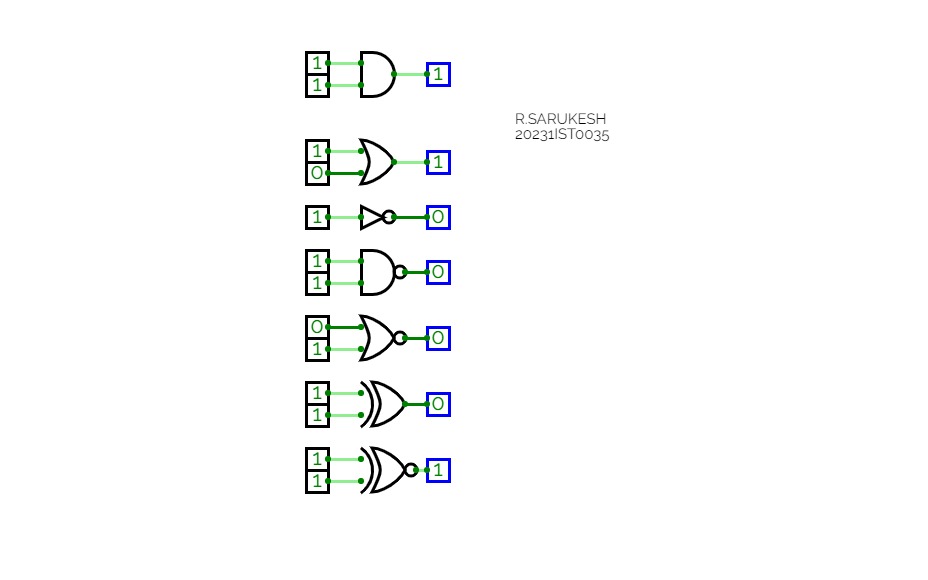

NAND GATE-Universal Gate

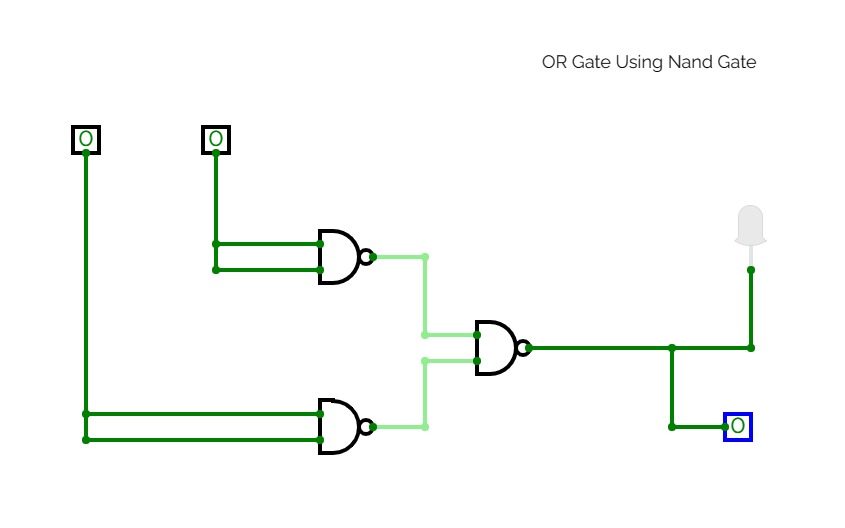

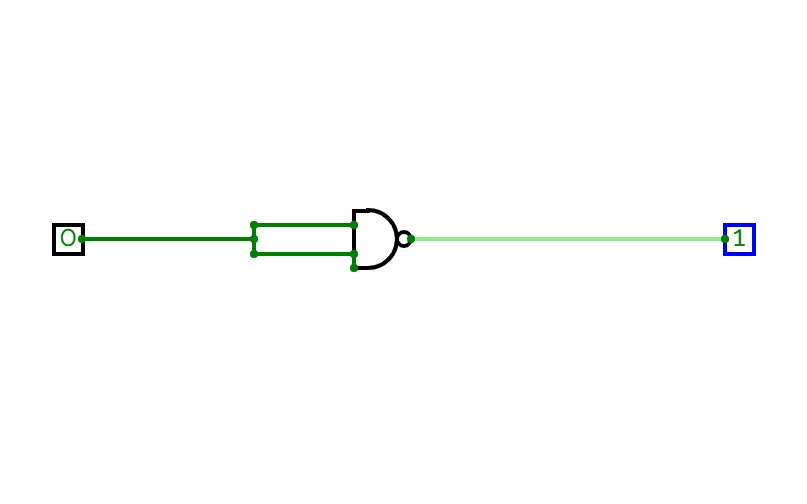

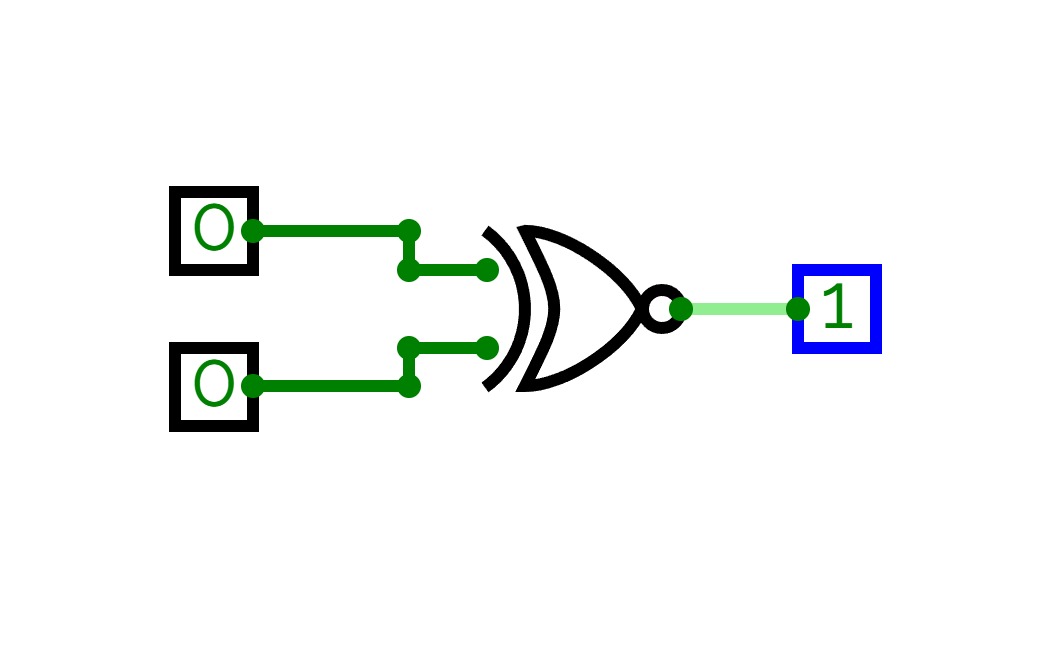

NAND GATE-Universal GateOR Gate Using NAND

OR Gate Using NANDJK FlipFlop NAND Gates (Rising edge)

JK FlipFlop NAND Gates (Rising edge)This demonstrate the JK-Flipflop.

J 0, K 0 => do nothing

J 1, K 0 => Set (Q = 1, Q' = 0)

J 0, K 1 => Reset (Q = 0, Q' = 1)

J 1, K 1 => Toggle Q and Q'

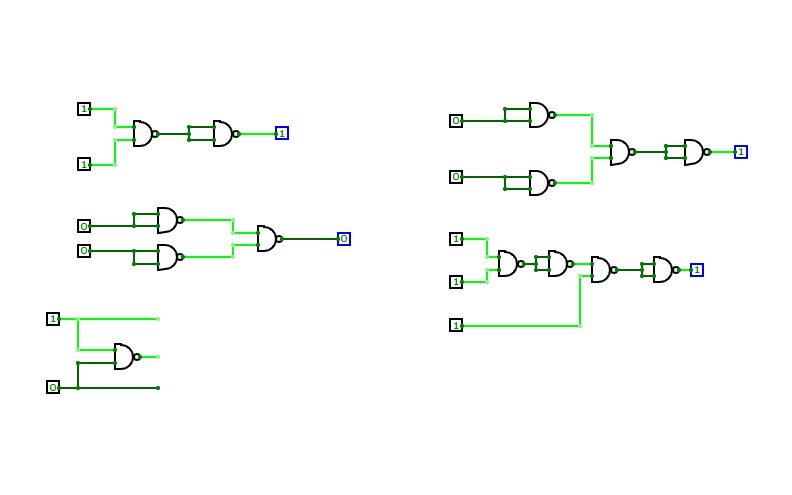

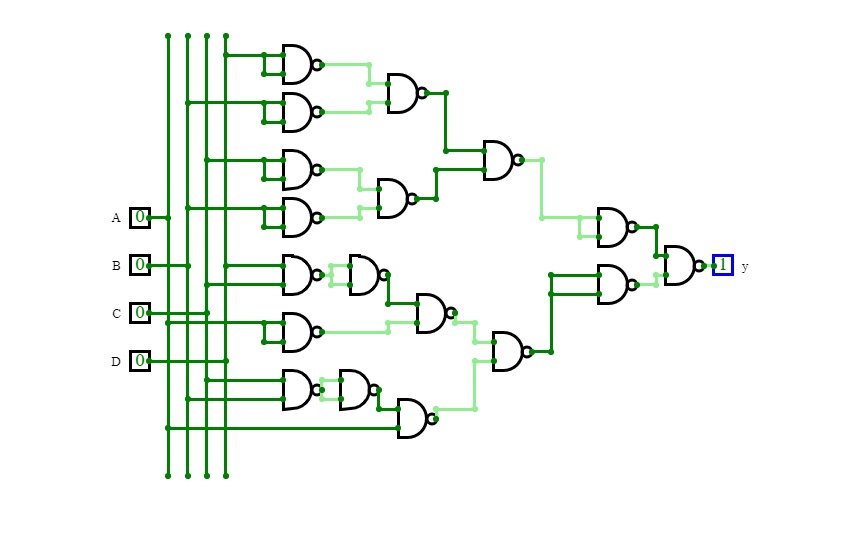

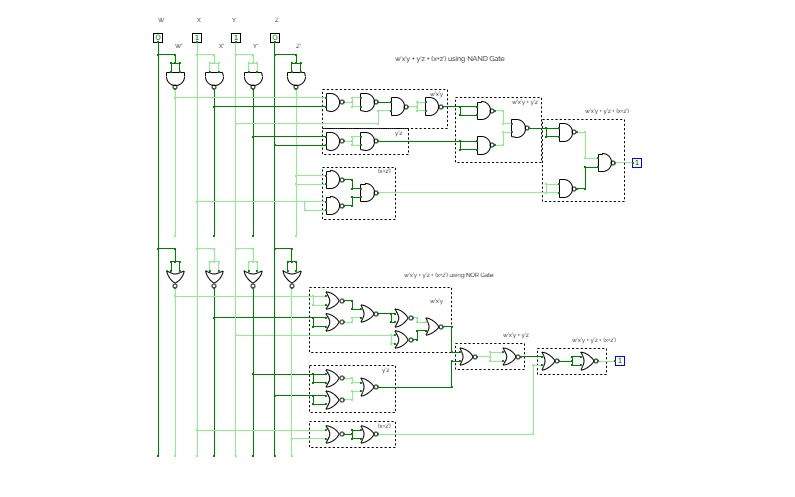

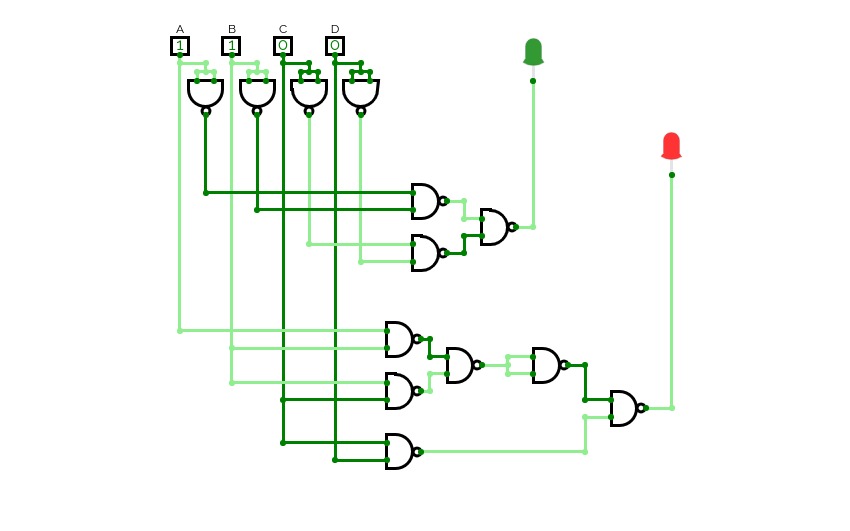

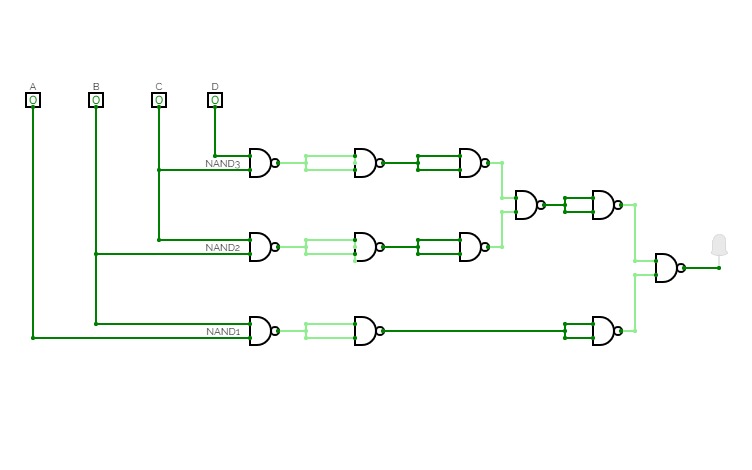

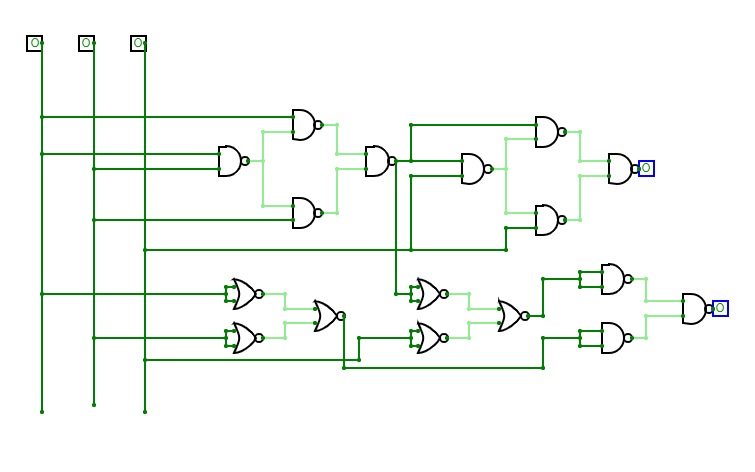

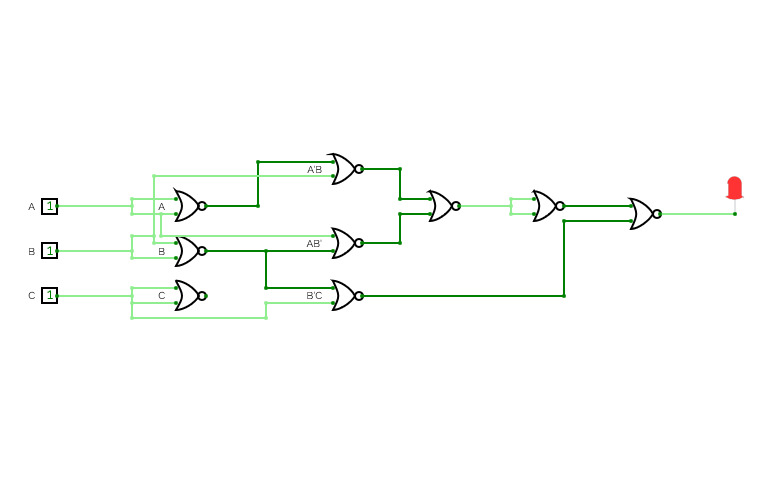

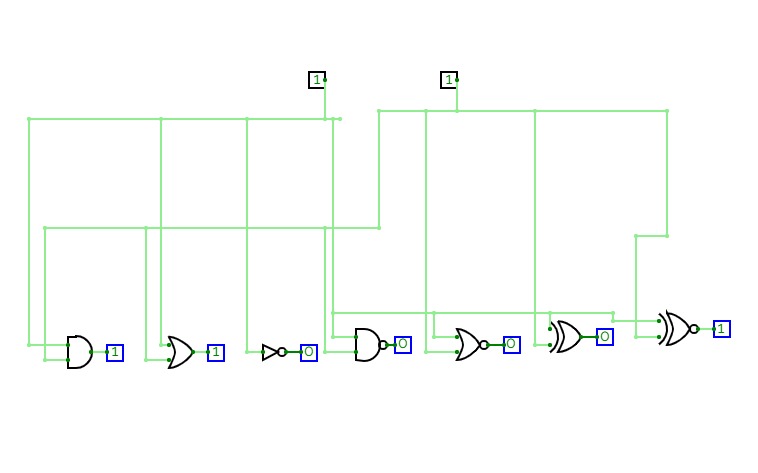

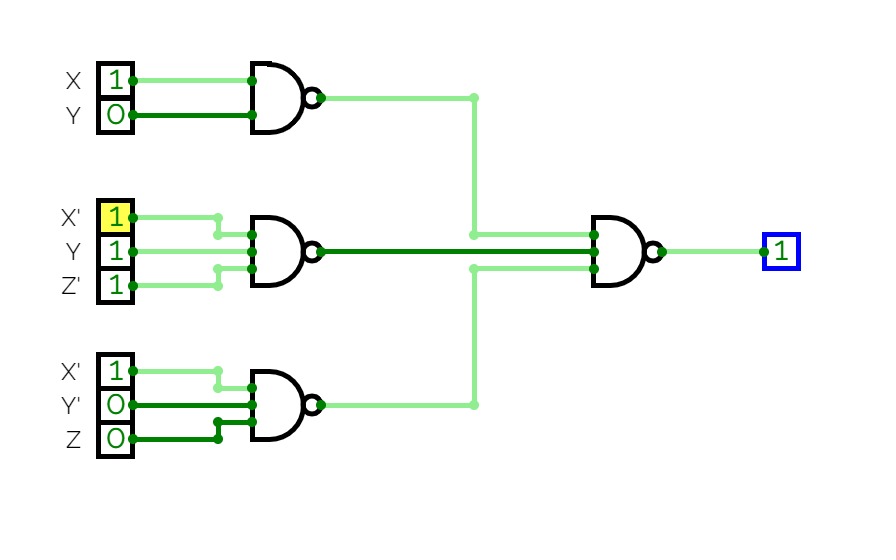

w’x’y + y’z + (x+z’)

w’x’y + y’z + (x+z’)Simulación de Circuitos Digitales

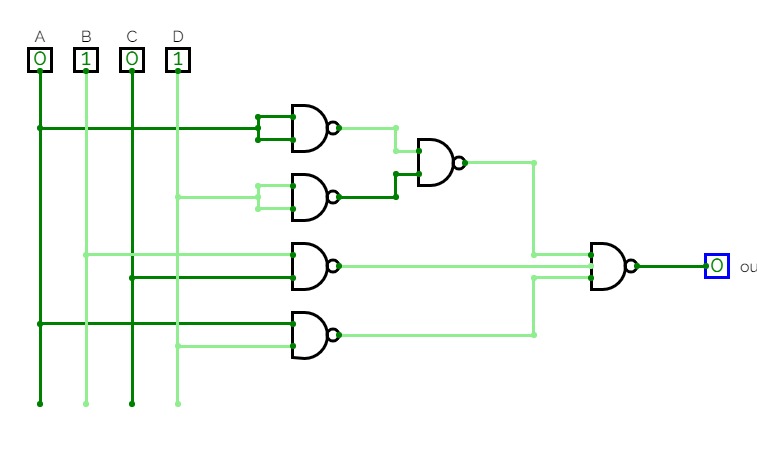

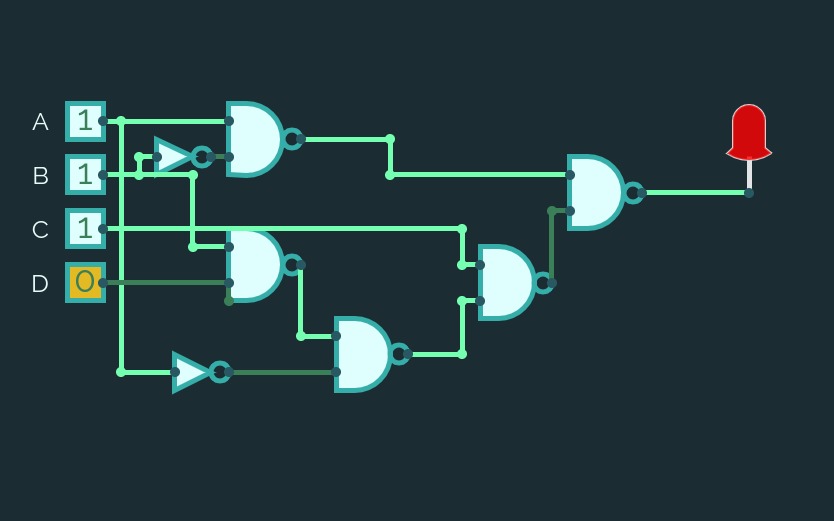

Simulación de Circuitos DigitalesObtener la expresión de F que permita implementarla con el menor número de puertas posible, de cualquier tipo, y representar el circuito equivalente.

F(A, B, C, D) = AB + BC + CD

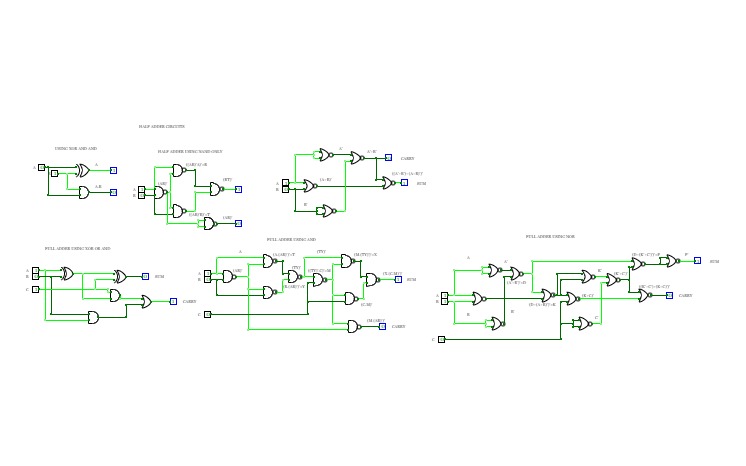

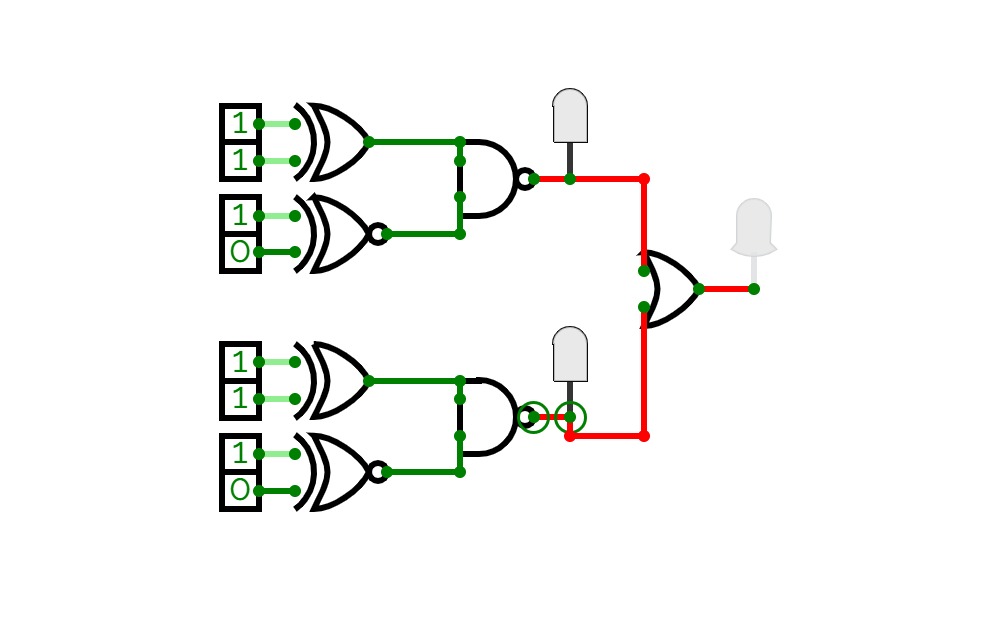

Full Adder using BOTH NAND and NOR gates.

Full Adder using BOTH NAND and NOR gates.Full Adder using BOTH NAND and NOR gates.

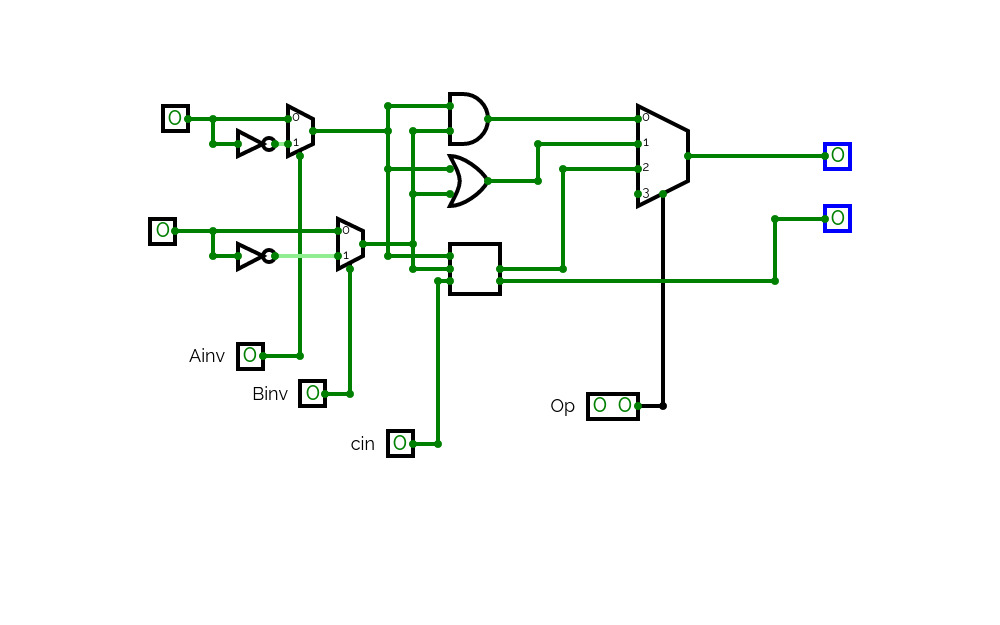

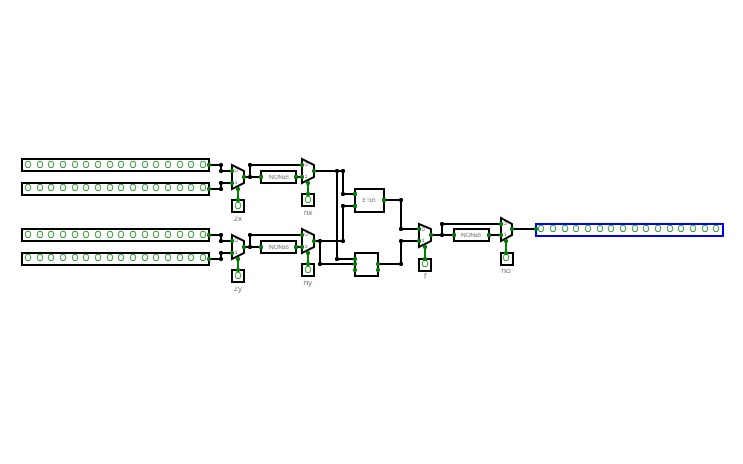

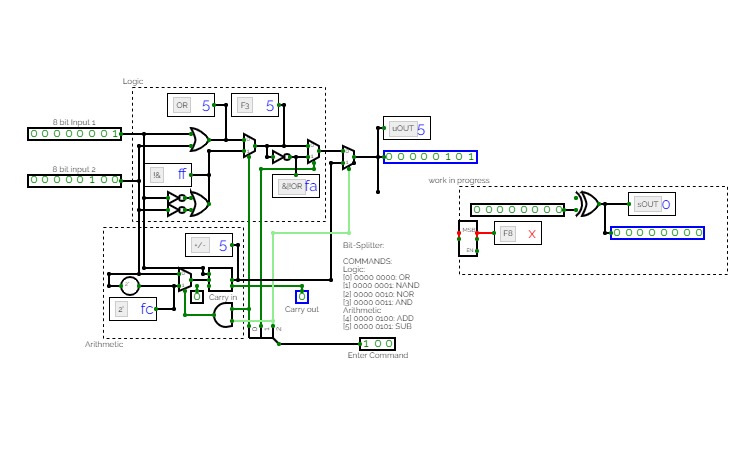

8-bit Arithmetic Logic Unit (2

8-bit Arithmetic Logic Unit (2A simple 8-bit arithmetic logical unit.

The following commands are implemented:

Logic Operations:

[0] 000: OR

[1] 001: NAND

[2] 010:NOR

[3] 011: AND

Arithmetic Operations:

[4] 100: ADD

[5] 101: SUB

The two's complement for subtraction is implemented with a NOT Gate and an adder (which simply adds 1 to the negated input).

8-bit Arithmetic Logic Unit (ALU)

8-bit Arithmetic Logic Unit (ALU)A simple 8-bit arithmetic logical unit.

The following commands are implemented:

Logic Operations:

[0] 000: OR

[1] 001: NAND

[2] 010:NOR

[3] 011: AND

Arithmetic Operations:

[4] 100: ADD

[5] 101: SUB

The two's complement for subtraction uses the built in component.

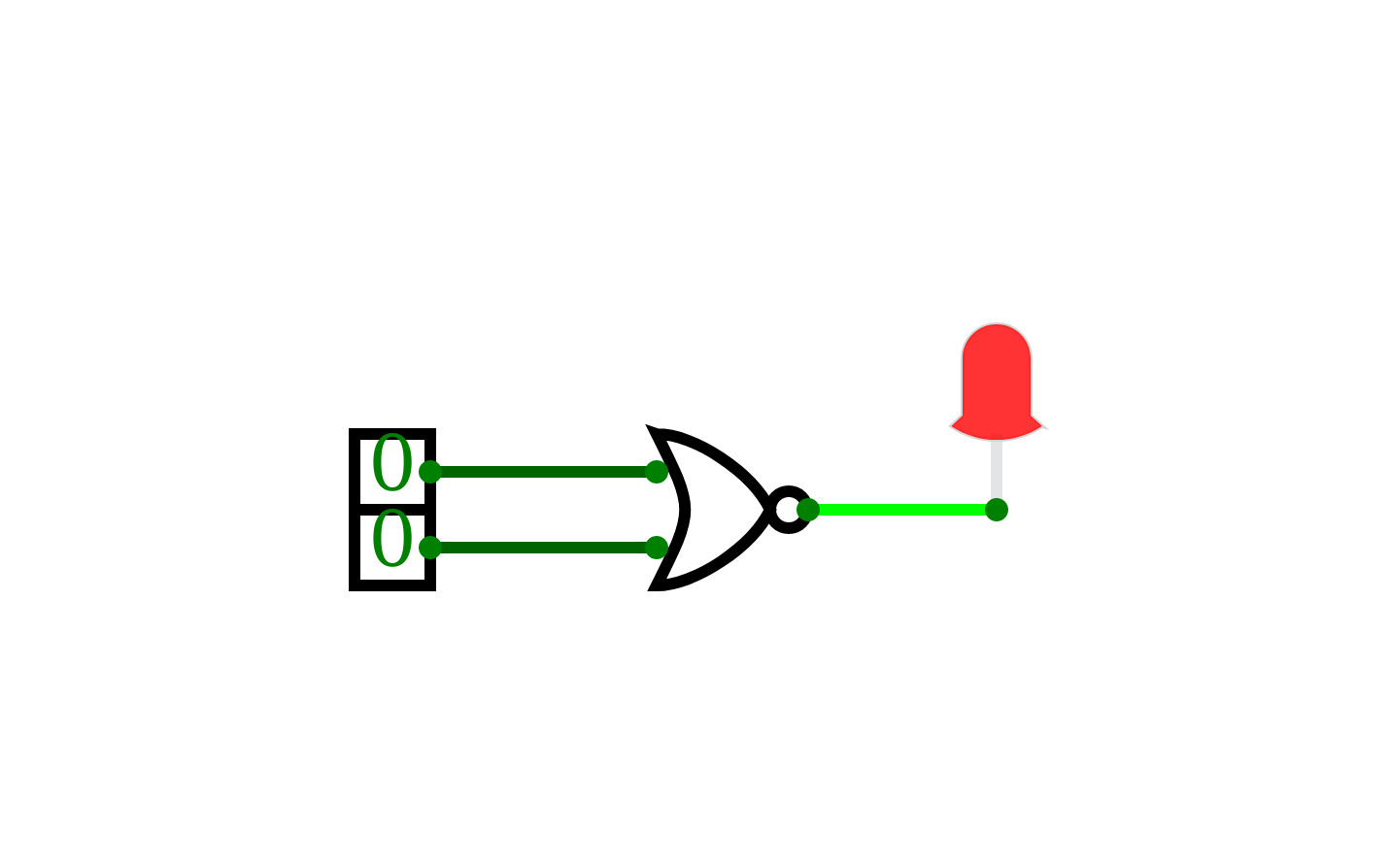

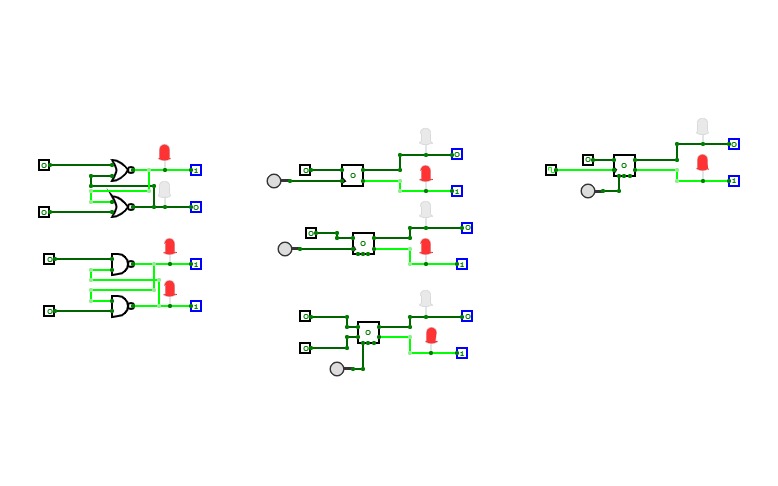

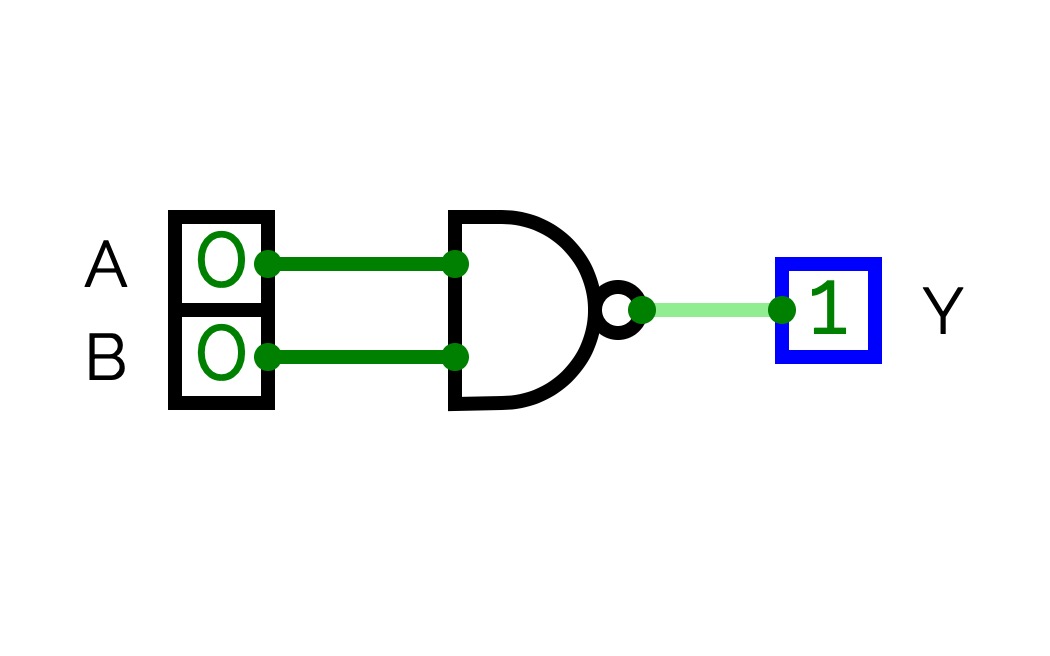

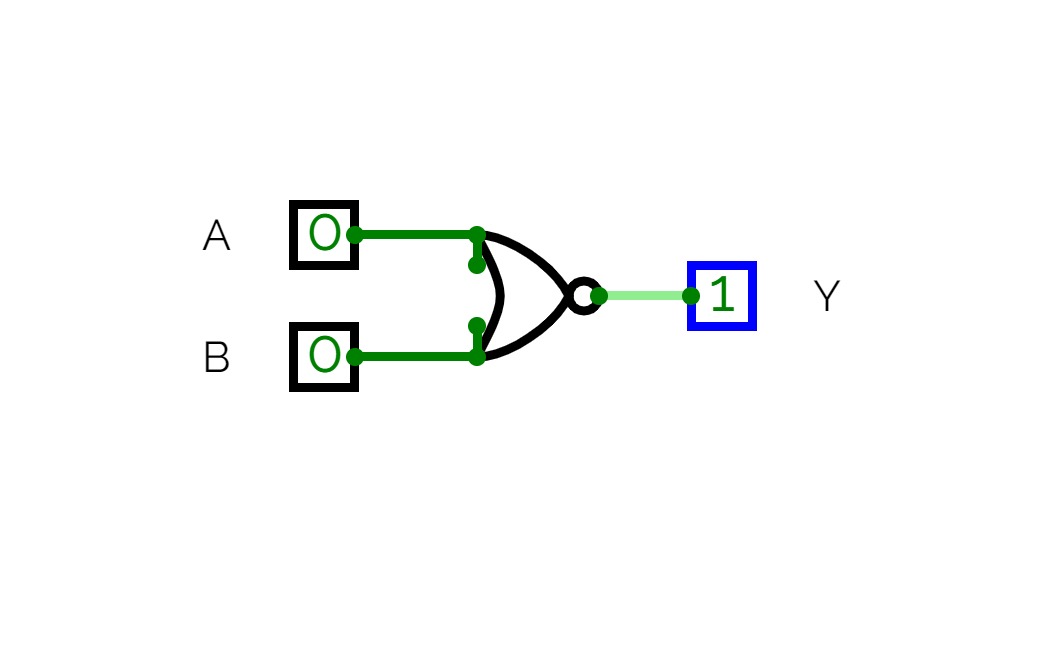

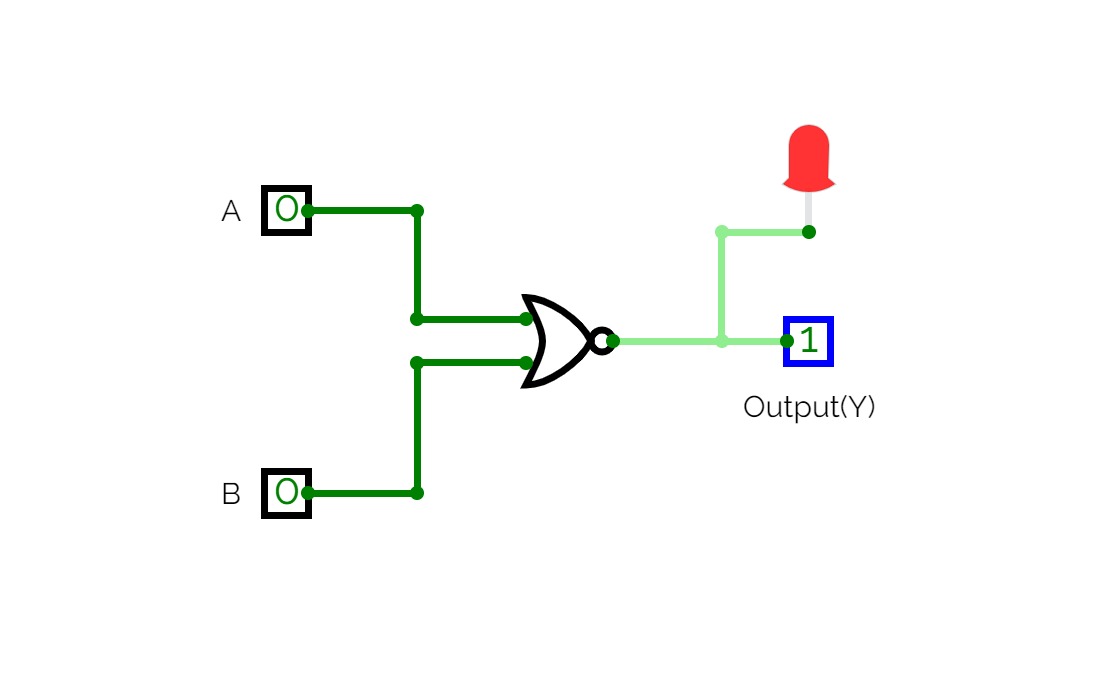

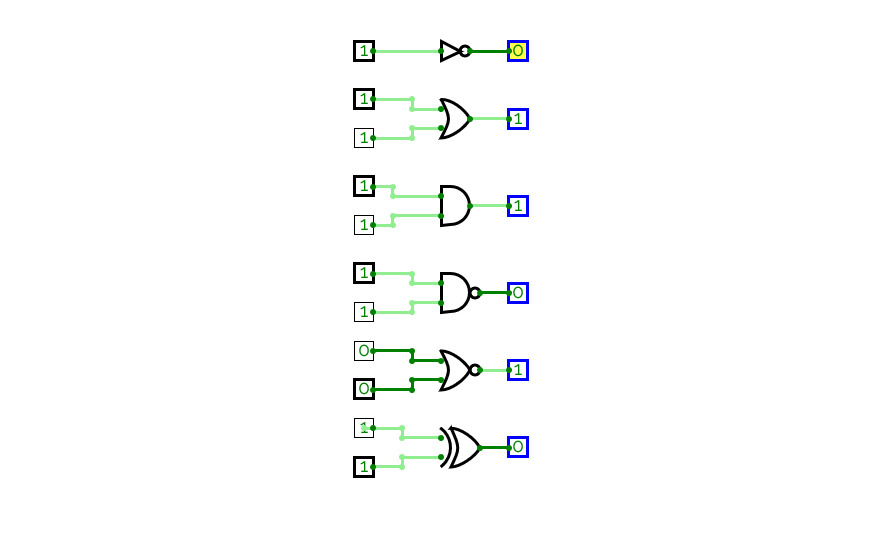

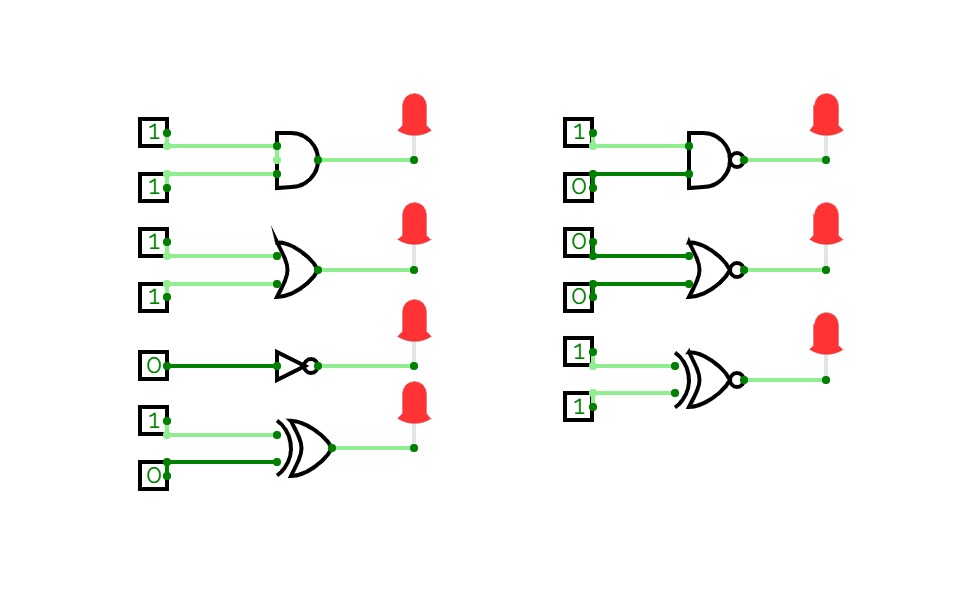

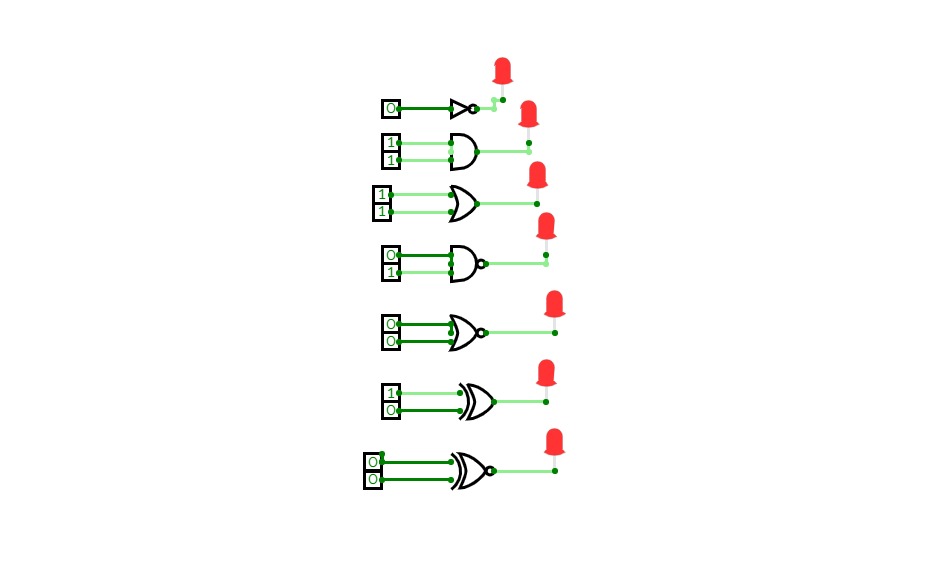

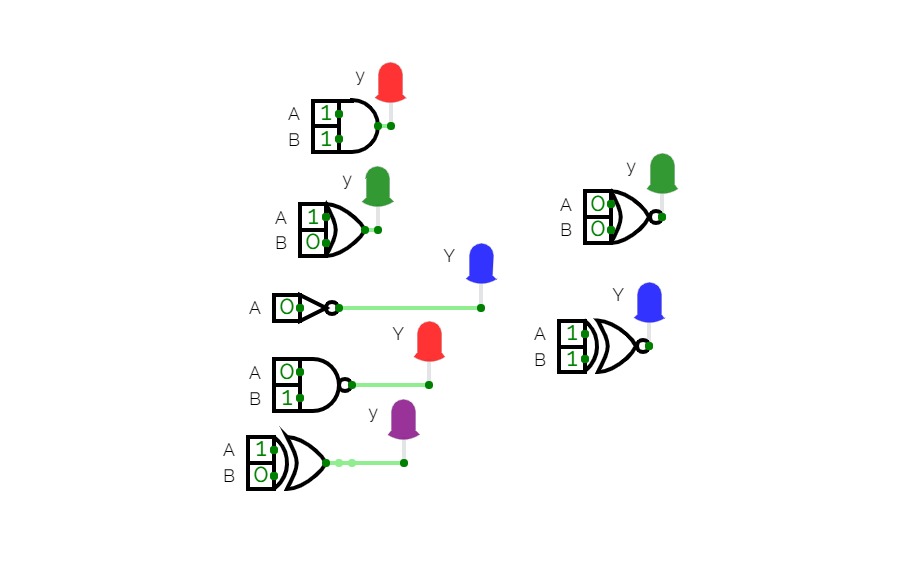

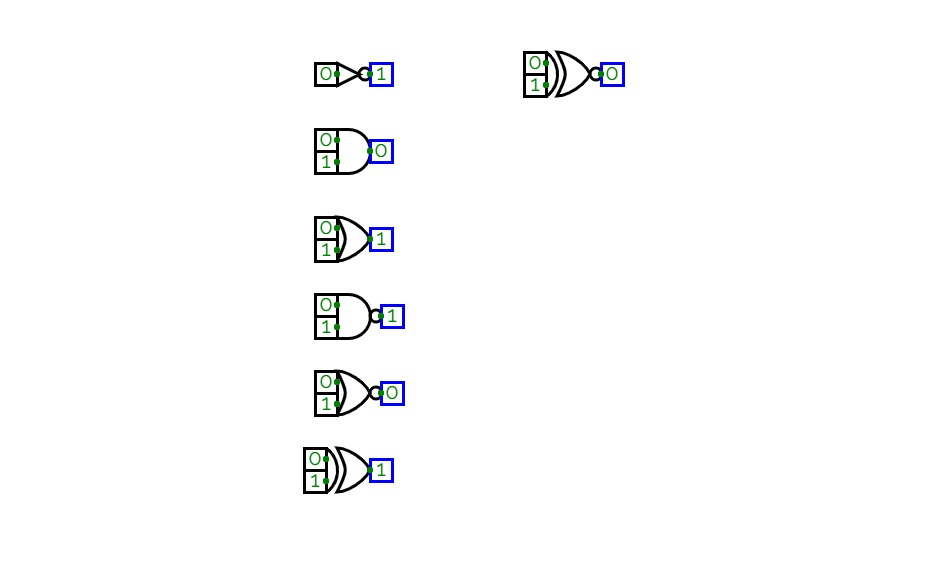

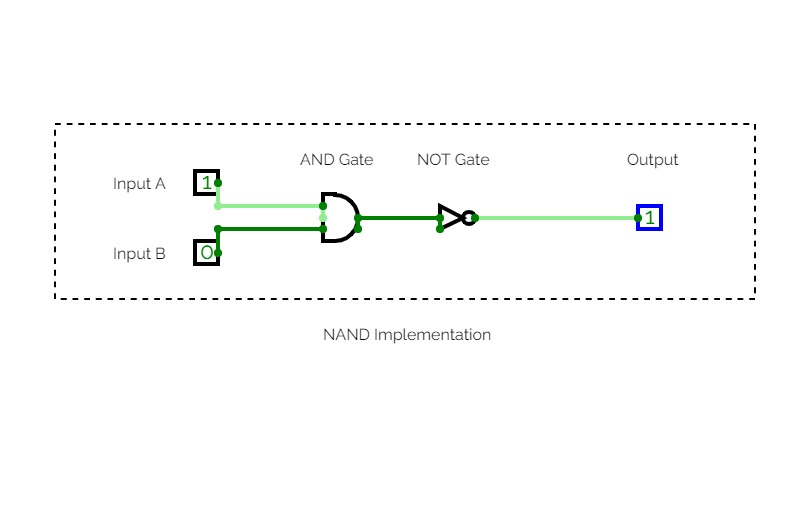

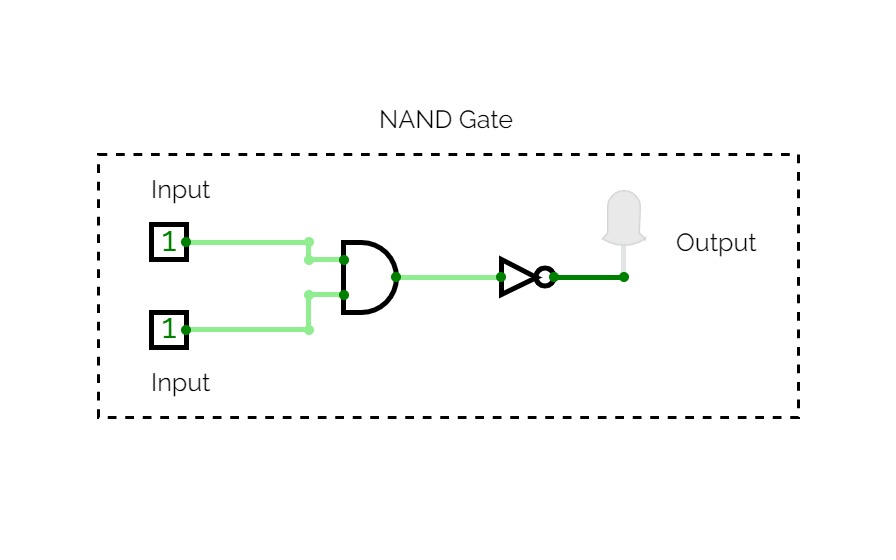

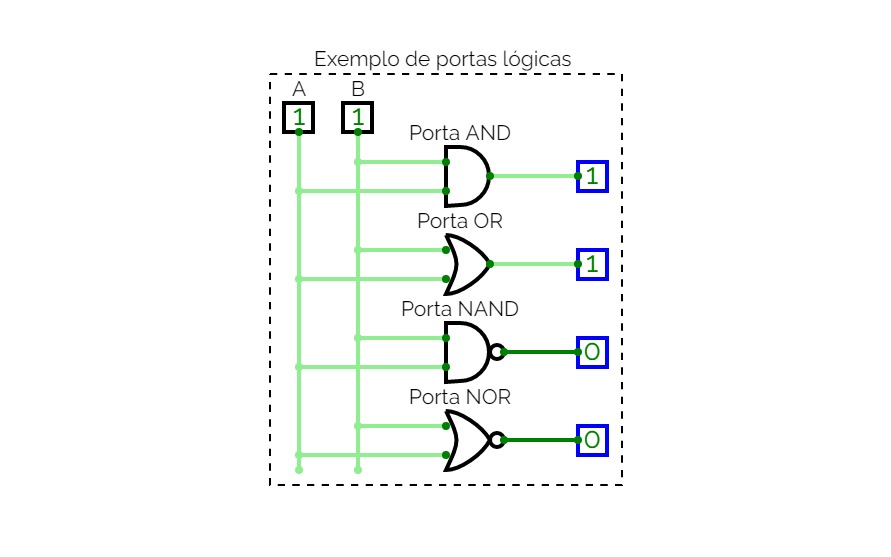

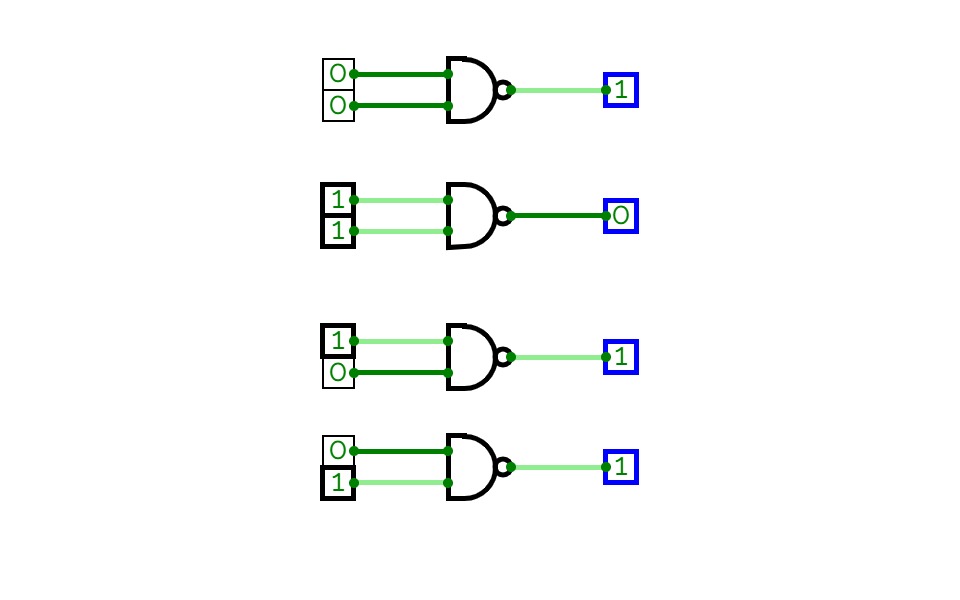

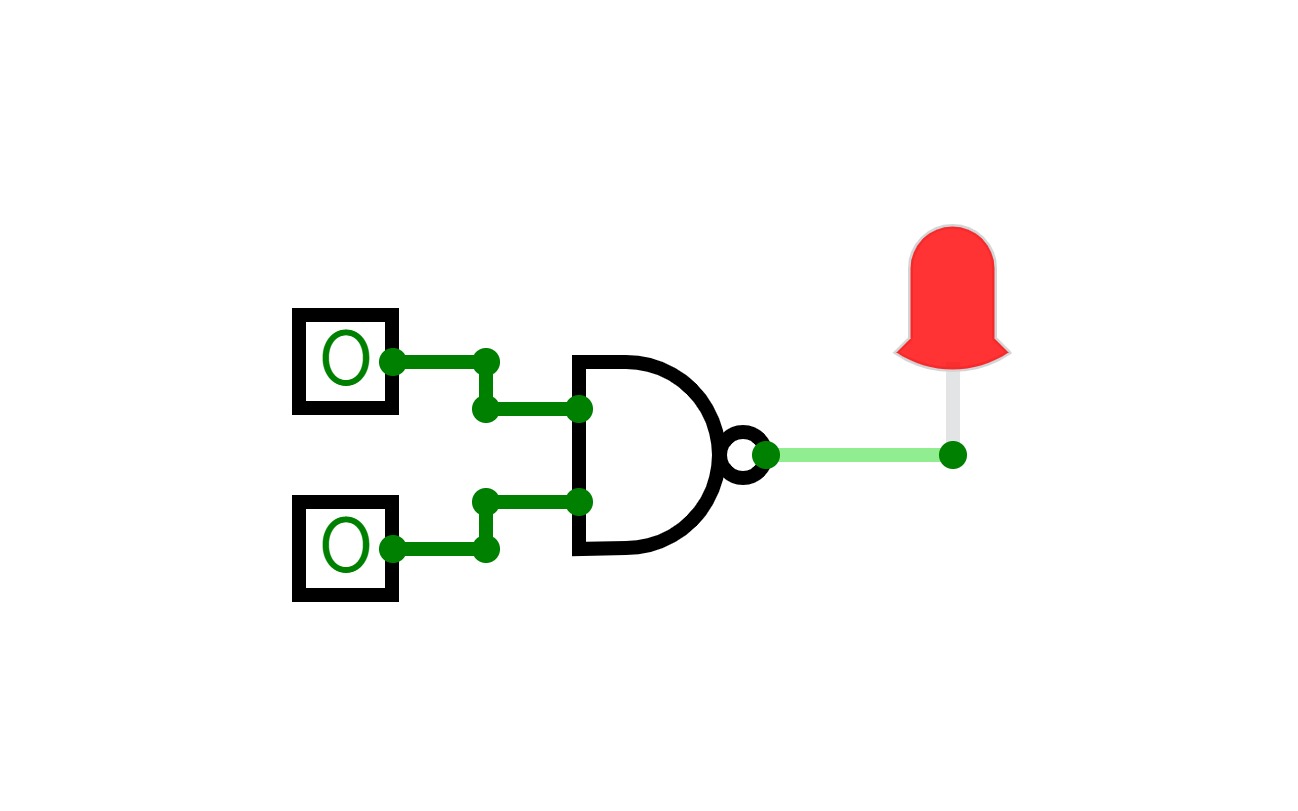

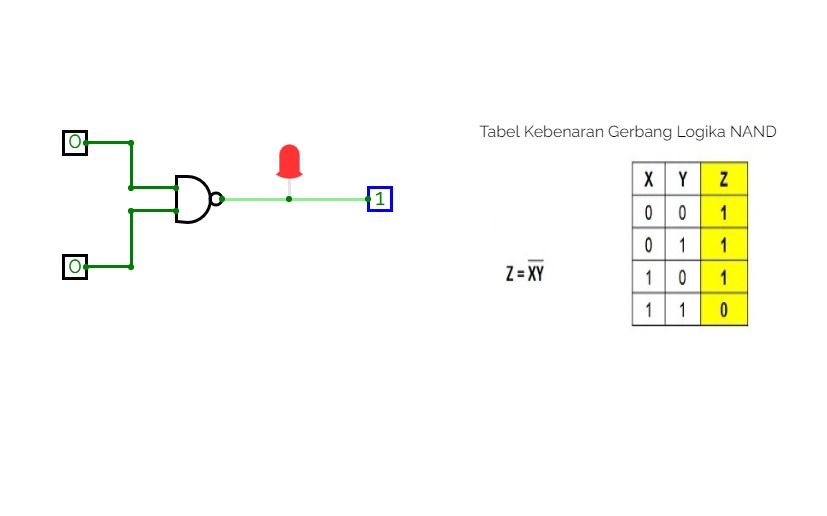

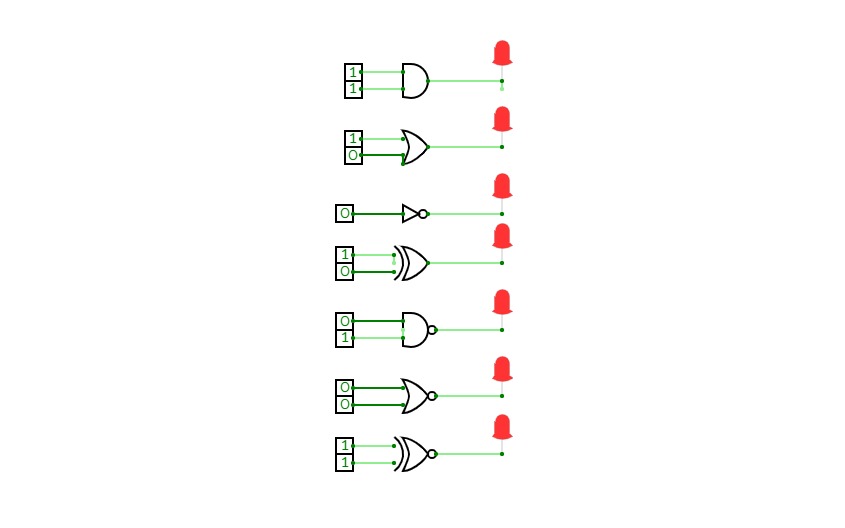

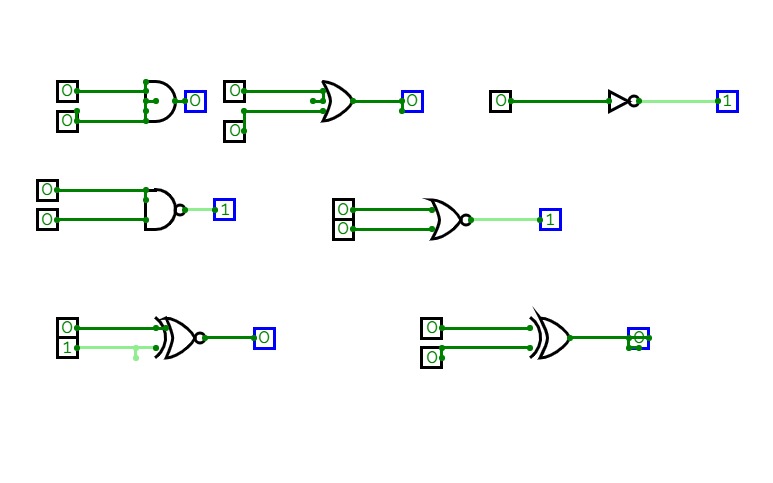

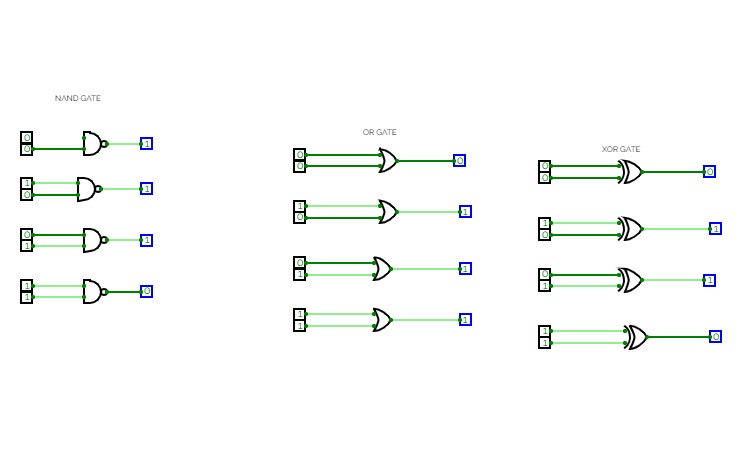

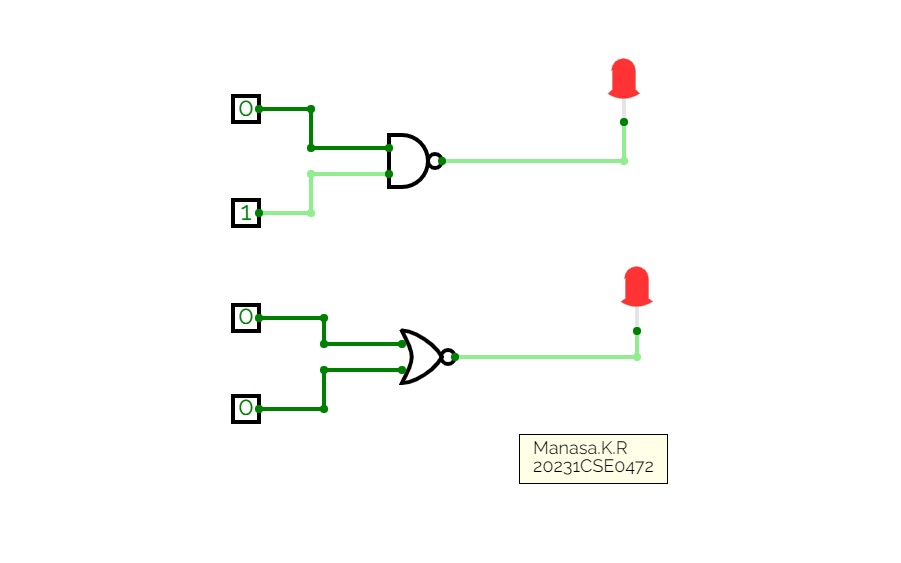

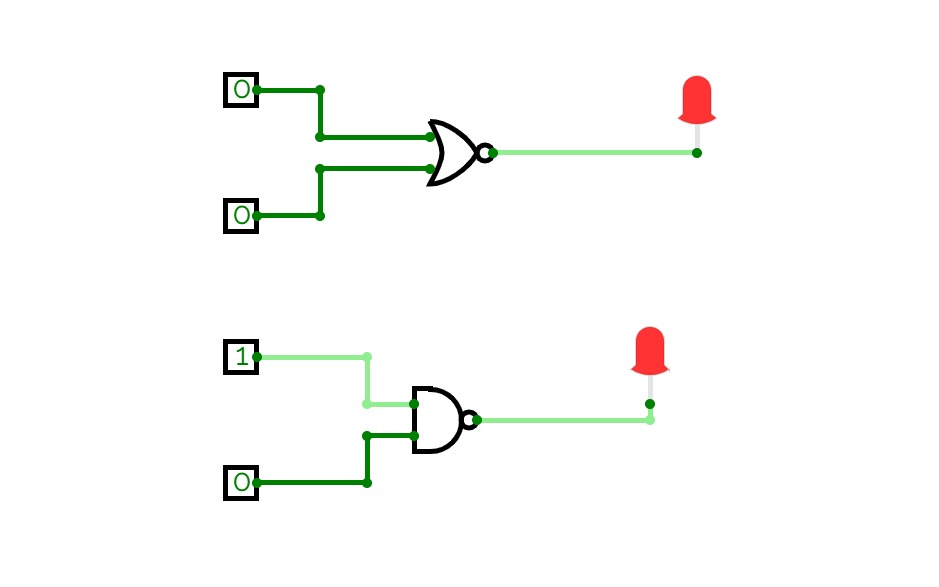

Gerbang Logika NAND

Gerbang Logika NANDGerbang Logika NAND ini adalah gabungan dari gerbang AND dan gerbang NOT. Karena itu output yang dihasilkan dari gerbang NAND ini adalah kebalikan dari gerbang AND.

Berikut adalah simulasi gerbang logika dasar NAND :

Basic-7Display-F-E

Basic-7Display-F-EProjeto de exemplo para ligar o segmento f & e do display de 7 segmentos utilizando portas lógicas.

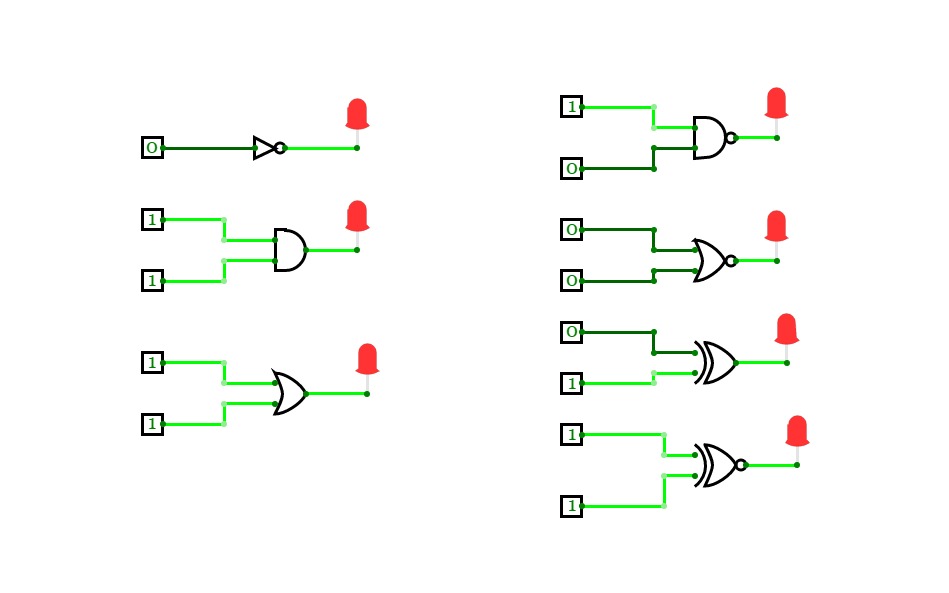

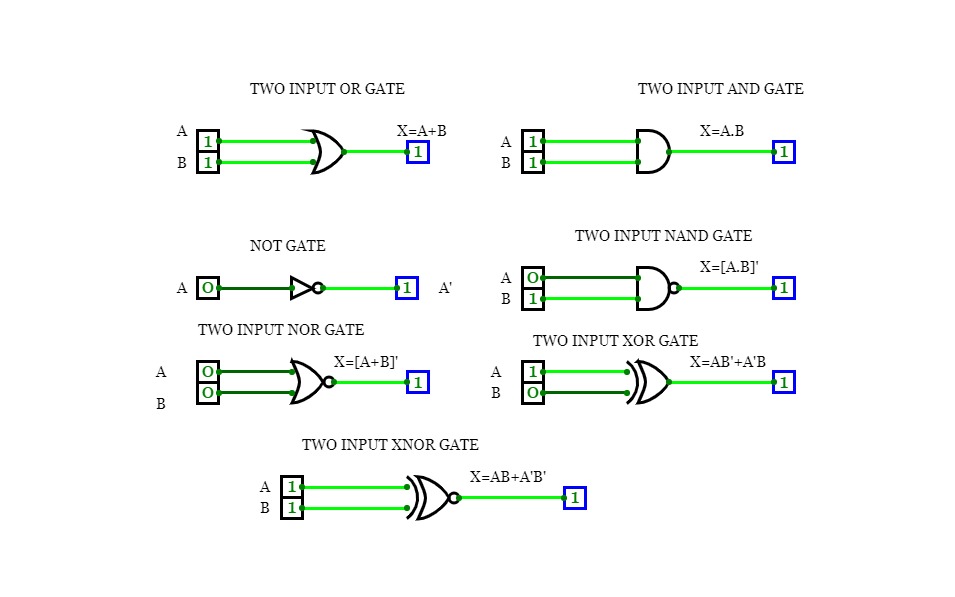

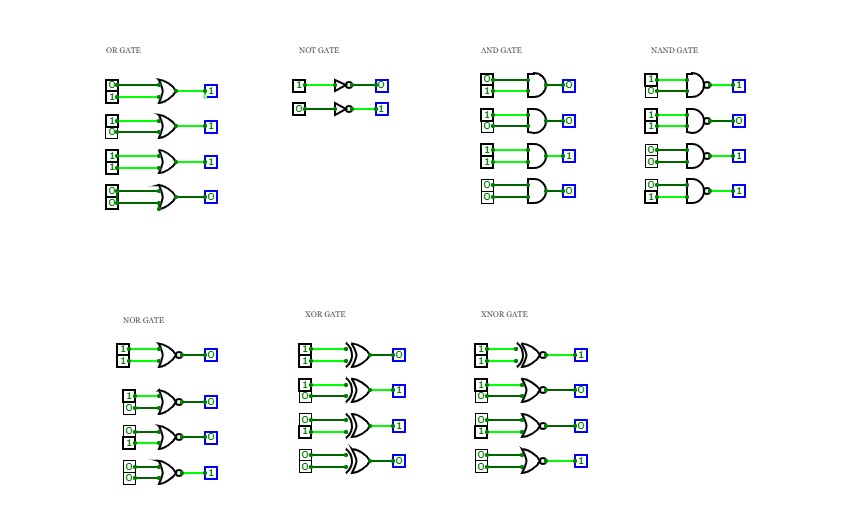

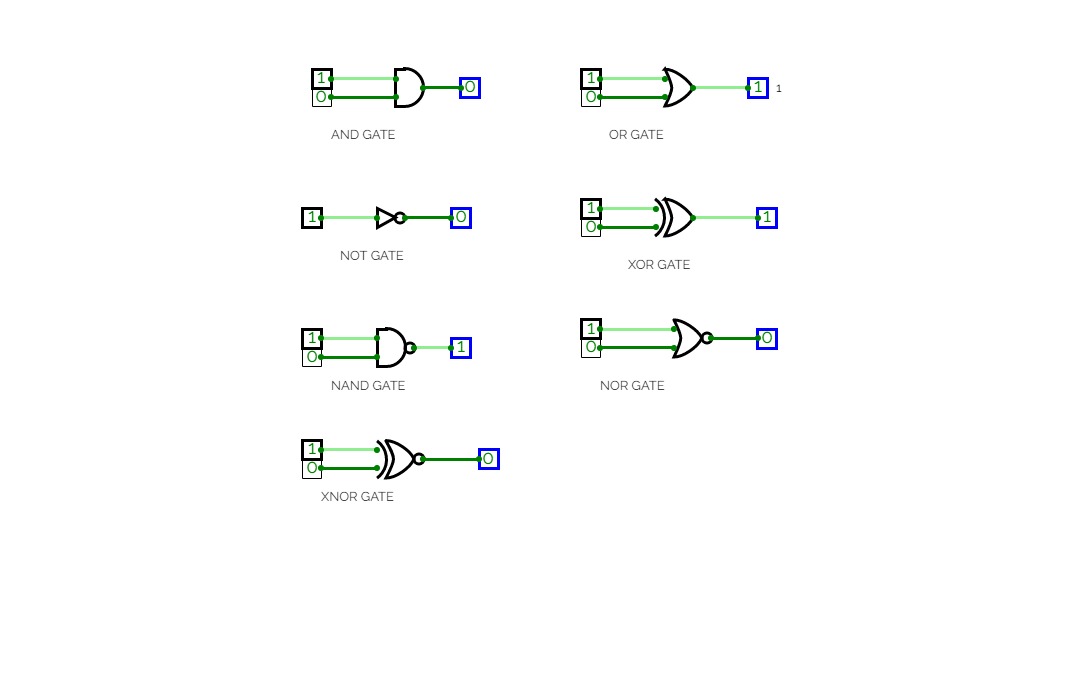

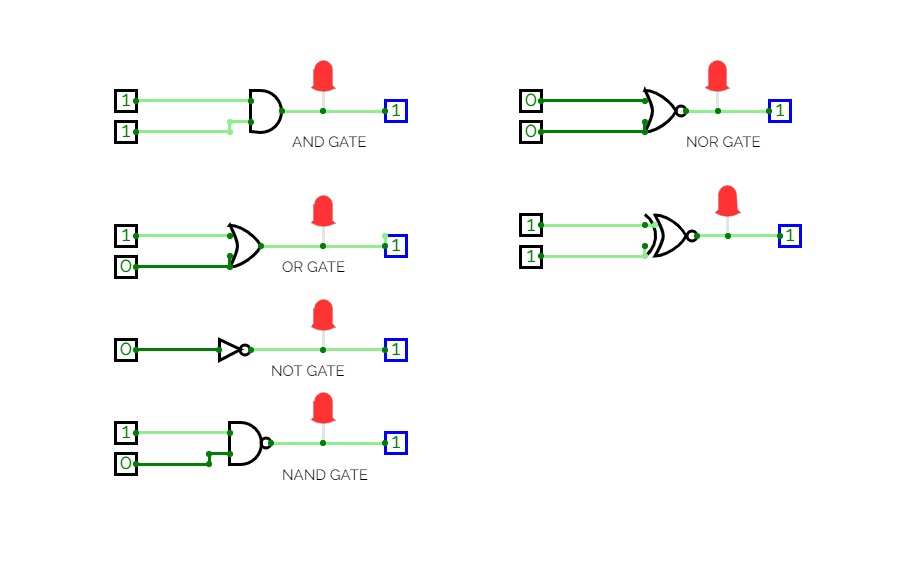

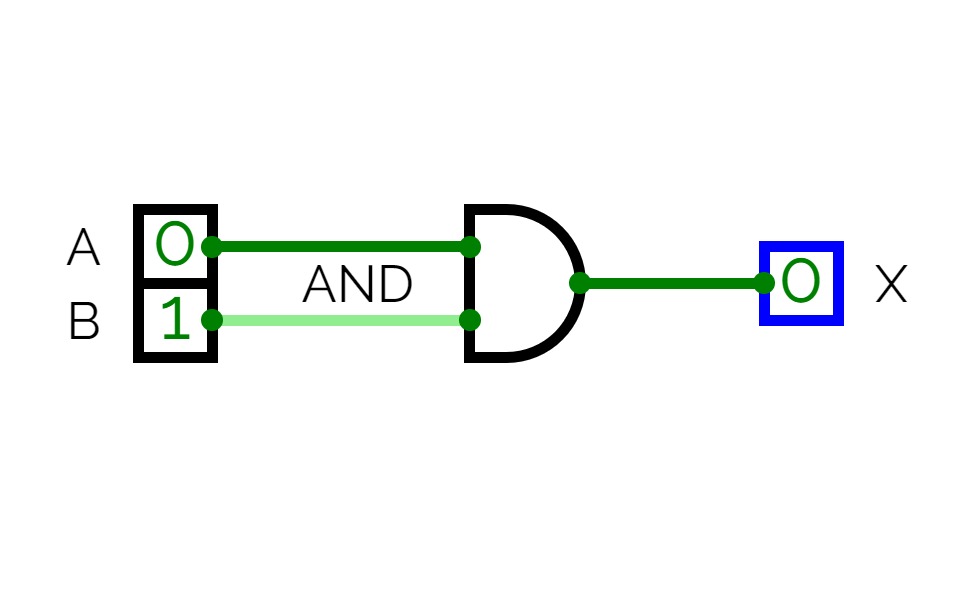

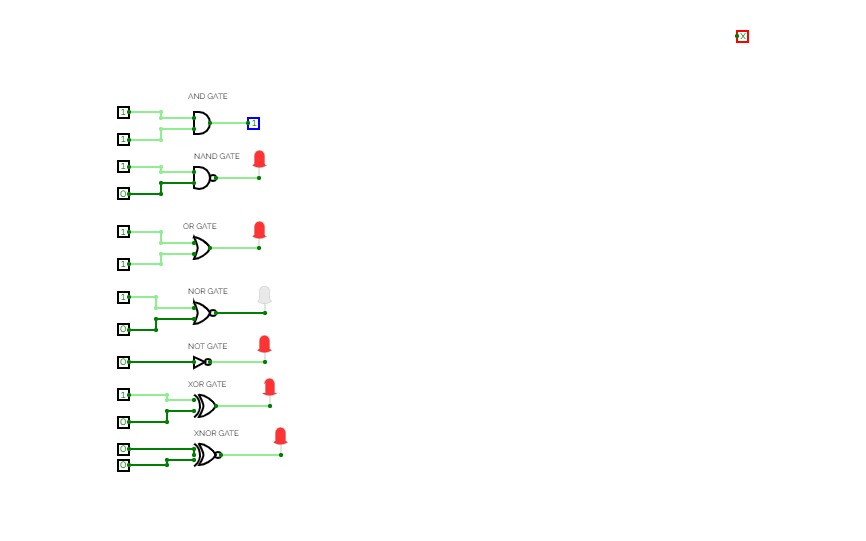

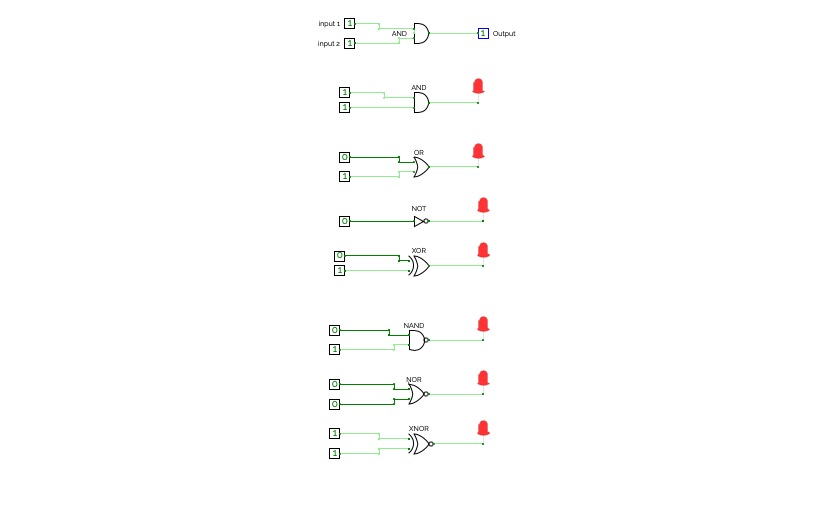

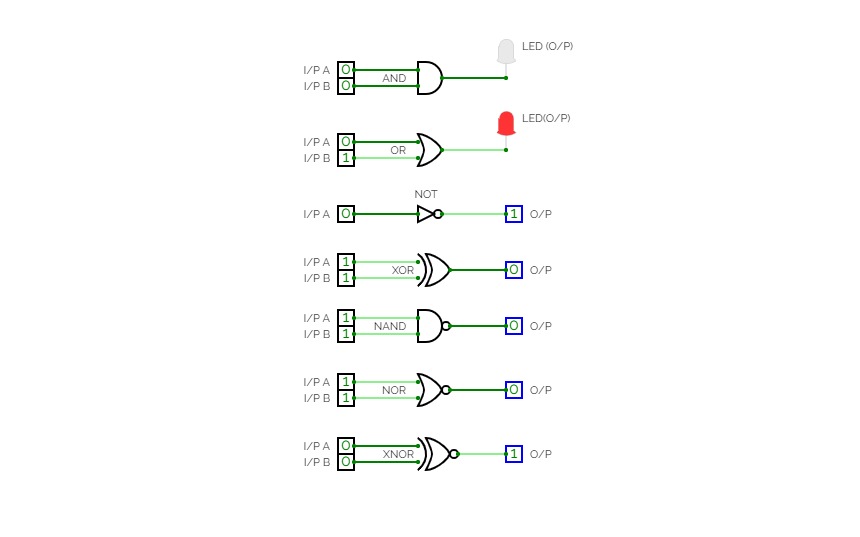

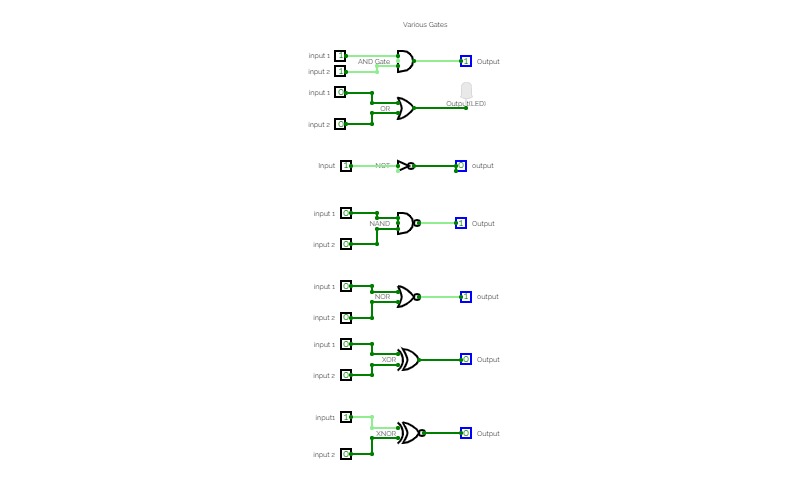

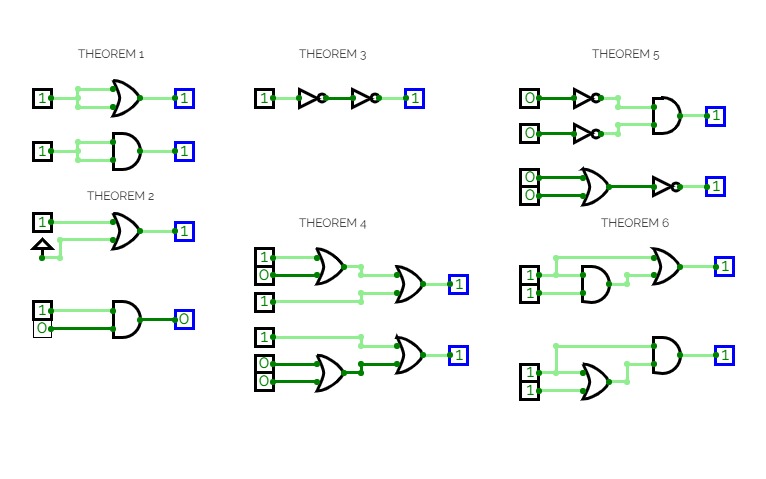

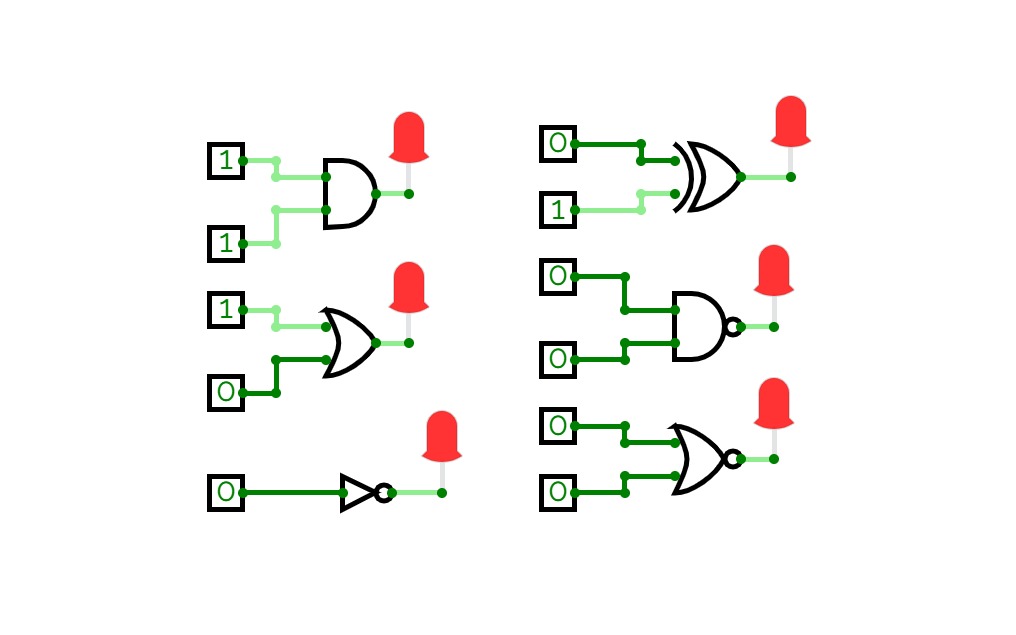

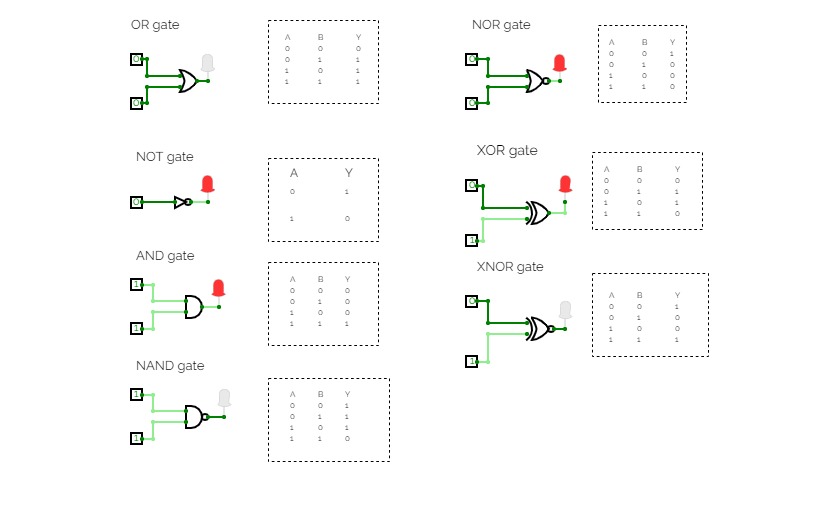

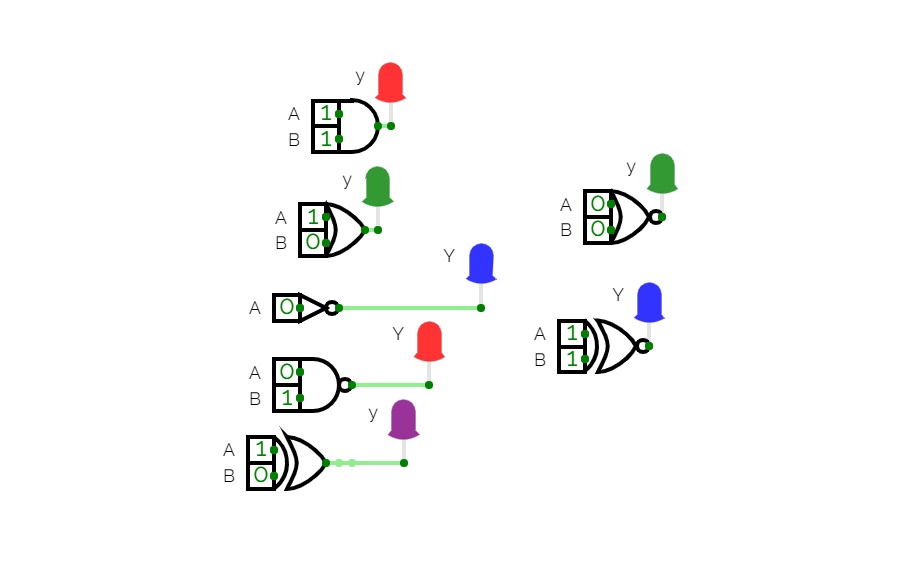

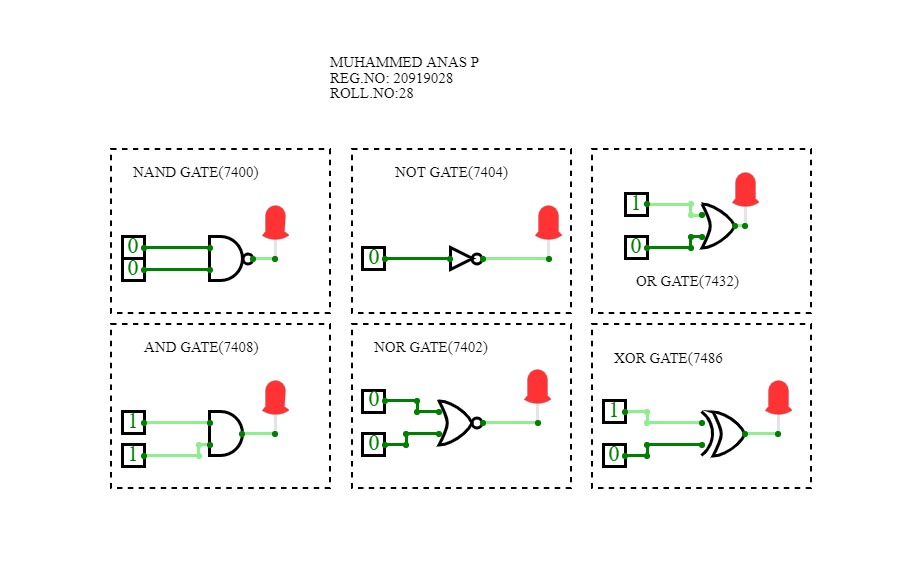

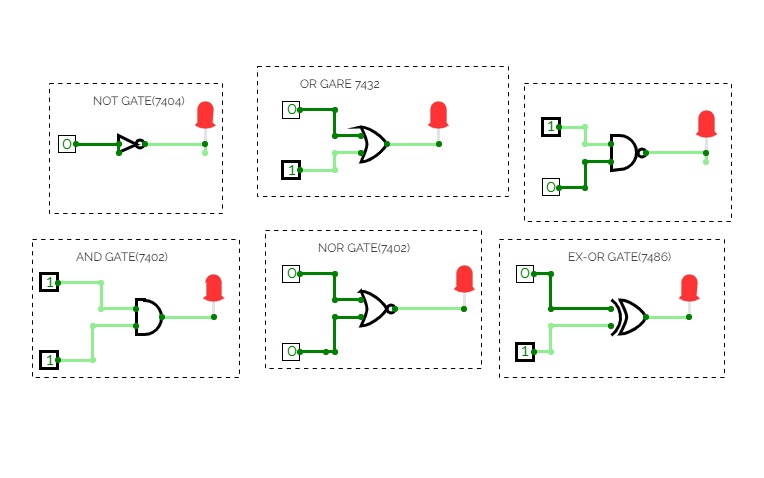

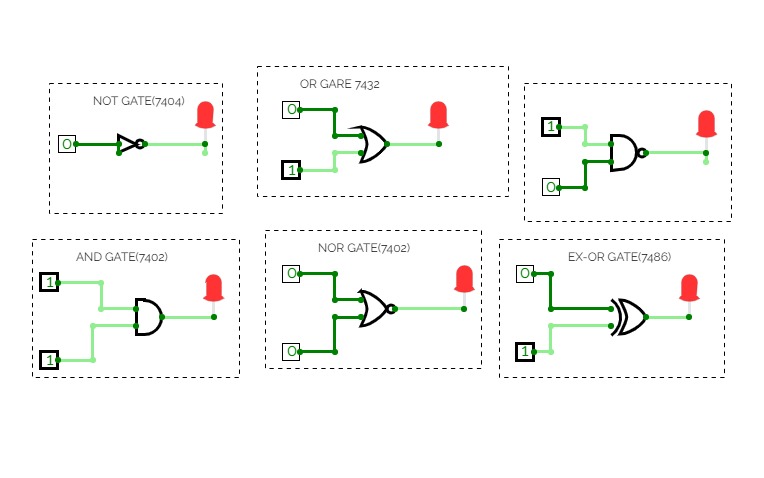

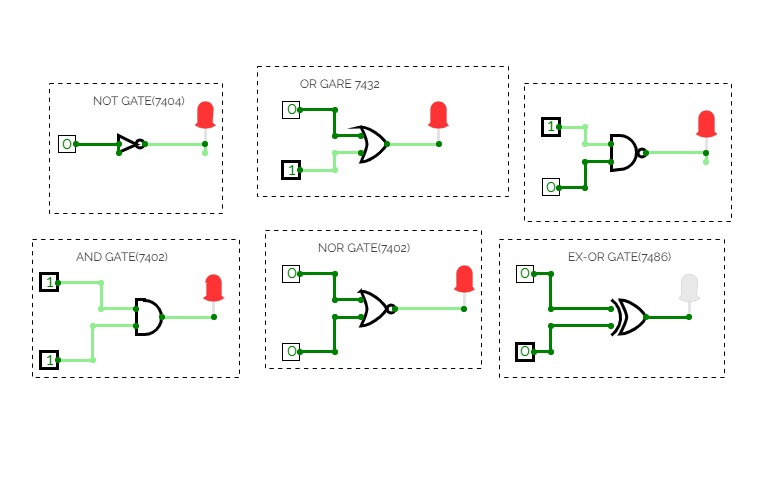

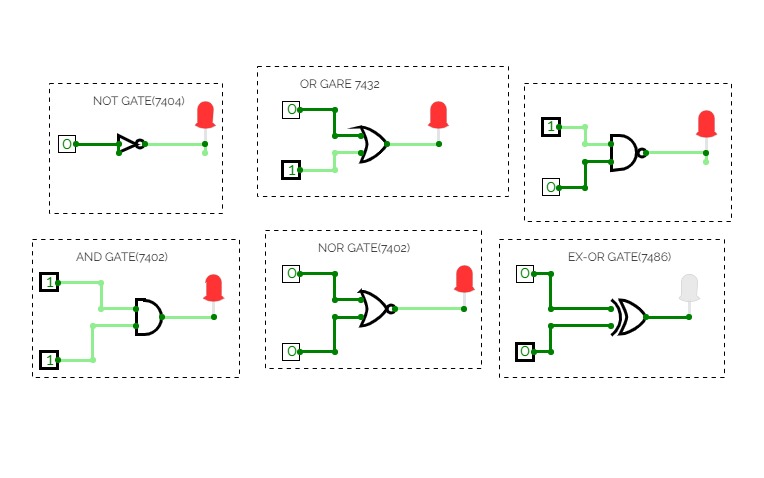

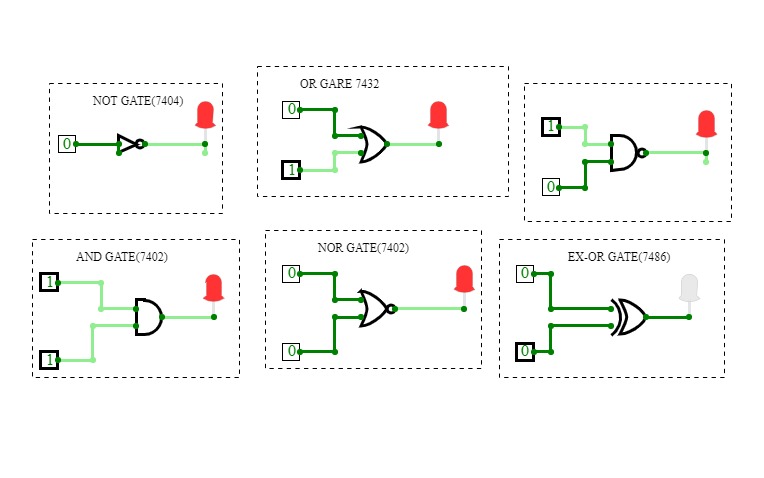

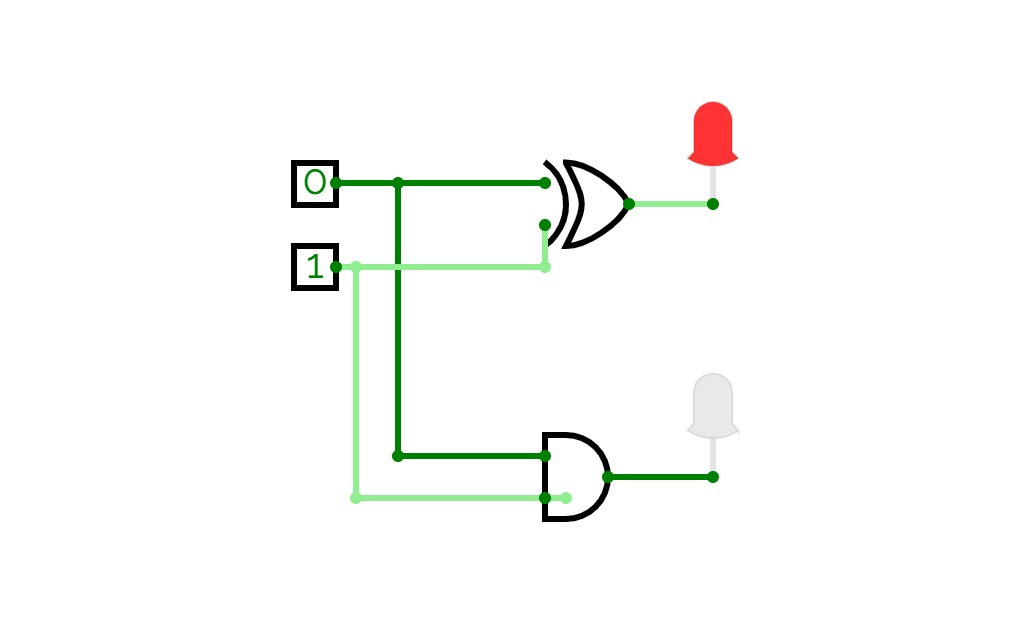

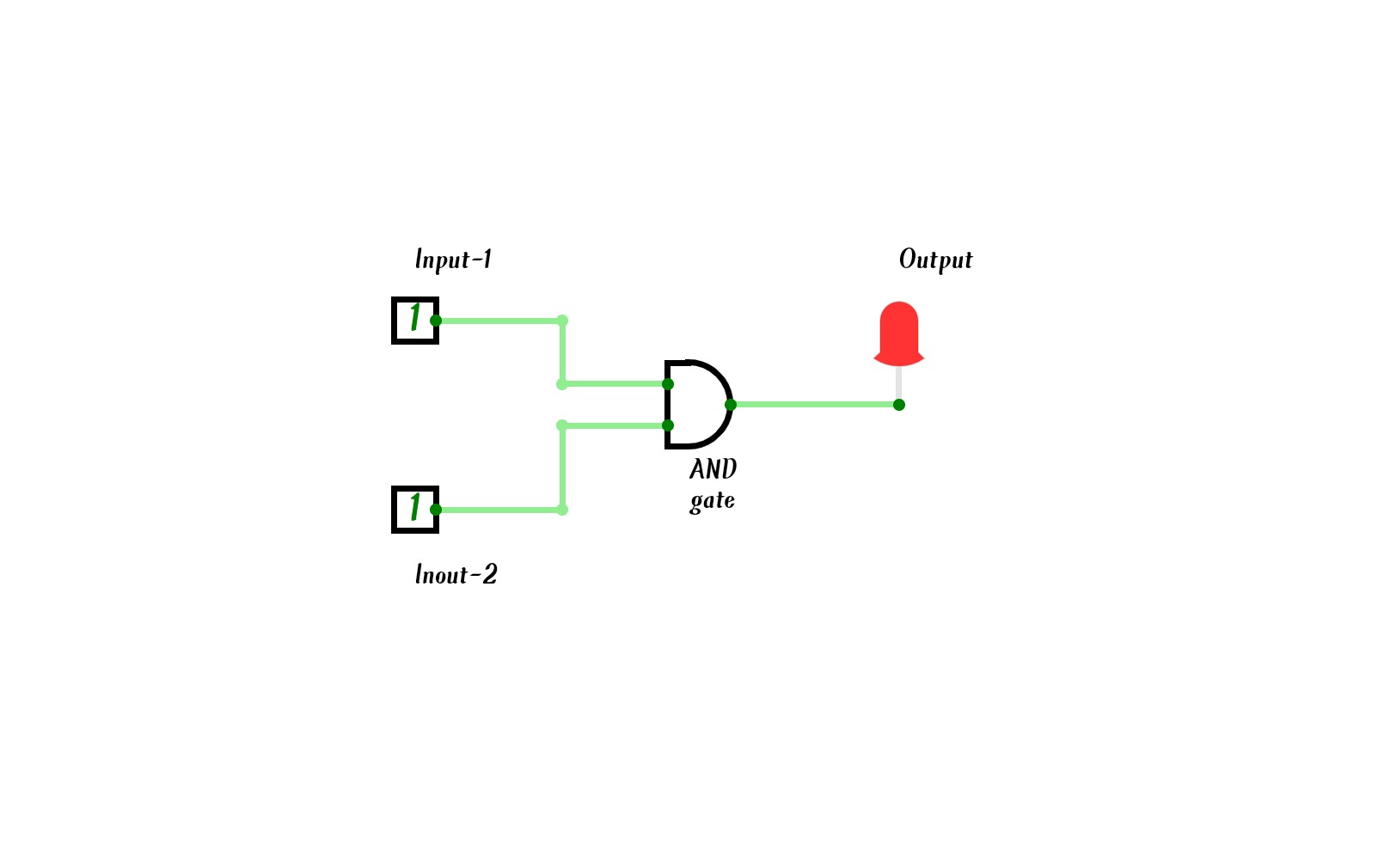

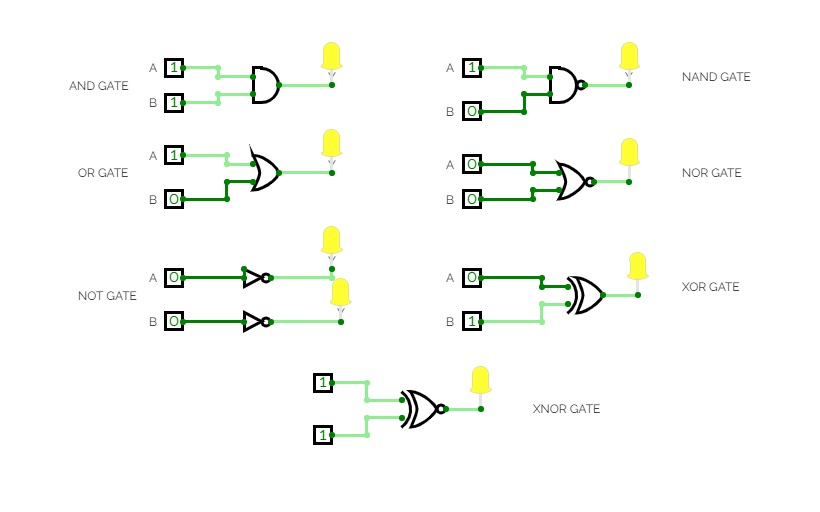

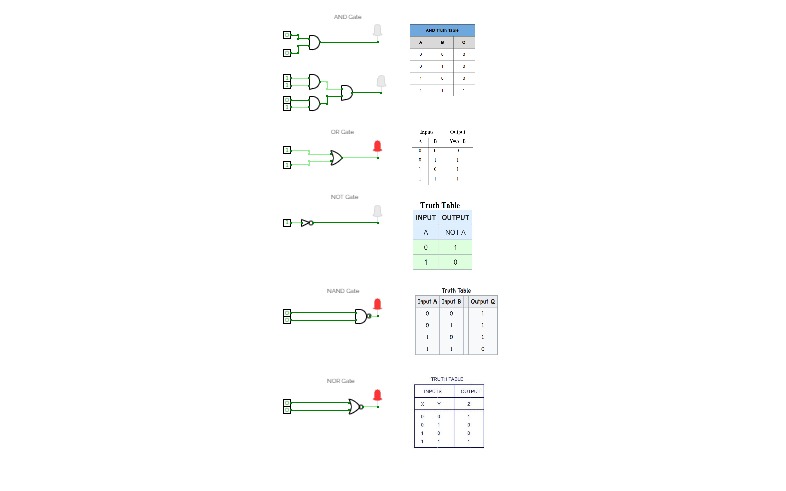

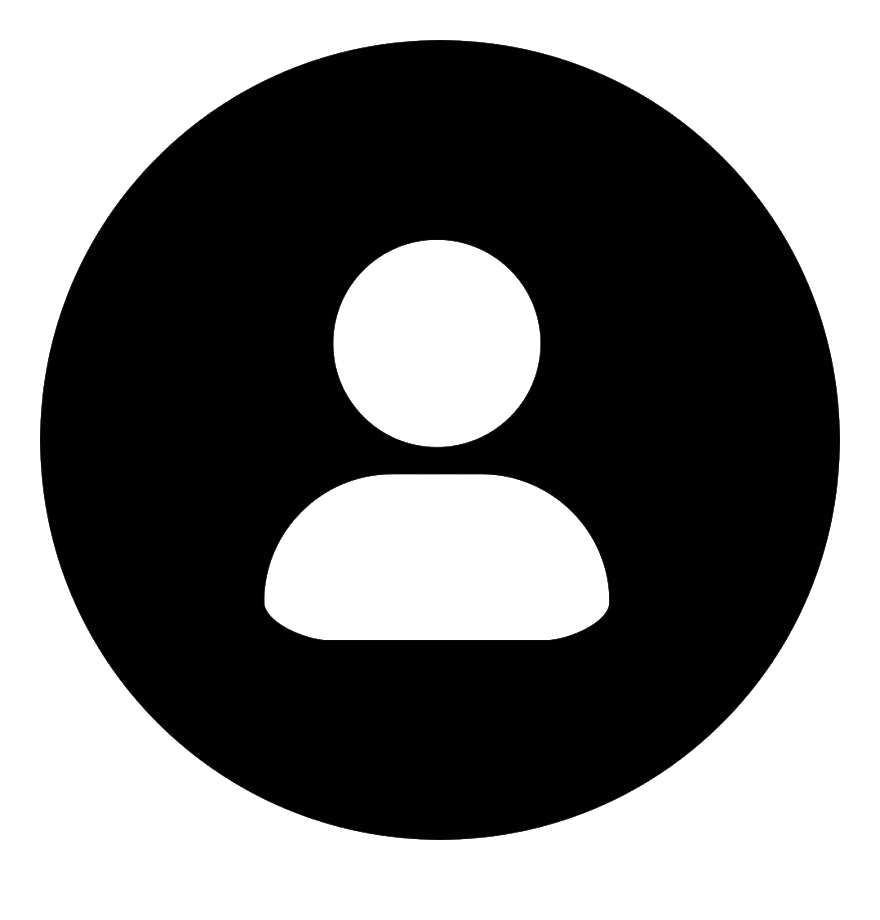

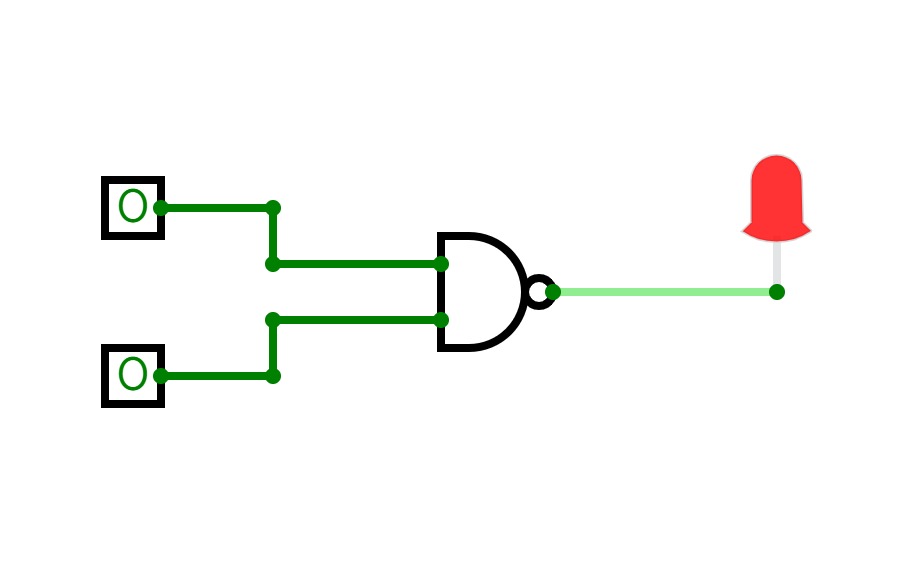

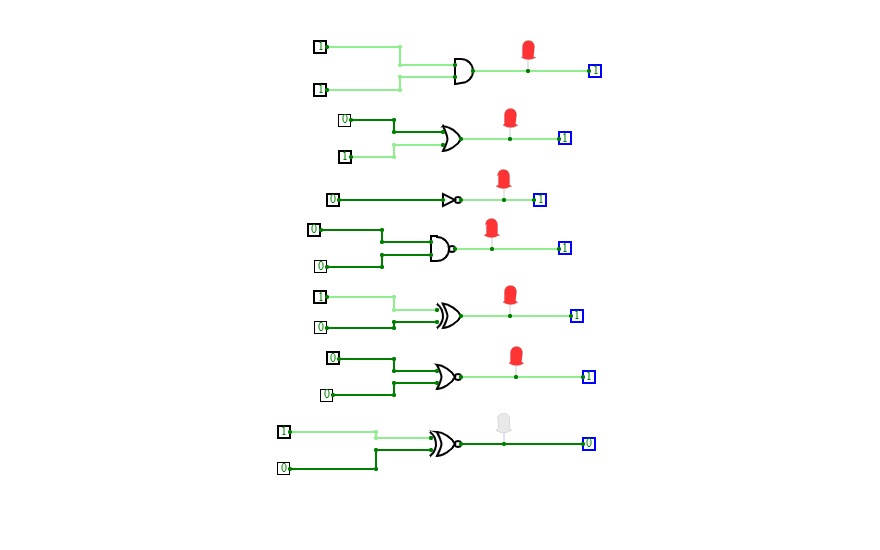

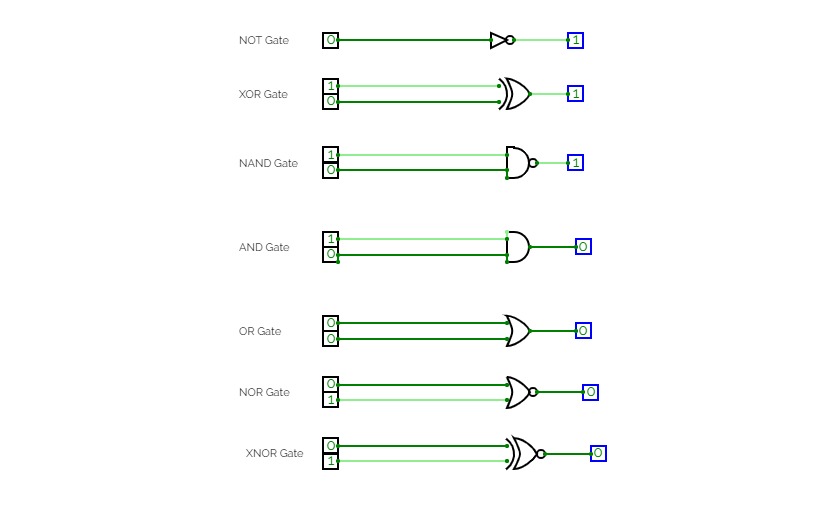

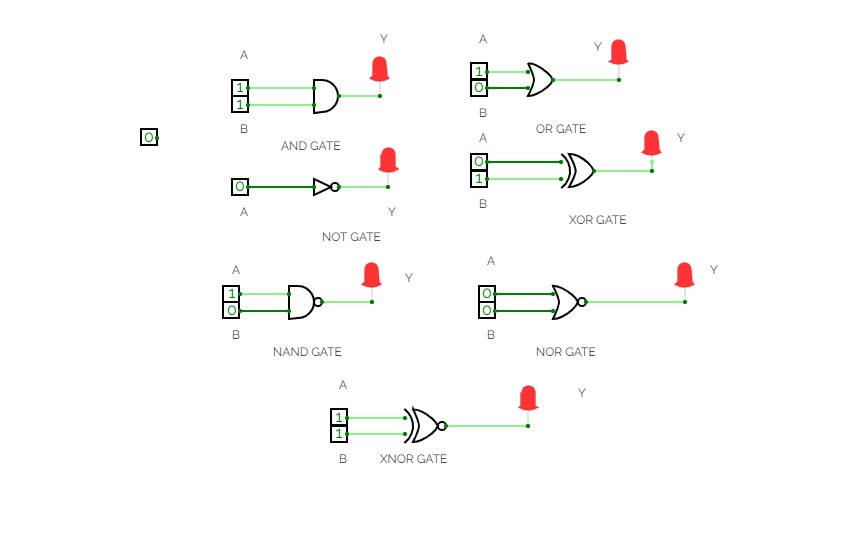

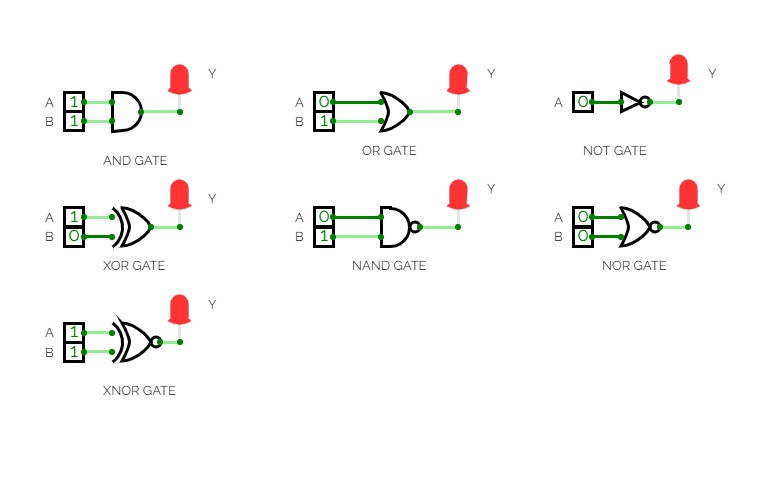

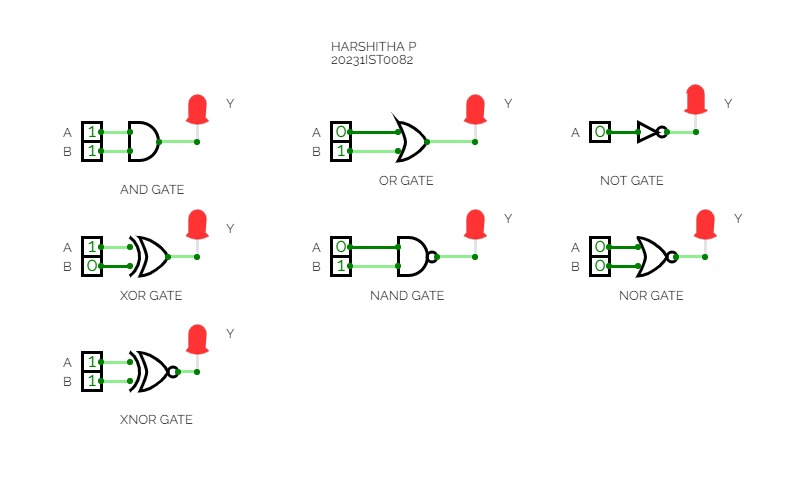

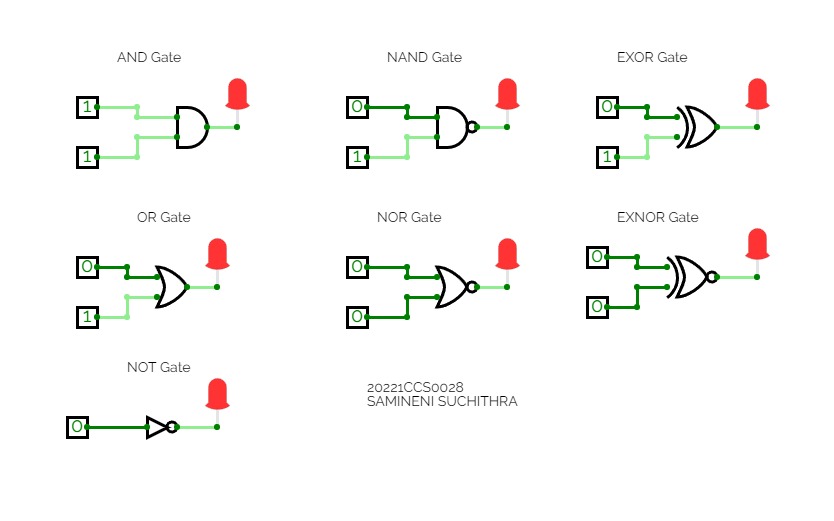

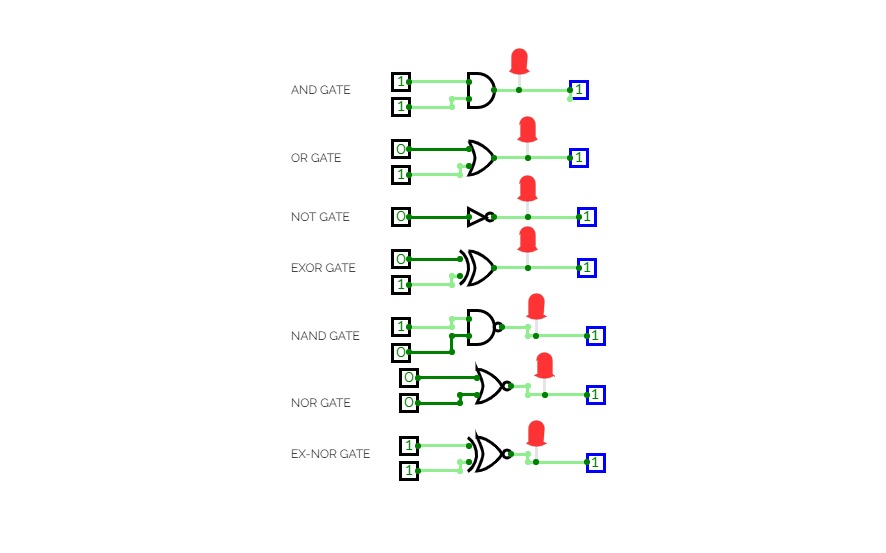

logic gates

logic gatesLogic gate is a physical device implementing a Boolean function. It performs a logic operation on one or more binary inputs and produces a single binary output.

A free, simple, online logic gate simulator. Investigate the behaviour of AND, OR, NOT, NAND, NOR and XOR gates. Select gates from the dropdown list and click "add node" to add more gates. Drag from the hollow circles to the solid circles to make connections. Right click connections to delete them. See below for more detailed instructions.

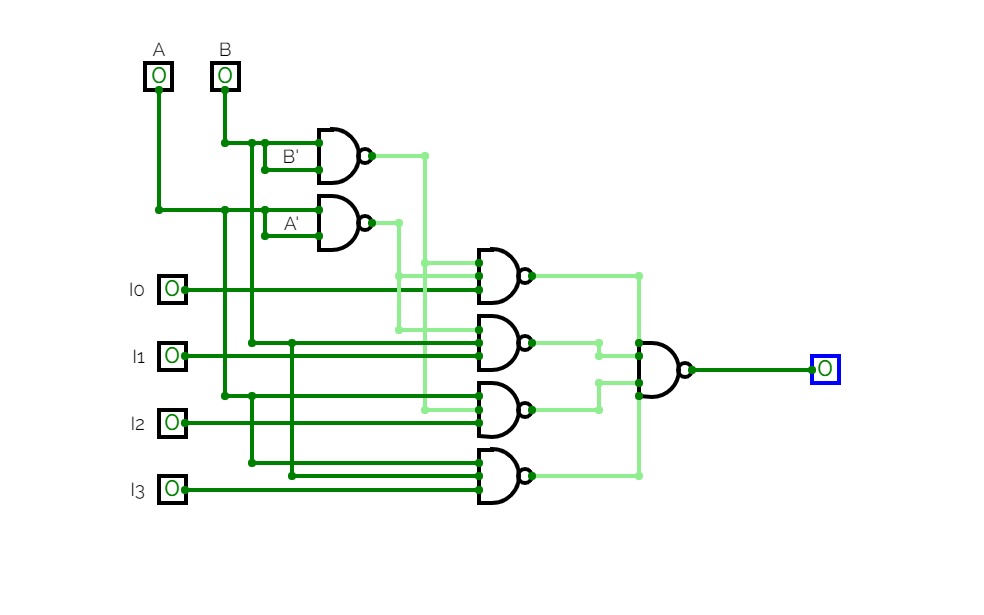

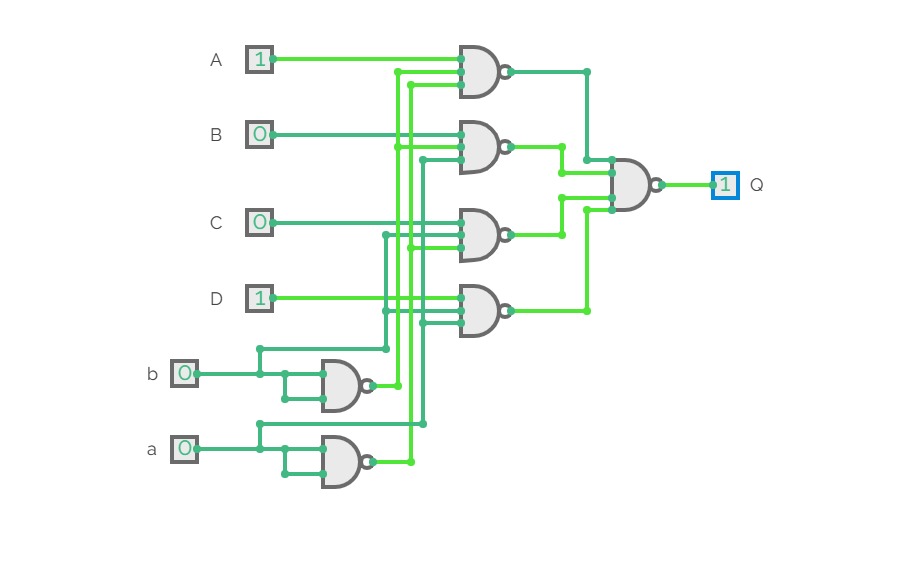

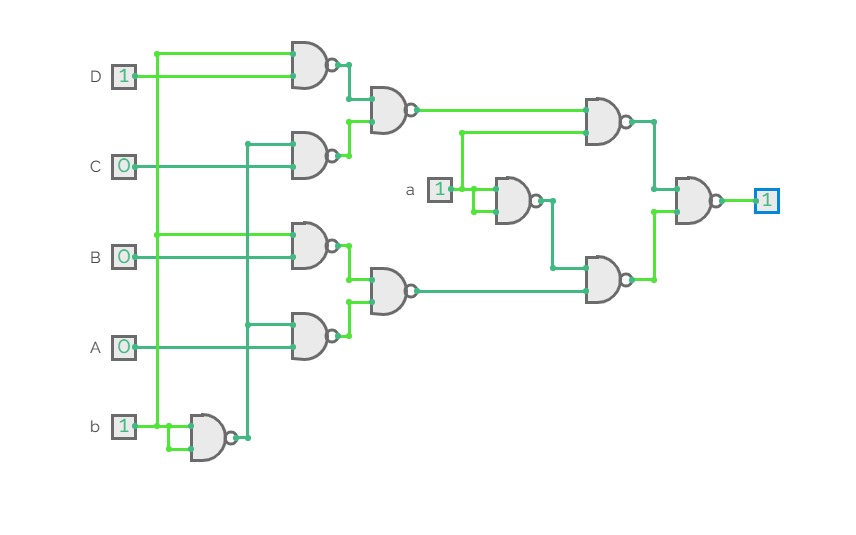

4-bit Multiplexer NAND Implementation

4-bit Multiplexer NAND Implementation4-bit Multiplexer implemented in NAND gates (both 3-input and 2-input)

4-bit Multiplexer in 2-input NAND

4-bit Multiplexer in 2-input NAND4-bit Multiplexer implemented in 2-input NAND gates.

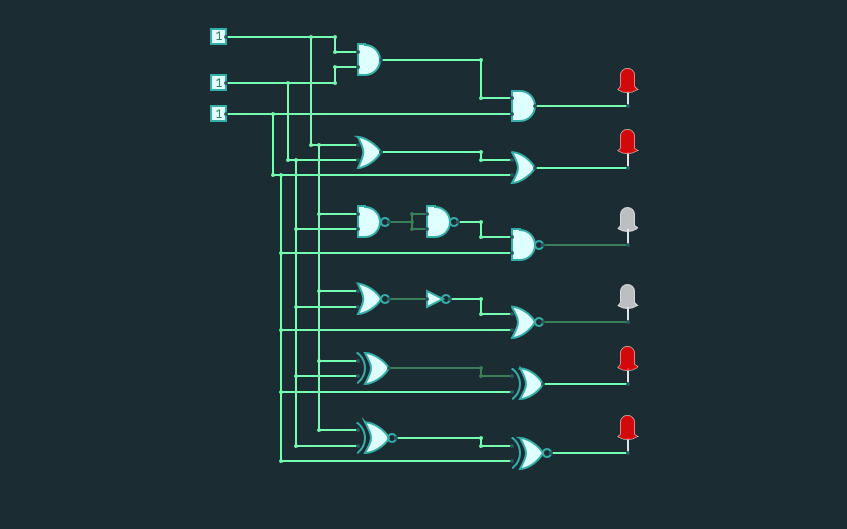

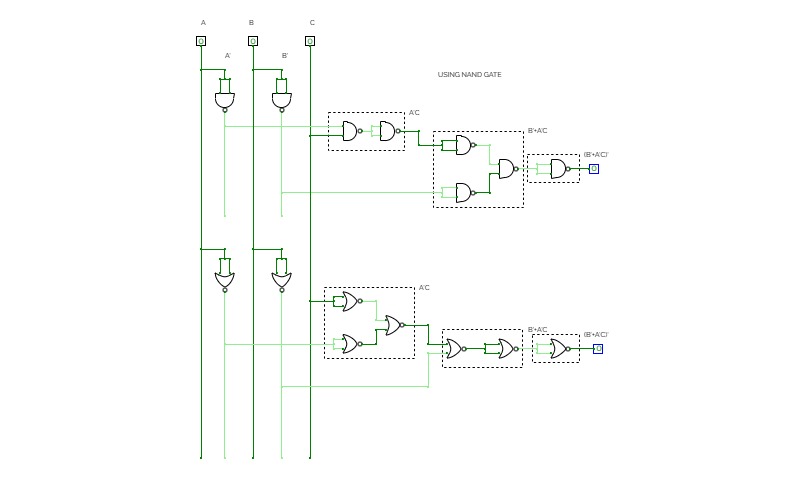

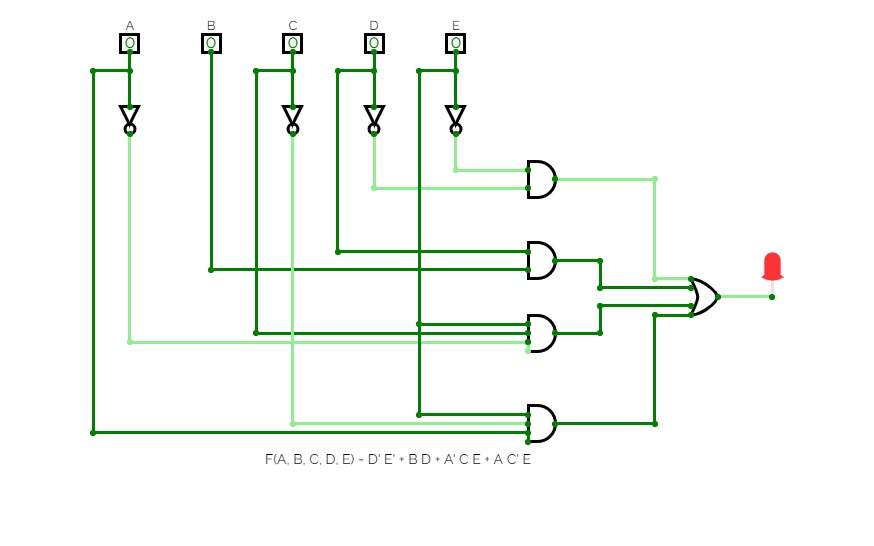

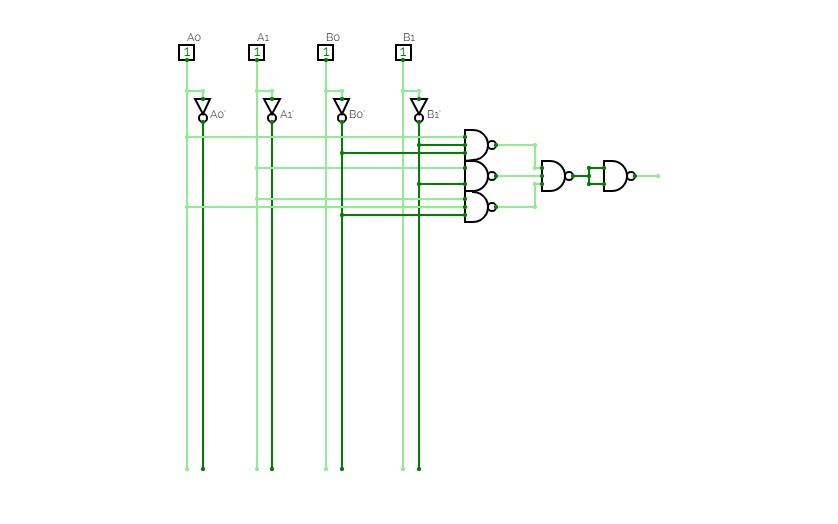

F(x, y, z)= xy + x'y'z + x'yz' and its complement using two level NAND gate only

F(x, y, z)= xy + x'y'z + x'yz' and its complement using two level NAND gate onlyLab5

Lab5Bramki NAND oraz demultipleksery