Quelques CLS

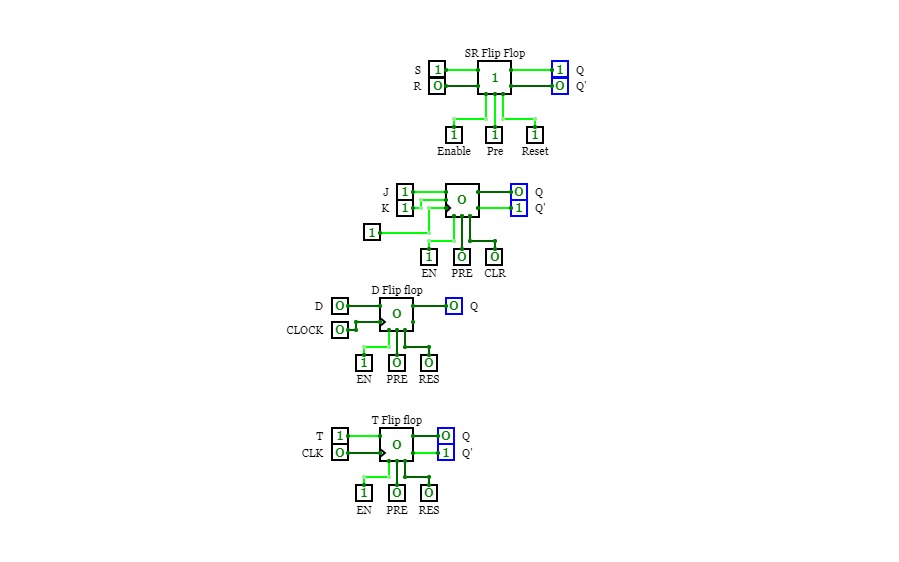

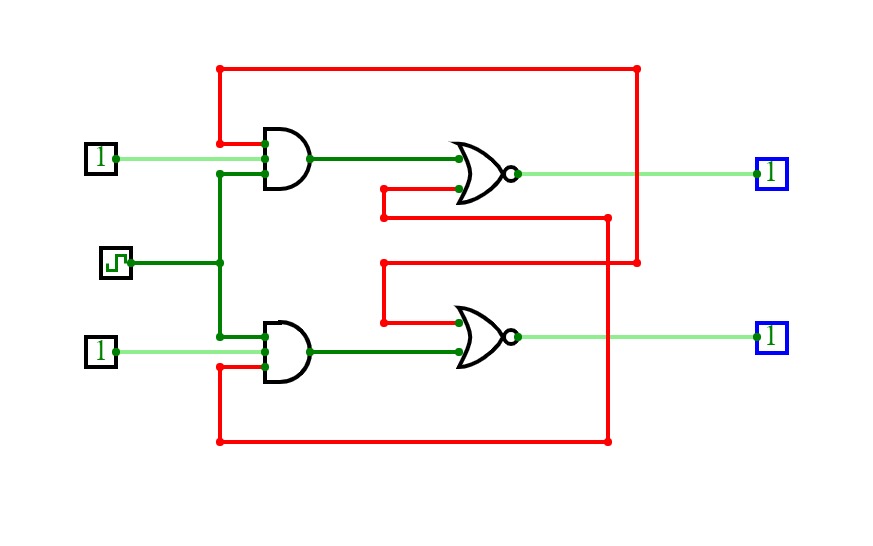

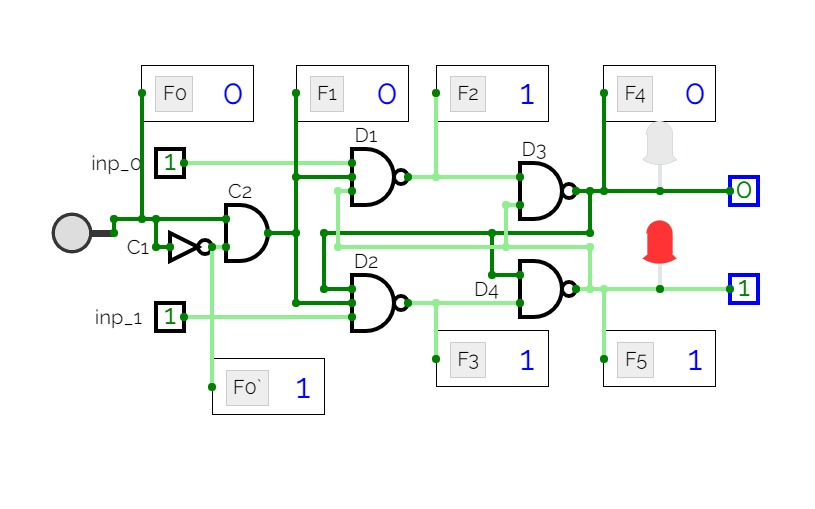

Quelques CLSDans ce projet, je construit quelques circuits logiques séquentiels:

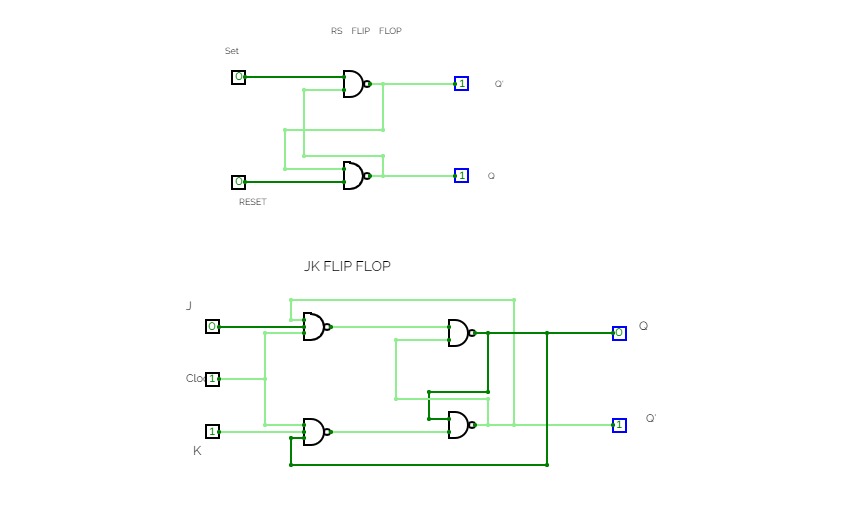

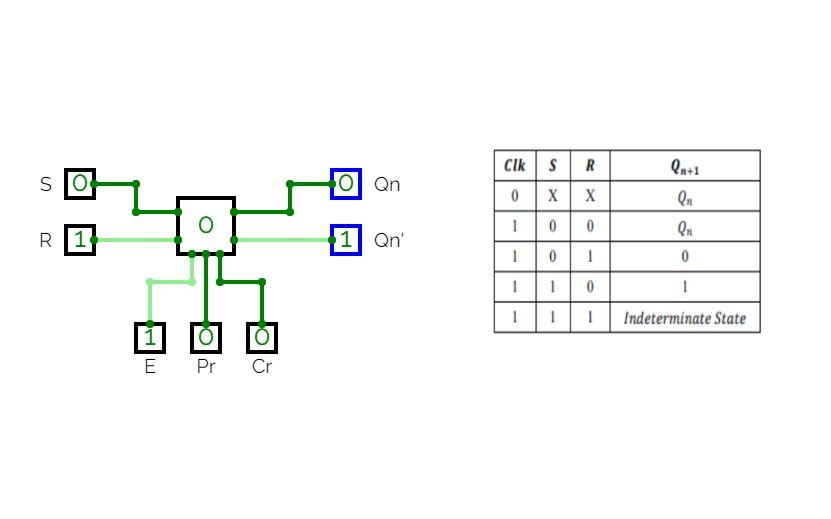

- Bascule RS

- Bascule RSH (syncnhrone)

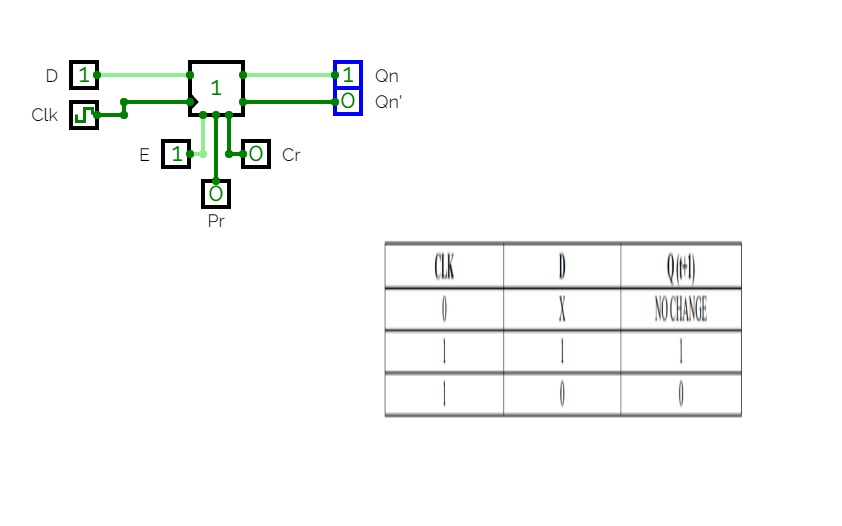

- Bascule D

- Bascule D synchrone

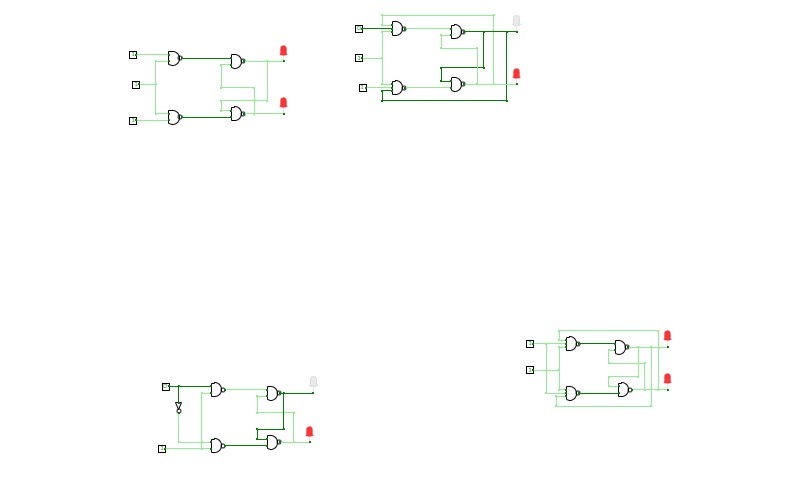

- Bascule JK

- Bascule K=JK synchrone

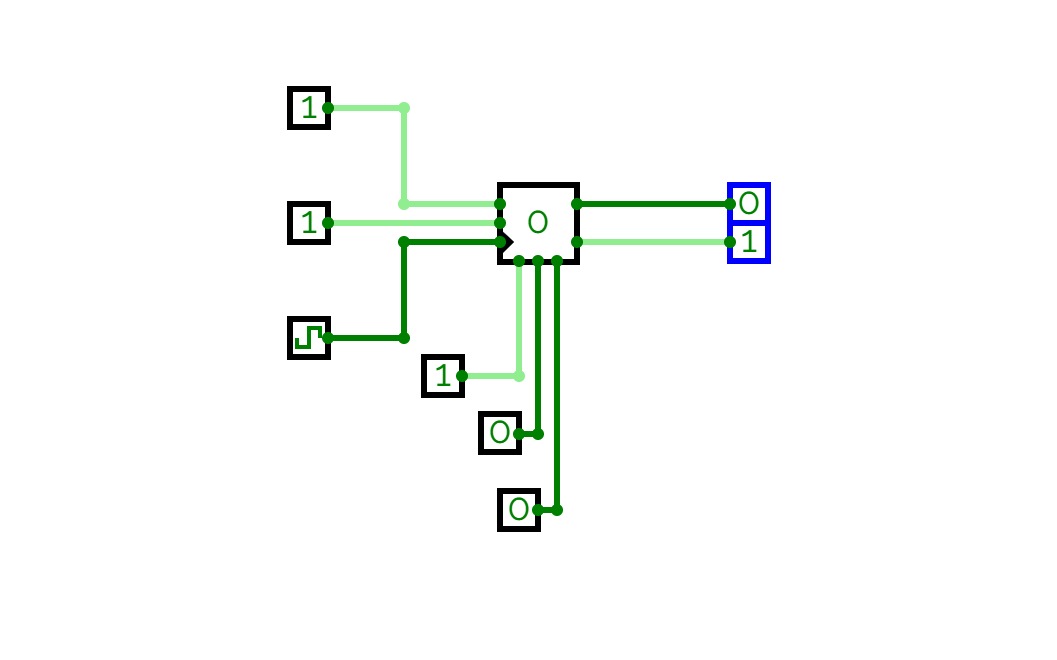

- Bascule D flipflop

- Registre

Flip Flop Verifications

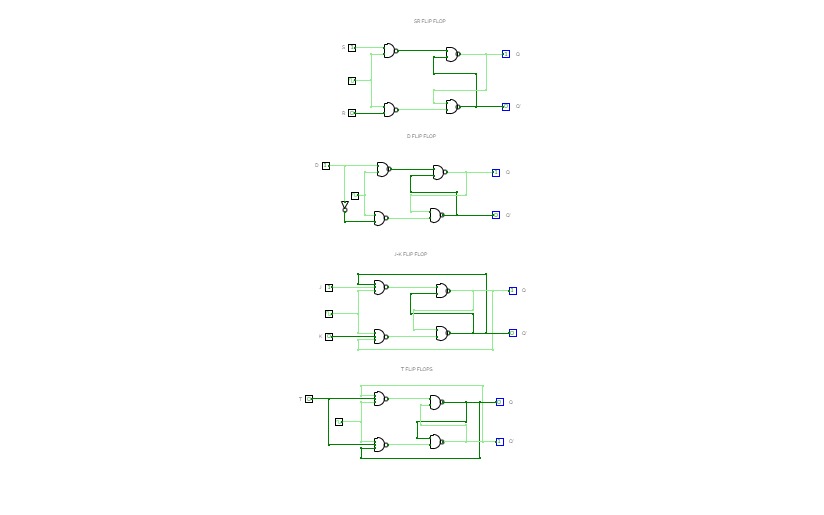

Flip Flop Verifications3NAND

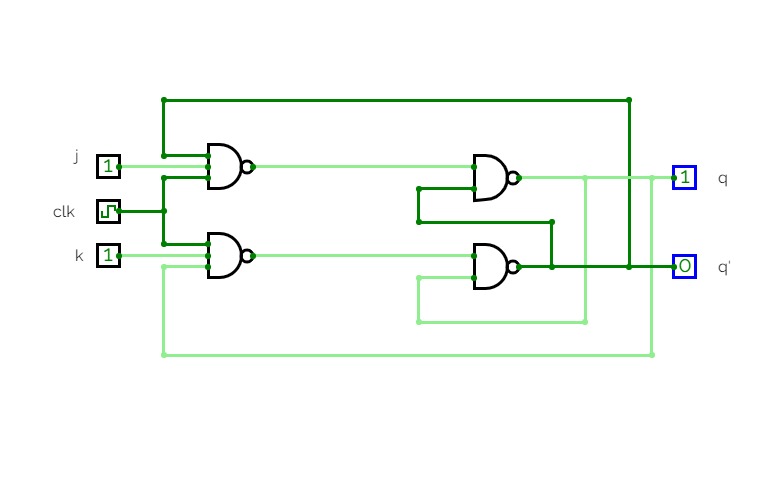

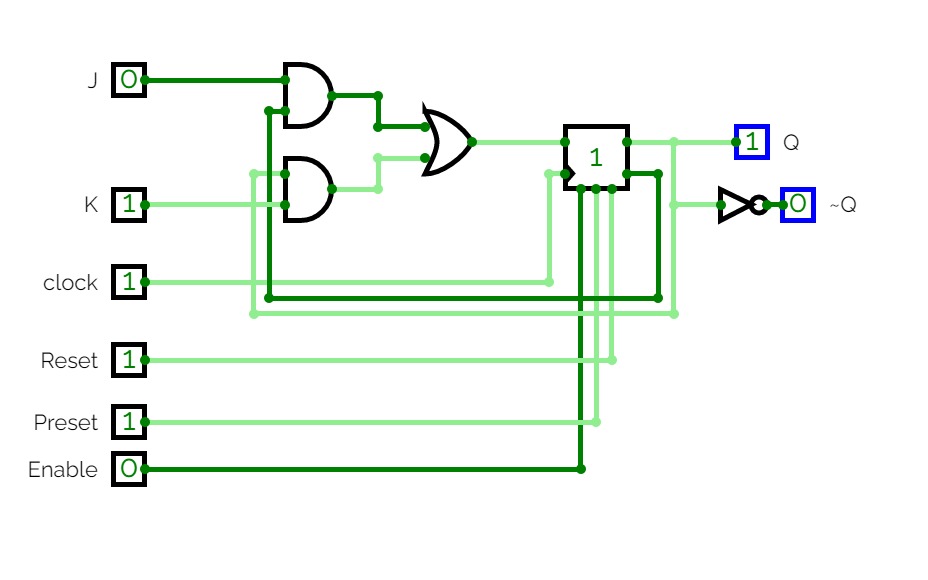

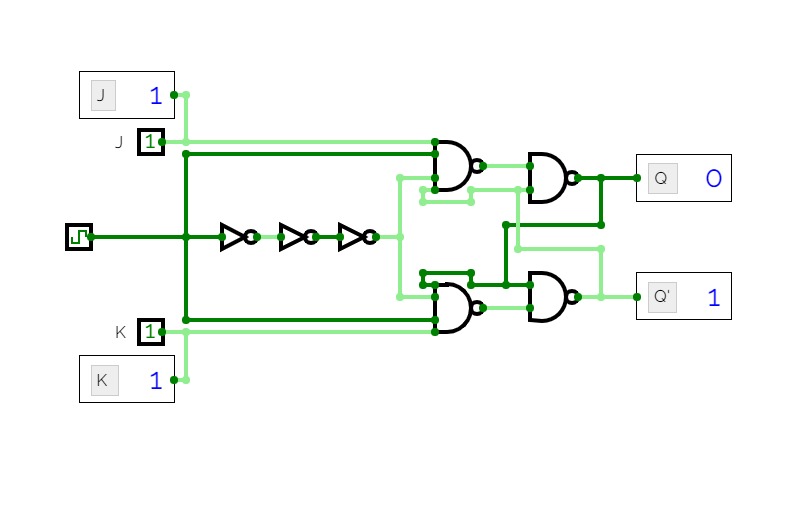

3NANDJK FlipFlop using AND and NOR Gates

JK FlipFlop using AND and NOR GatesA J-K flip-flop is nothing more than an S-R flip-flop with an added layer of feedback. This feedback selectively enables one of the two set/reset inputs so that they cannot both carry an active signal to the multivibrator circuit, thus eliminating the invalid condition.

JK Flip-Flop using Sequential Logic

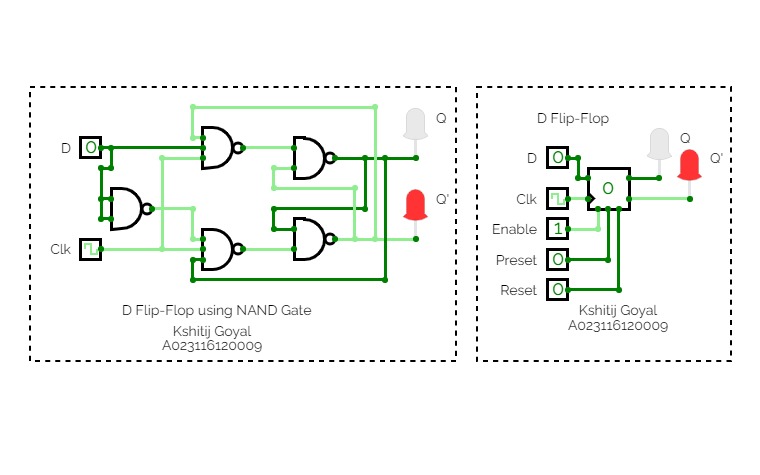

JK Flip-Flop using Sequential LogicFlip Flop Using NAND GATE

Flip Flop Using NAND GATEFlip Flop Using NAND GATE

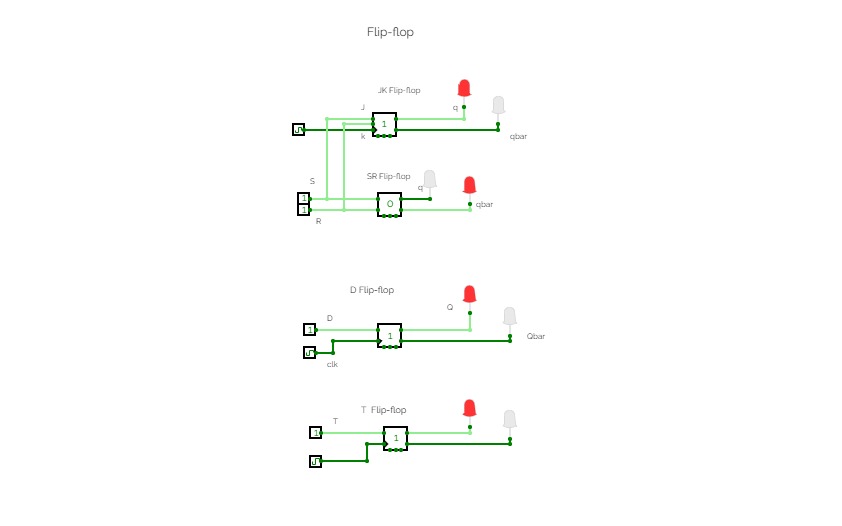

SR, JK, D, T Flip Flop

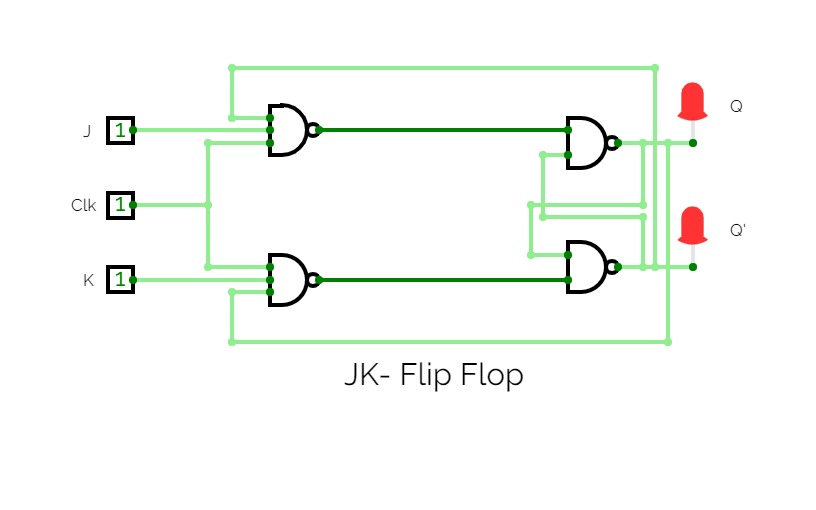

JK- Flip Flop by Souvik Ghosh

JK- Flip Flop by Souvik GhoshFLip Flop CIrcuit

FLip Flop CIrcuitrs and jk flip flop using nand gate.

JK FF

JK FFExperiment 07

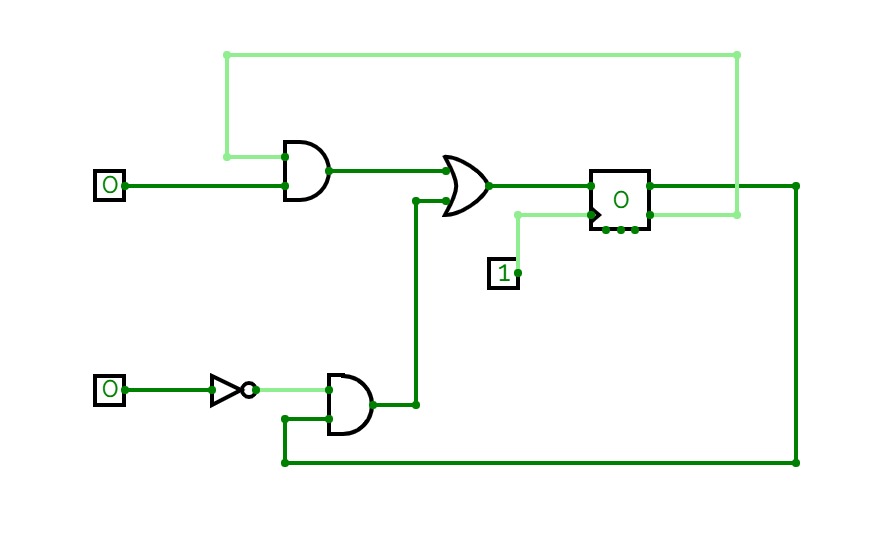

Experiment 07Flip Flop JK with T

Flip Flop JK with TOriginal CircuitVerse JK Flip Flop had a bug that sometimes after J=1, K=1, if you tried to get J=0, K=0 it would invert the value instead of keeping it, as would it be expected. This can be avoided by using a T Flip Flop and finite state machine logic to make the JK Flip Flop.

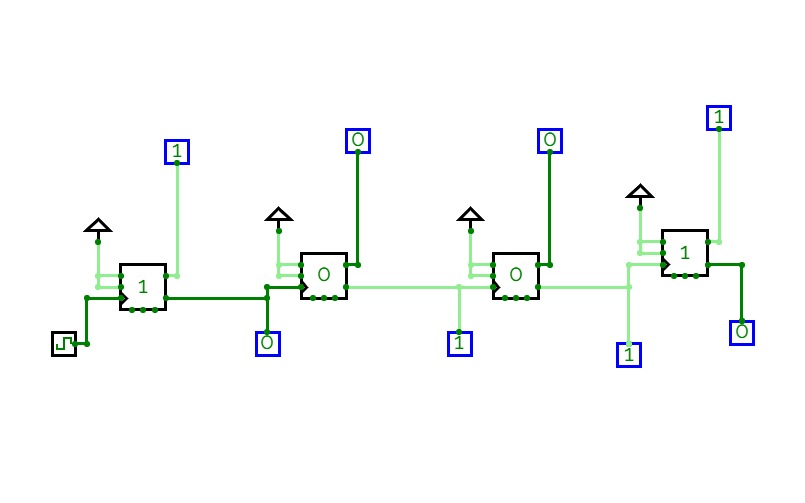

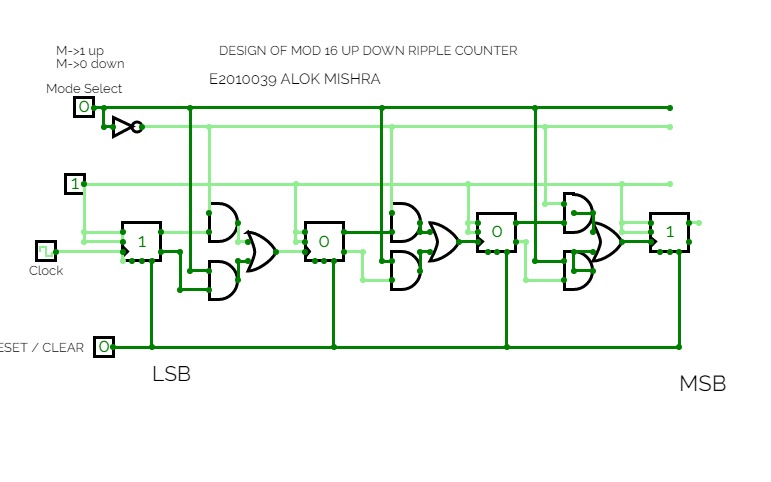

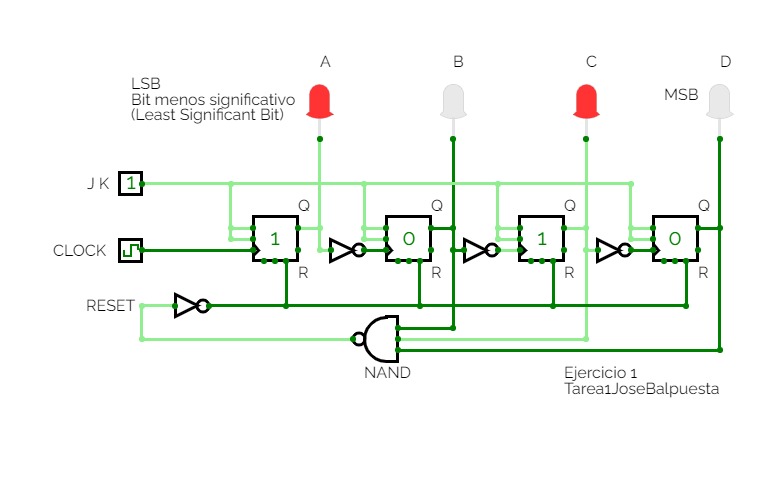

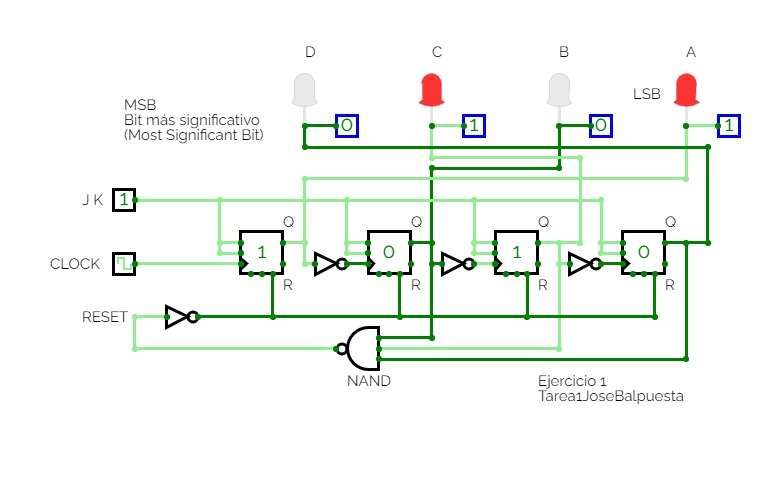

Contador de Rizo MOD-14

Contador de Rizo MOD-14Contador de Rizo Asíncrono MOD-14

Contador de Rizo MOD-14

Contador de Rizo MOD-14Contador de Rizo MOD-14 BINARIO

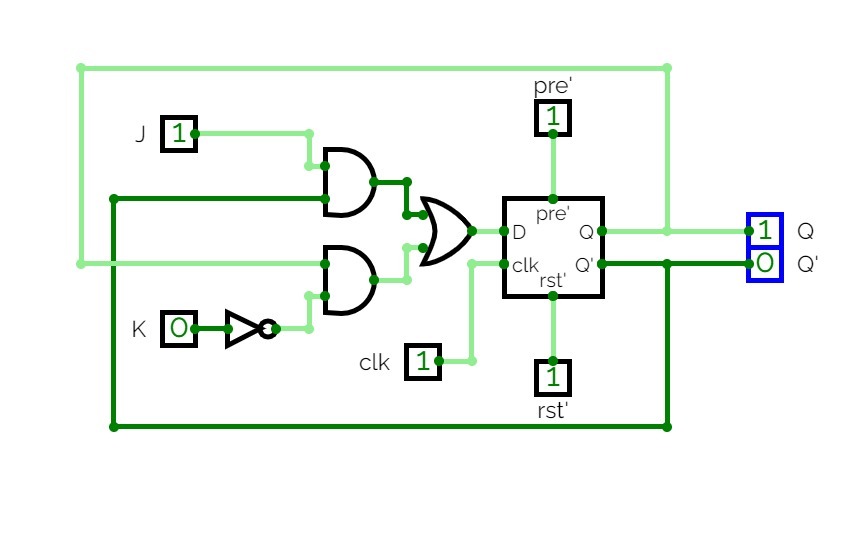

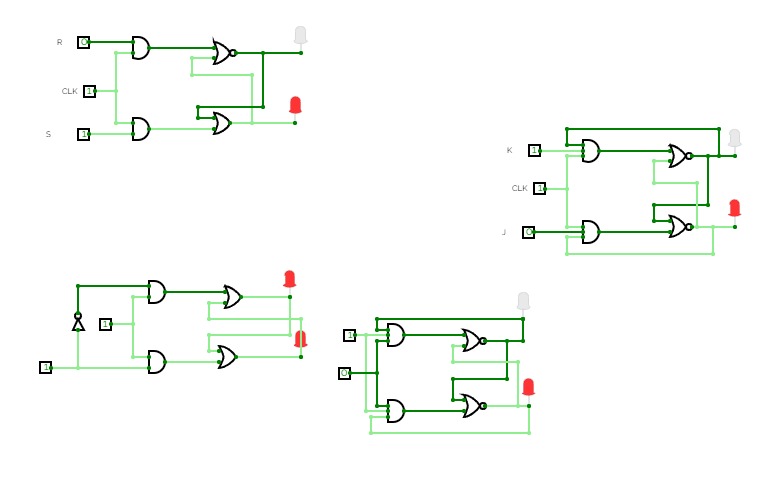

JK FlipFlop NAND Gates (Rising edge)

JK FlipFlop NAND Gates (Rising edge)This demonstrate the JK-Flipflop.

J 0, K 0 => do nothing

J 1, K 0 => Set (Q = 1, Q' = 0)

J 0, K 1 => Reset (Q = 0, Q' = 1)

J 1, K 1 => Toggle Q and Q'

Untitled

Untitledexperiment6

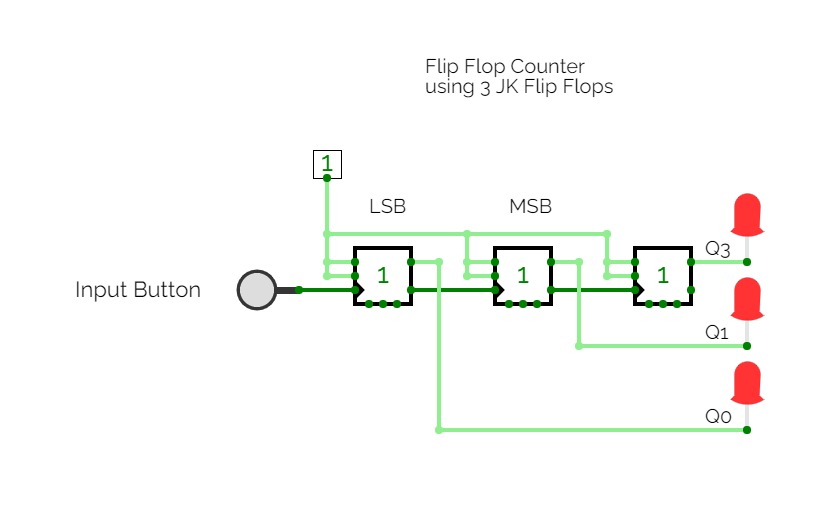

experiment6JK Flip Flop

JK Flip FlopA collection of different JK Flip Flop Circuits. If you're finding this from the CDA Computer Org review the Basic JK Flip Flop is the circuit we learned about in class.

(See this Stack Exchange post for more info https://electronics.stackexchange.com/questions/491352/jk-latch-possible-ben-eater-error/491439#491439)