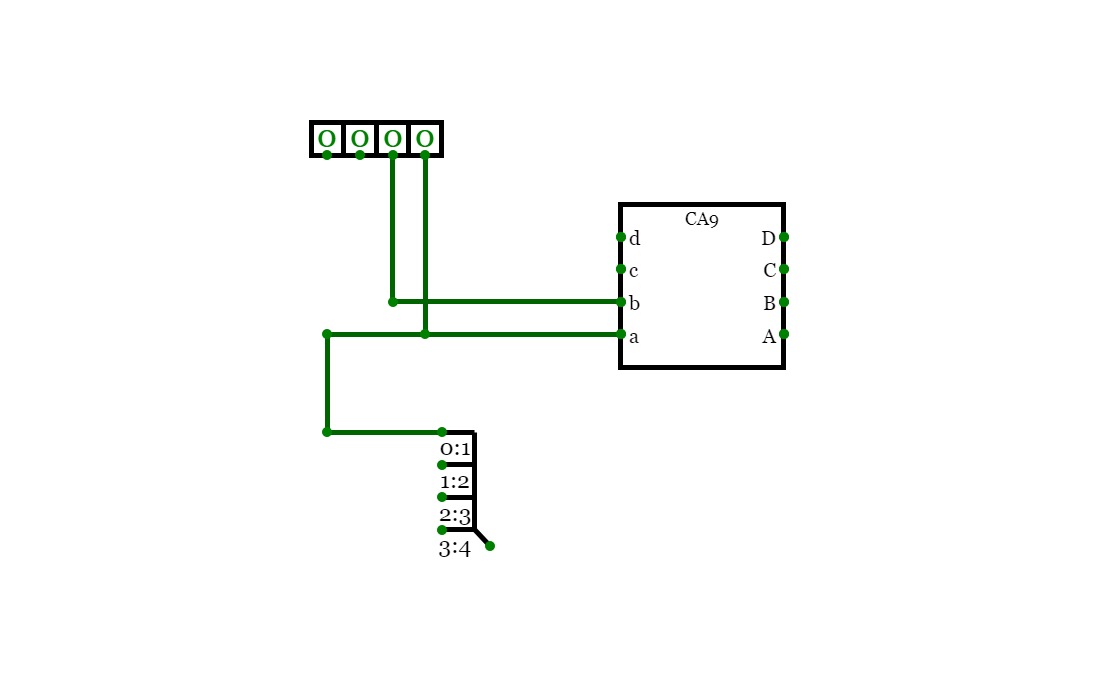

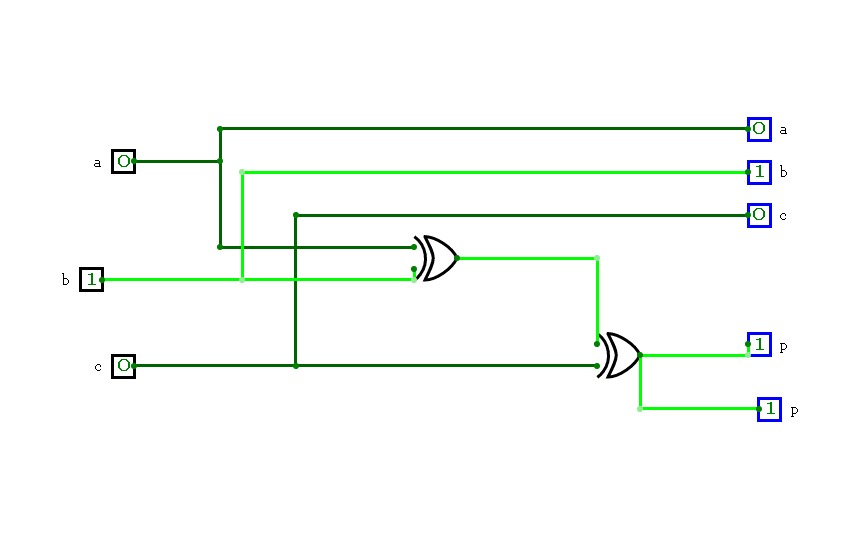

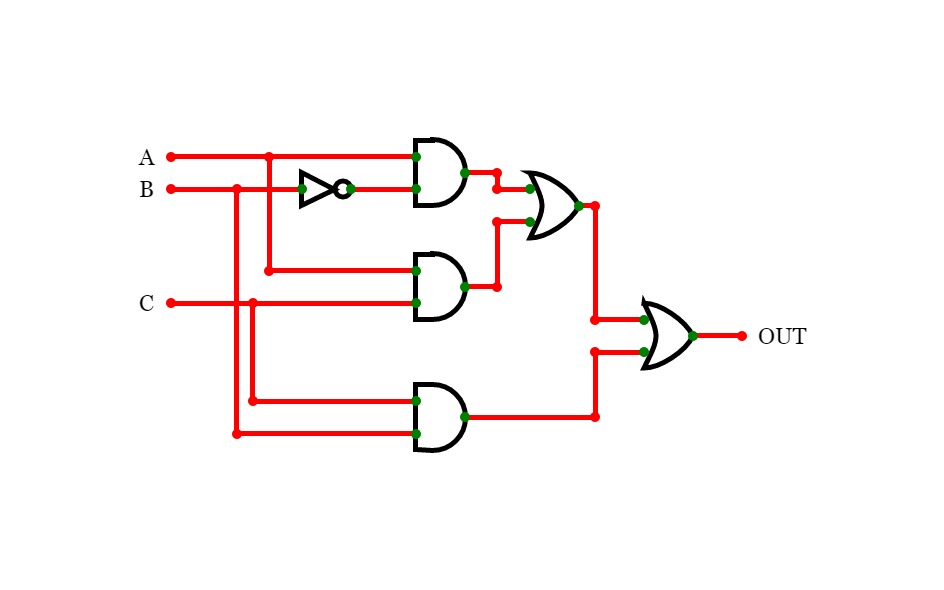

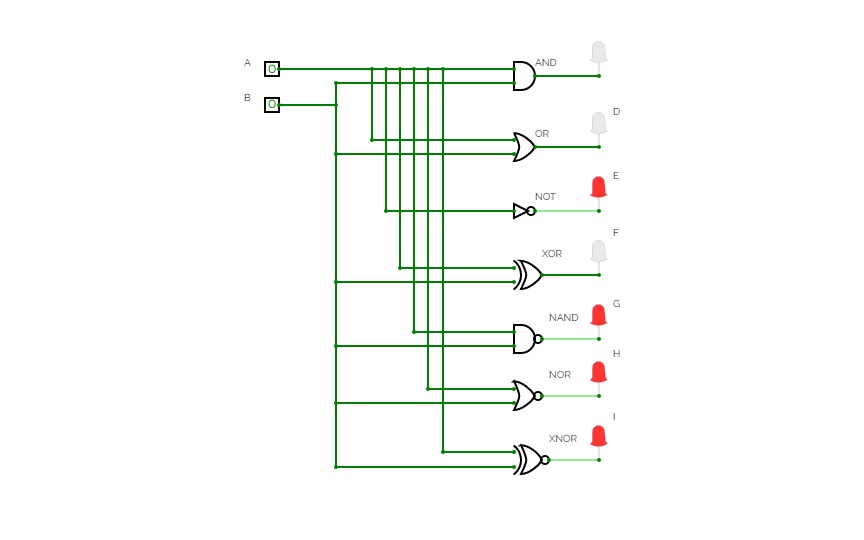

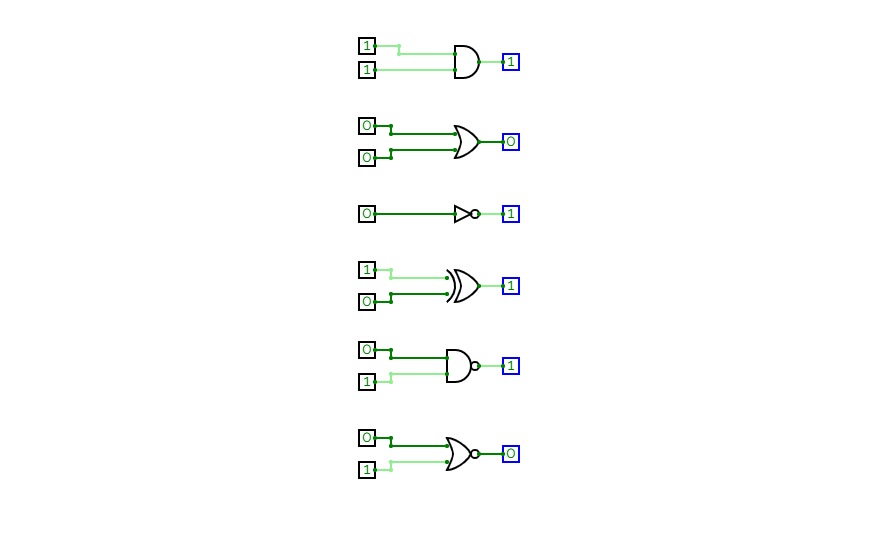

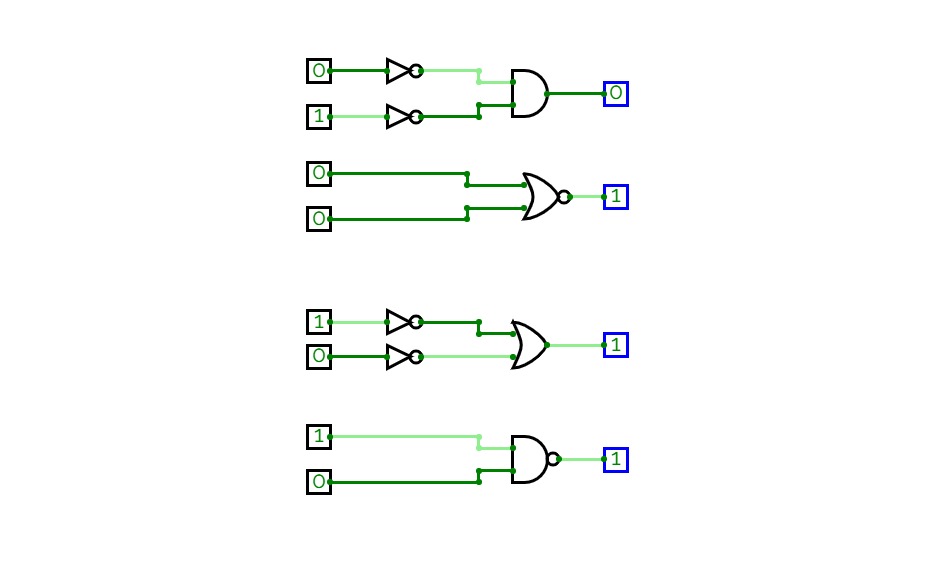

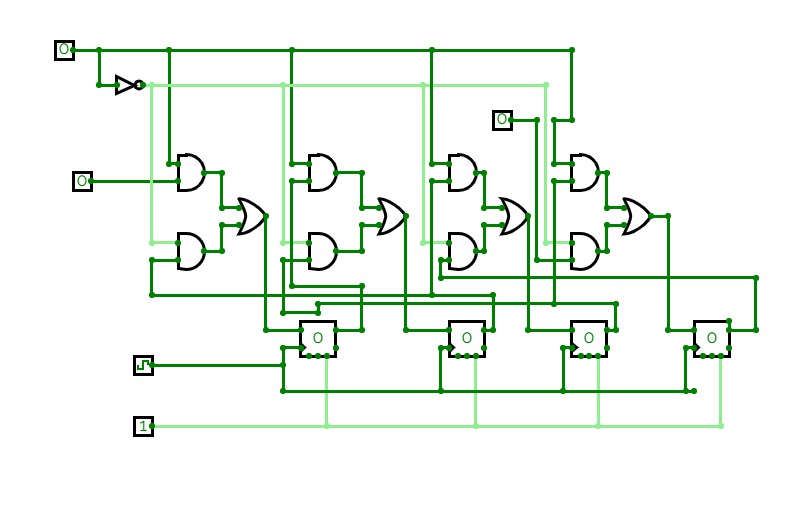

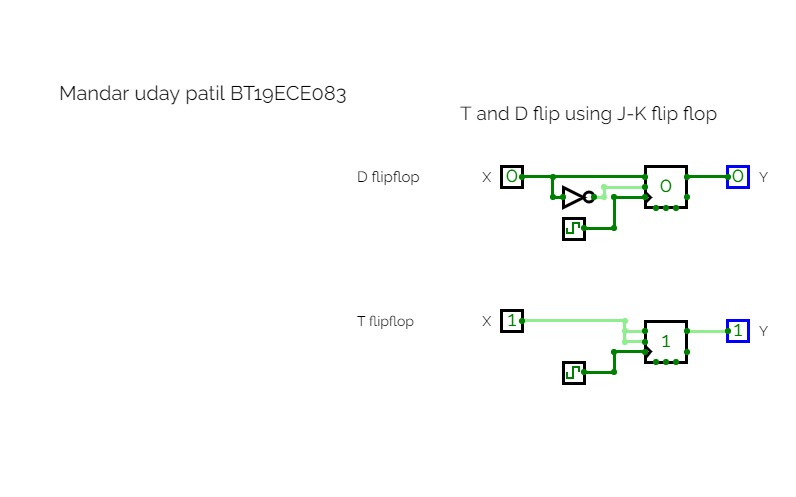

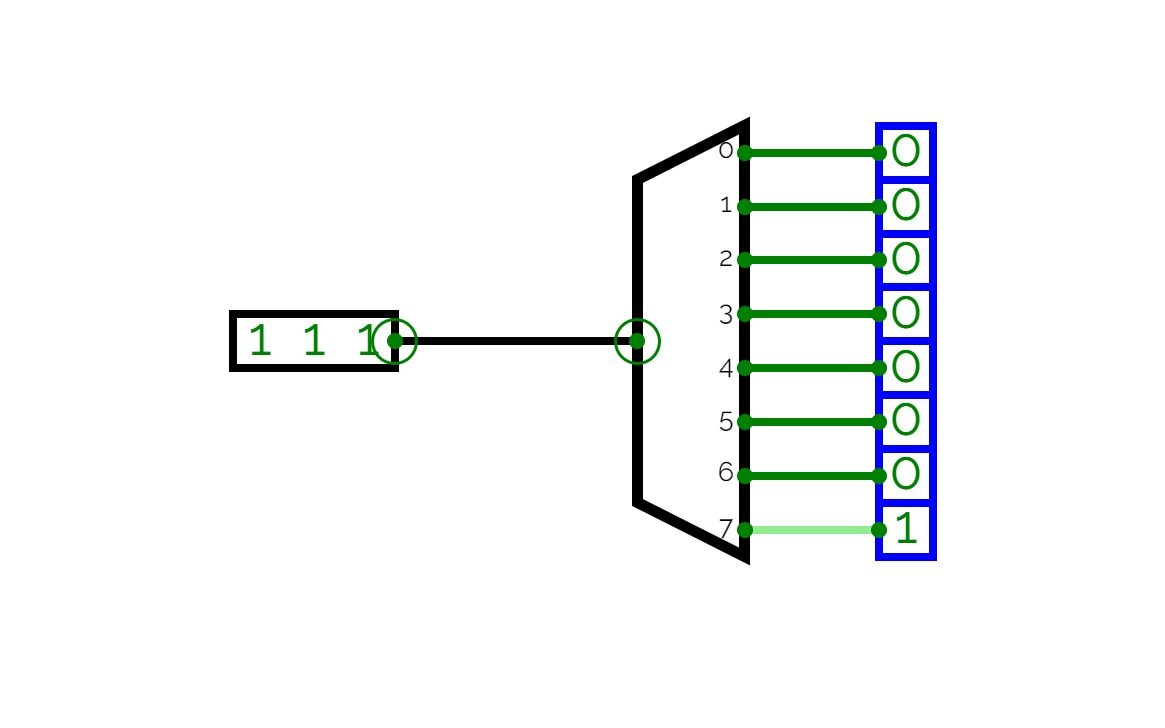

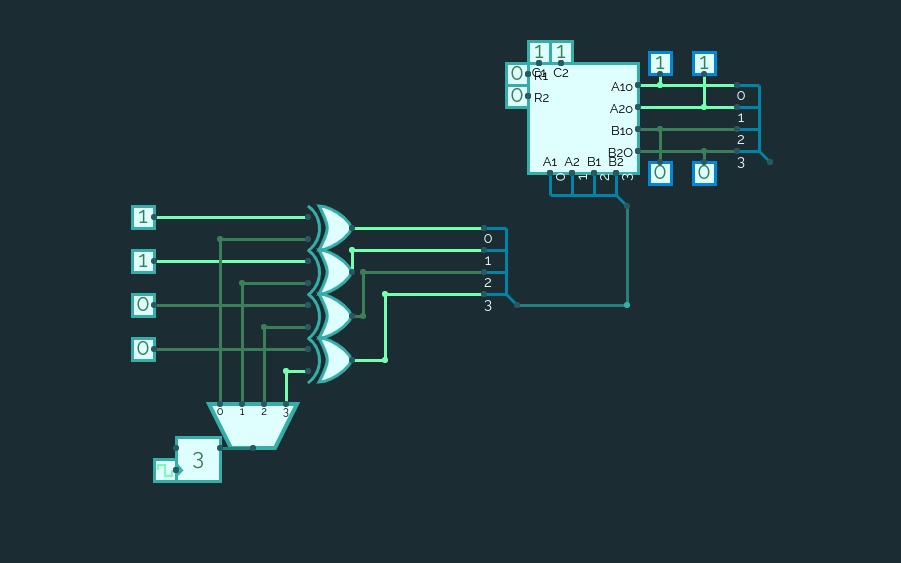

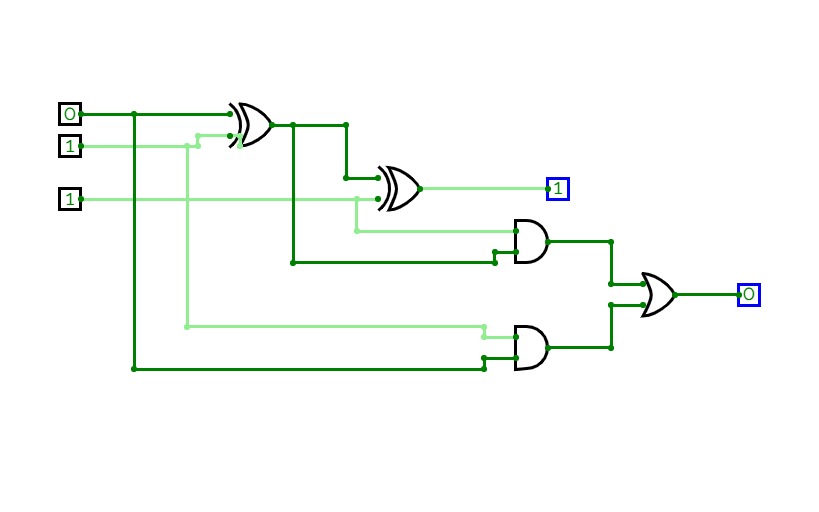

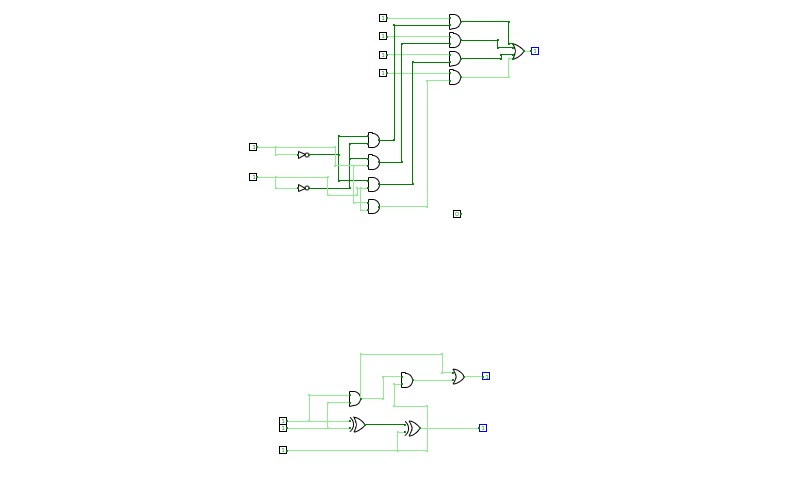

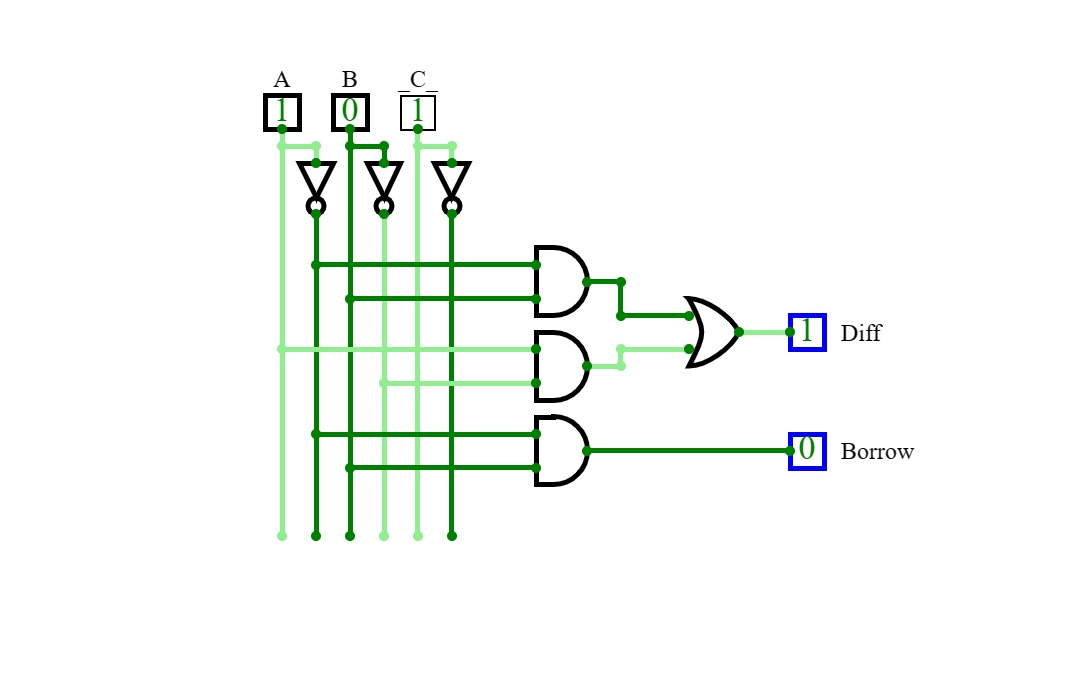

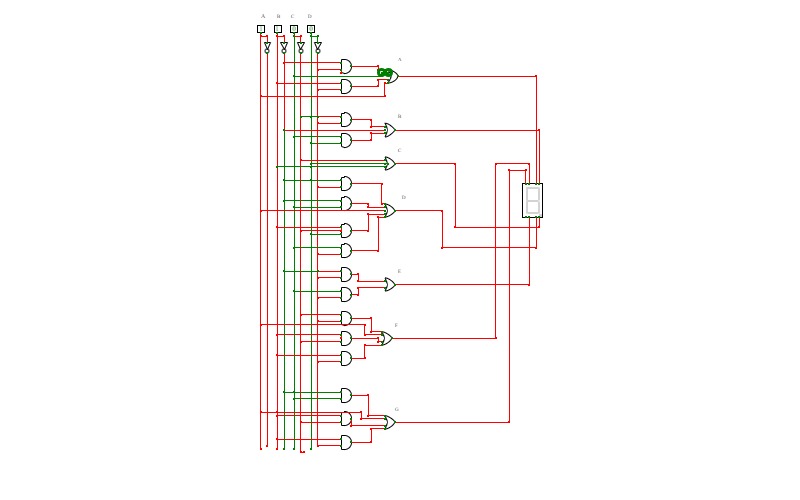

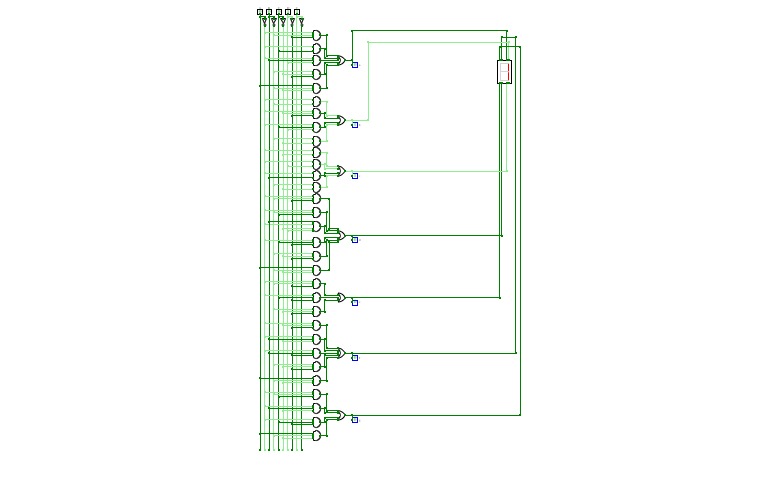

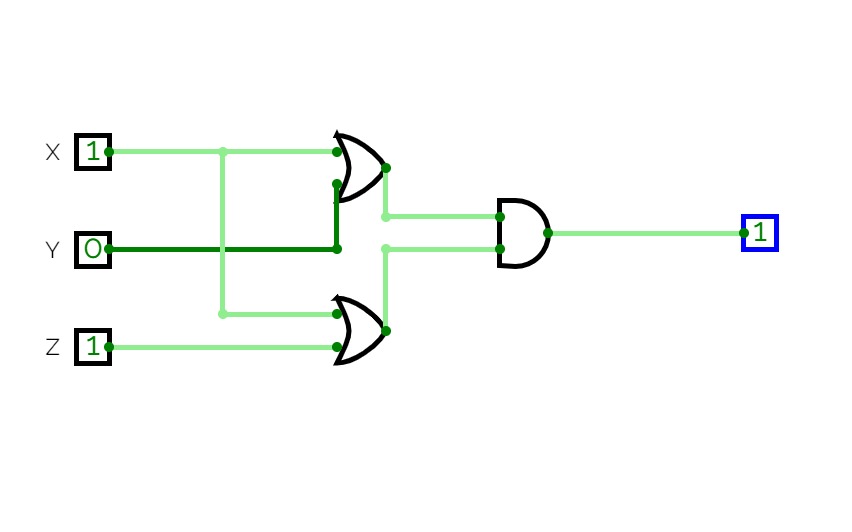

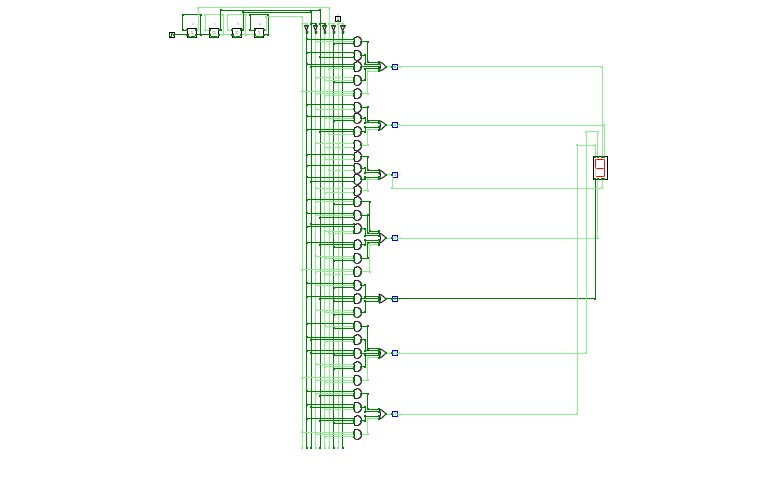

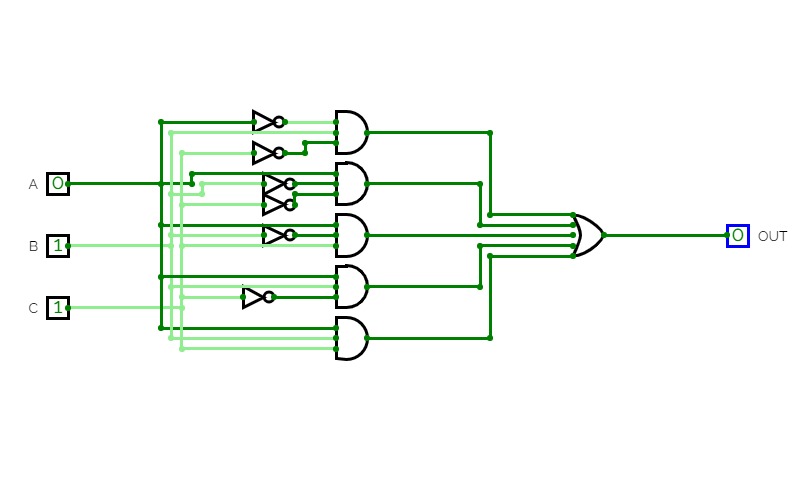

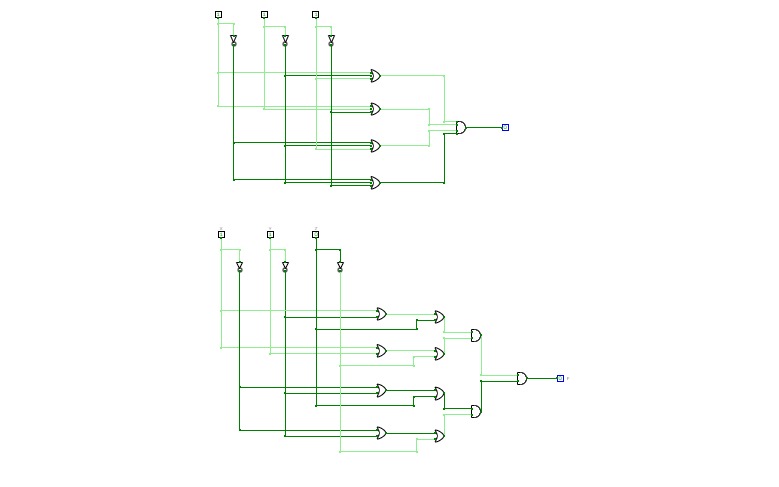

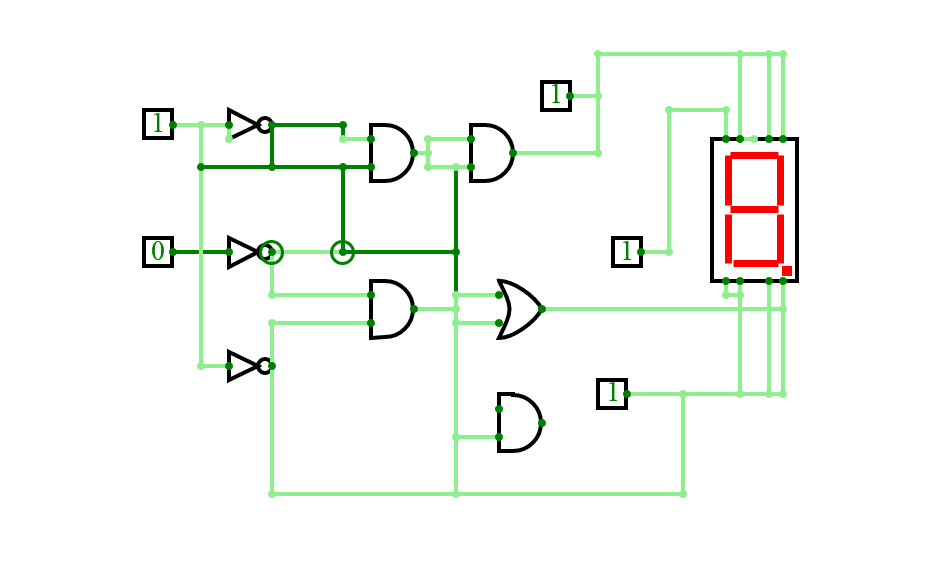

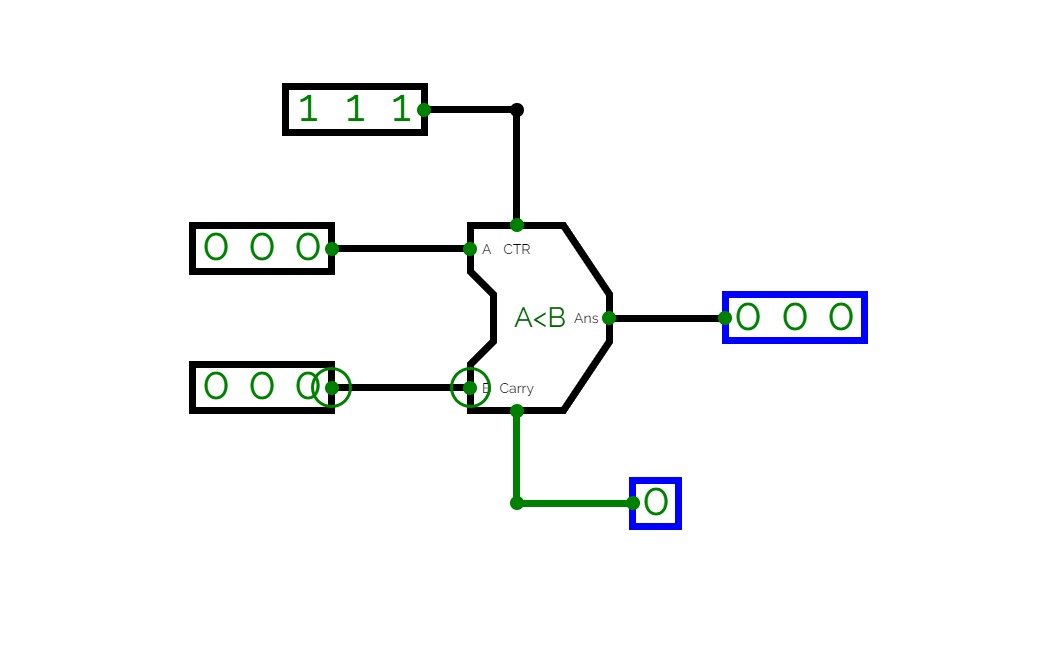

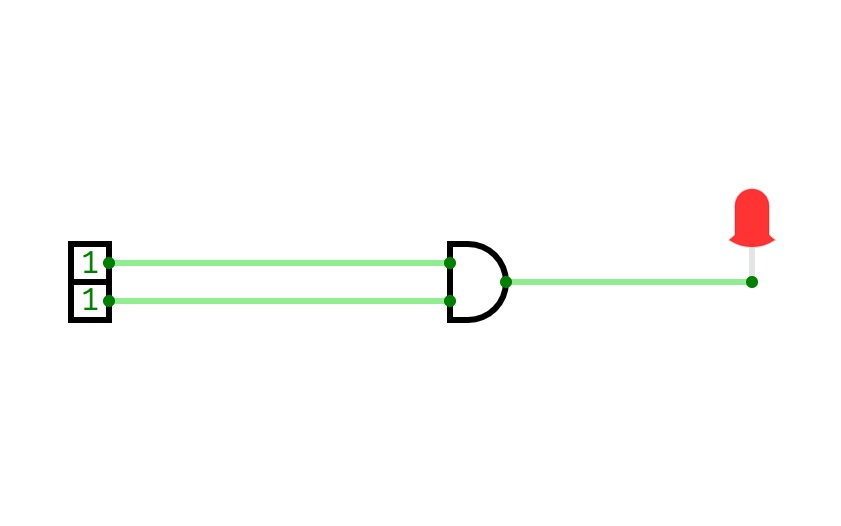

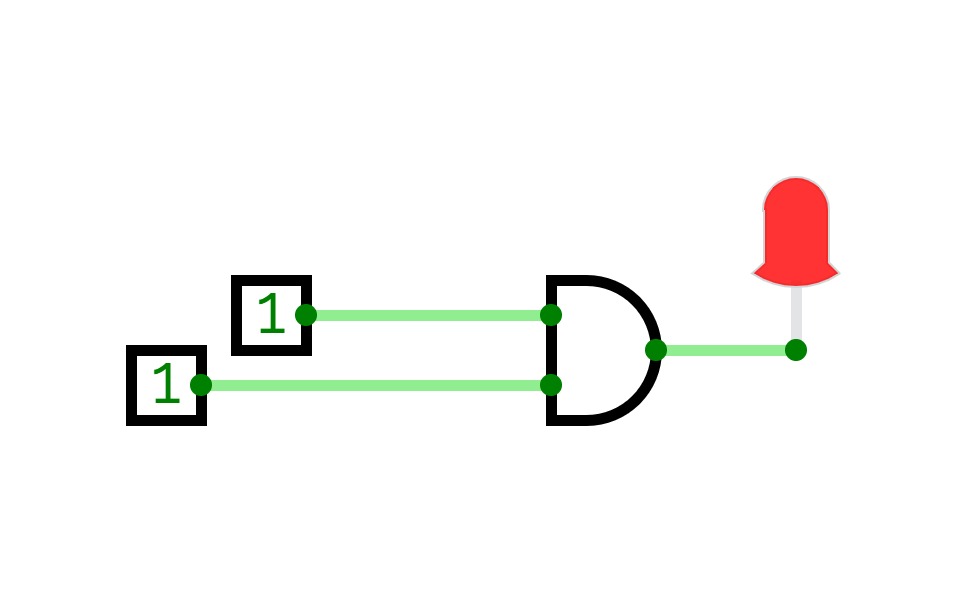

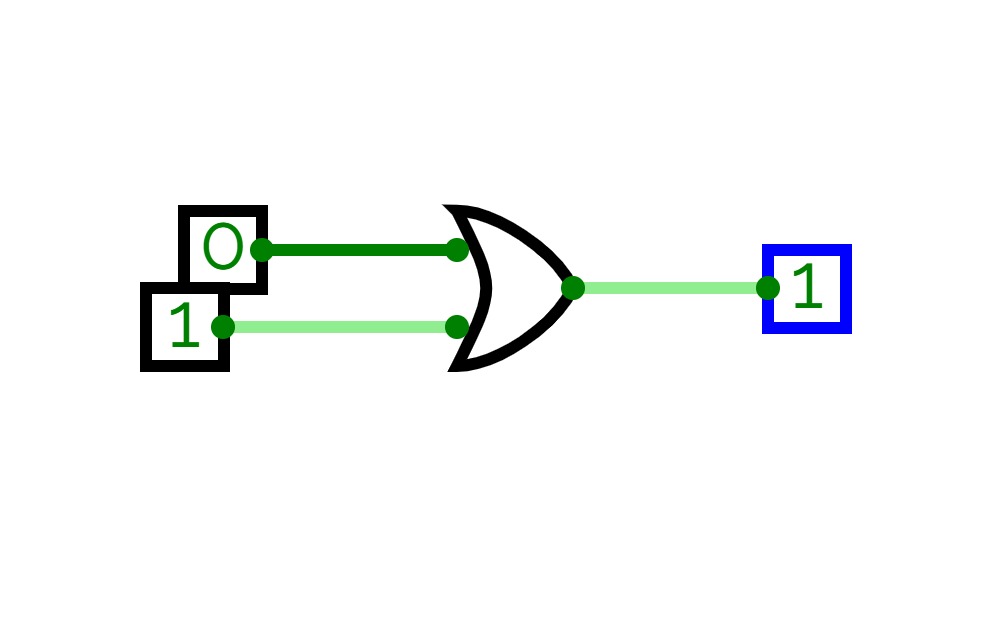

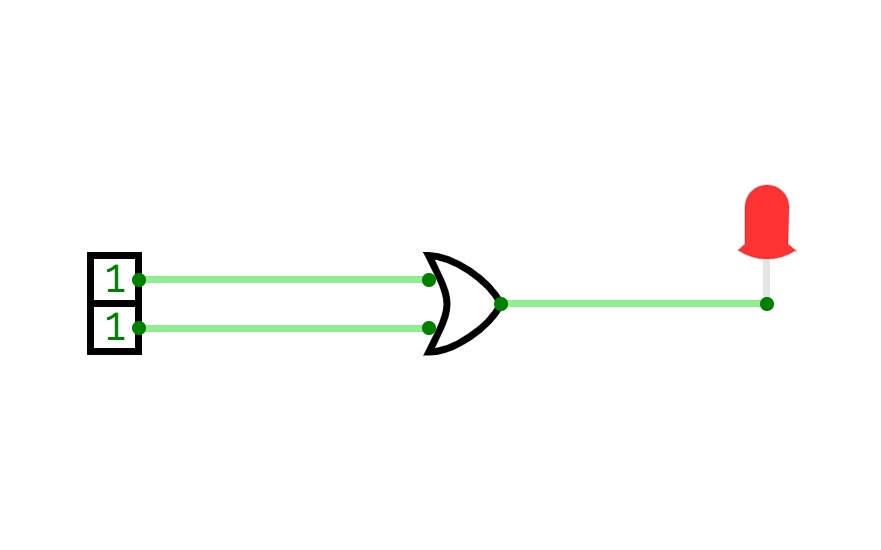

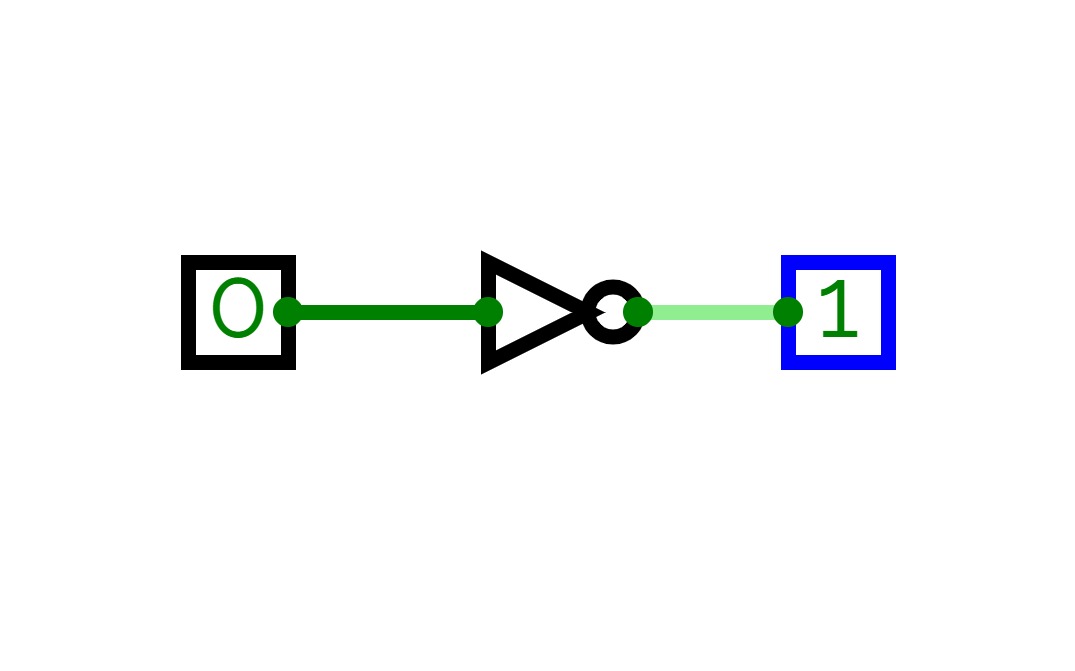

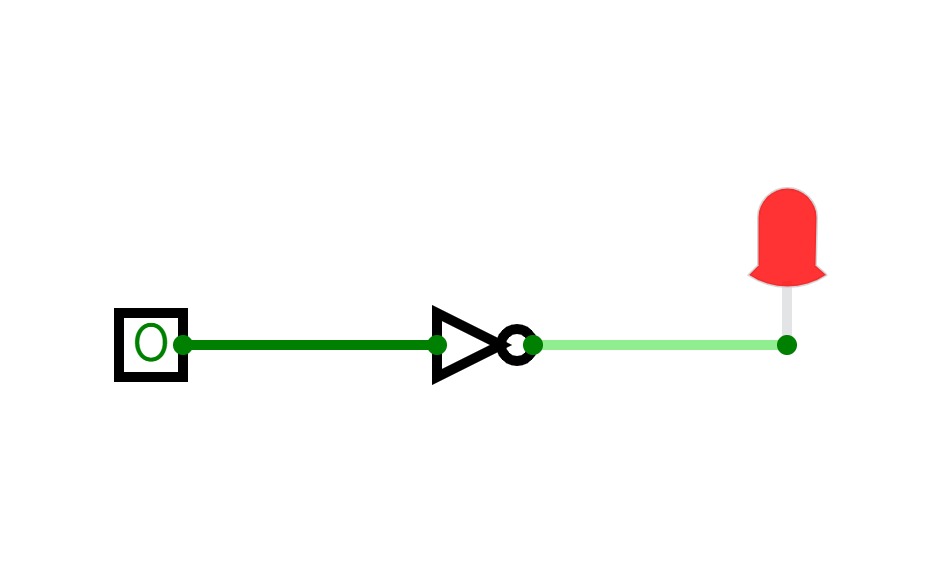

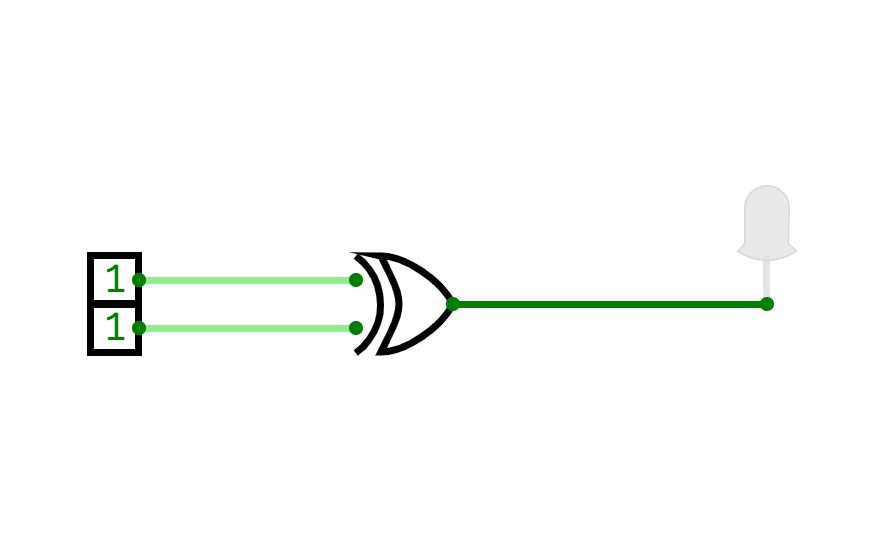

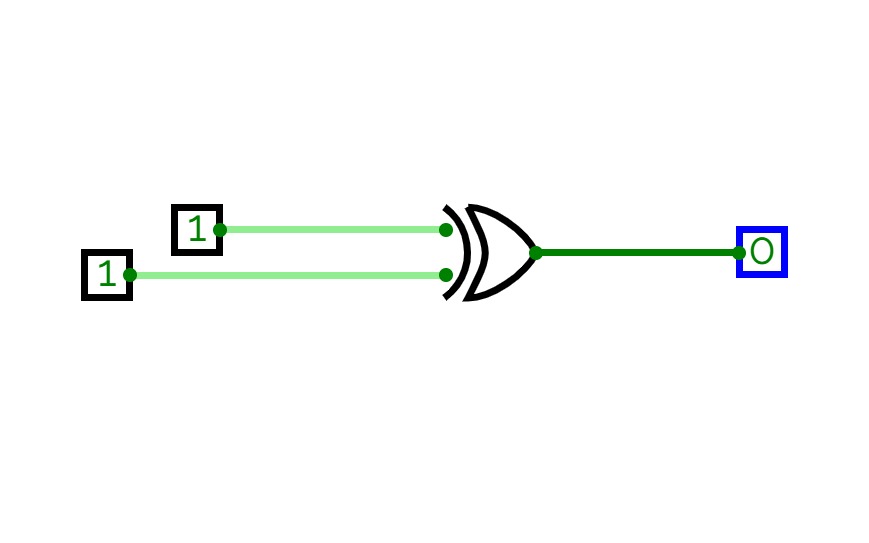

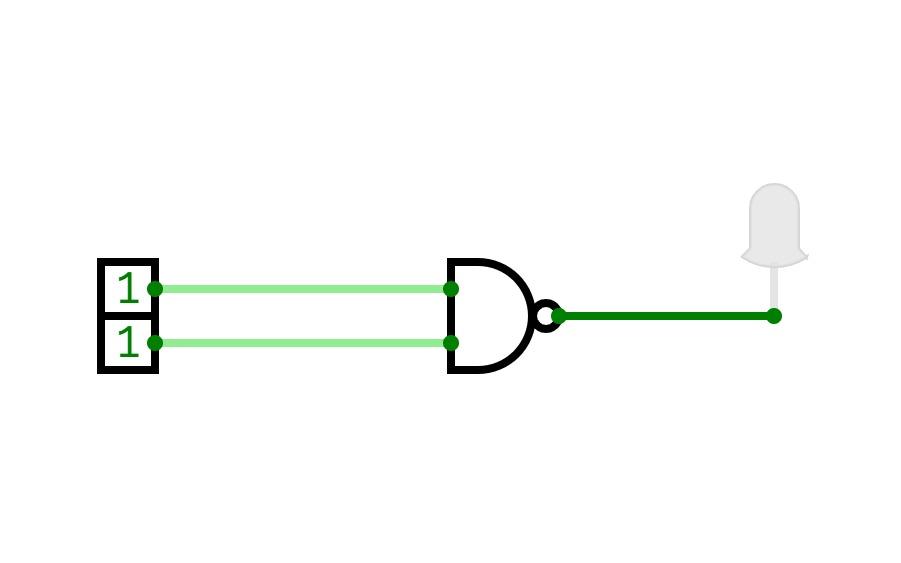

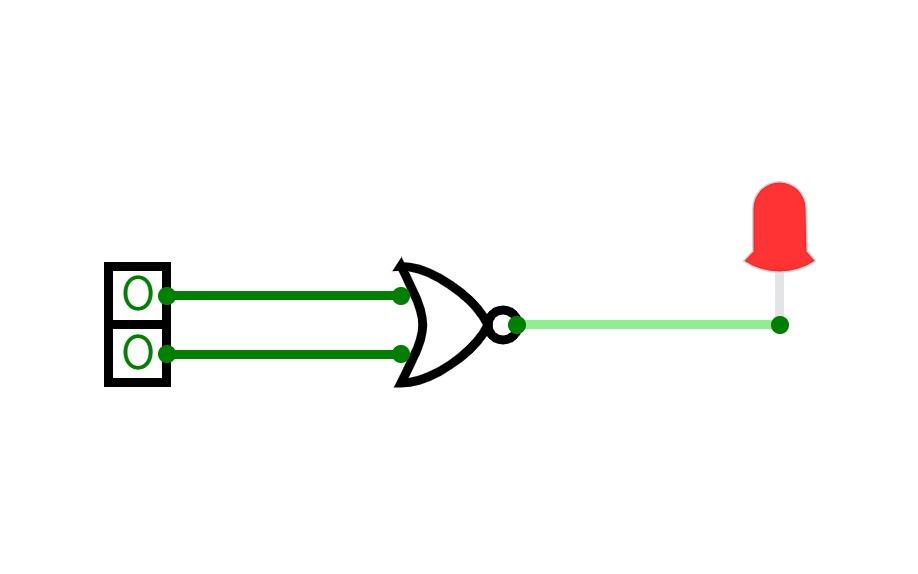

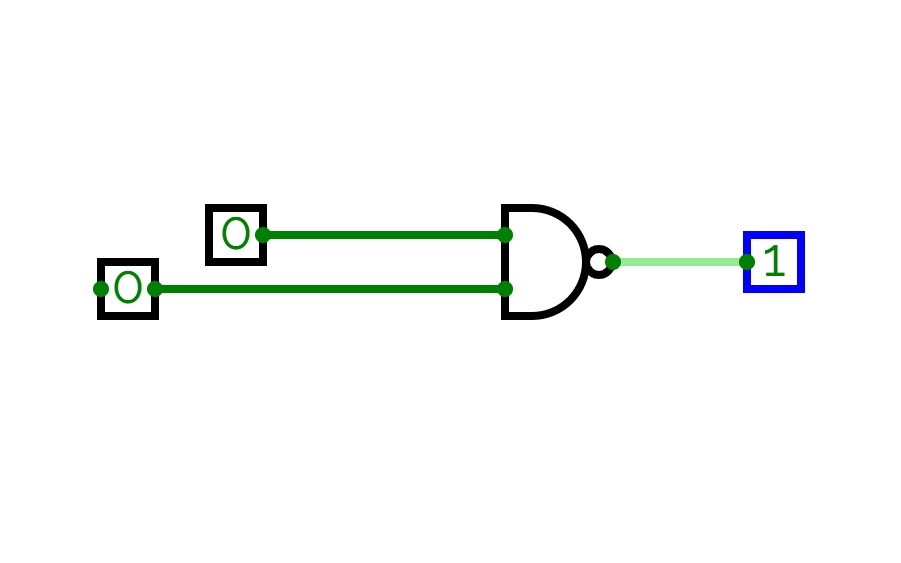

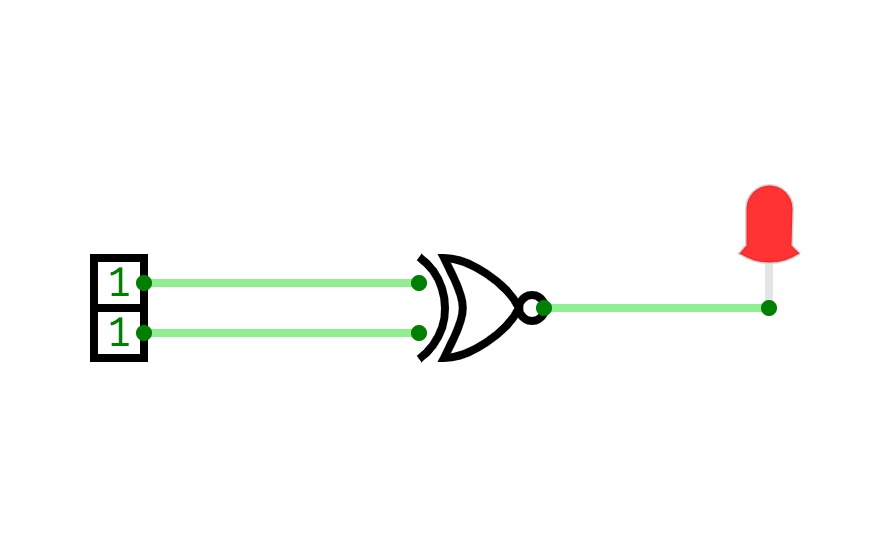

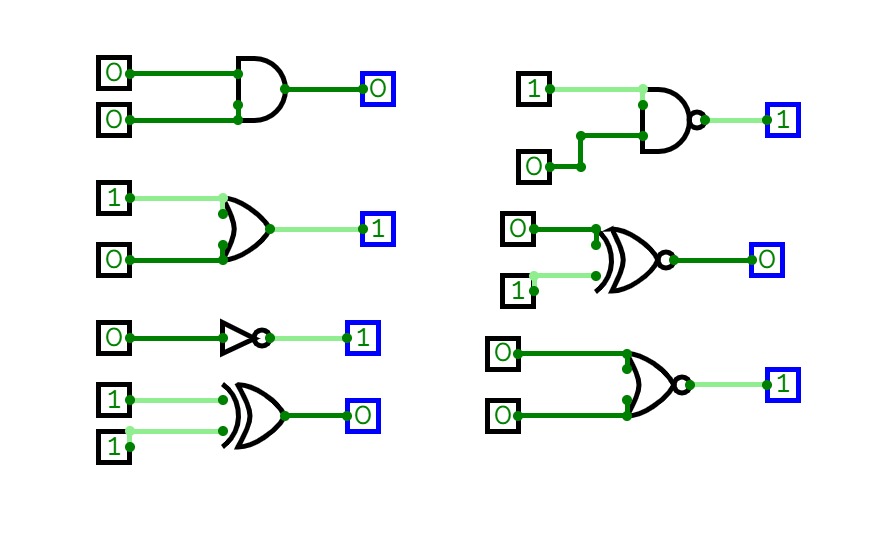

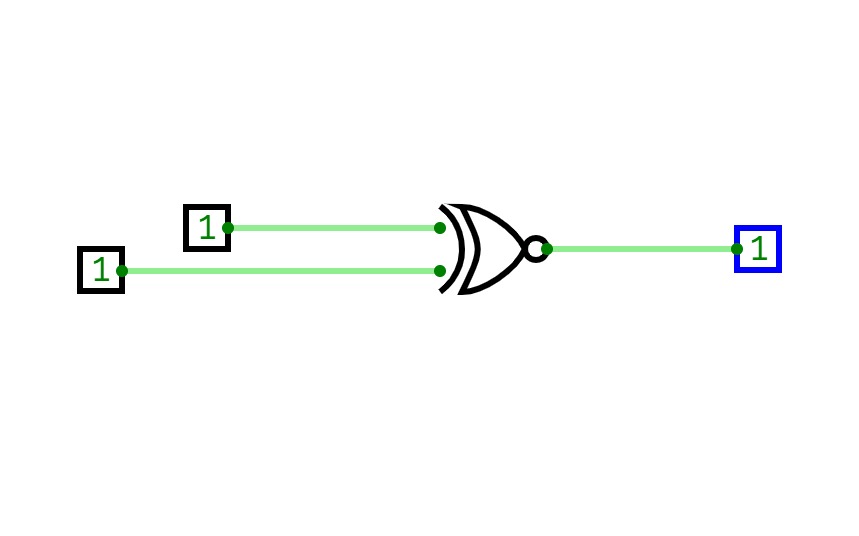

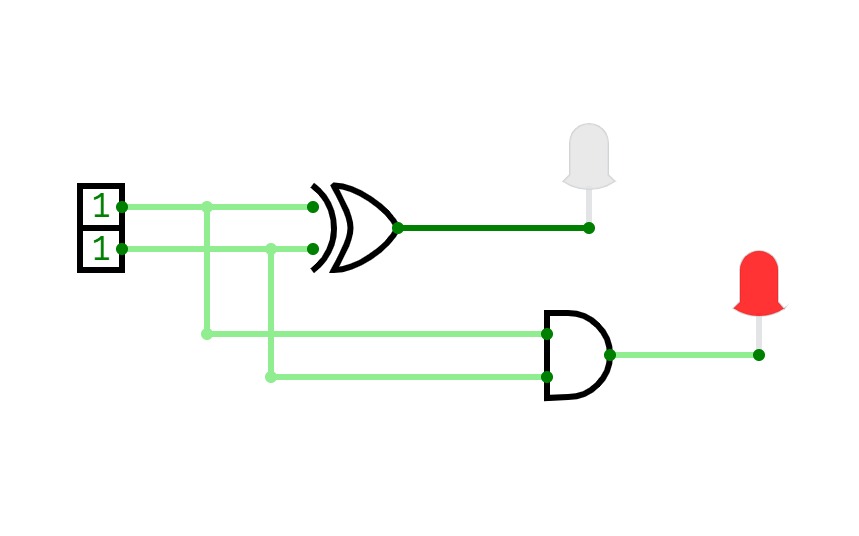

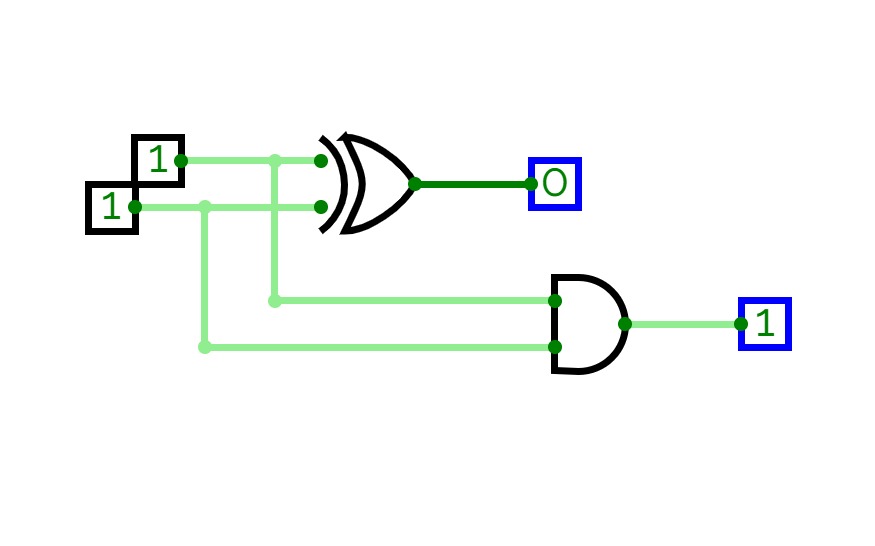

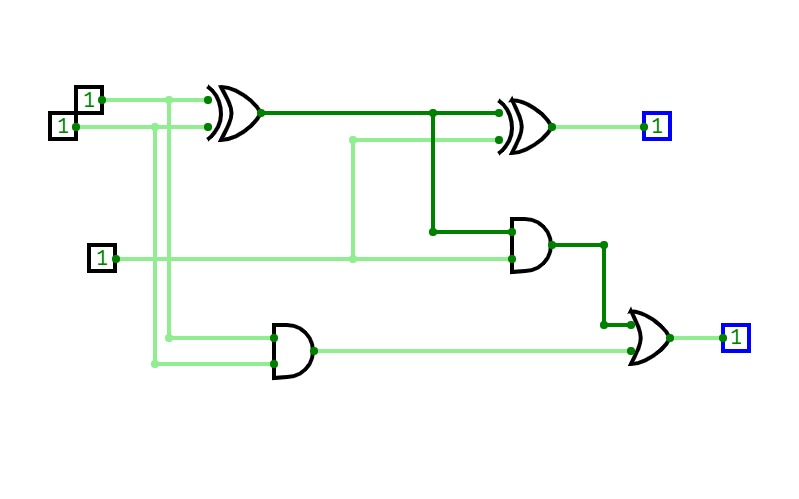

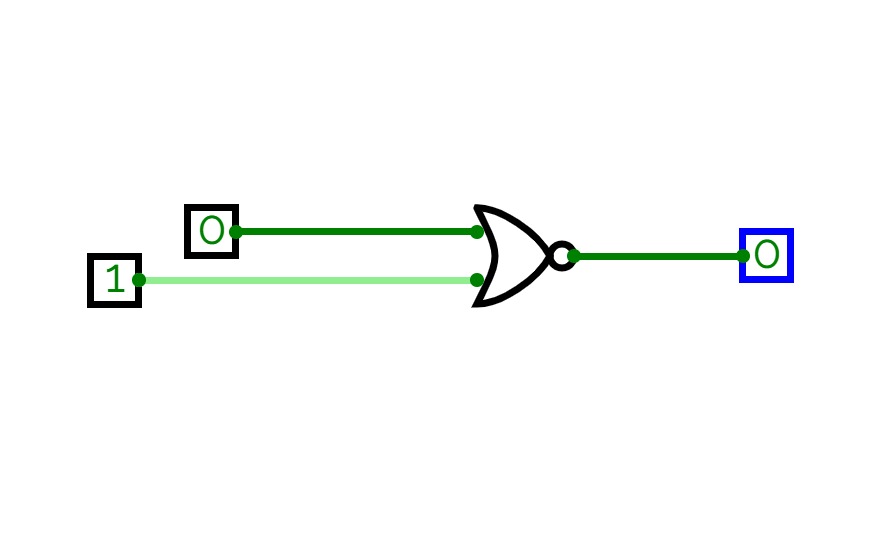

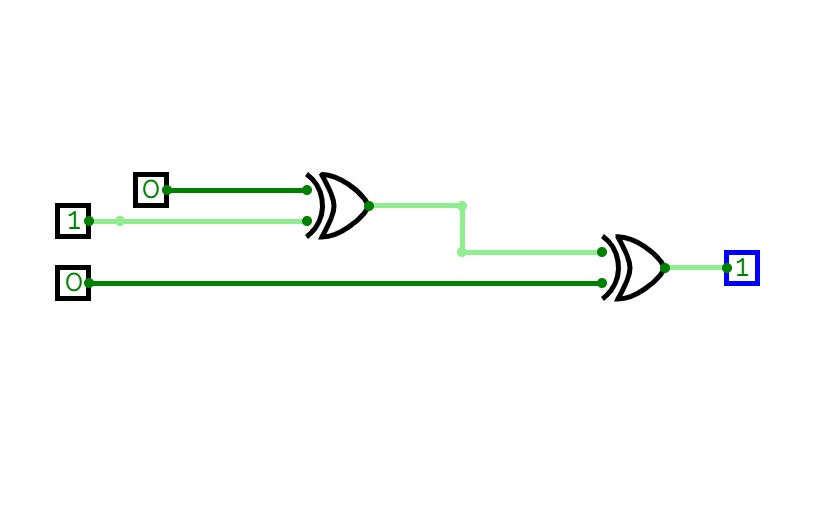

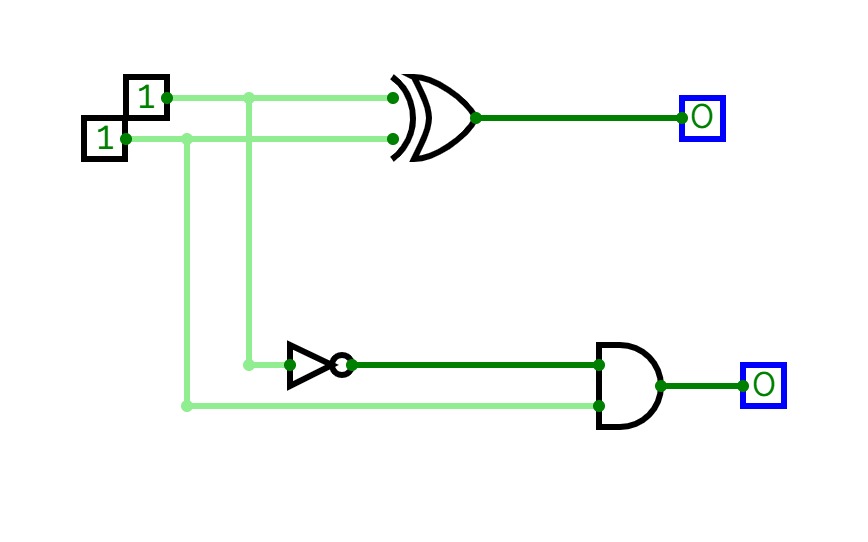

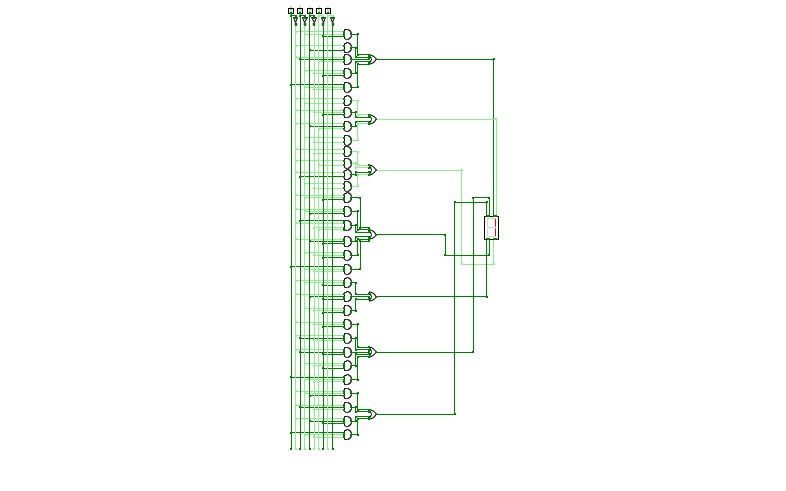

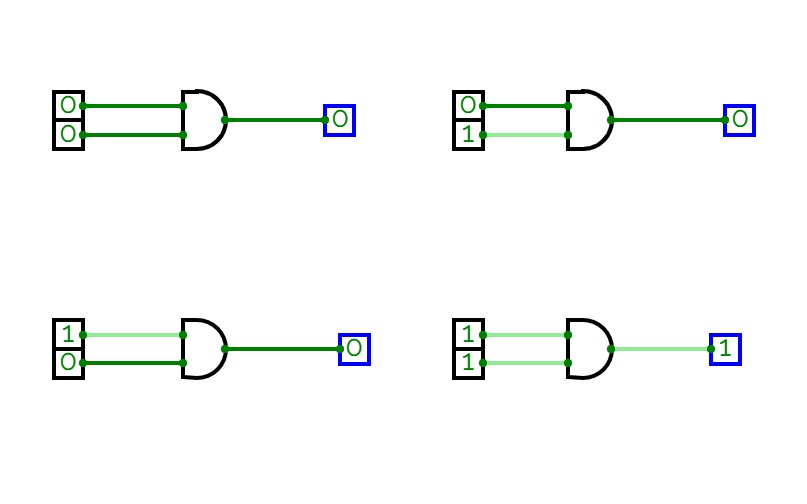

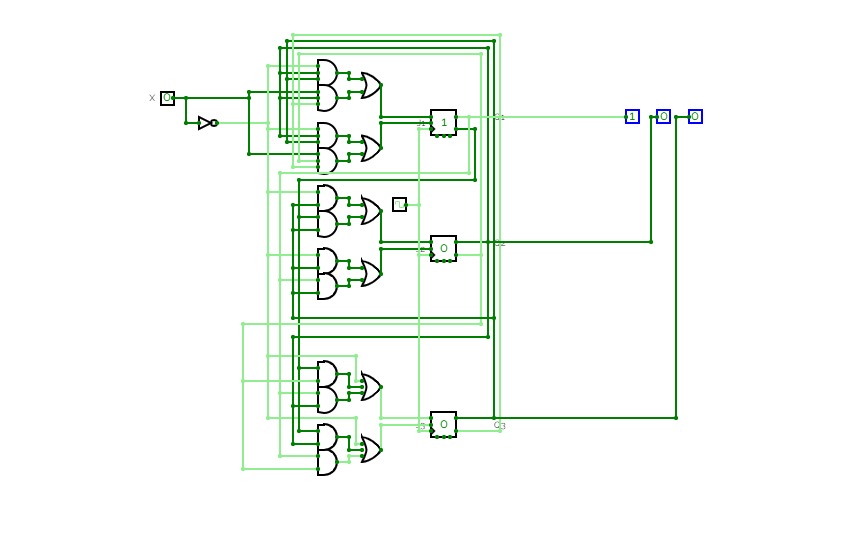

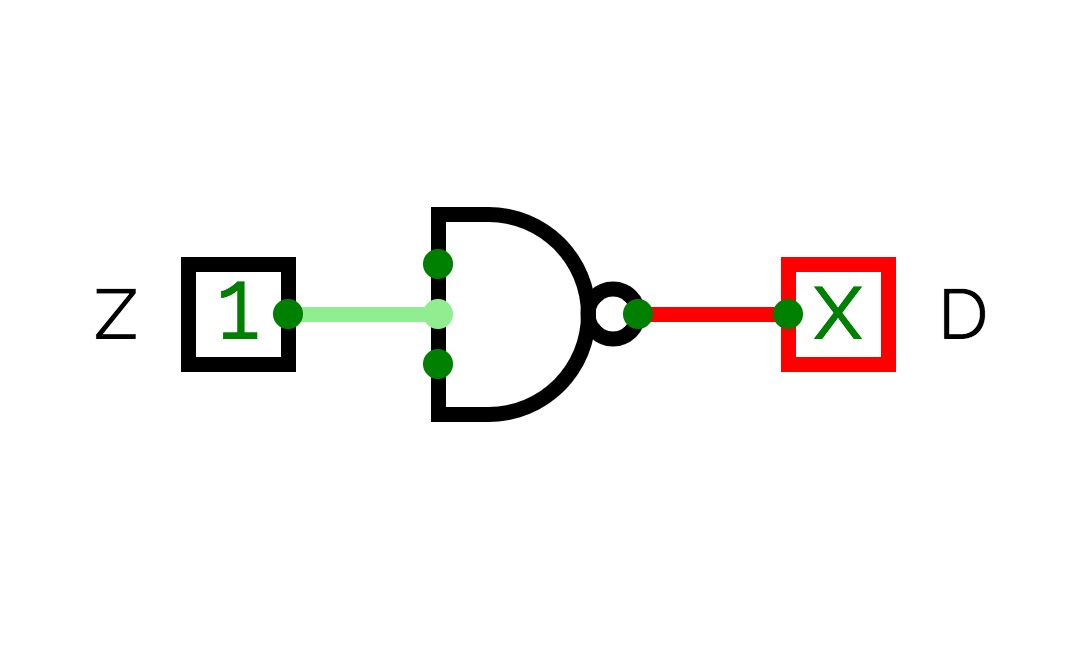

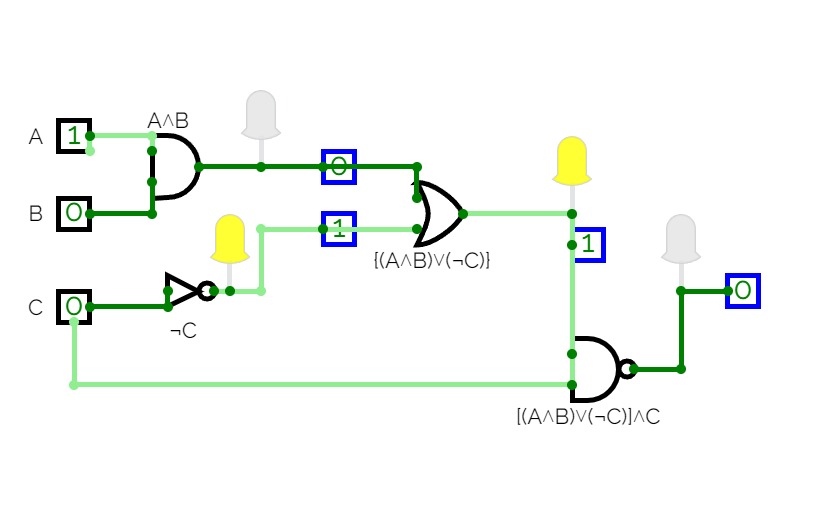

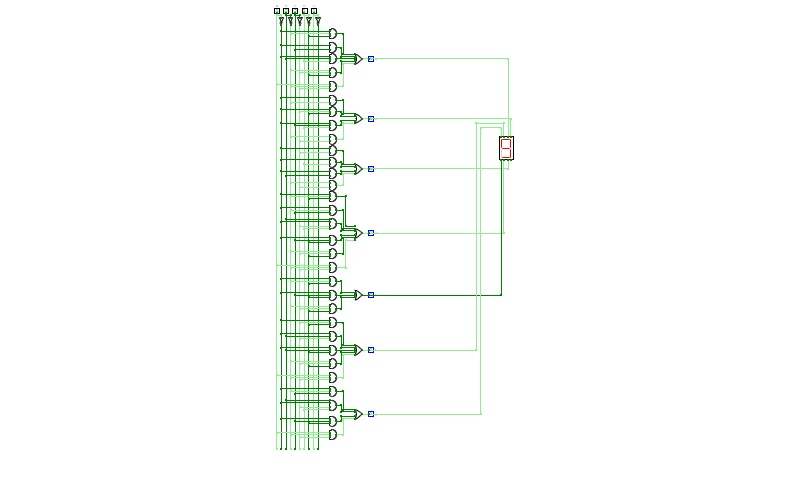

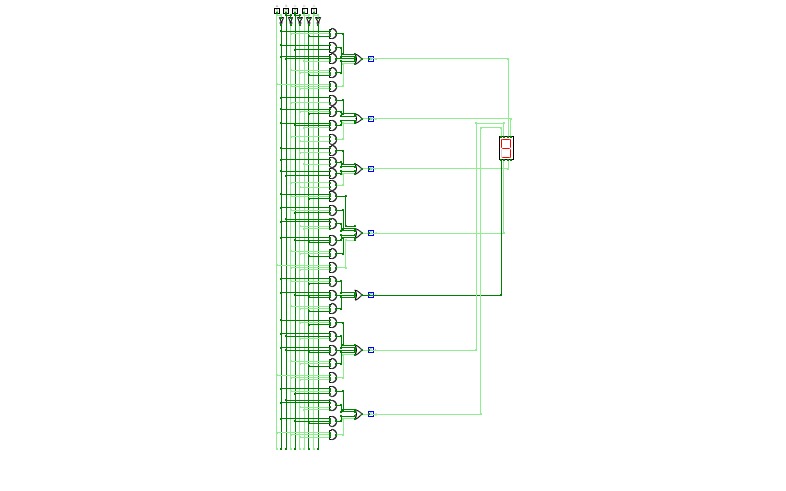

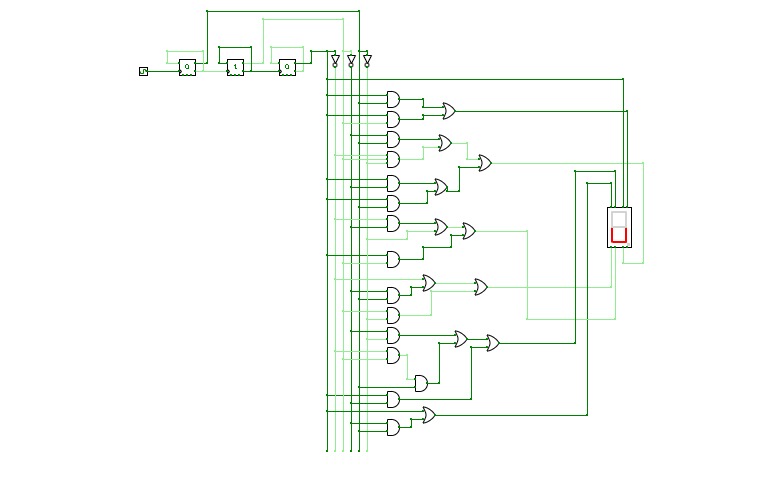

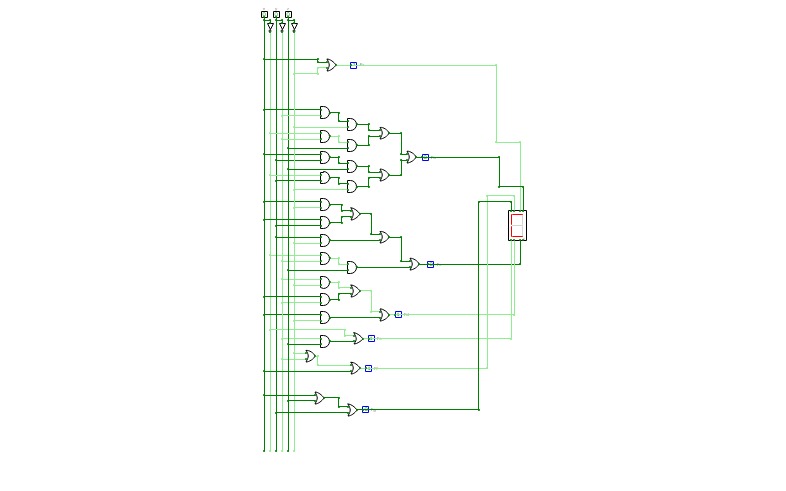

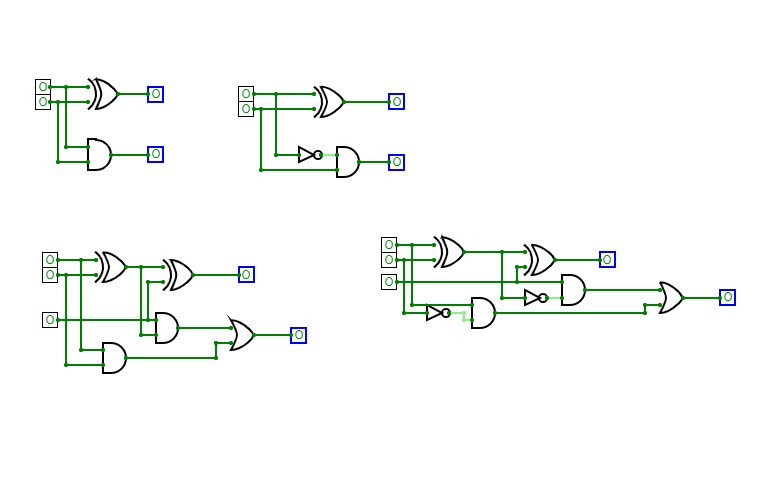

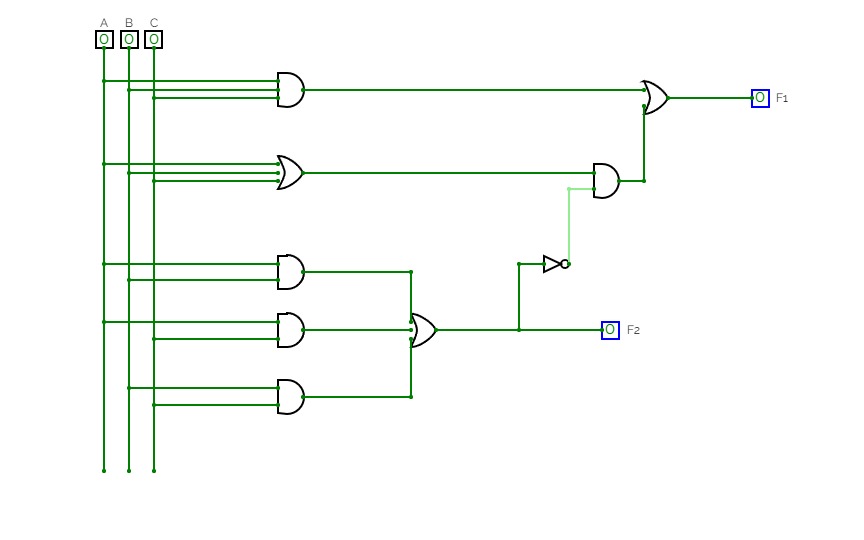

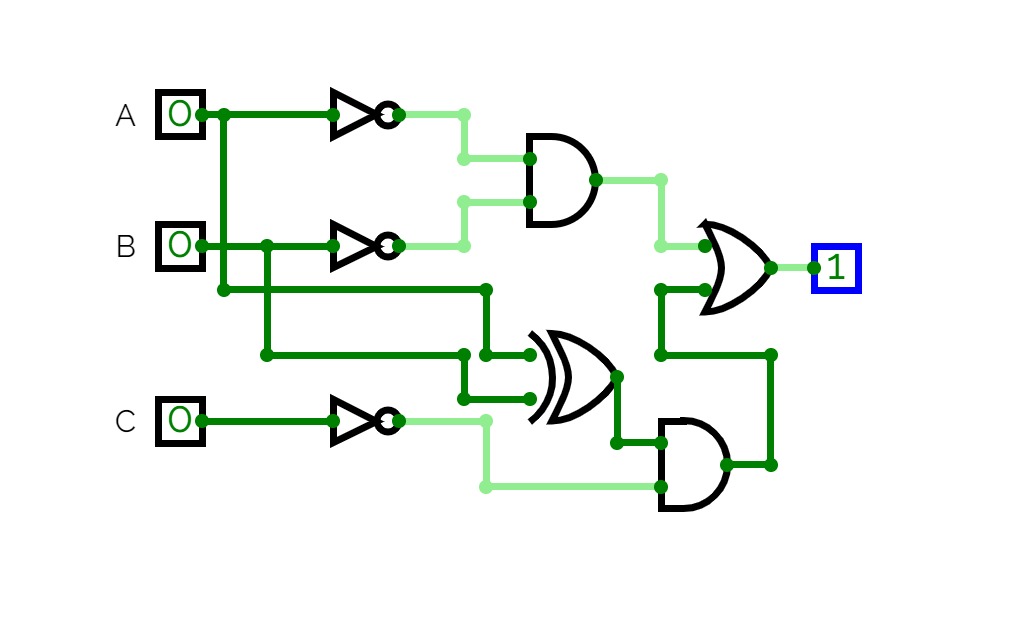

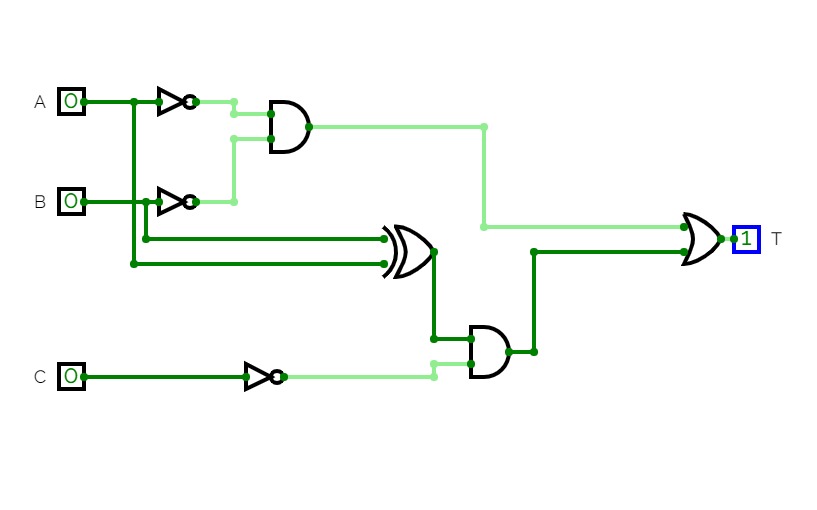

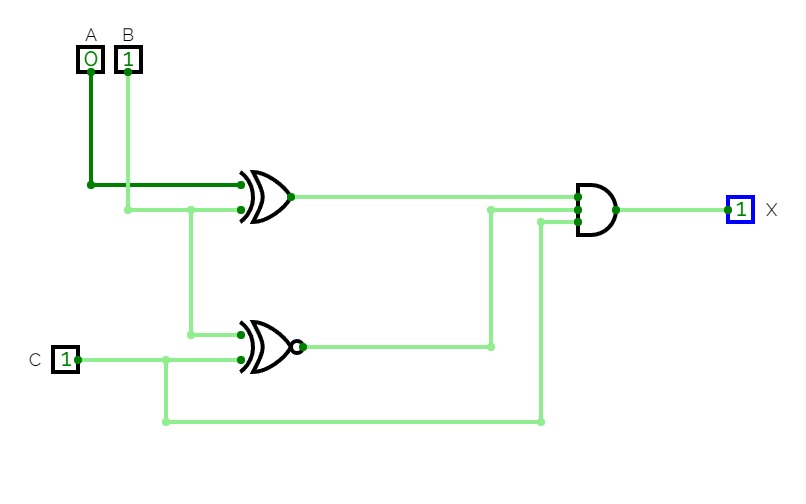

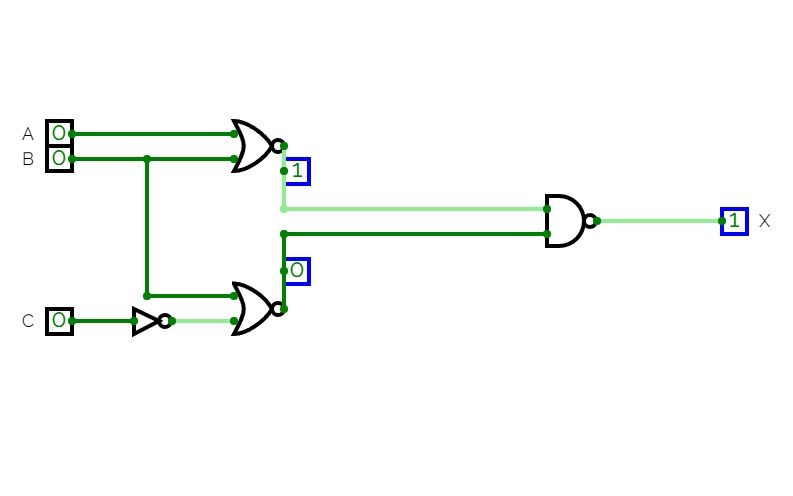

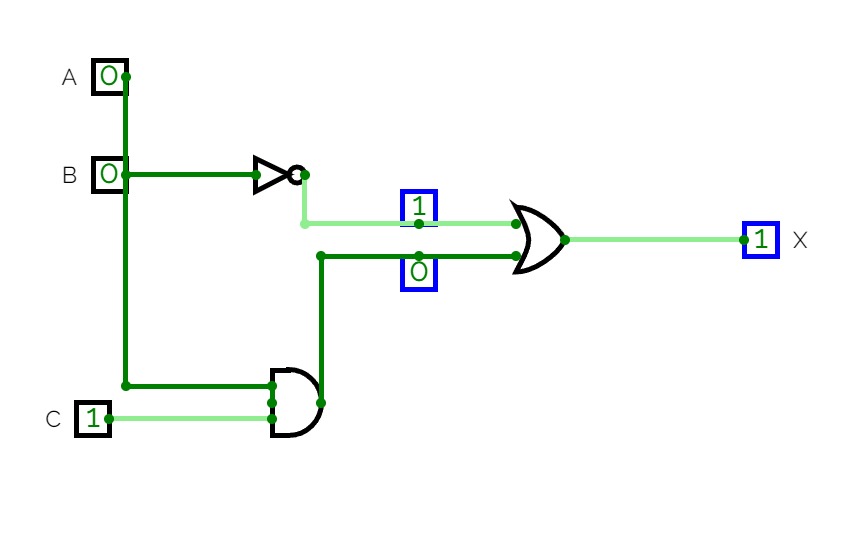

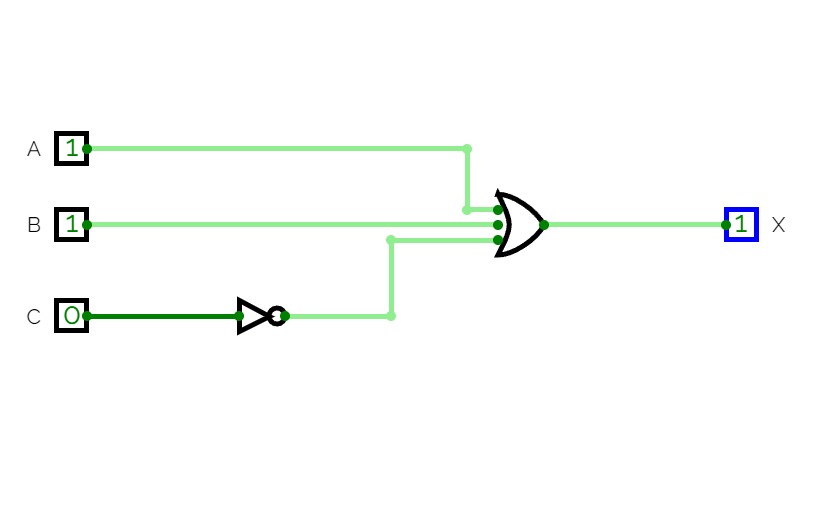

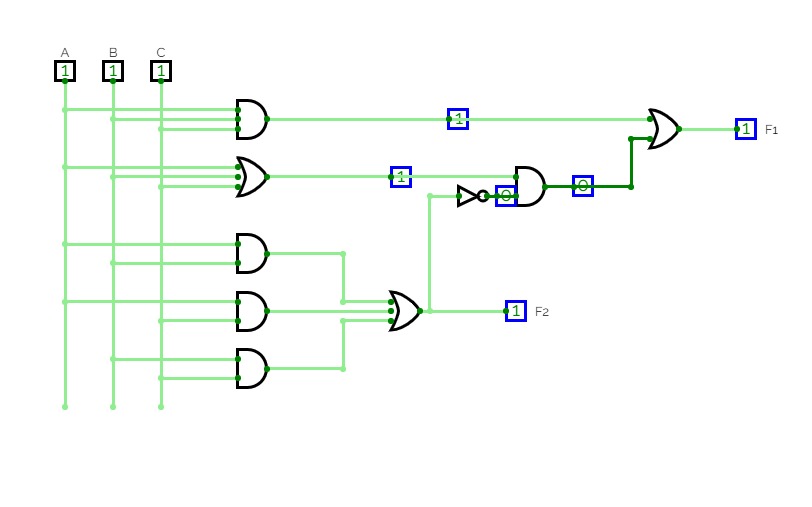

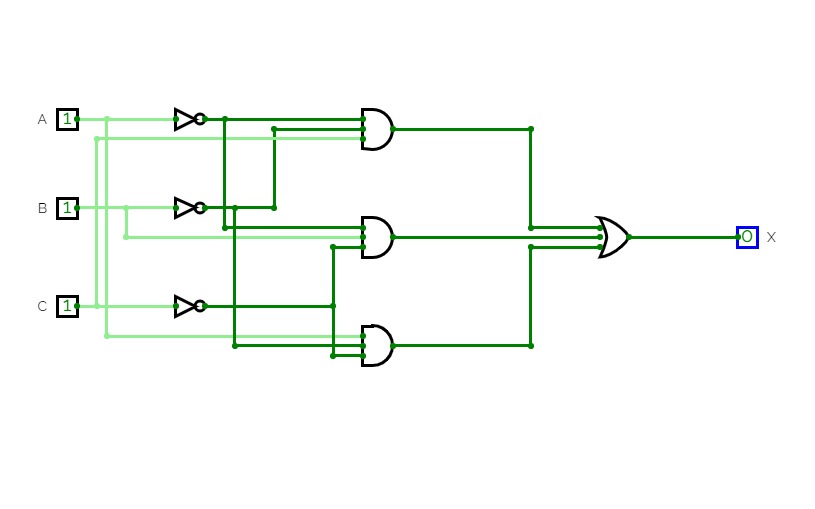

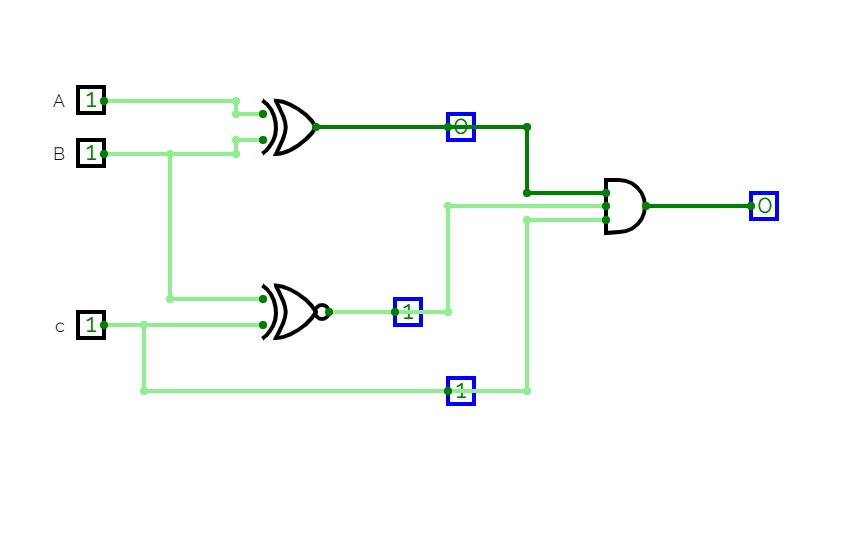

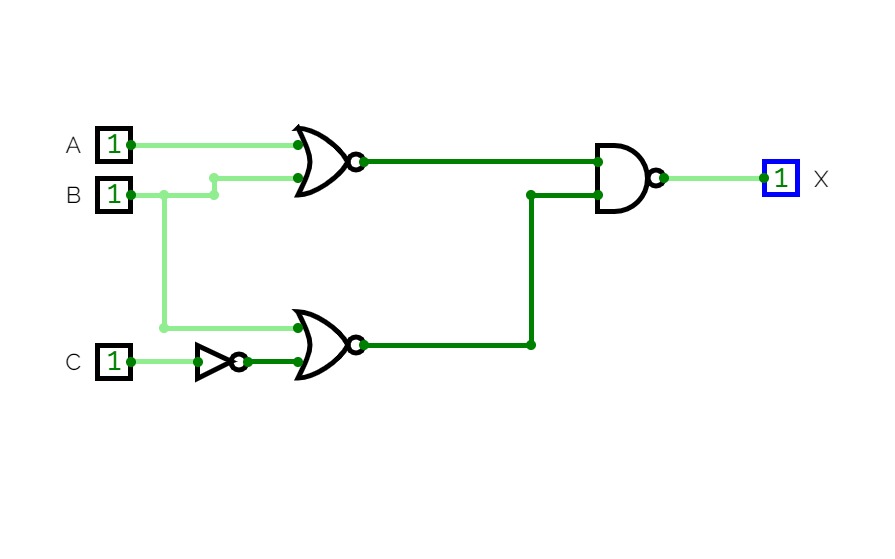

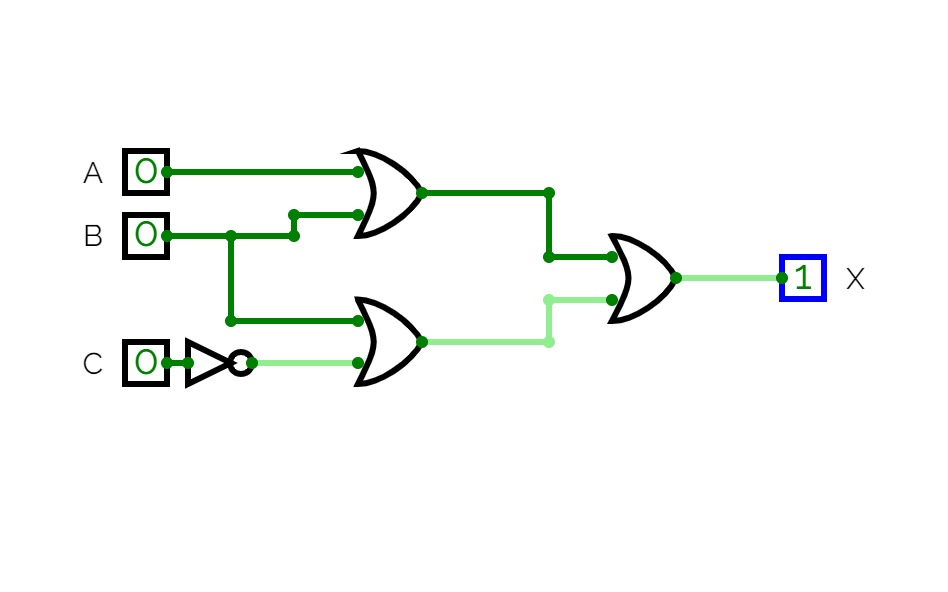

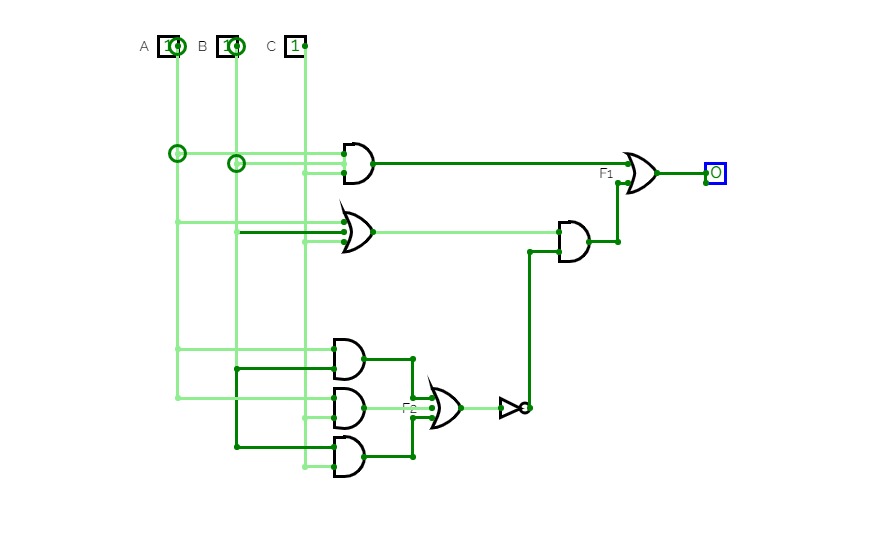

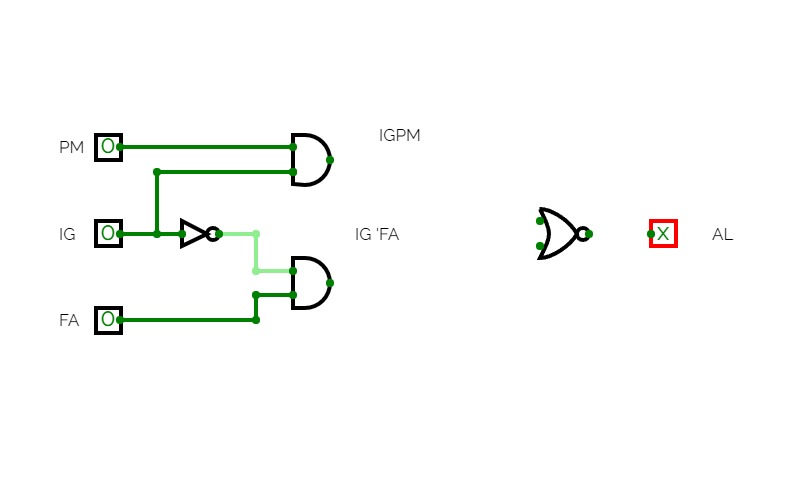

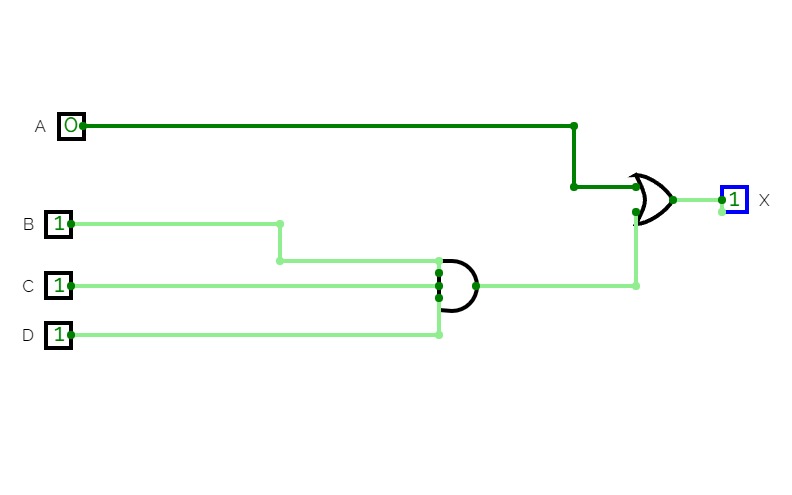

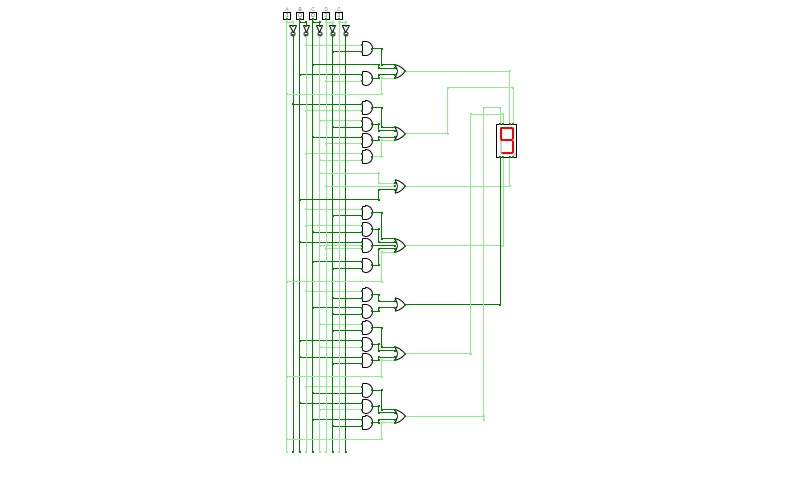

UN TANQUE CON TRES SENSORES N1, N2, N3 DE LLENADO, NECESITA EL DISEÑO DE UN CIRCUITO PARA SU EXCELENTE FUNCIONAMIENTO Y DESEMPEÑO PARA ESTO EL CLIENTE PIDE UN PAR DE MECANISMO PARA QUE EL DISPOSITIVO FUNCIONE COMO EL TIENE PREVISTO PRIMERO EL QUIERE QUE LA BOMBA TENGA UN ENCENDIDO Y APAGADO AUTOMÁTICO A TRAVÉS DEL CIRCUITO Y ESTO SE DARÁ CUANDO LOS SENSORES INFORMEN SI YA PASO O NO EL NIVEL DE ELLOS DE TAL MANERA QUE MAS SINTETIZADO SU FUNCIONAMIENTO ENCENDERA TANTO LA BOMBA COMO LA ALARMA SI: EL TANQUE ESTA TOTALMENTE VACIO LA ALARMA SE ENCENCERA INDICANDOLE AL USUARIO QUE HAY QUE LLENAR EL TANQUE, LA BOMBA SE ENCENDERA SI EL NIVEL DEL AGUA ESTA POR ENCIMA DE N1 Y DEBAJO DE N2 AL IGUAL QUE SI ESTA POR ENCIMA DE N1 Y N2 PERO POR DEBAJO DE N3 ESTO YA QUE EL TANQUE NO SE HA LLENADO COMPLETAMENTE Y LA ALARMA SE VOLVERA A ENCENDER CUANDO EL NIVEL DEL AGUA SEA MAYOR A LA UBICACION DE N1, N2 Y N3 DE TAL MANERA QUE EL USUARIO APAGE LA LLAVE QUE PERMITE QUE LA BOMBA SE ENCIENDA.