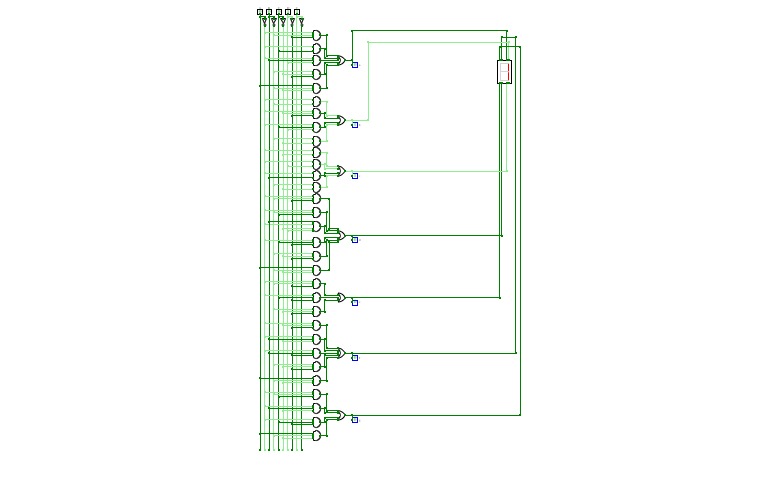

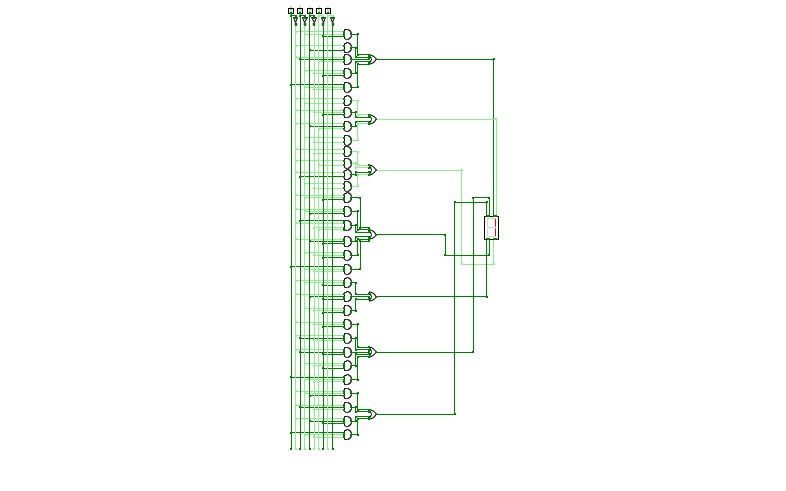

FF exercise "0101" Sequence Detector

FF exercise "0101" Sequence Detectormatching the expected output:

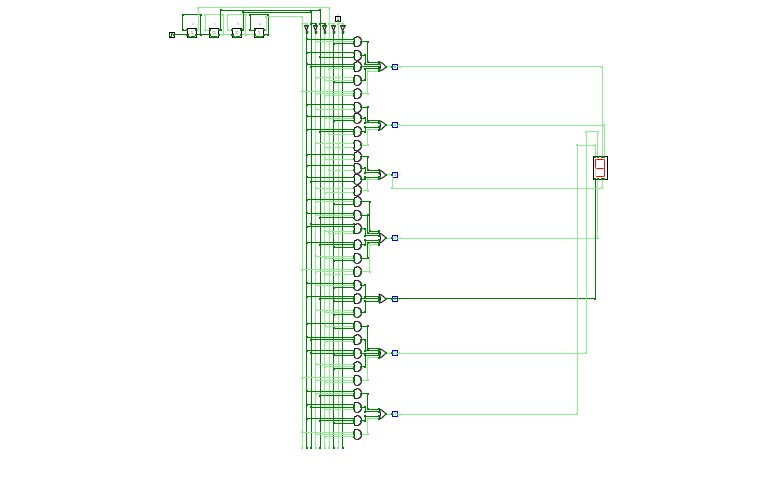

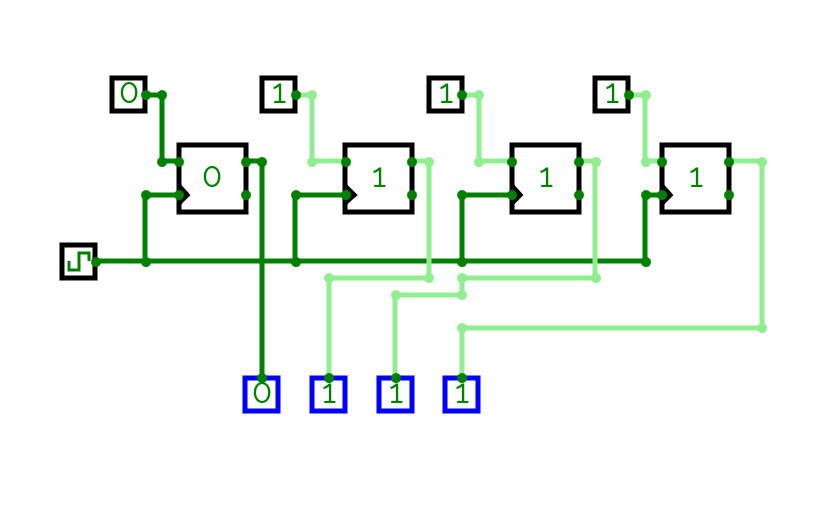

Johnson Counter

Johnson CounterDone by:

Saranga K. Mahanta

18-14-038

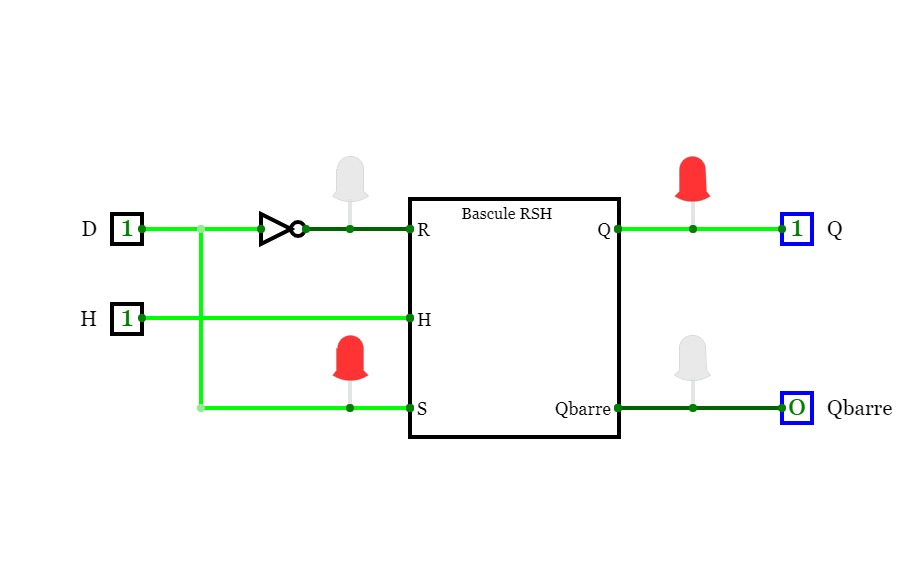

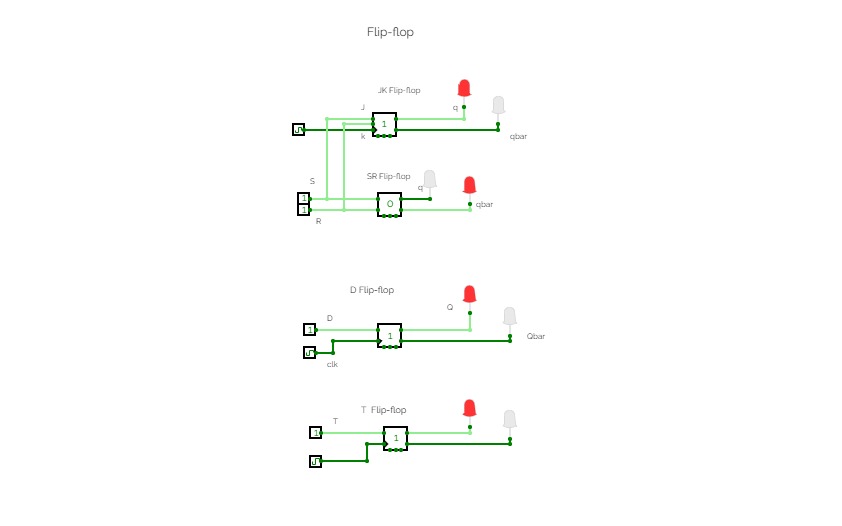

Quelques CLS

Quelques CLSDans ce projet, je construit quelques circuits logiques séquentiels:

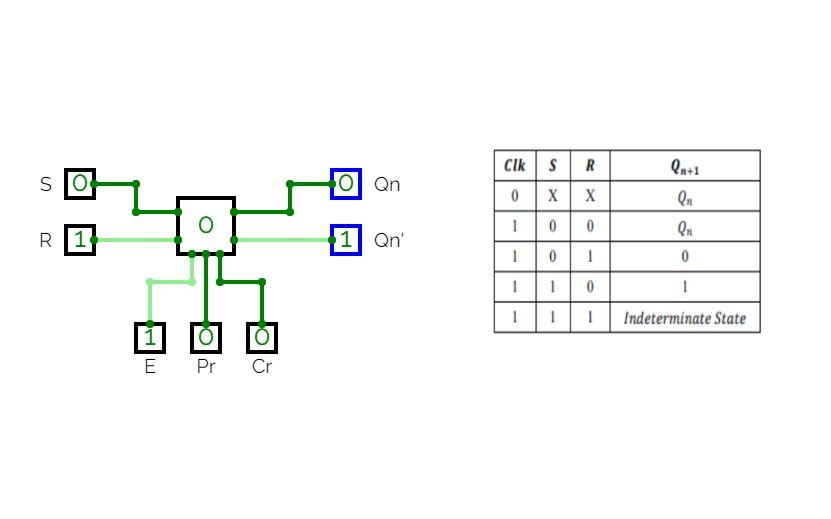

- Bascule RS

- Bascule RSH (syncnhrone)

- Bascule D

- Bascule D synchrone

- Bascule JK

- Bascule K=JK synchrone

- Bascule D flipflop

- Registre

Devoir 3 (bascules)

Devoir 3 (bascules)dans ce projet j'édite les circuits logiques :

bascule RS

bascule D

registre

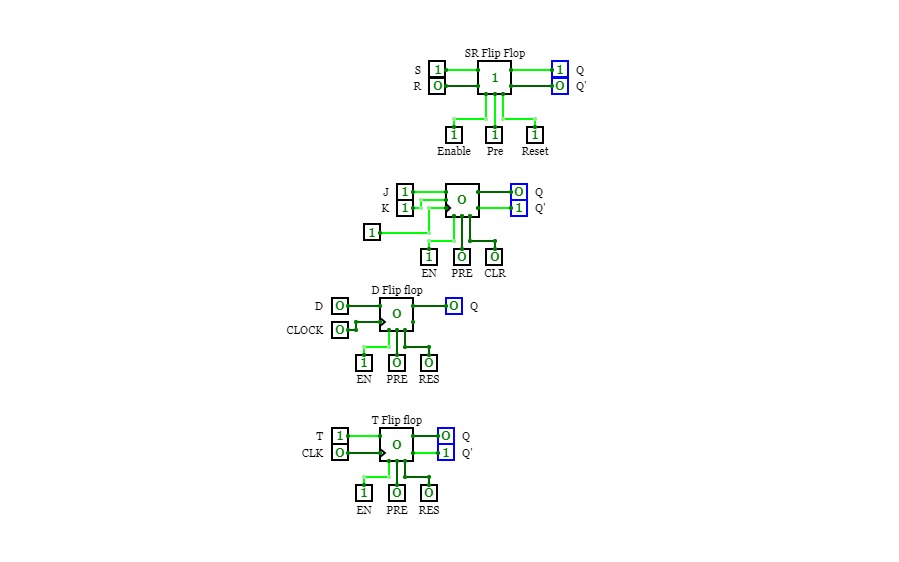

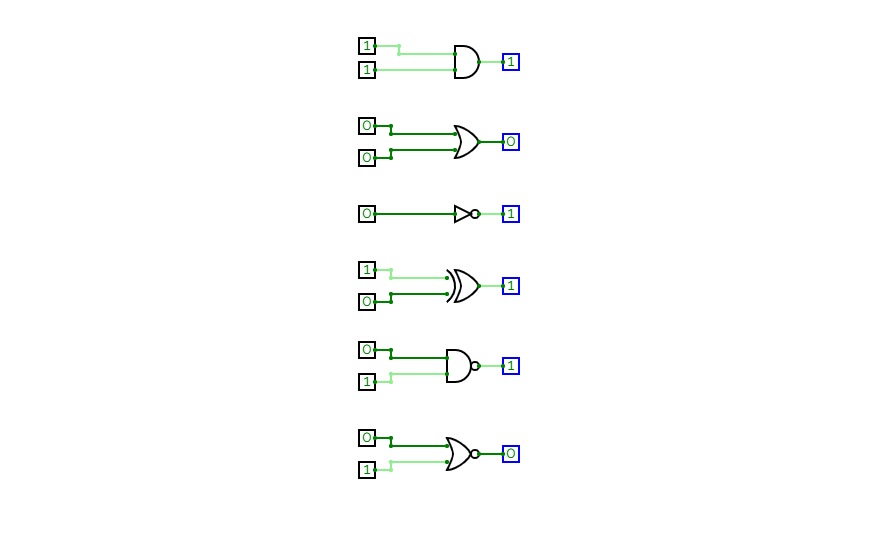

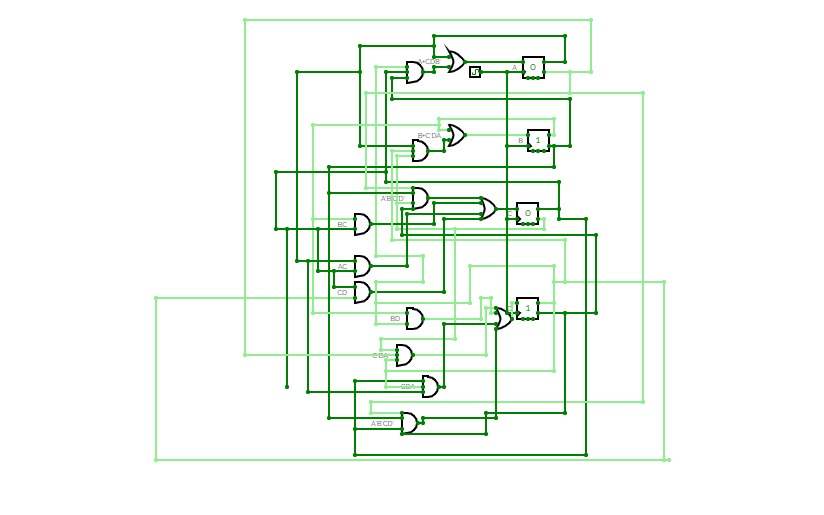

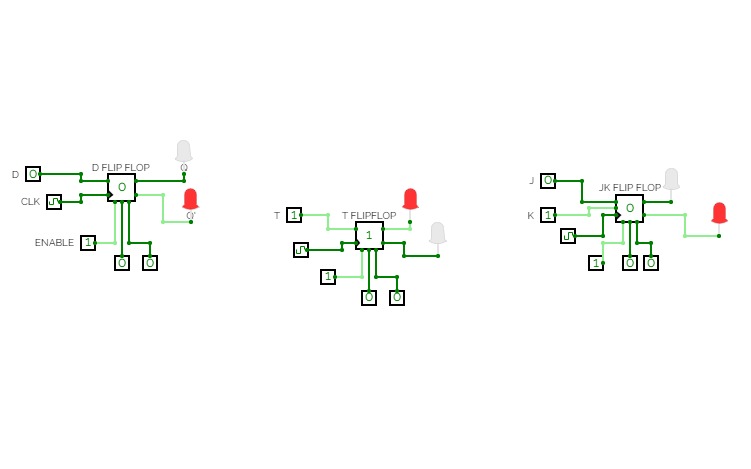

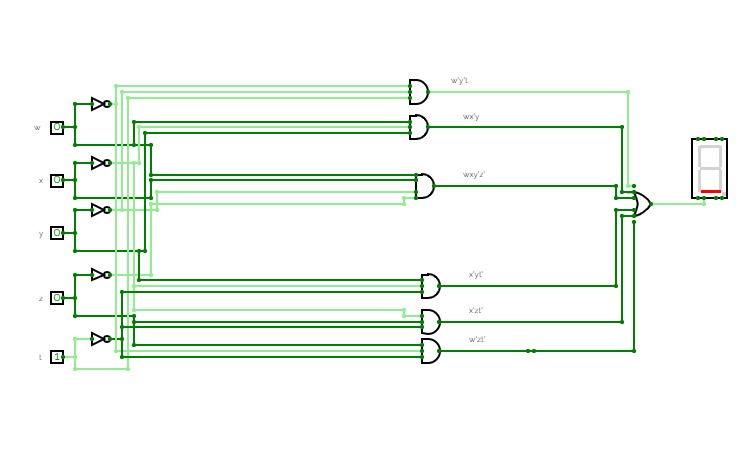

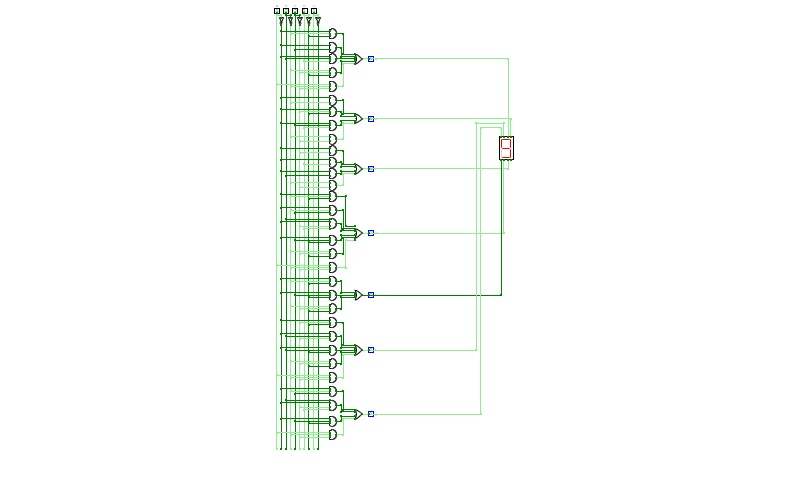

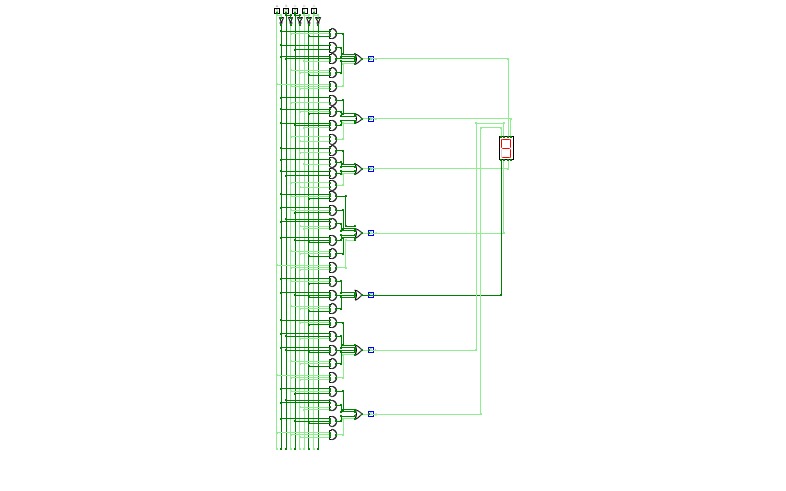

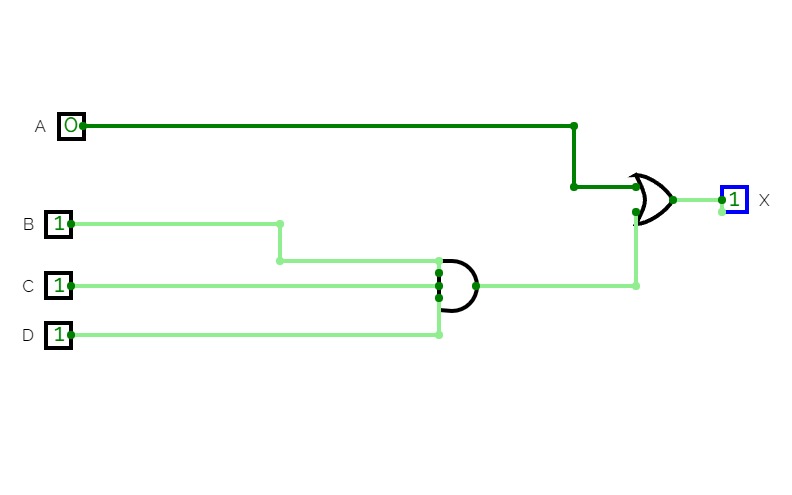

Flip Flop Verifications

Flip Flop VerificationsDLD Practical assignment Hana Hesham T 36 52-2395

DLD Practical assignment Hana Hesham T 36 52-2395T flip flop equation for A=A+CDB'

T flip flop equation for B=B+C'DA

T flip flop equation for C=A'B'C'D'+BC+AC+CD

T flip flop equation for D=C'DA'+BD+CDA+A'B'CD'

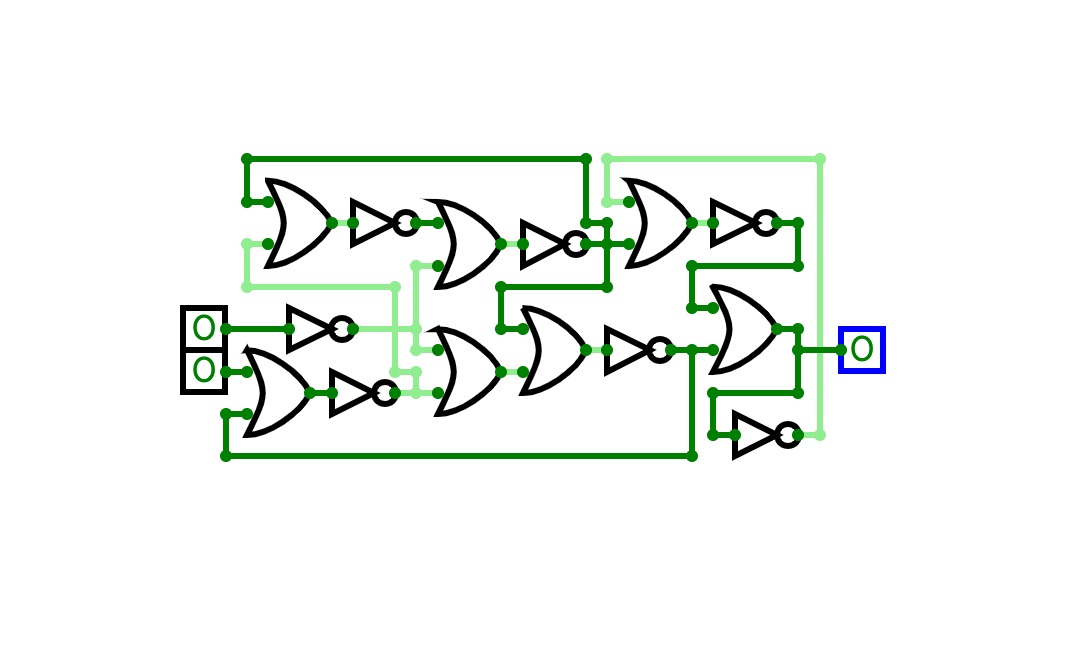

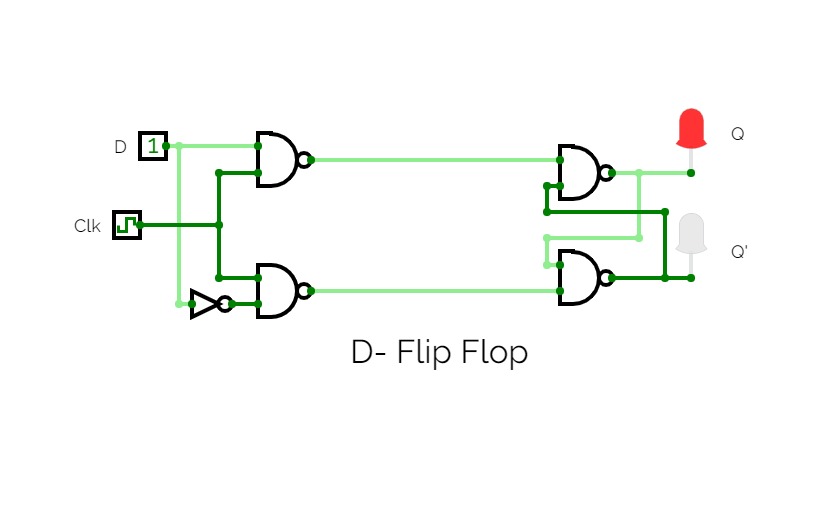

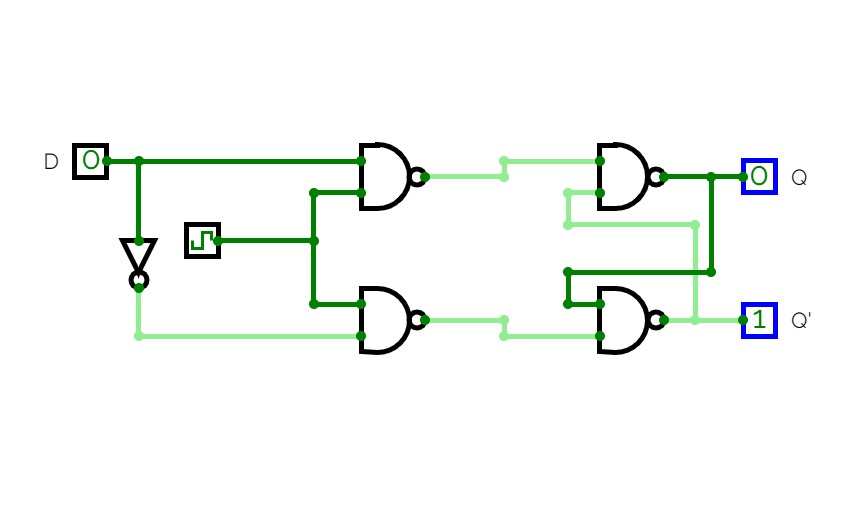

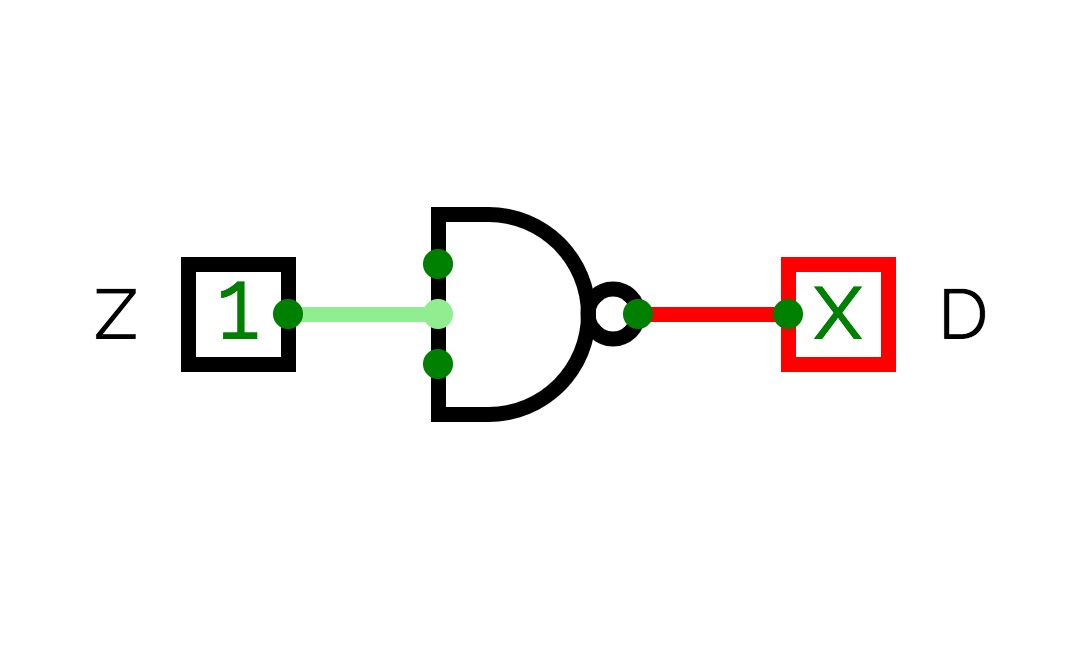

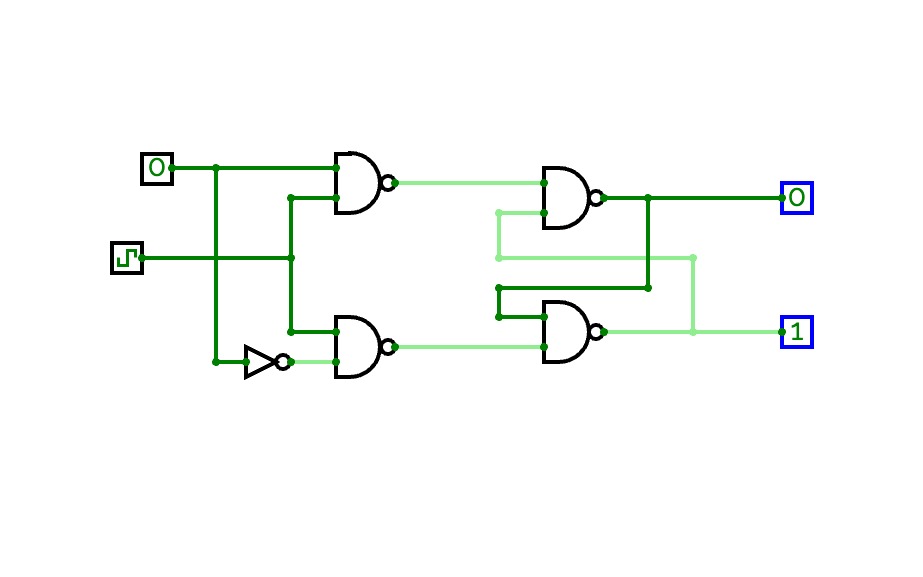

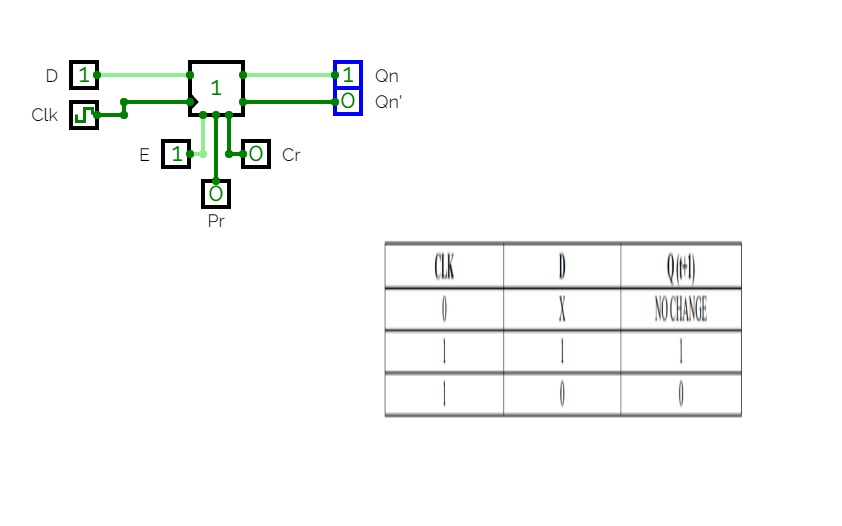

D Flip Flop

D Flip FlopD Flip Flop made from NOT and OR gates

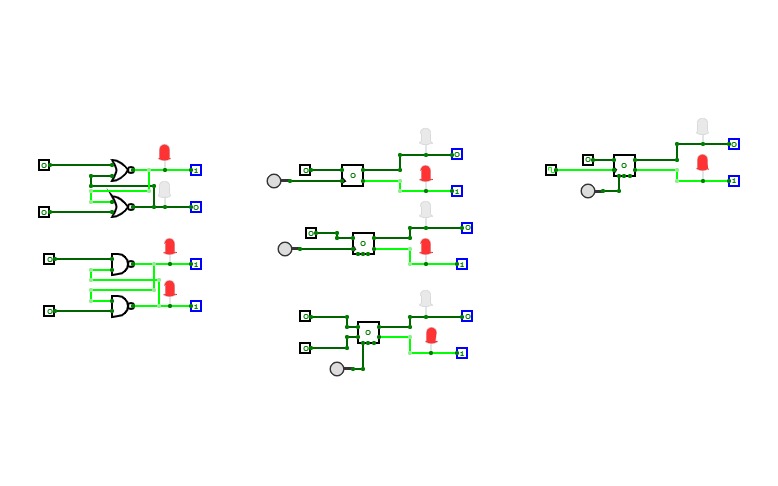

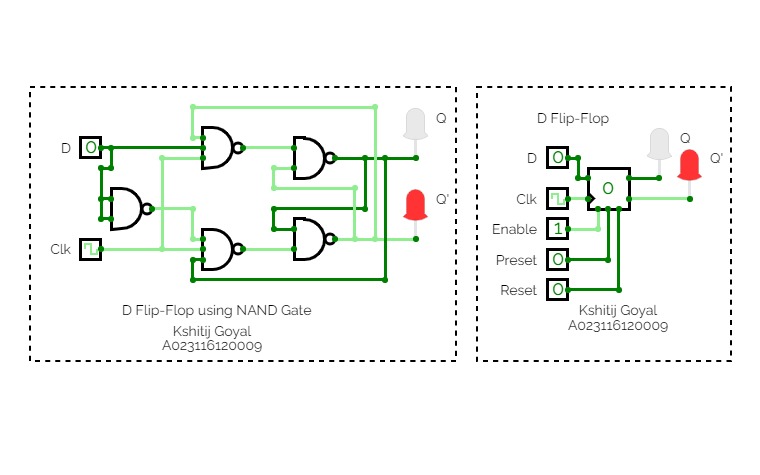

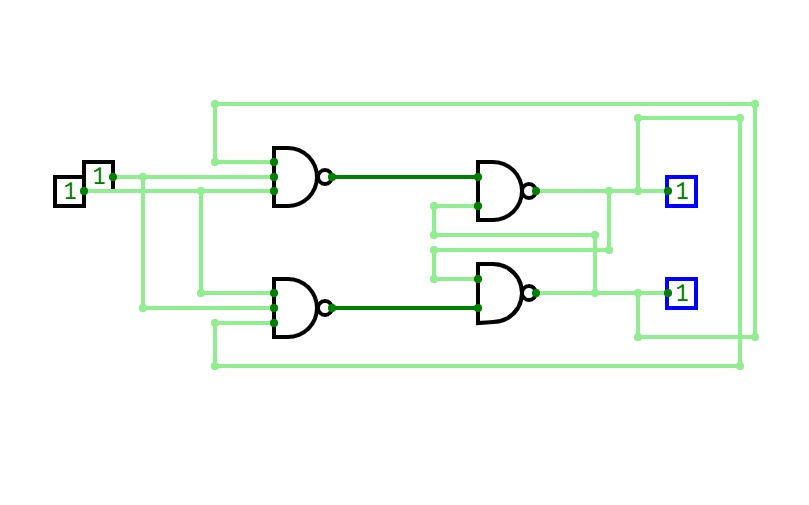

Flip Flop Using NAND GATE

Flip Flop Using NAND GATEFlip Flop Using NAND GATE

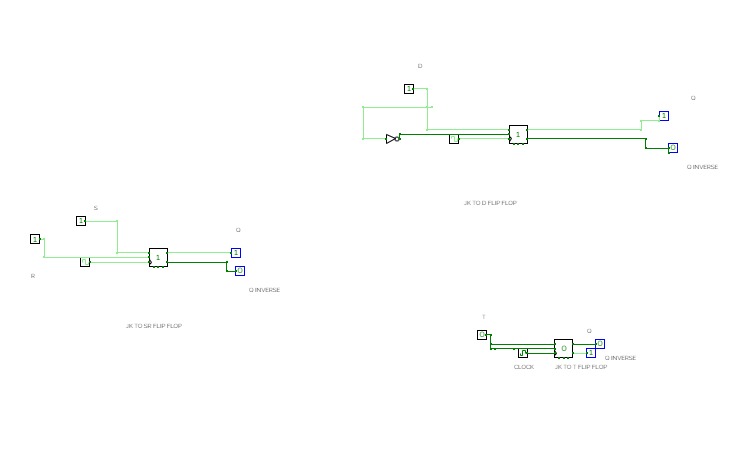

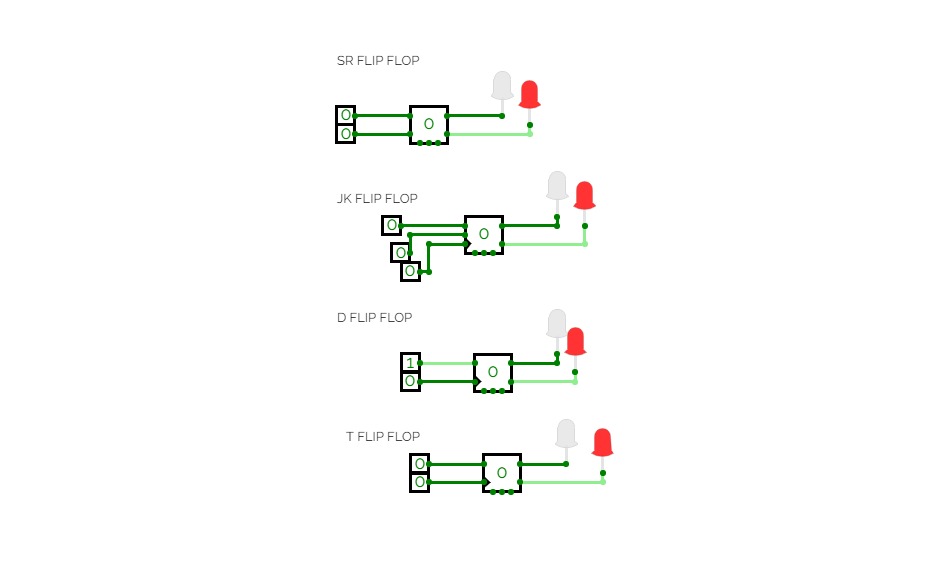

SR, JK, D, T Flip Flop

D- Flip Flop by Souvik Ghosh

D- Flip Flop by Souvik GhoshFLIP FLOPS

FLIP FLOPSD flip flop

D flip flopLAB 3

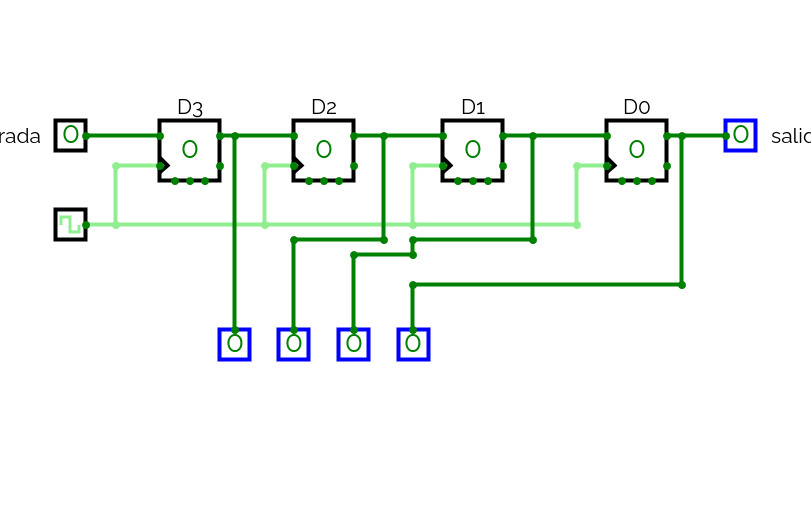

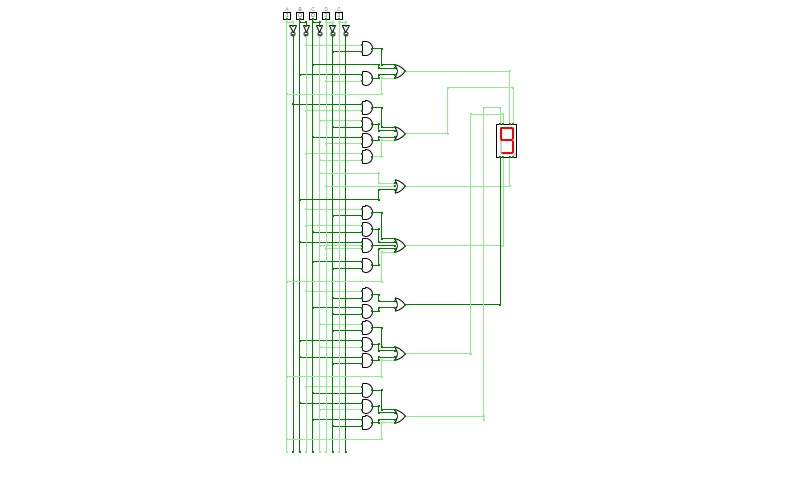

LAB 3RegistroD

RegistroDRegistro de almacenamiento realizado con biestables D

regitroDdes

regitroDdesRegistro de desplazamiento realizado con biestables D

Untitled

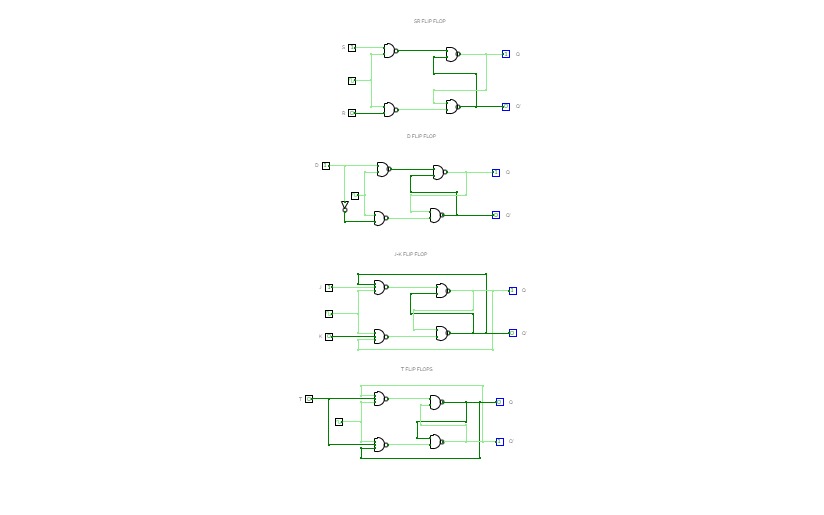

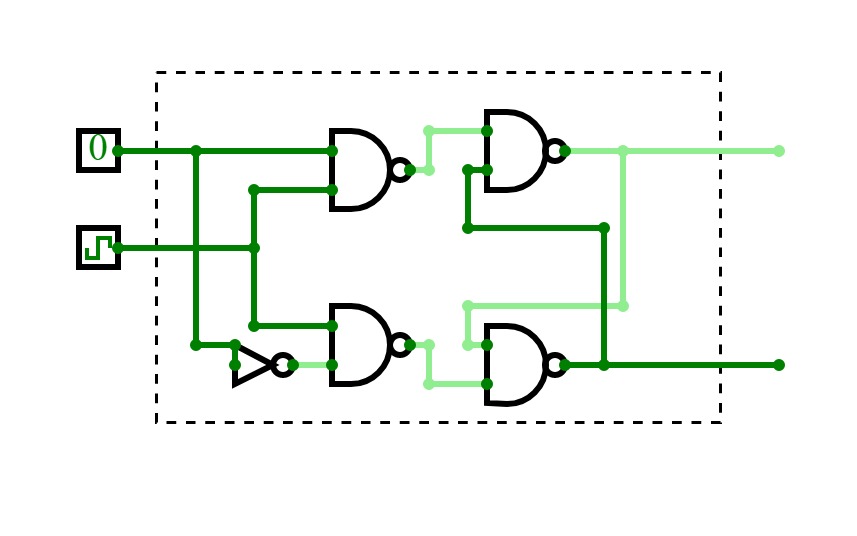

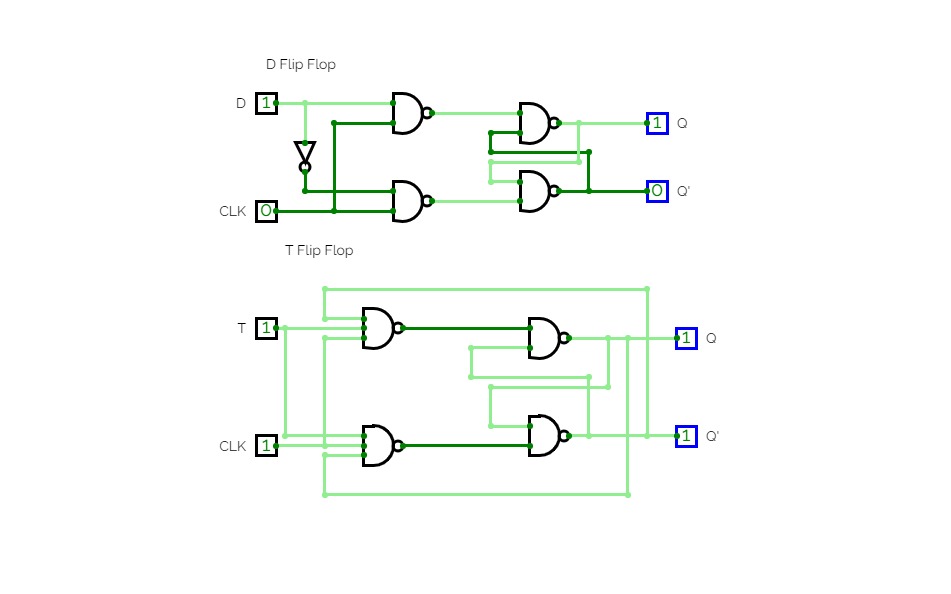

UntitledAssignment-5: Flip-Flops using NAND and NOT Gates

Assignment-5: Flip-Flops using NAND and NOT GatesDescription:

1) Implement, truth table and generate waveform

2) D, T, SR, JK- latch using NAND and NOR gates

3) D, T, SR, JK - FF using NAND and NOR gates

4) D-FF using SR-FF

5) Master-slave JK-FF using NAND Gate