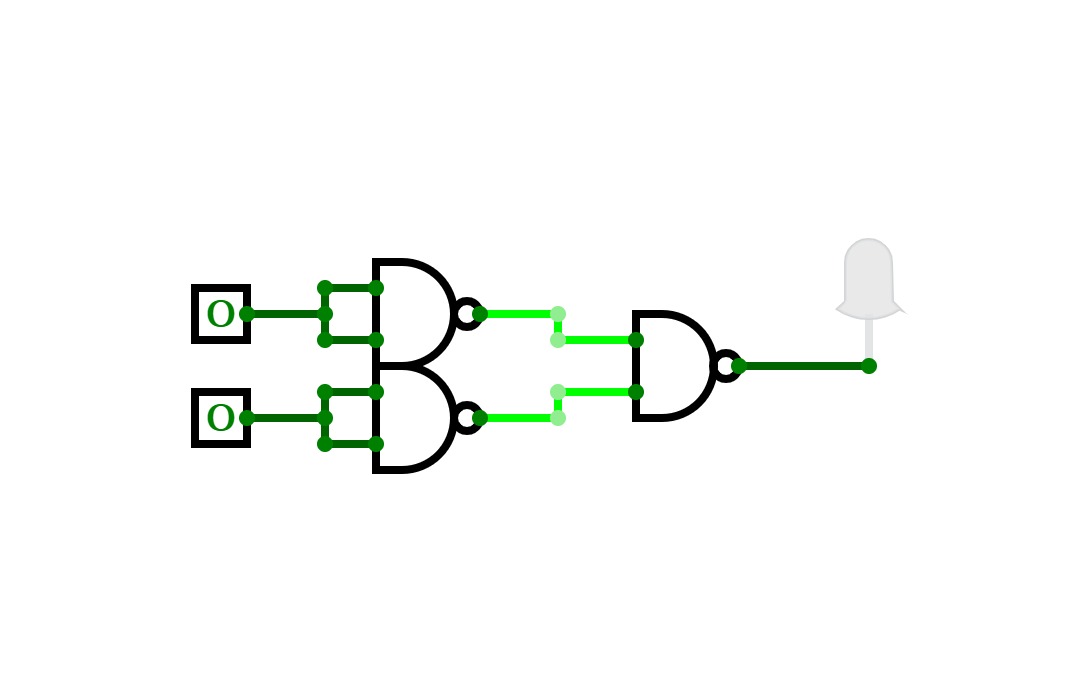

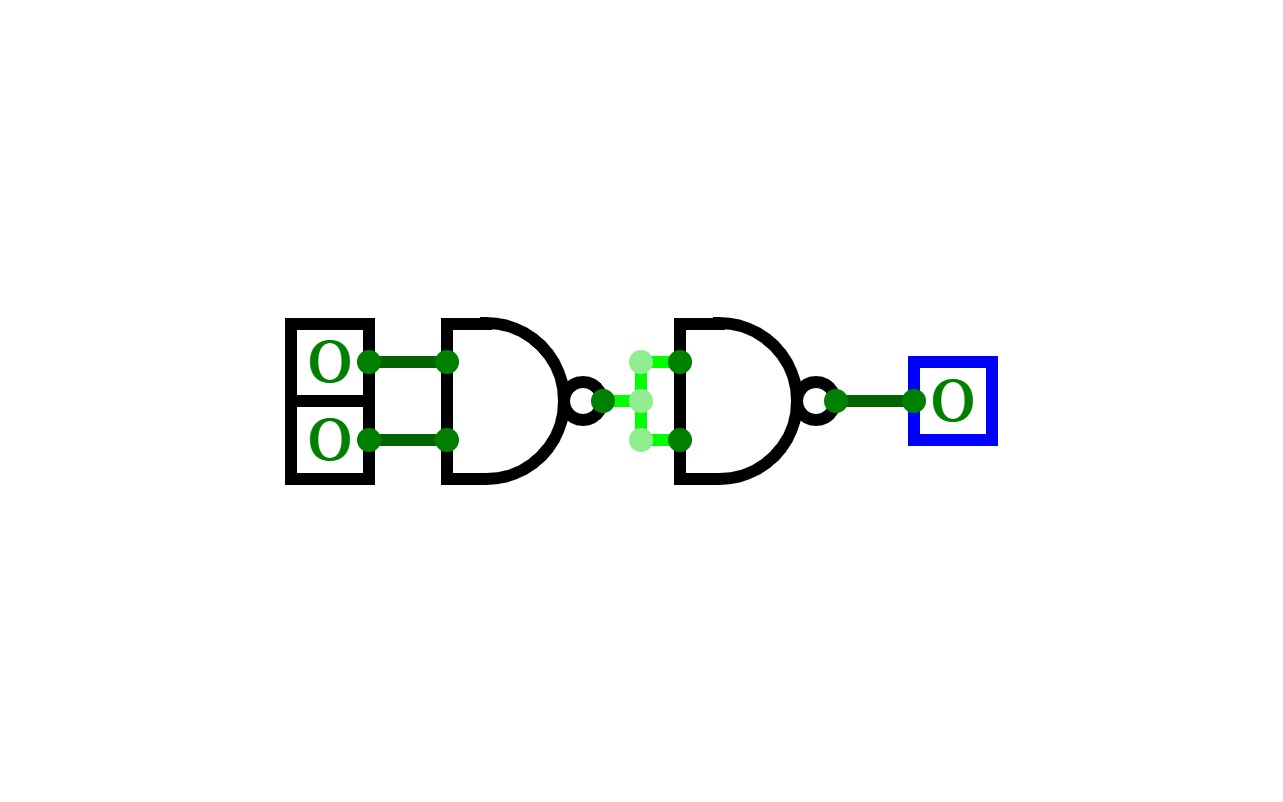

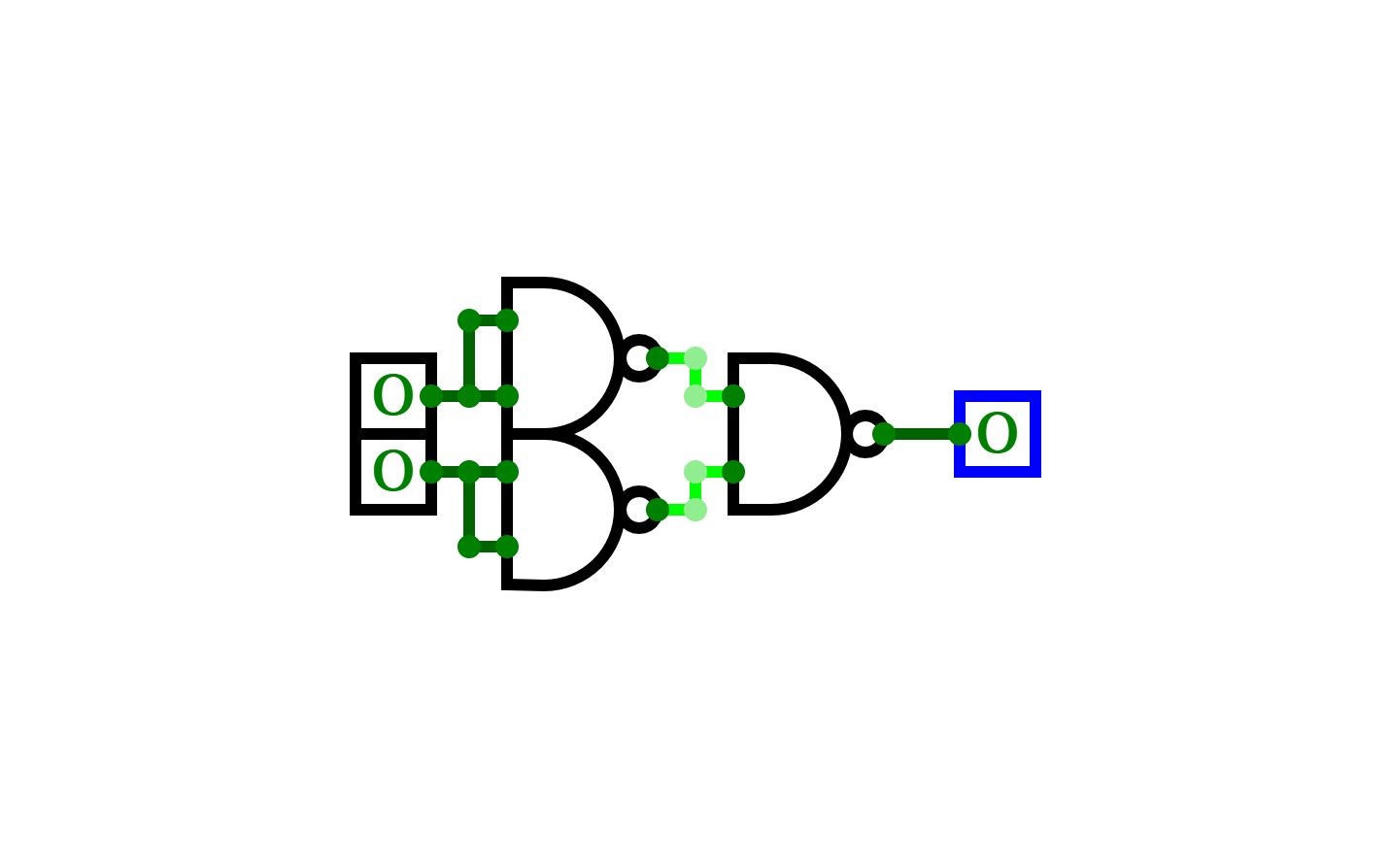

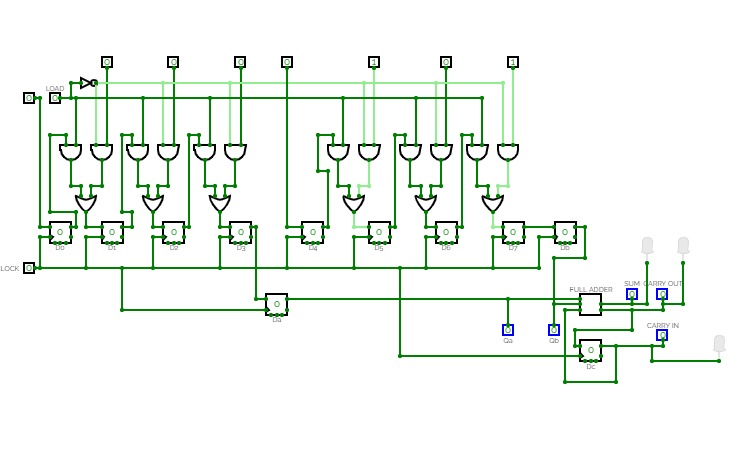

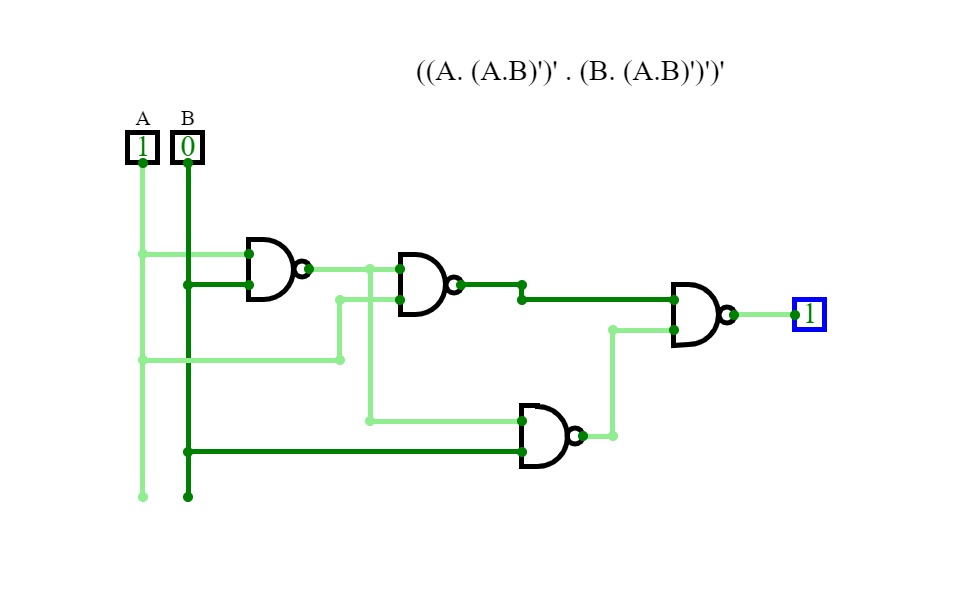

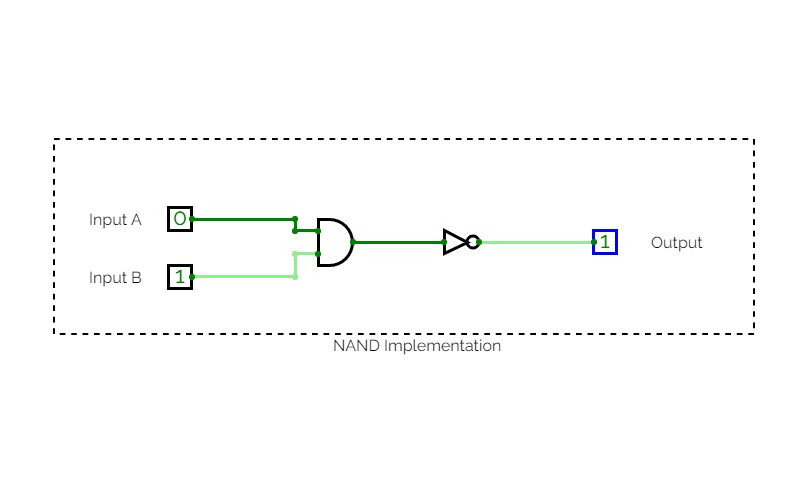

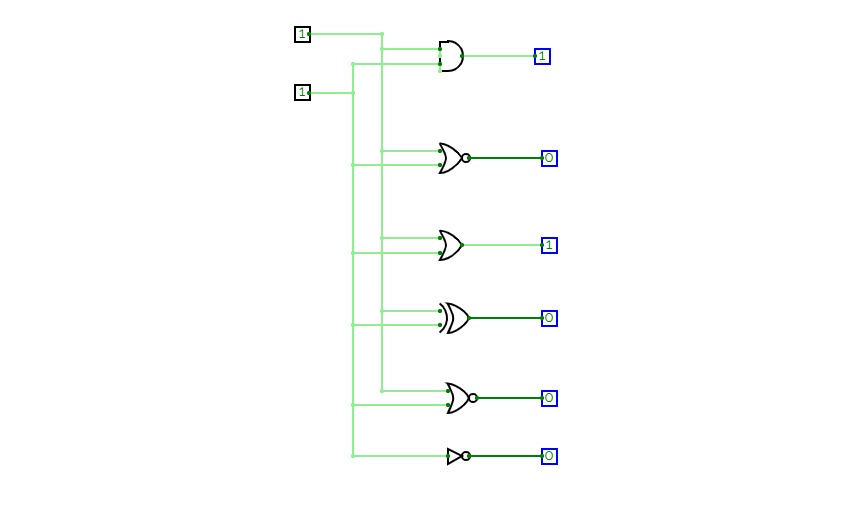

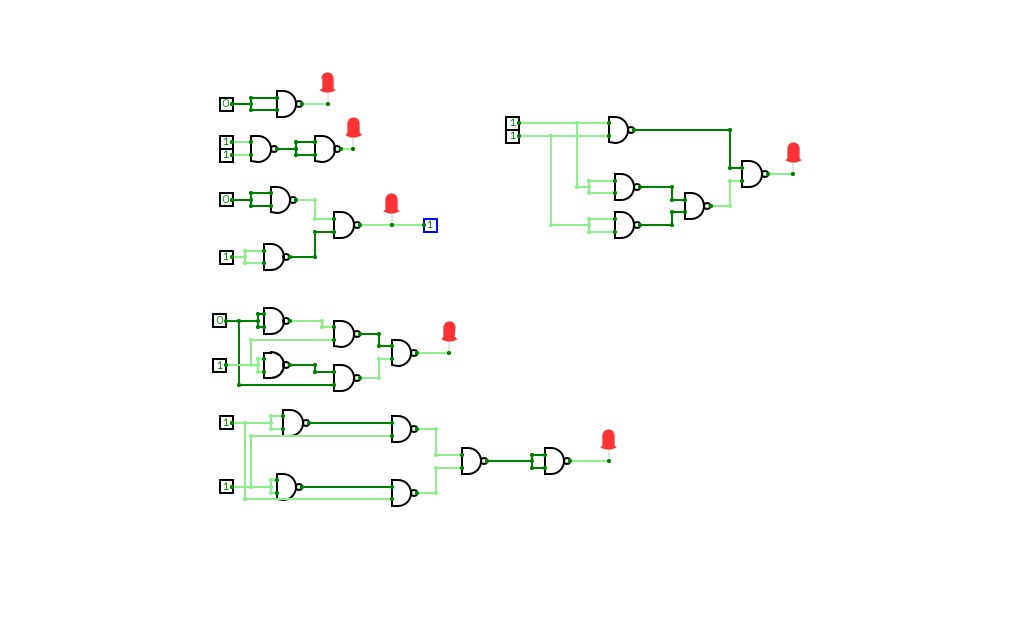

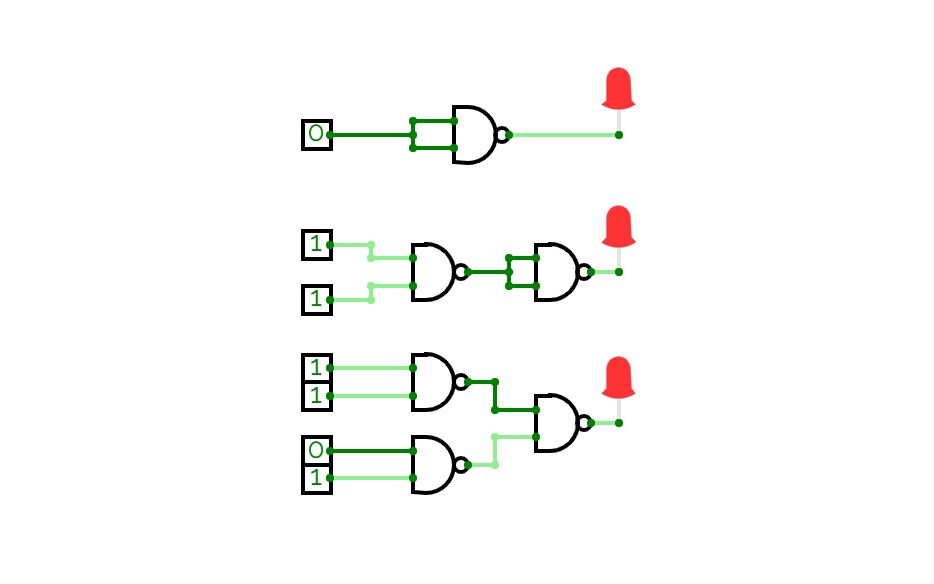

Full Adder (Only NAND)

Full Adder (Only NAND)Addition has never been so easy!

From NandGame.

Project 1

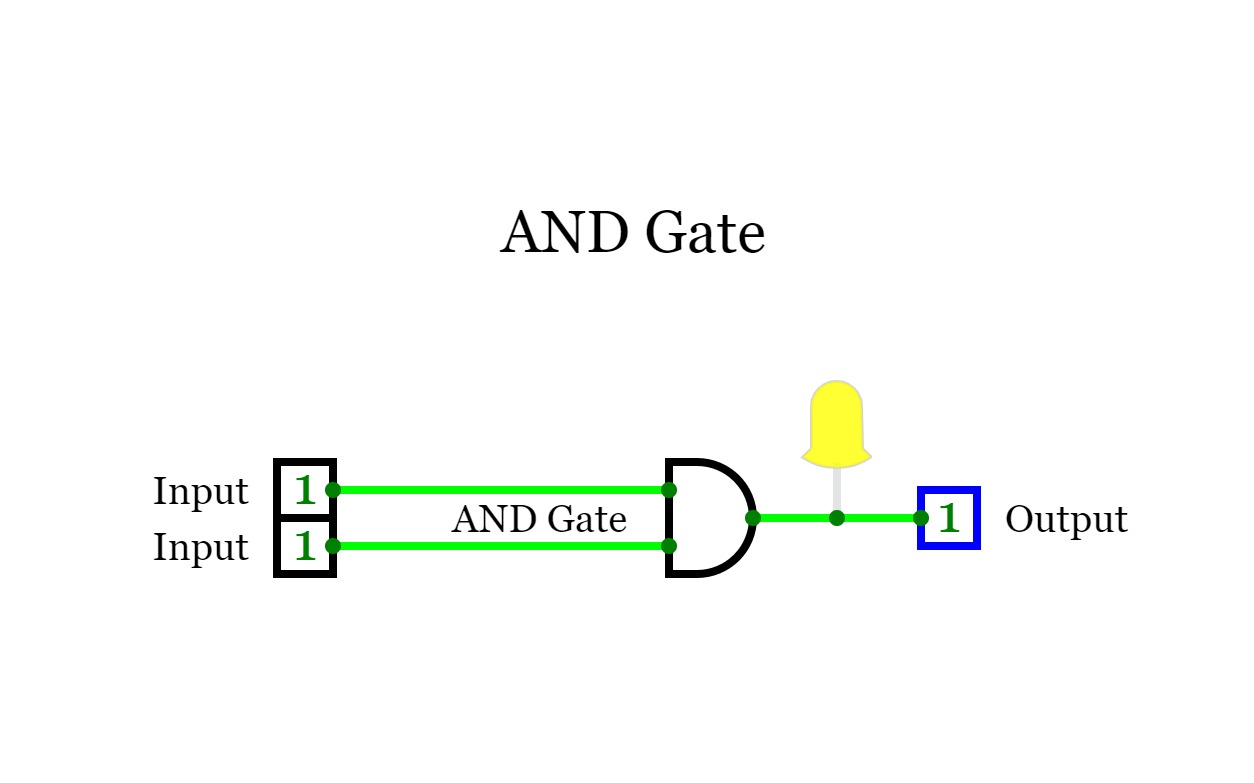

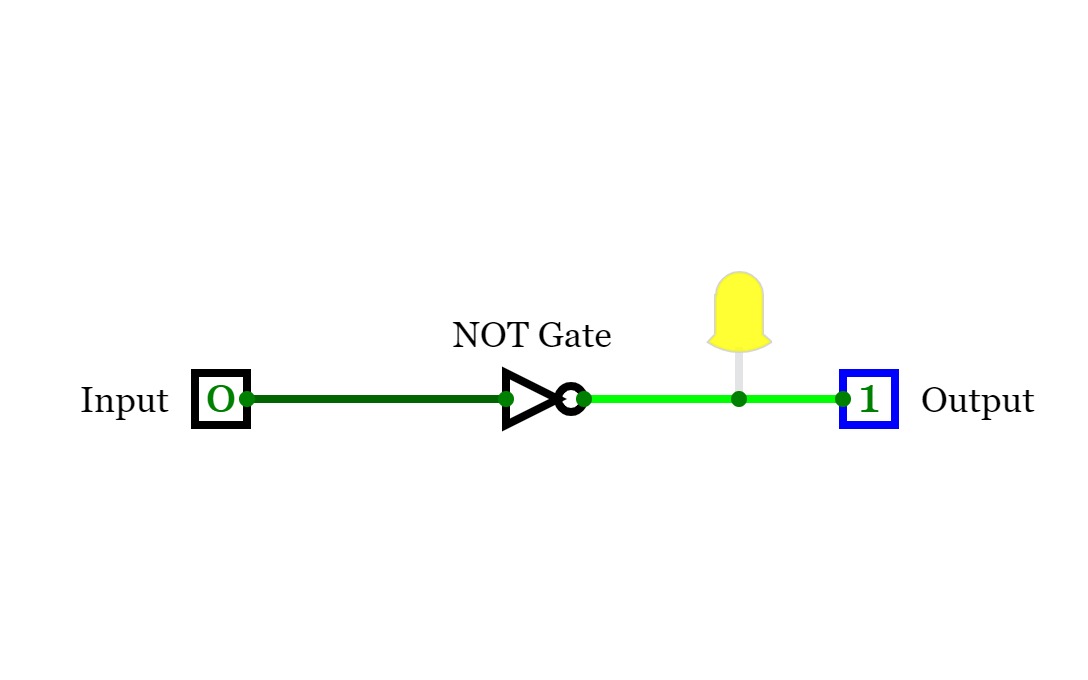

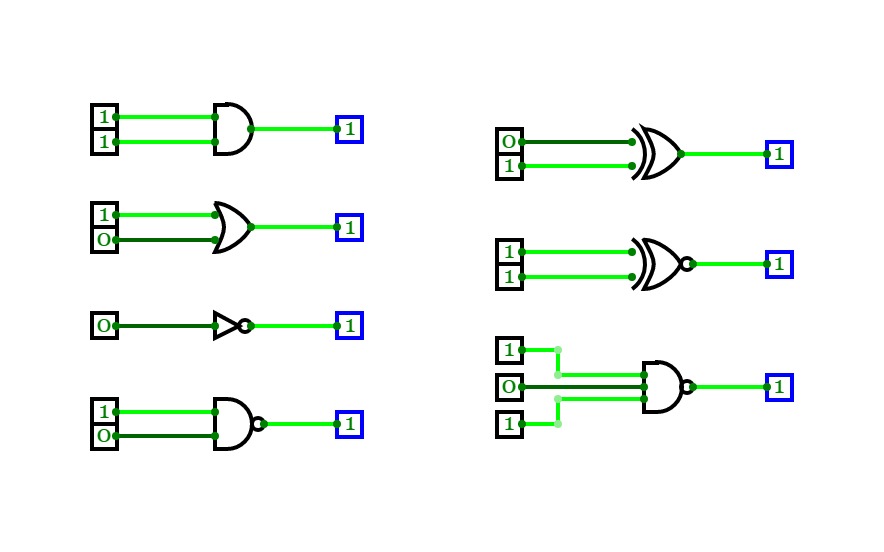

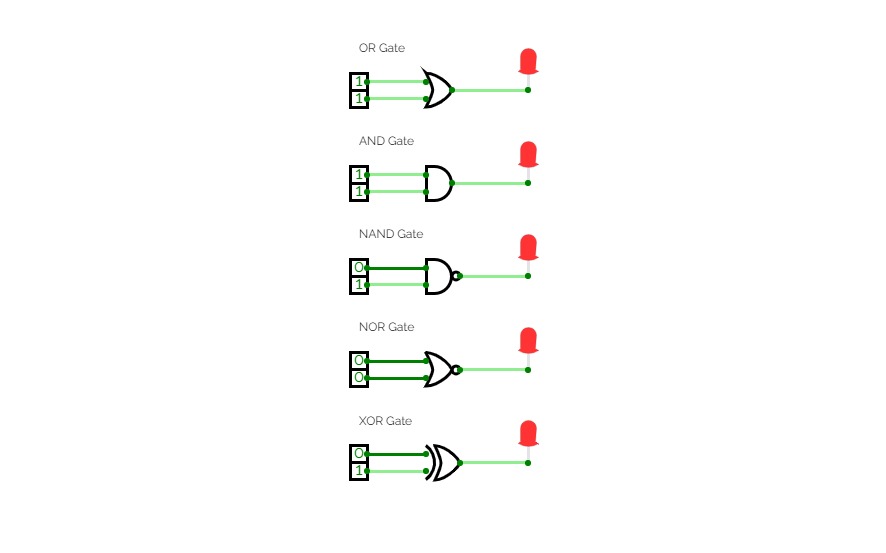

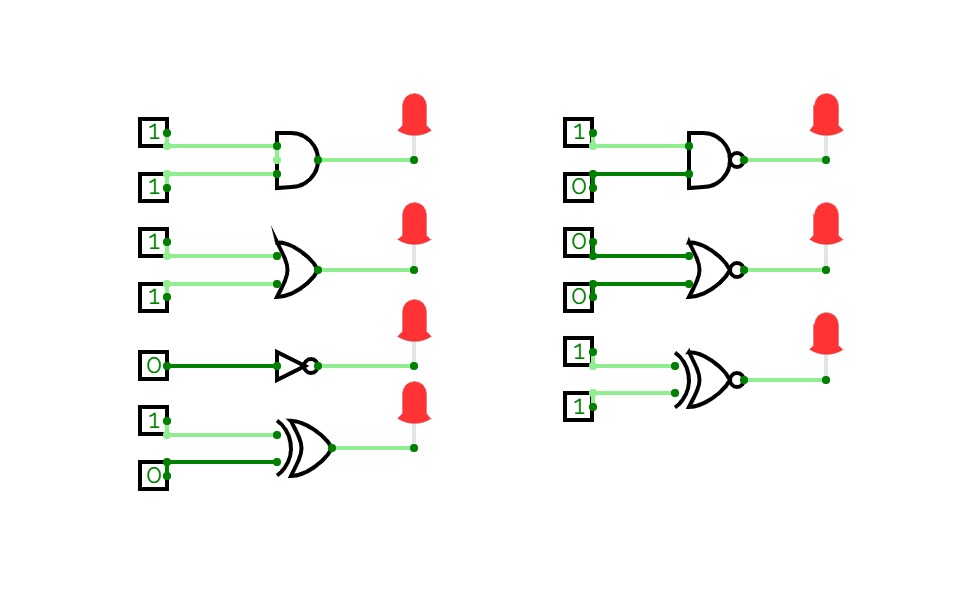

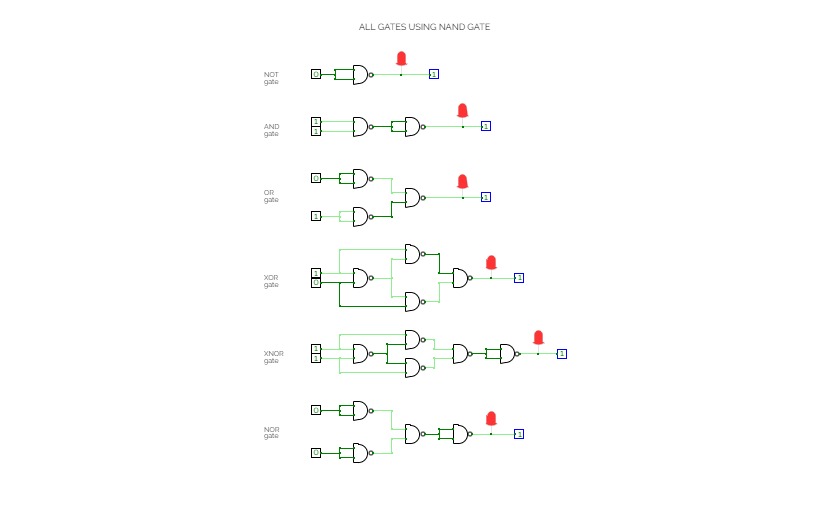

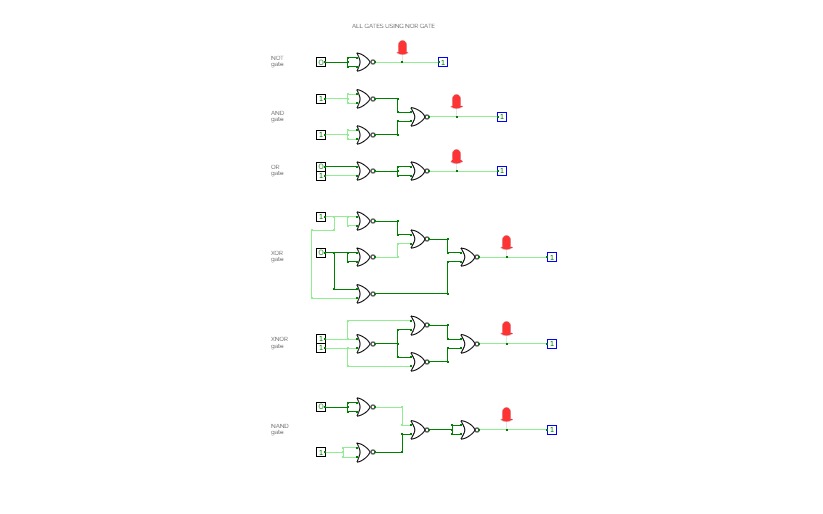

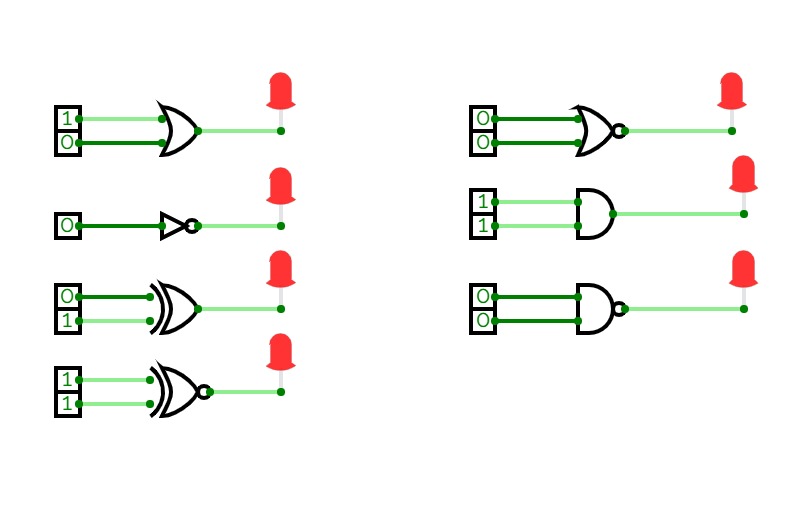

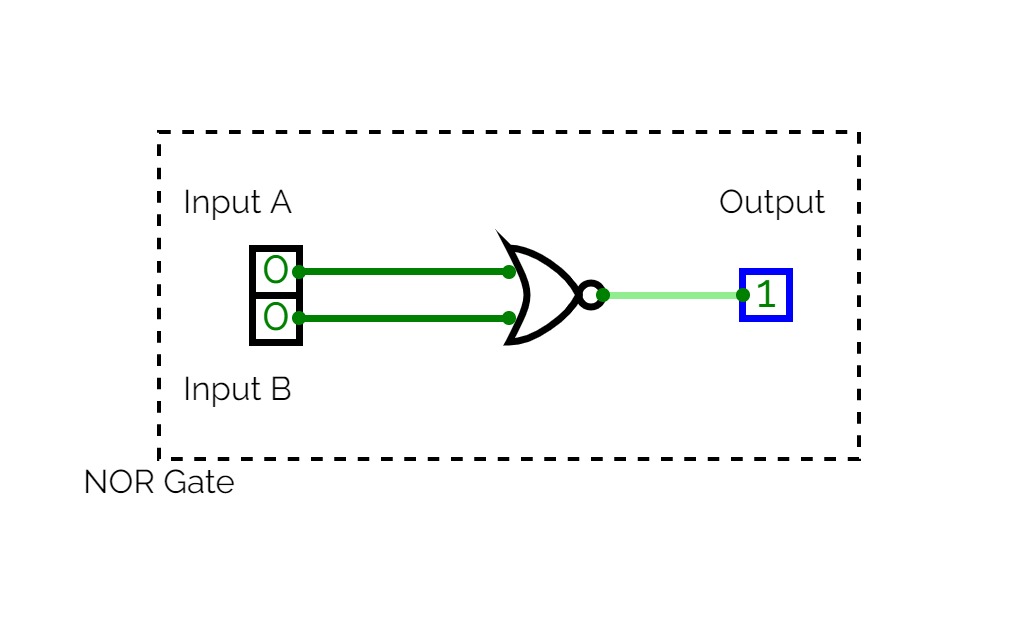

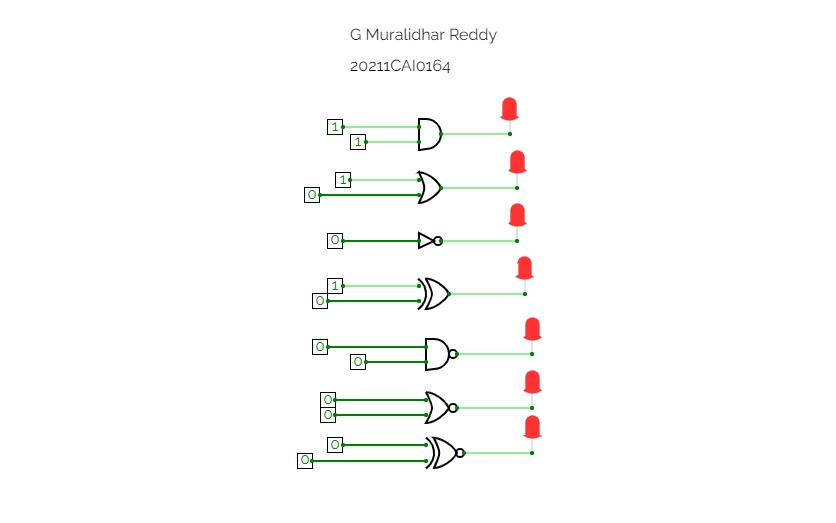

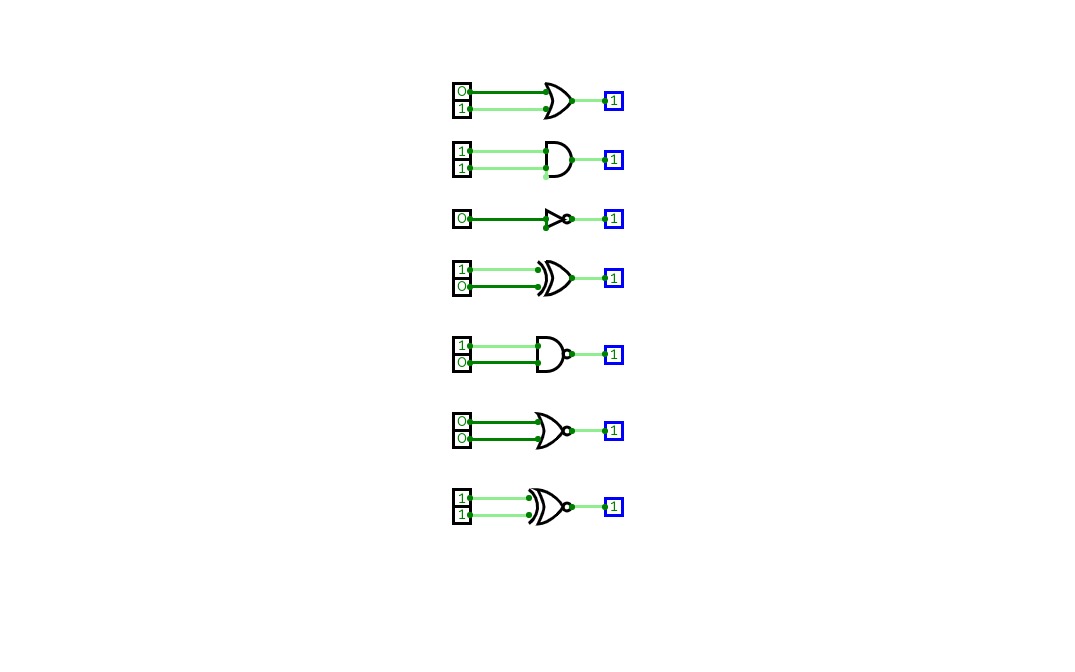

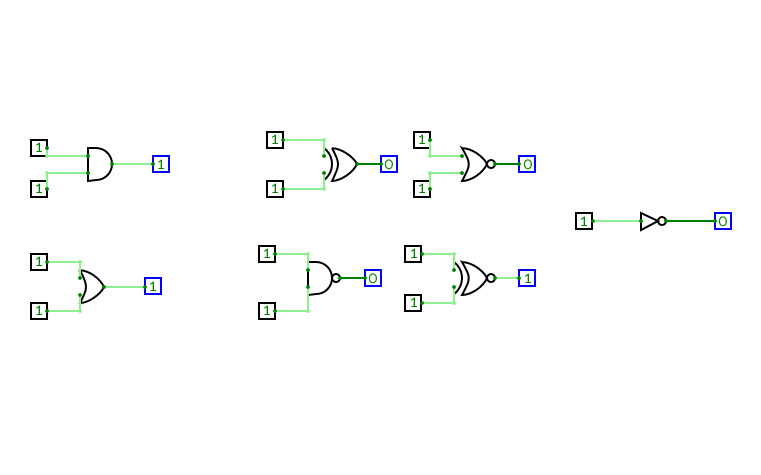

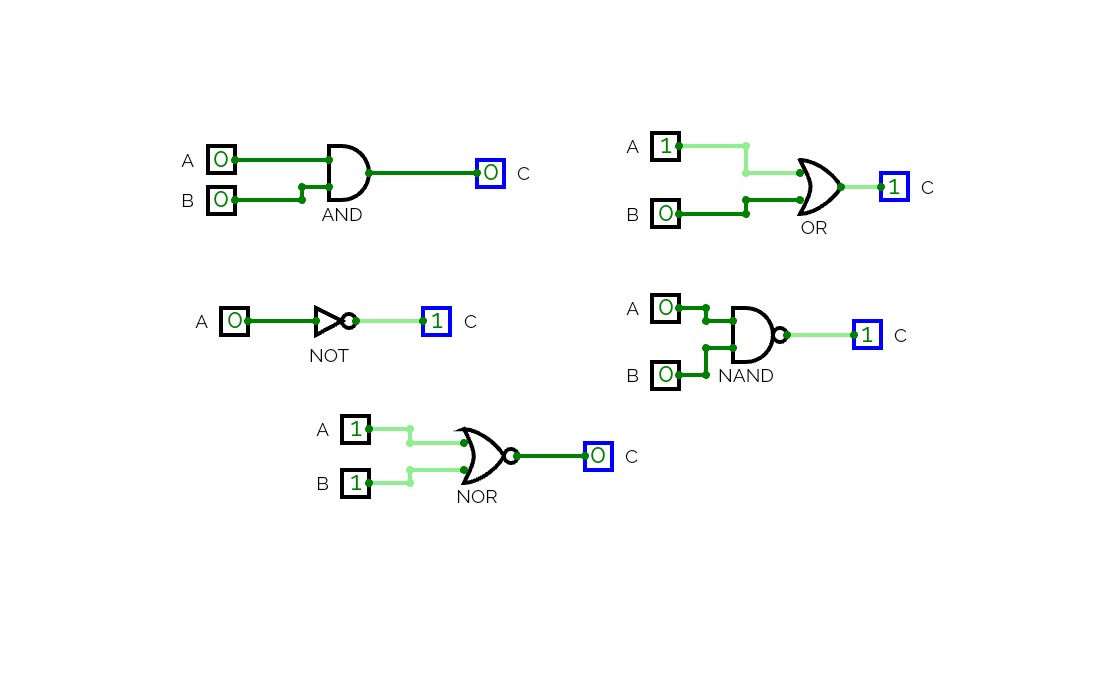

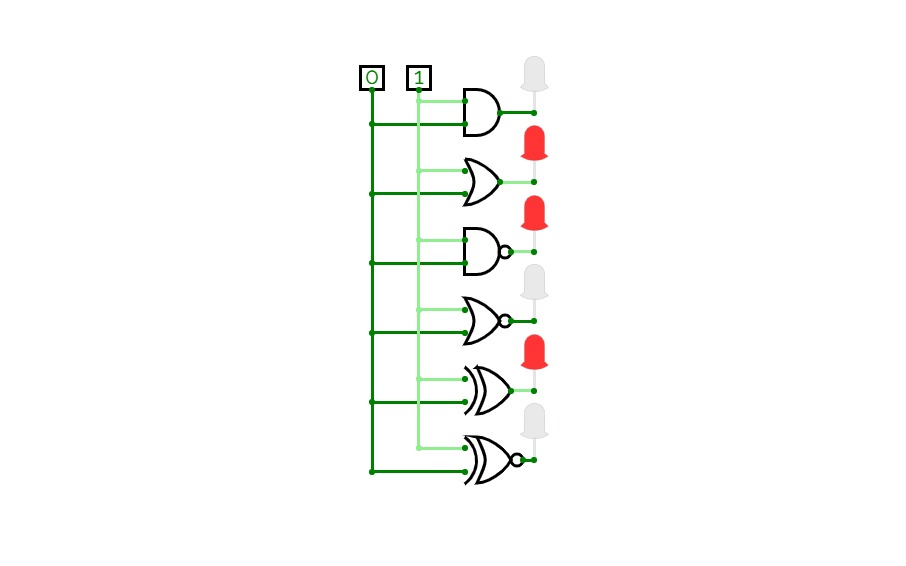

Project 1Aim :- Study and verify the outputs of the logic gates (AND, OR, NOT, NAND, NOR, Ex-OR, and

Ex-NOR).

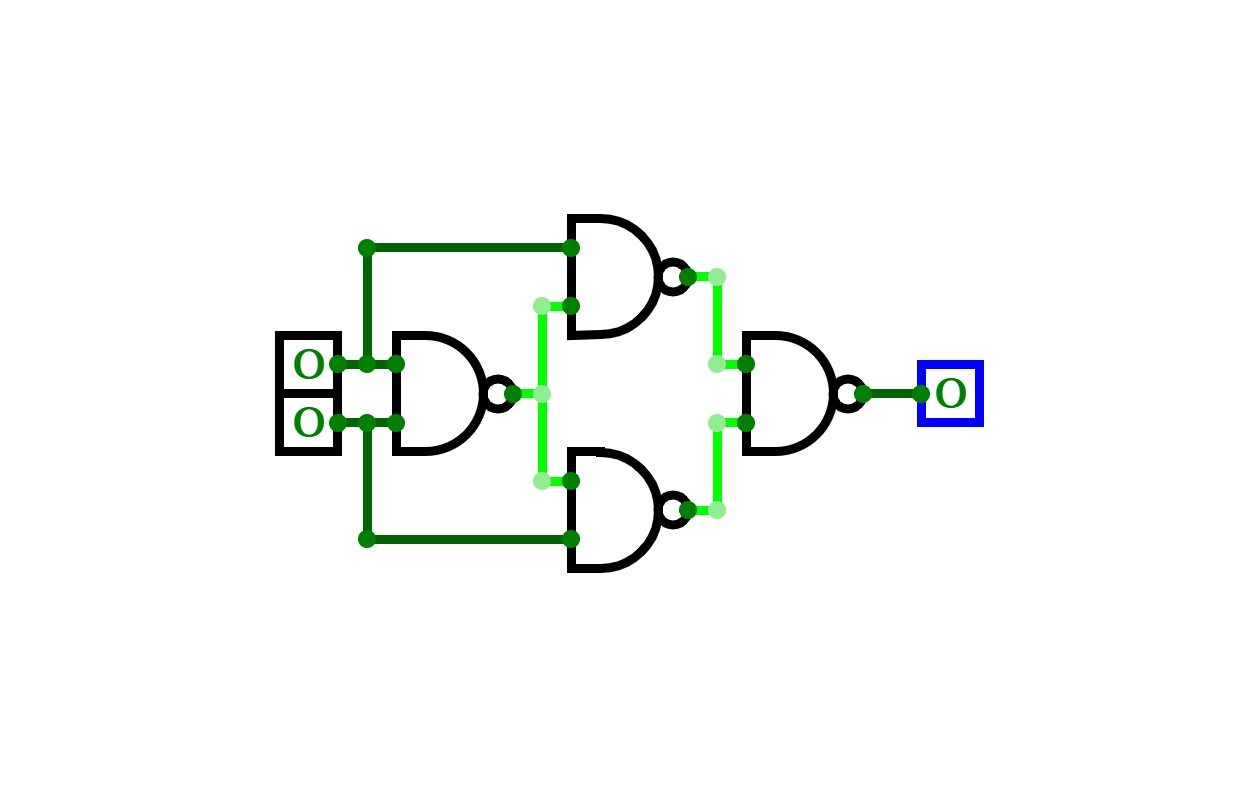

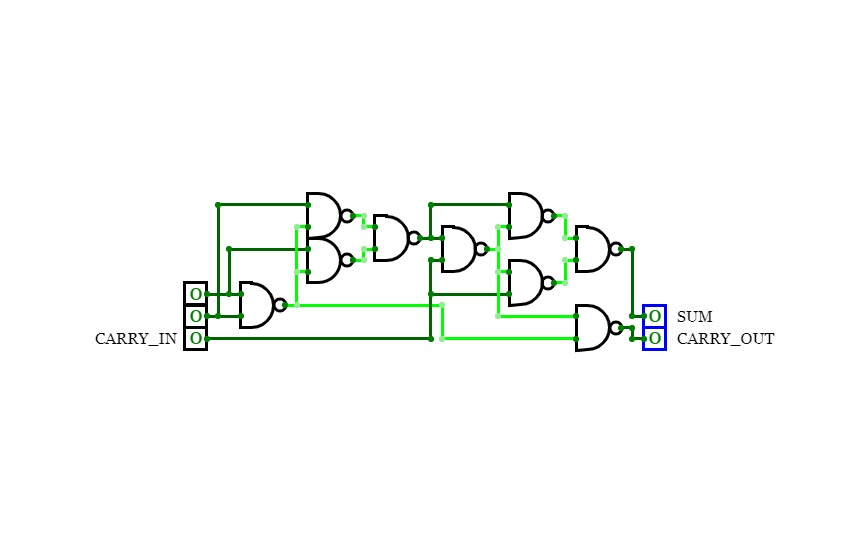

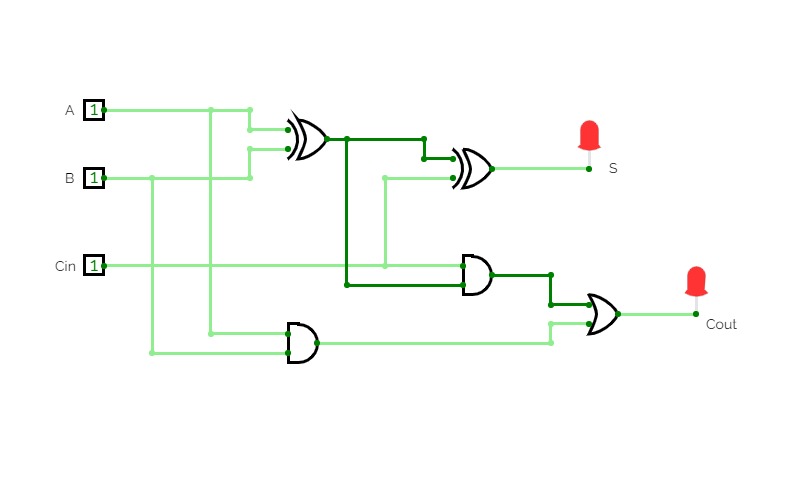

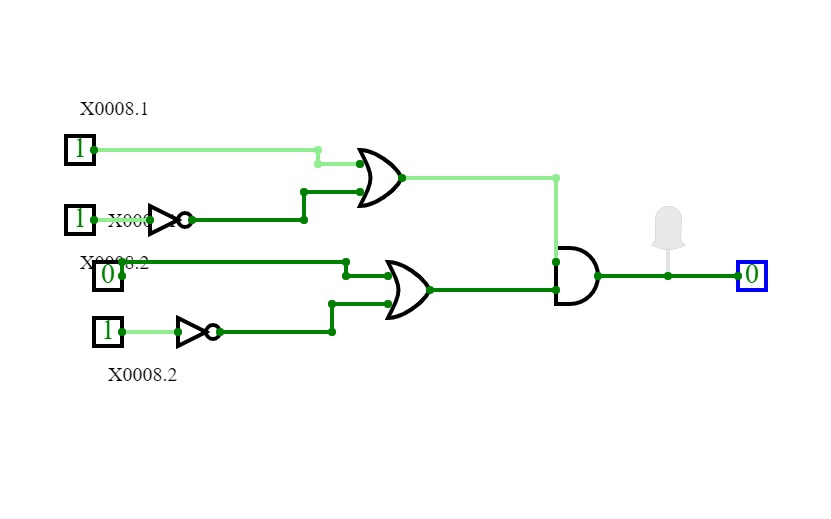

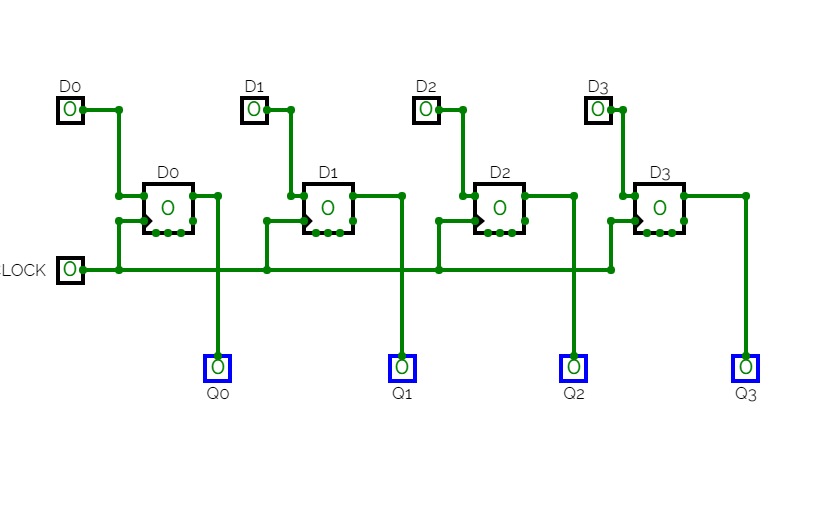

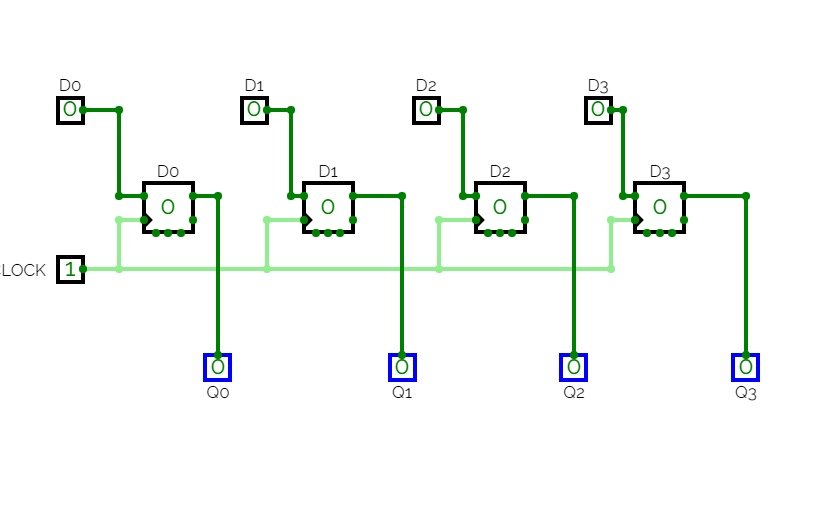

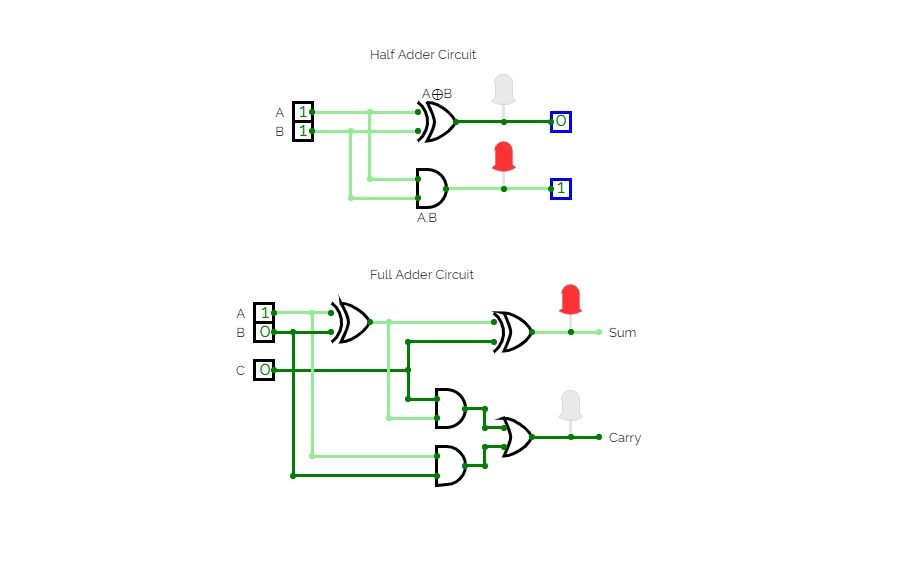

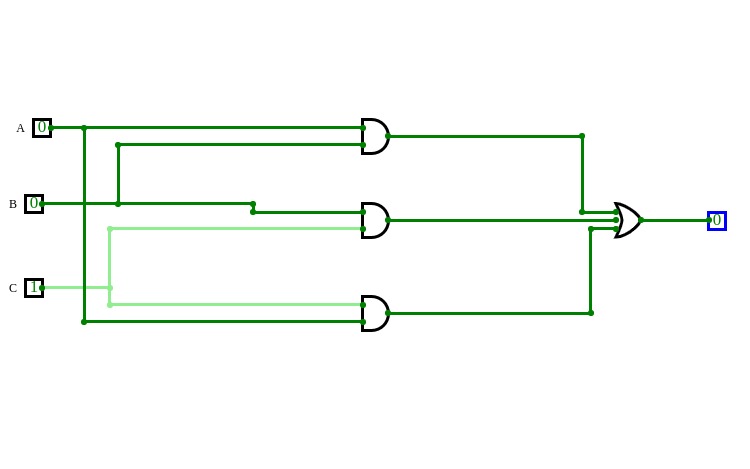

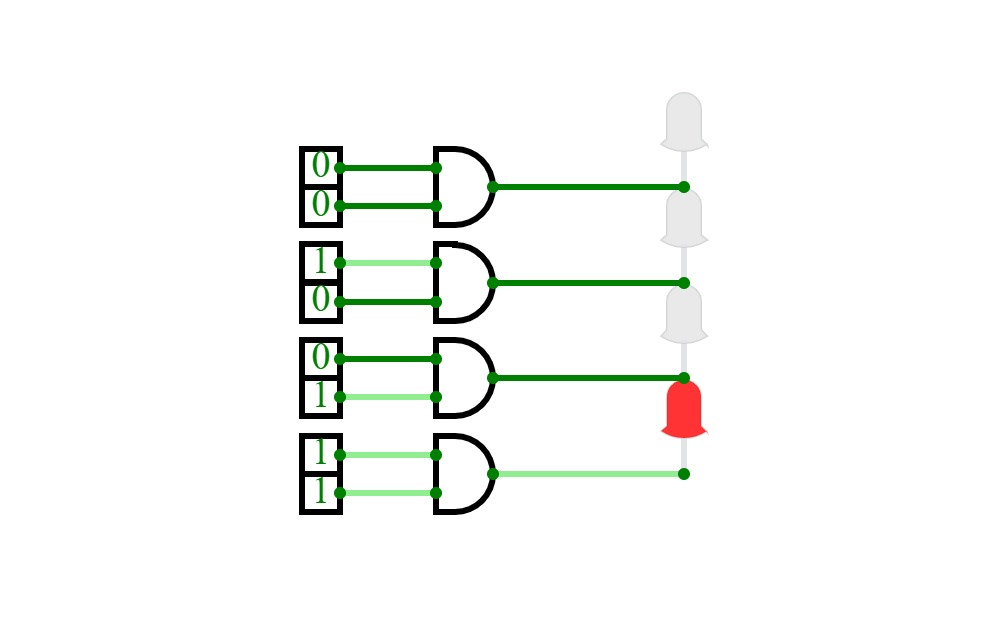

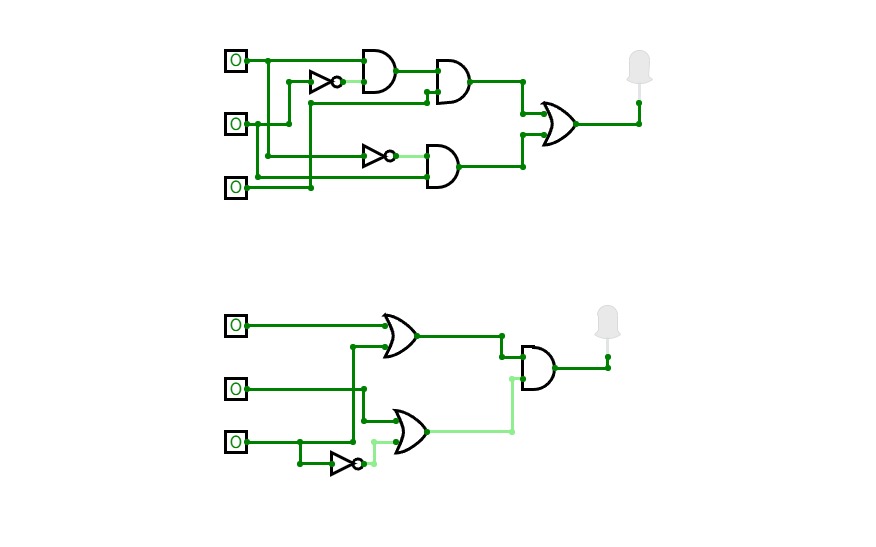

Adder Circuit

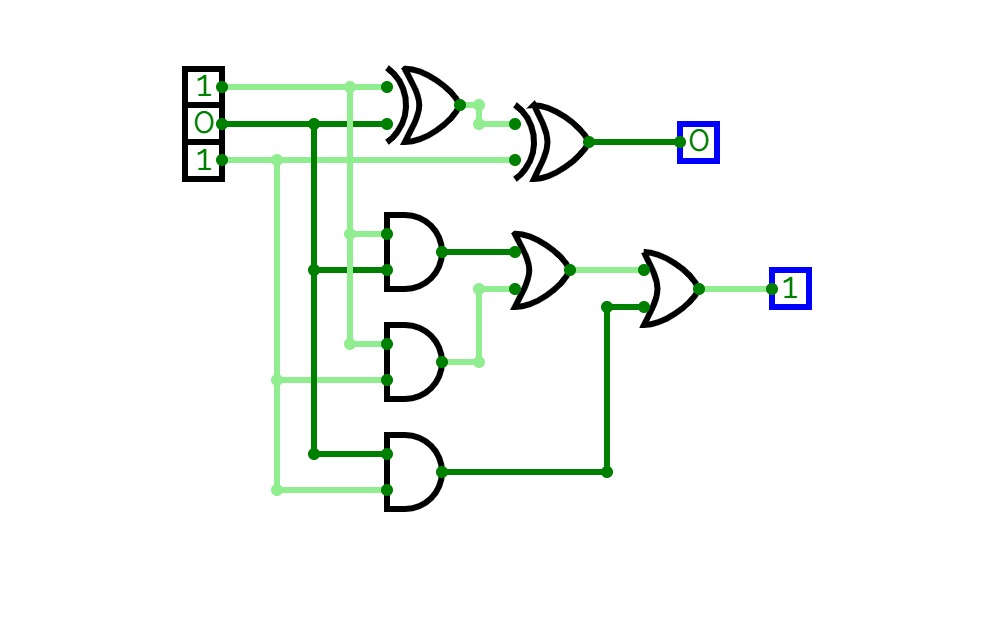

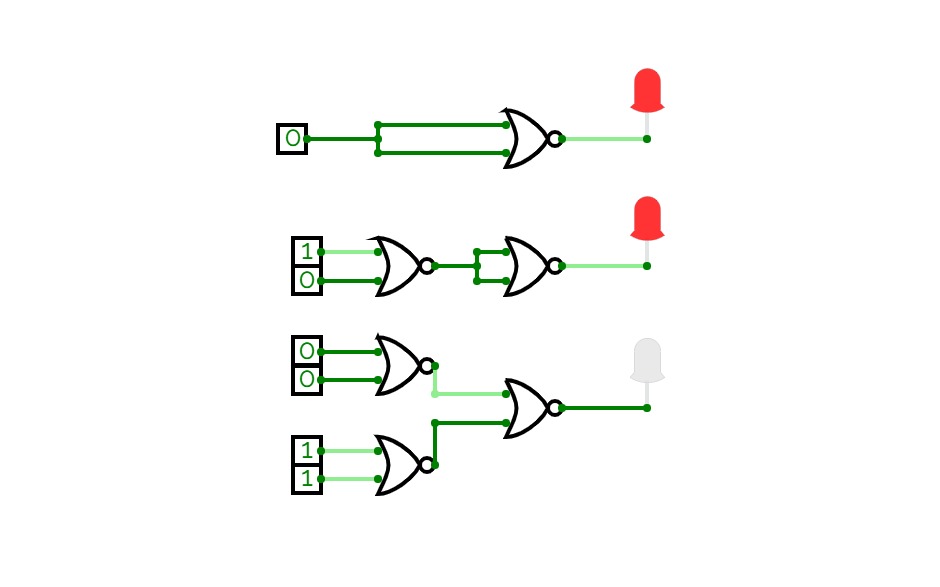

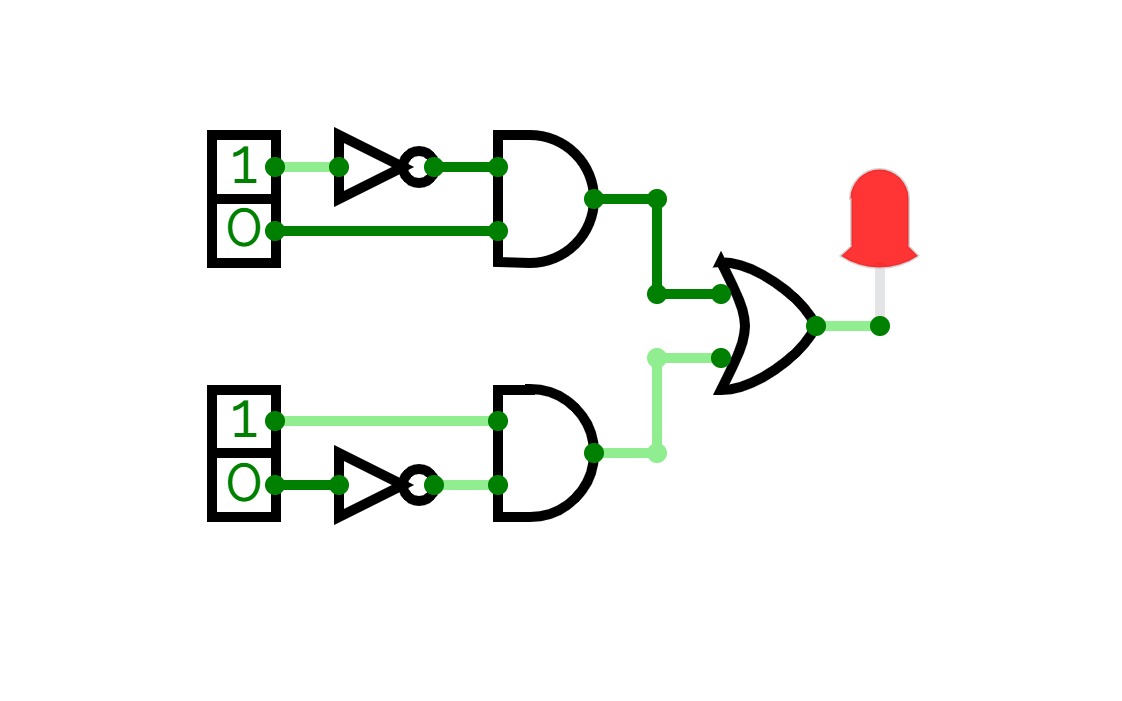

Adder CircuitHalf Adder : The addition of 2 bits is done using a combination circuit called Half adder. The input variables are augend and addend bits and output variables are sum & carry bits. A and B are the two input bits.

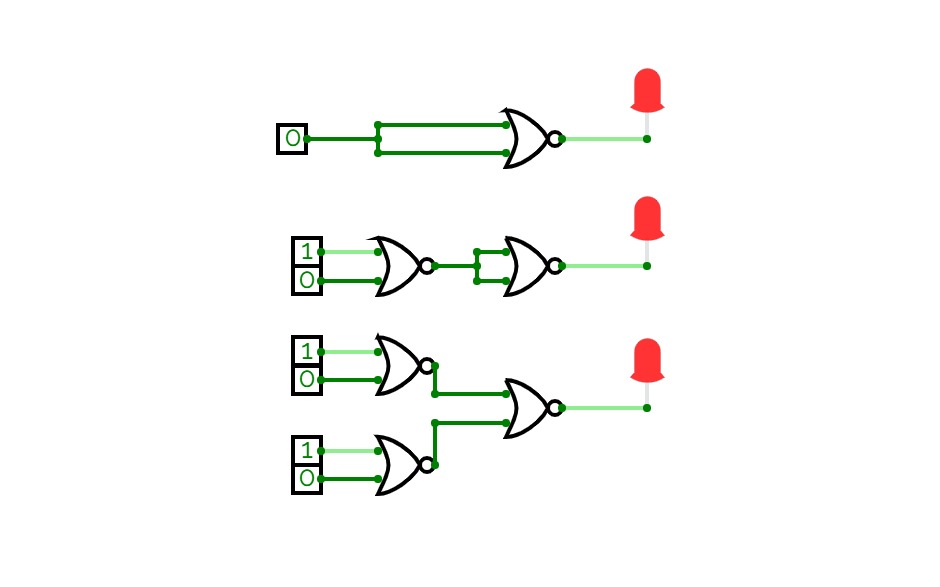

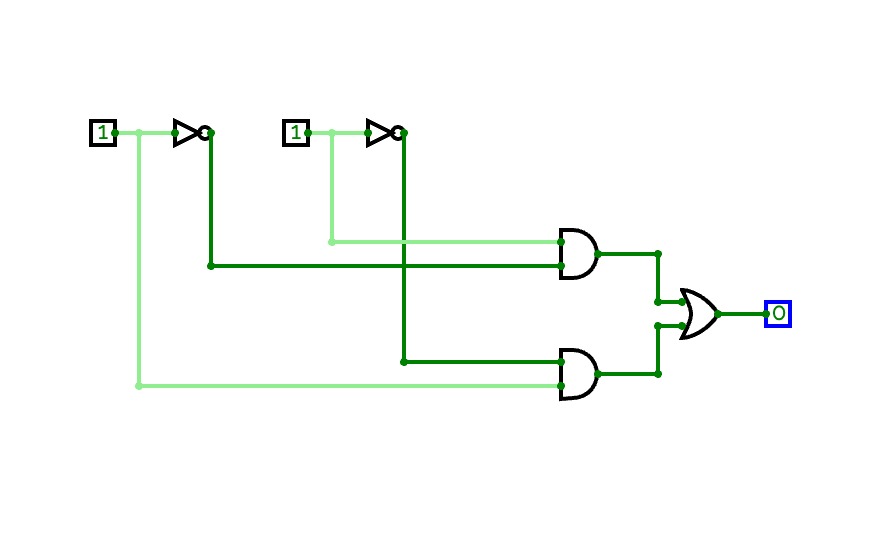

Full Adder Circuit : Full Adder is the adder which adds three inputs and produces two outputs. The first two inputs are A and B and the third input is an input carry as C-IN. The output carry is designated as C-OUT and the normal output is designated as S which is SUM.

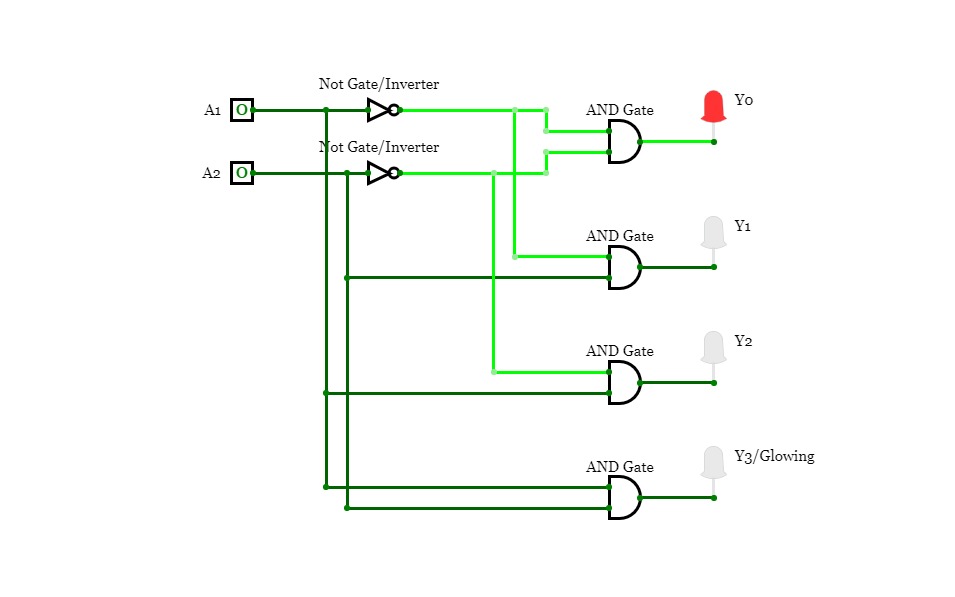

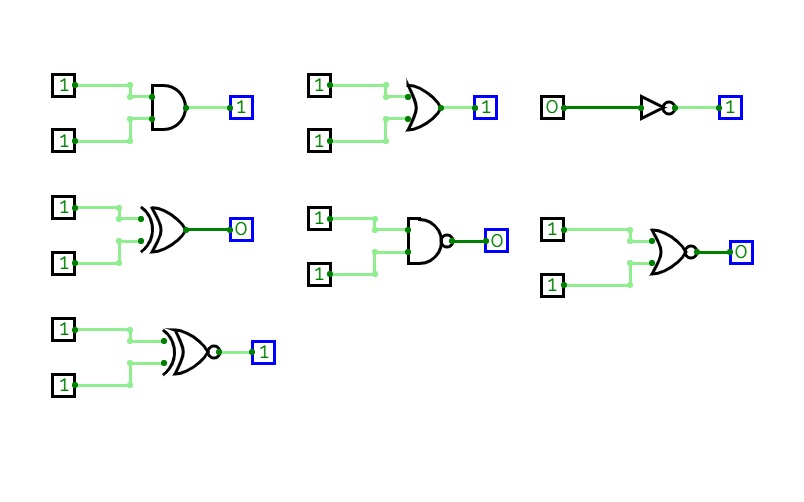

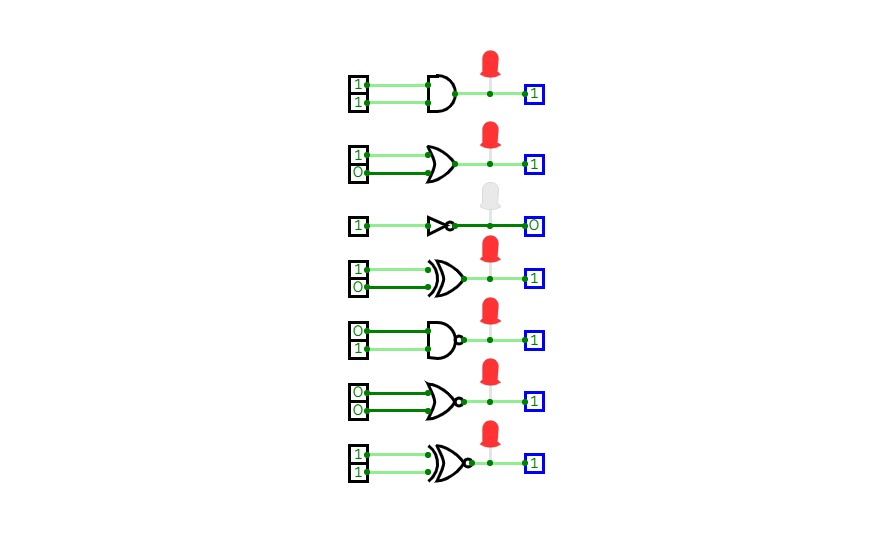

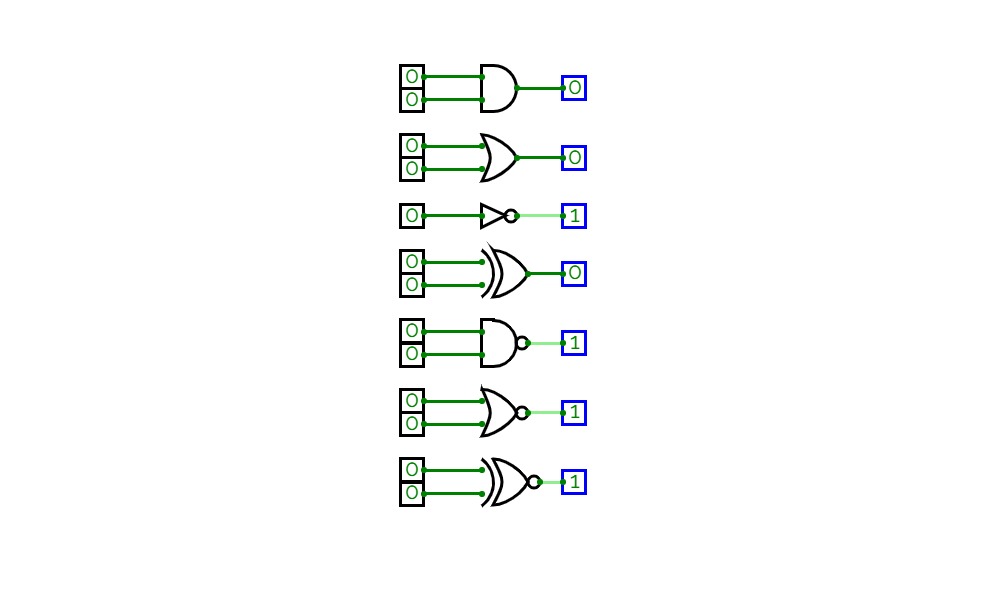

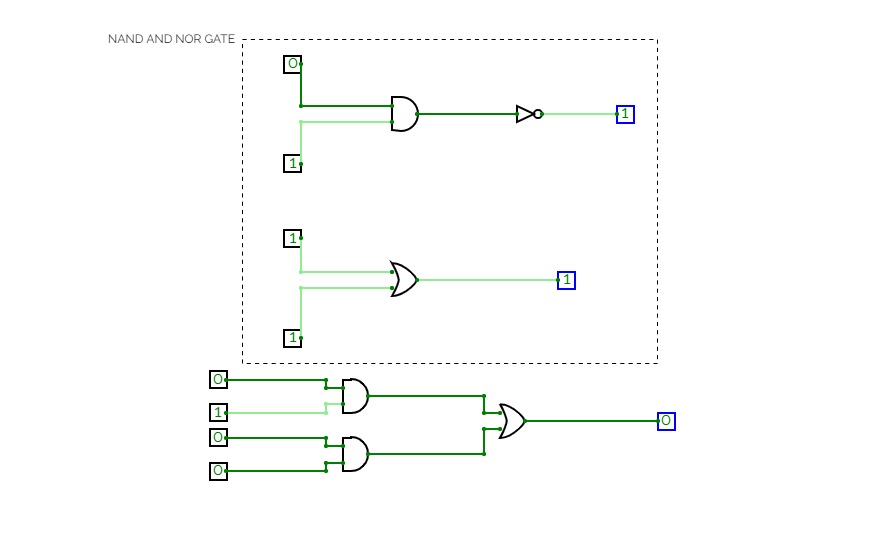

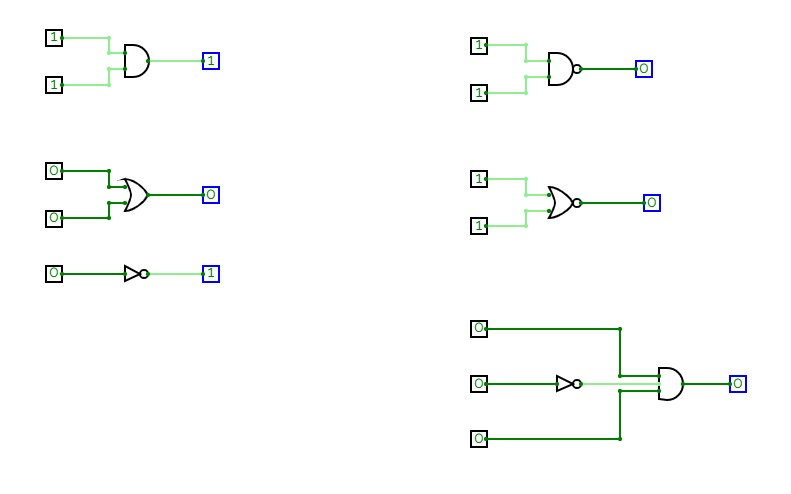

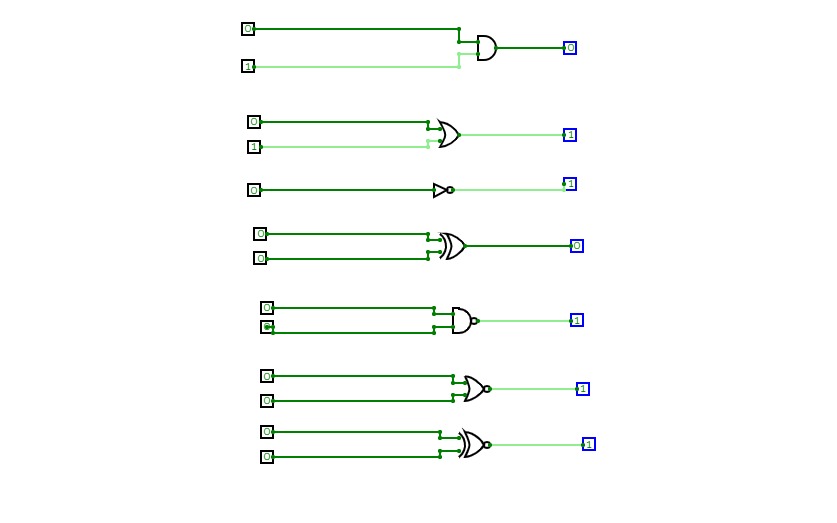

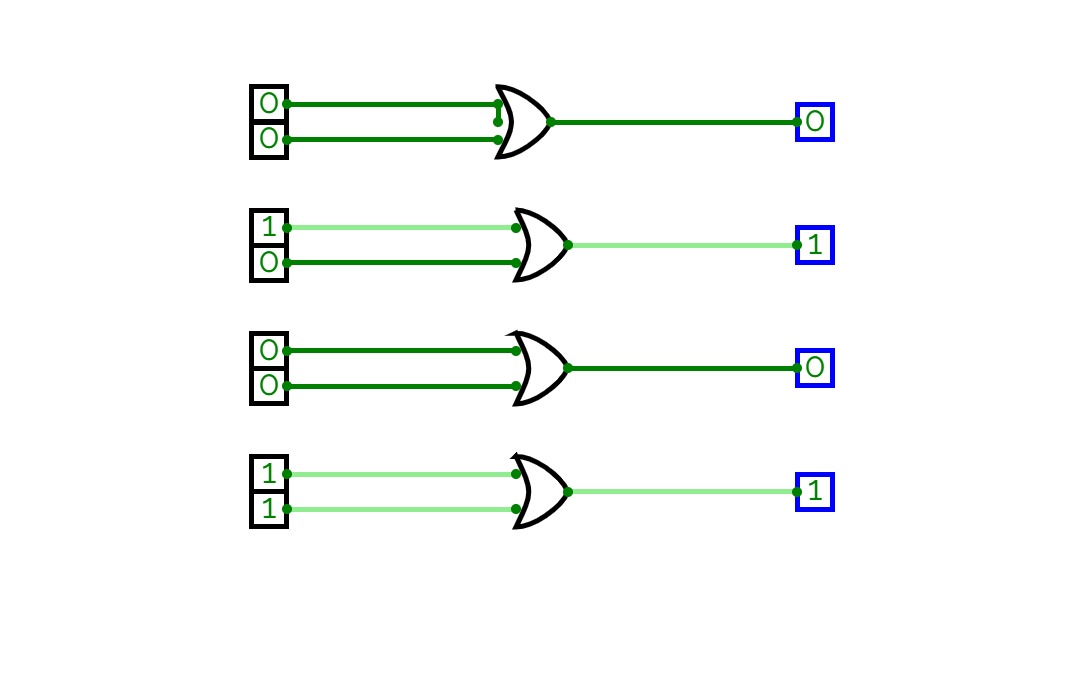

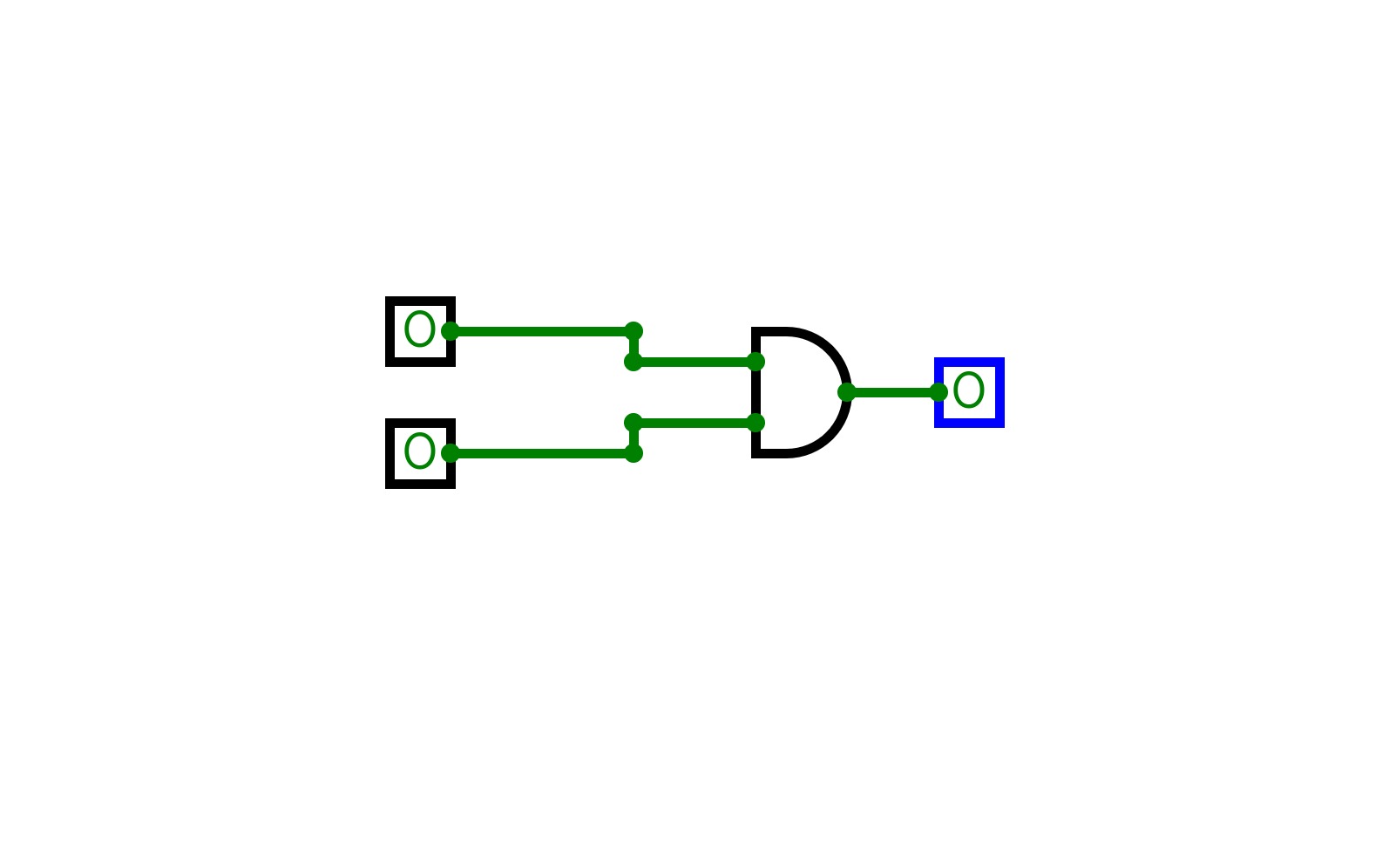

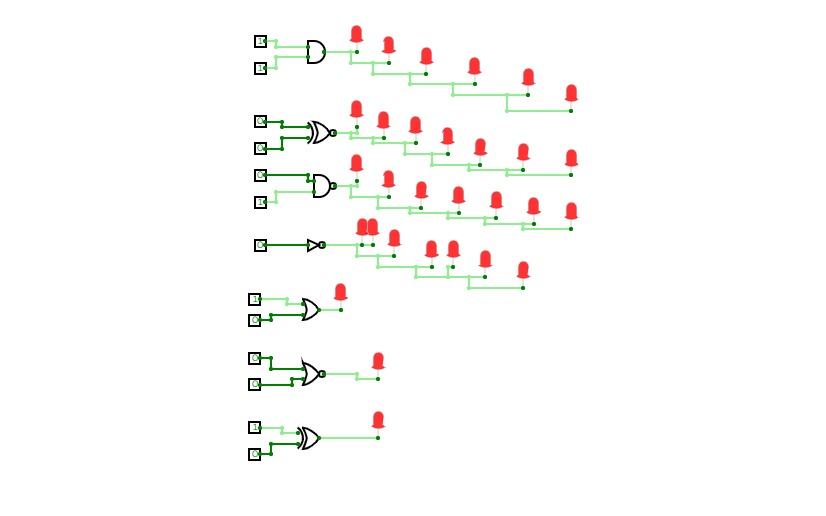

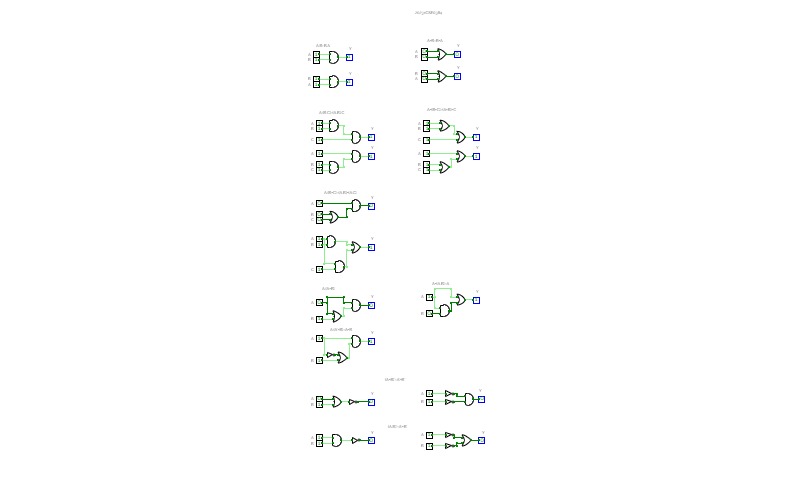

Gates (table varification)

Gates (table varification)all gates varification truth table

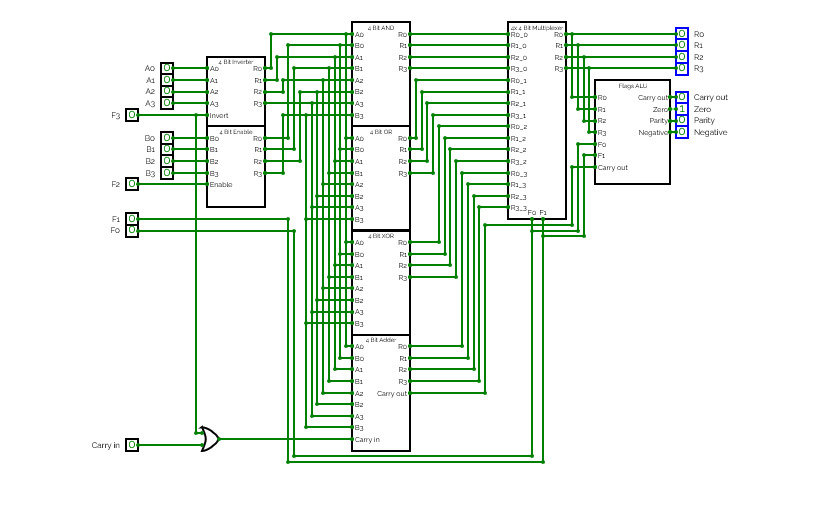

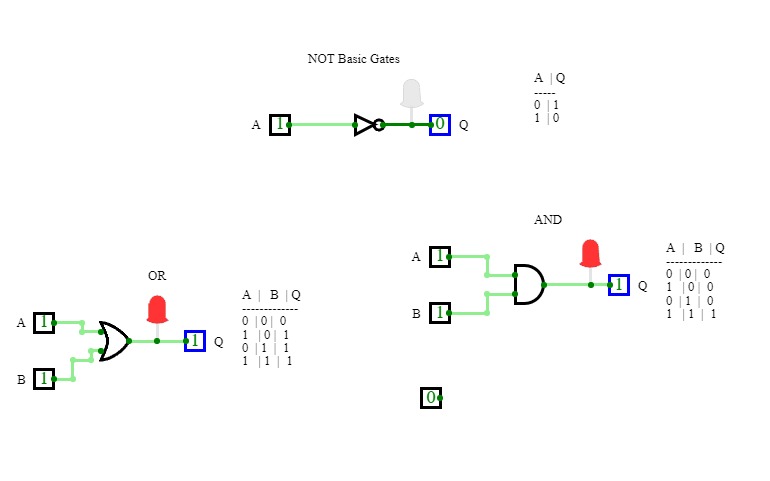

EXPERIMENT 1

EXPERIMENT 1Usage of Basic Gates and Universal Gates

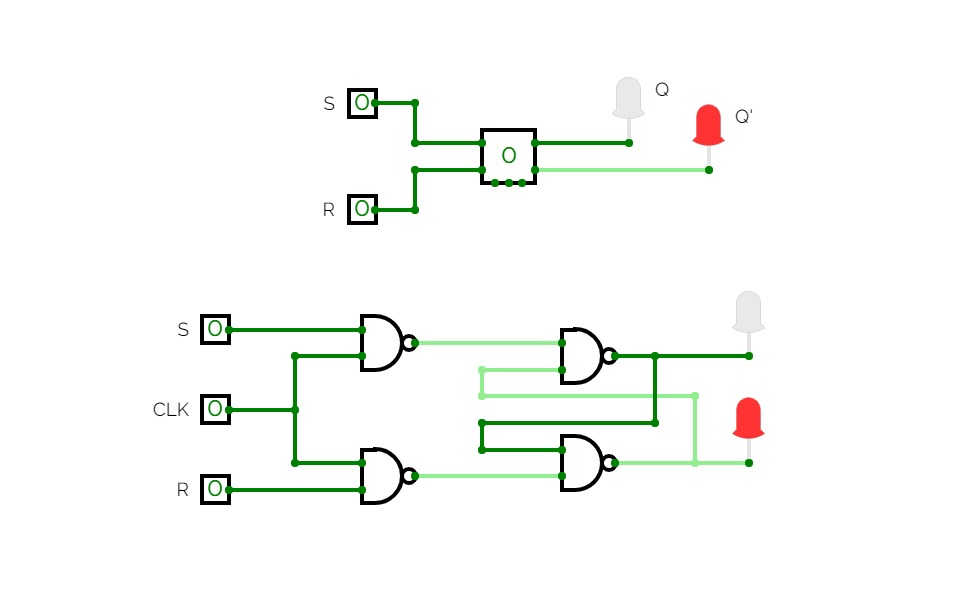

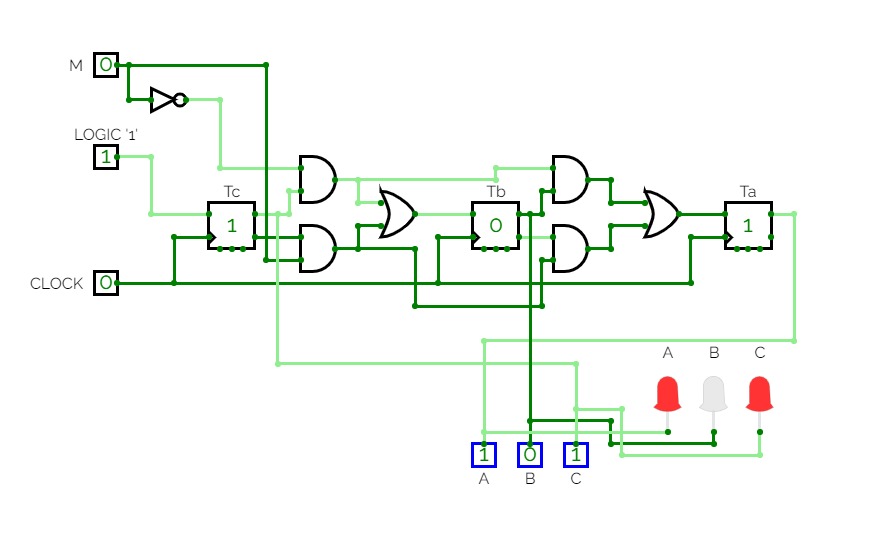

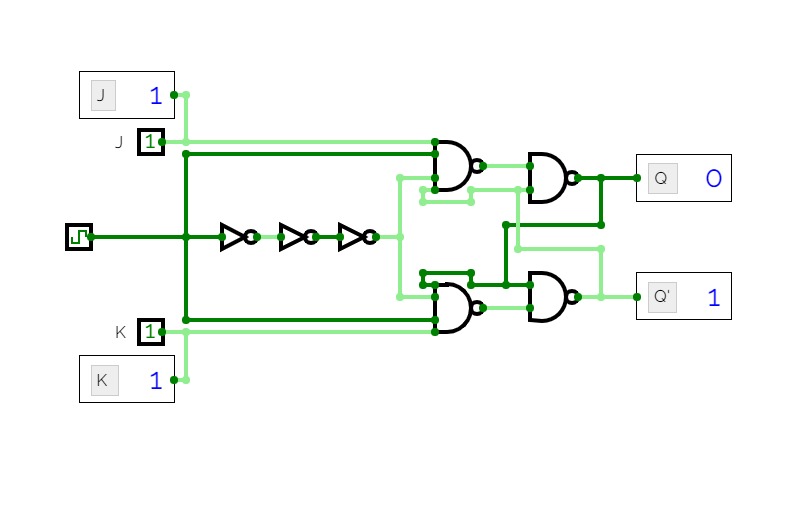

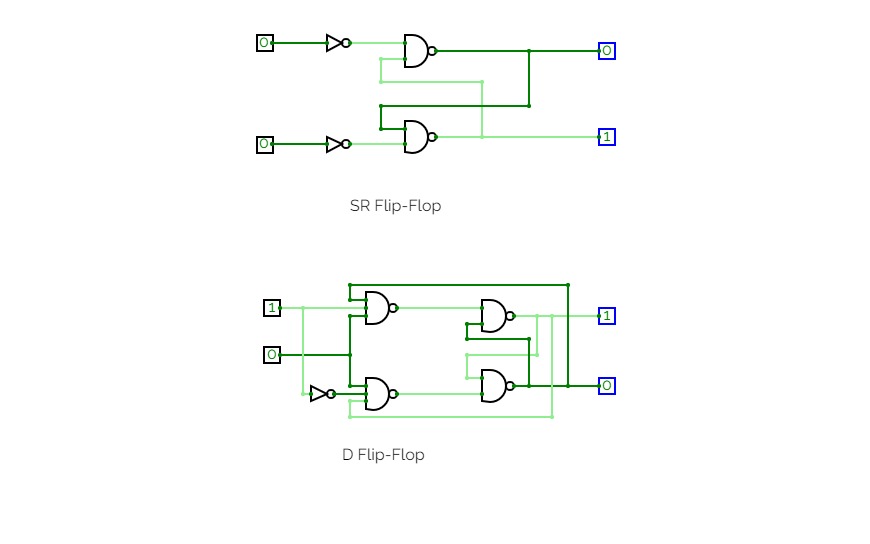

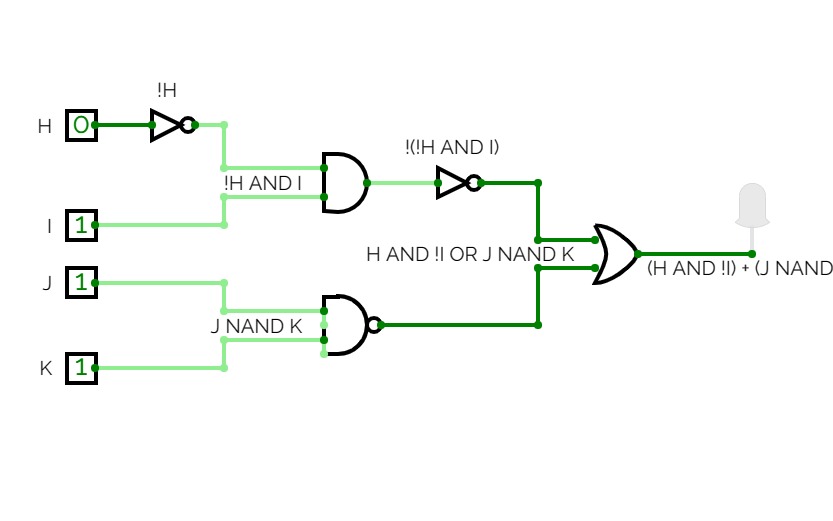

JK FlipFlop NAND Gates (Rising edge)

JK FlipFlop NAND Gates (Rising edge)This demonstrate the JK-Flipflop.

J 0, K 0 => do nothing

J 1, K 0 => Set (Q = 1, Q' = 0)

J 0, K 1 => Reset (Q = 0, Q' = 1)

J 1, K 1 => Toggle Q and Q'

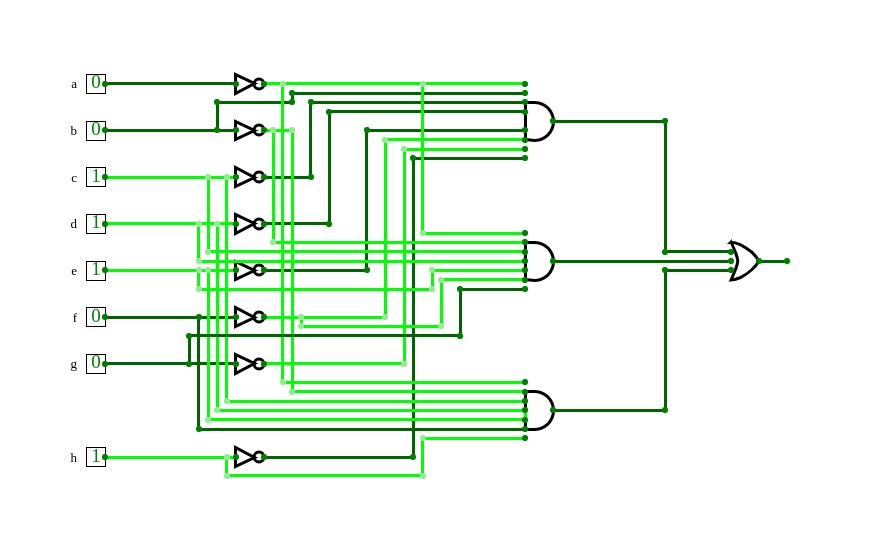

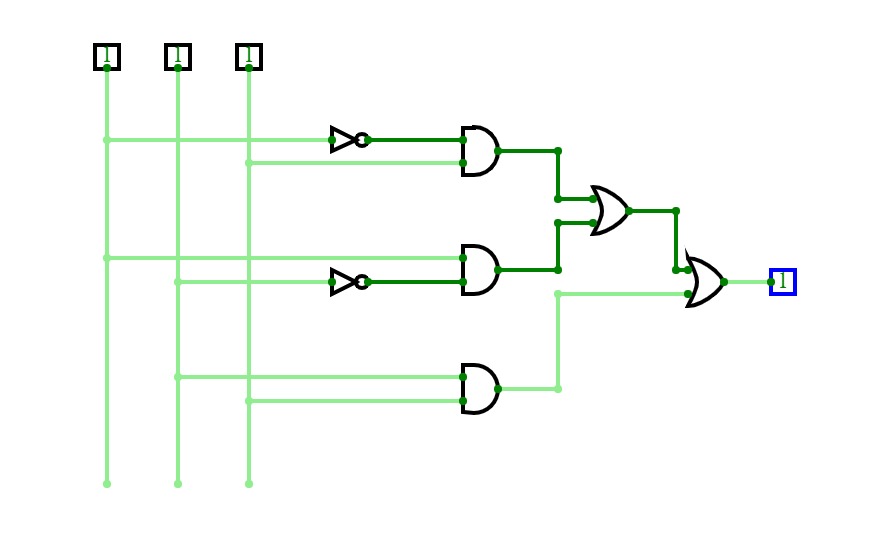

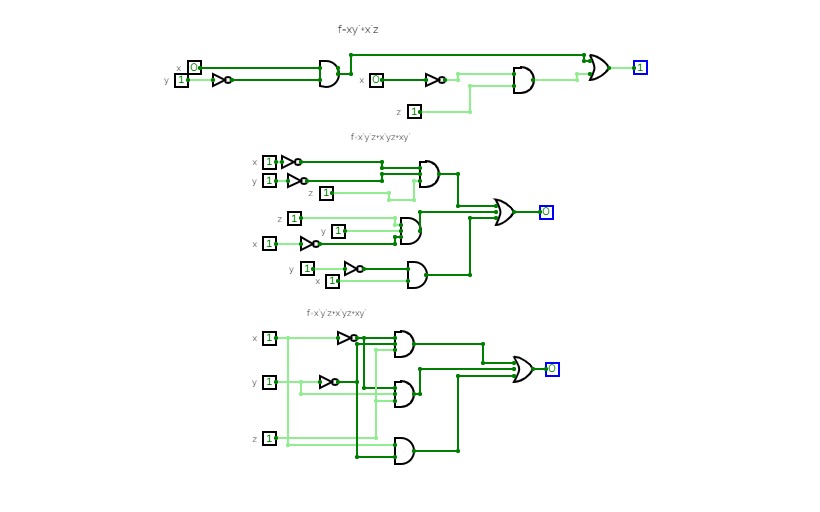

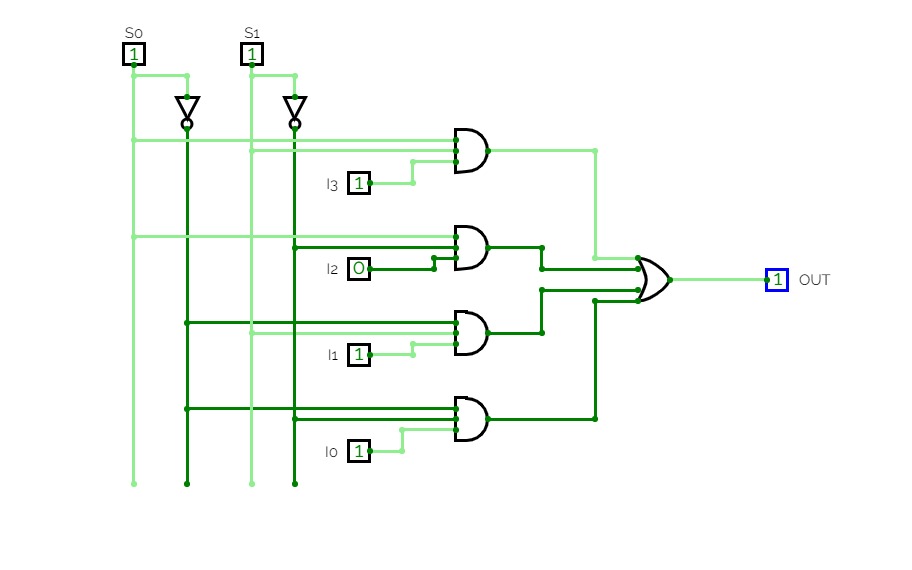

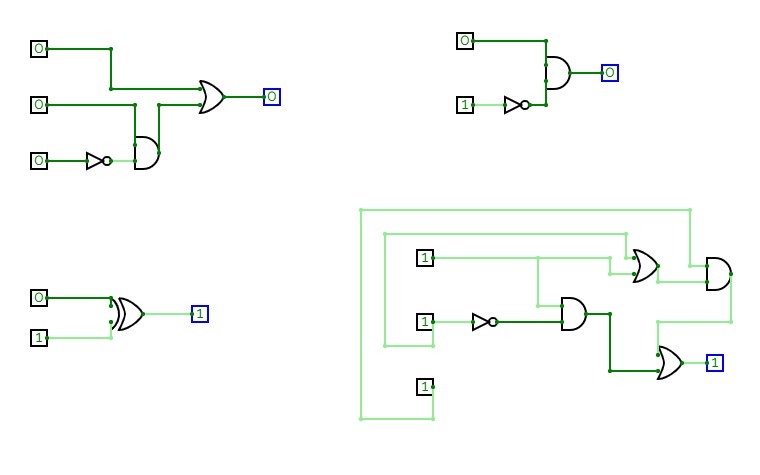

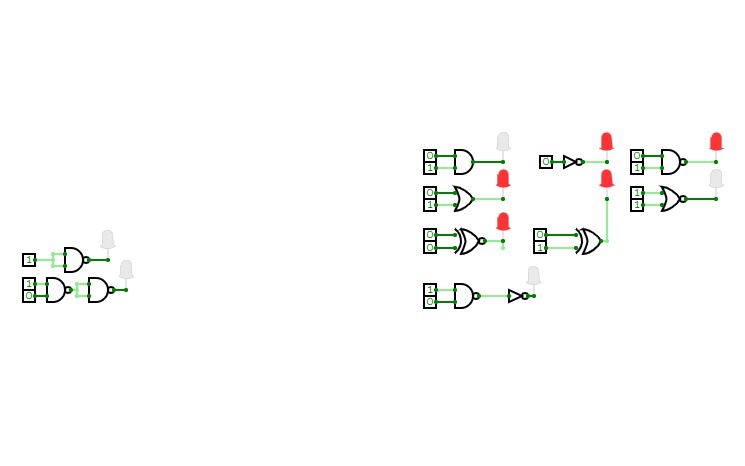

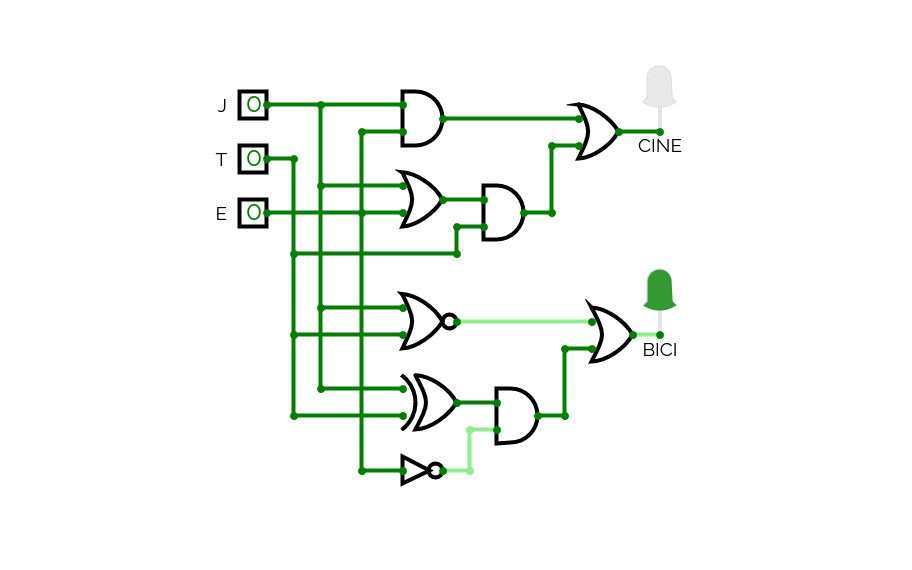

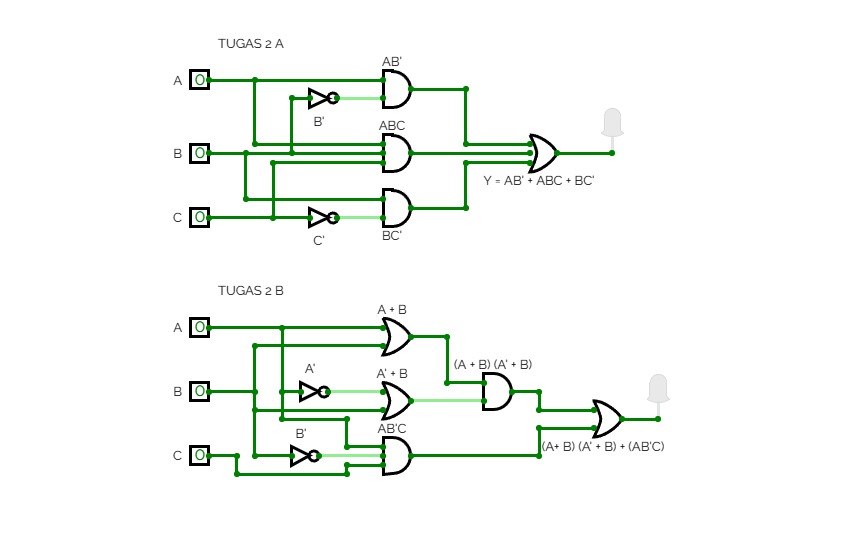

Clase 16 05112023

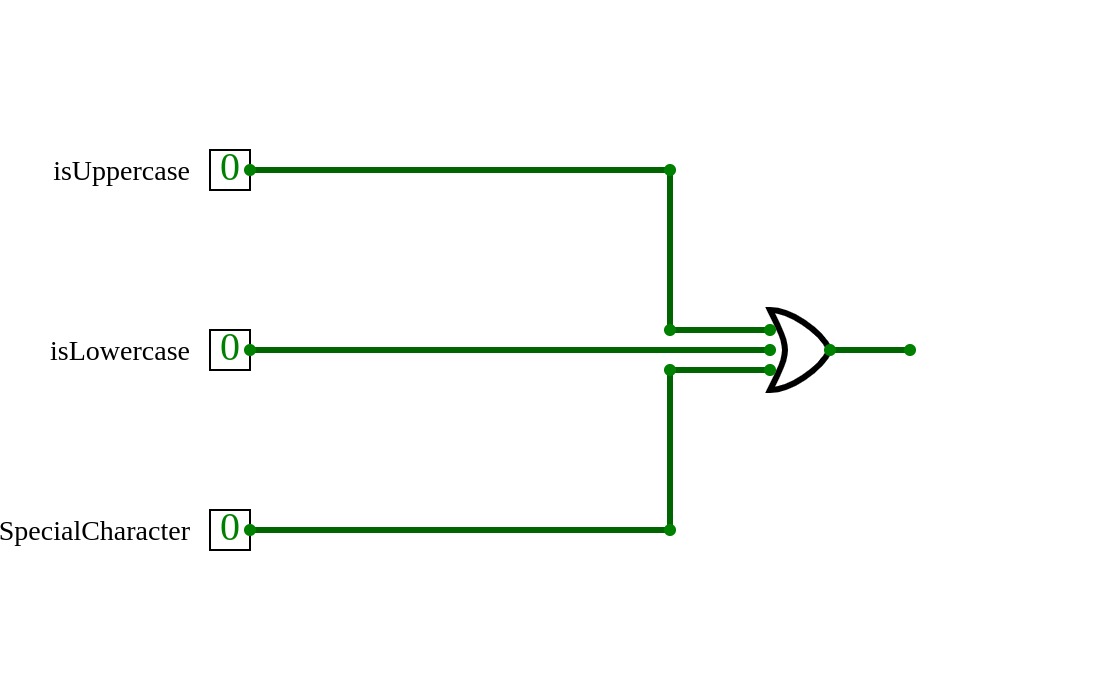

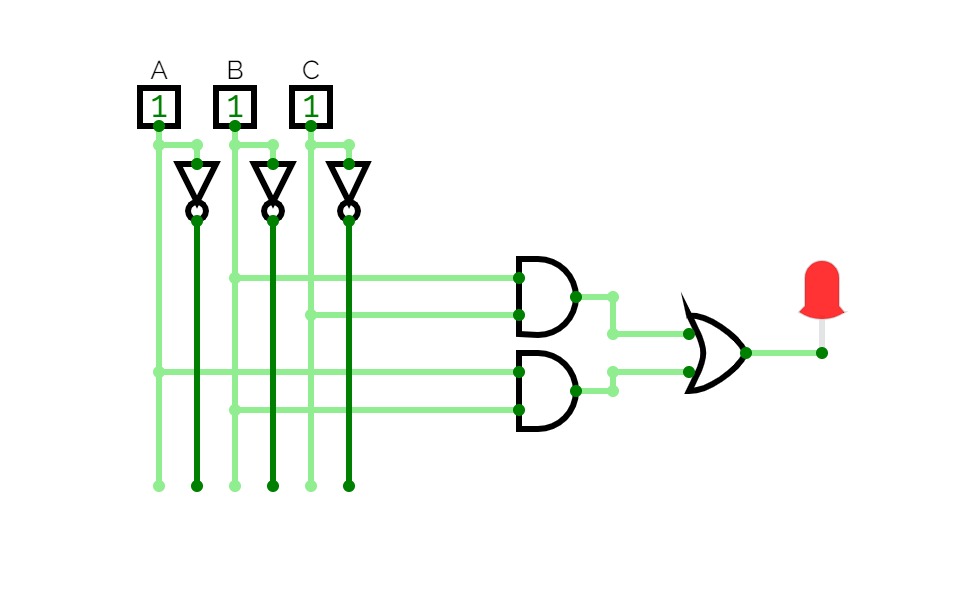

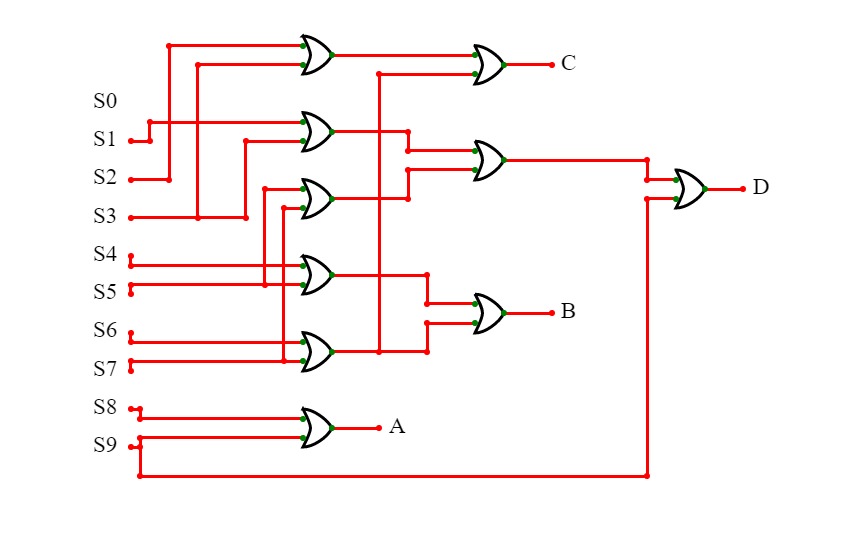

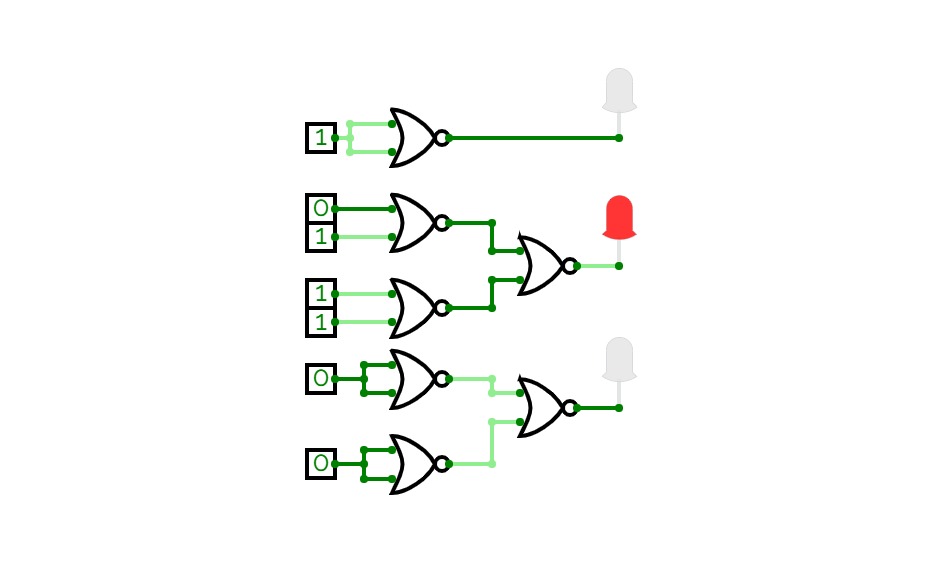

Clase 16 05112023Odd Voting Circuit

Odd Voting CircuitJuan, Tadashi y Eric se reúnen una vez a la semana para ir al cine o pasear en bicicleta. Para decidir que hacer, utilizan un circuito digital en el que, por medio de botones, votan y de manera democrática el circuito les indica lo que van a hacer. El objetivo consiste en diseñar un circuito lógico que calcule de forma automática la decisión que se debe tomar.

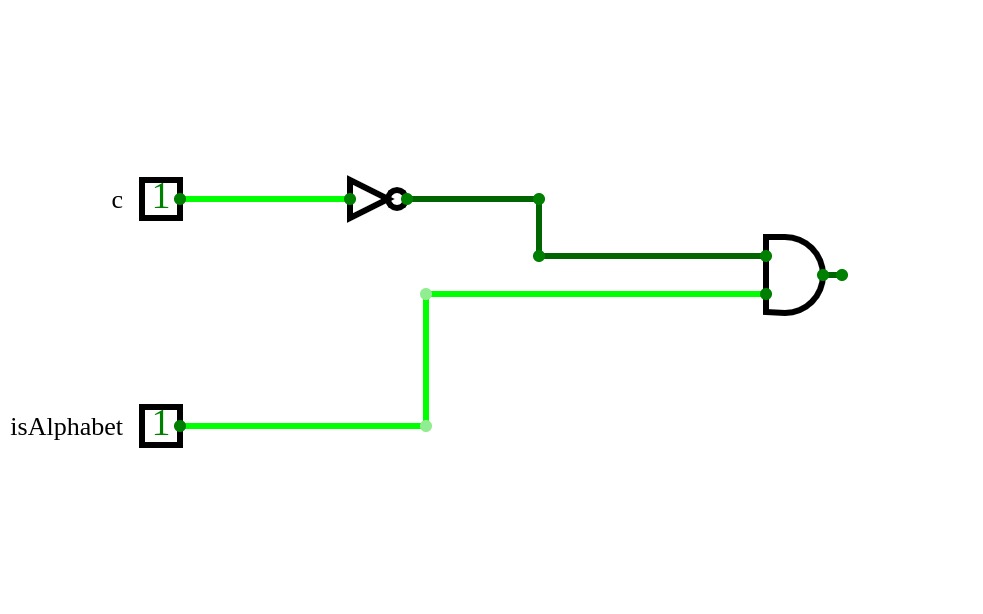

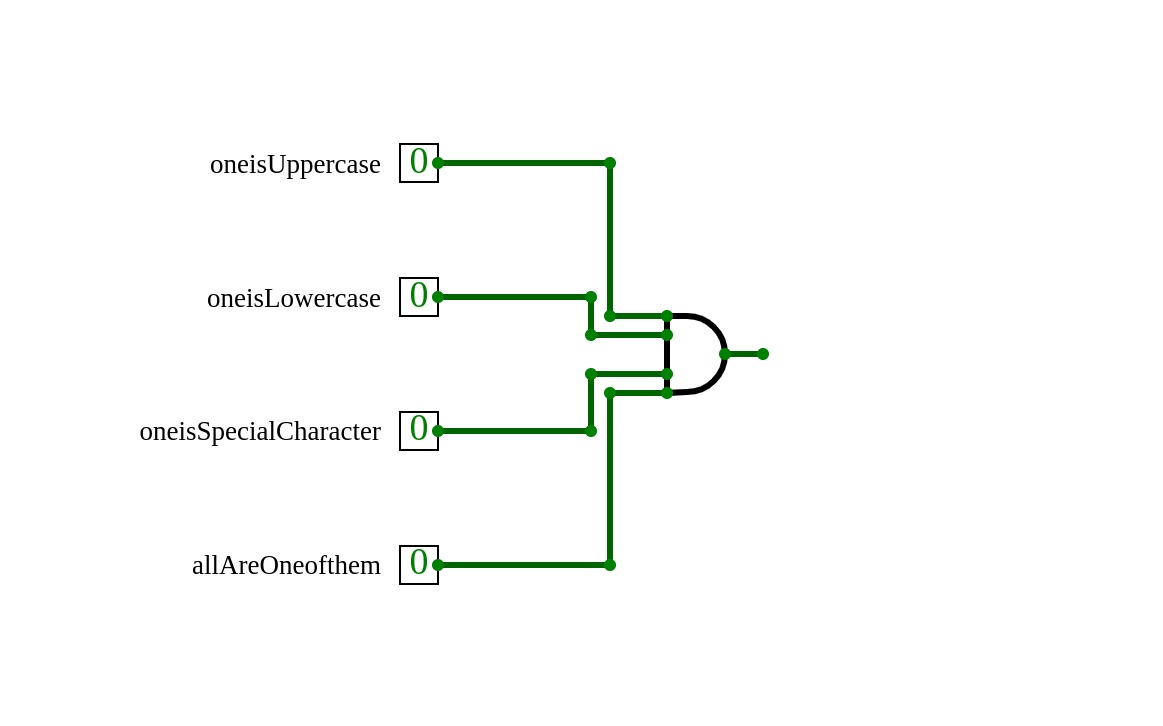

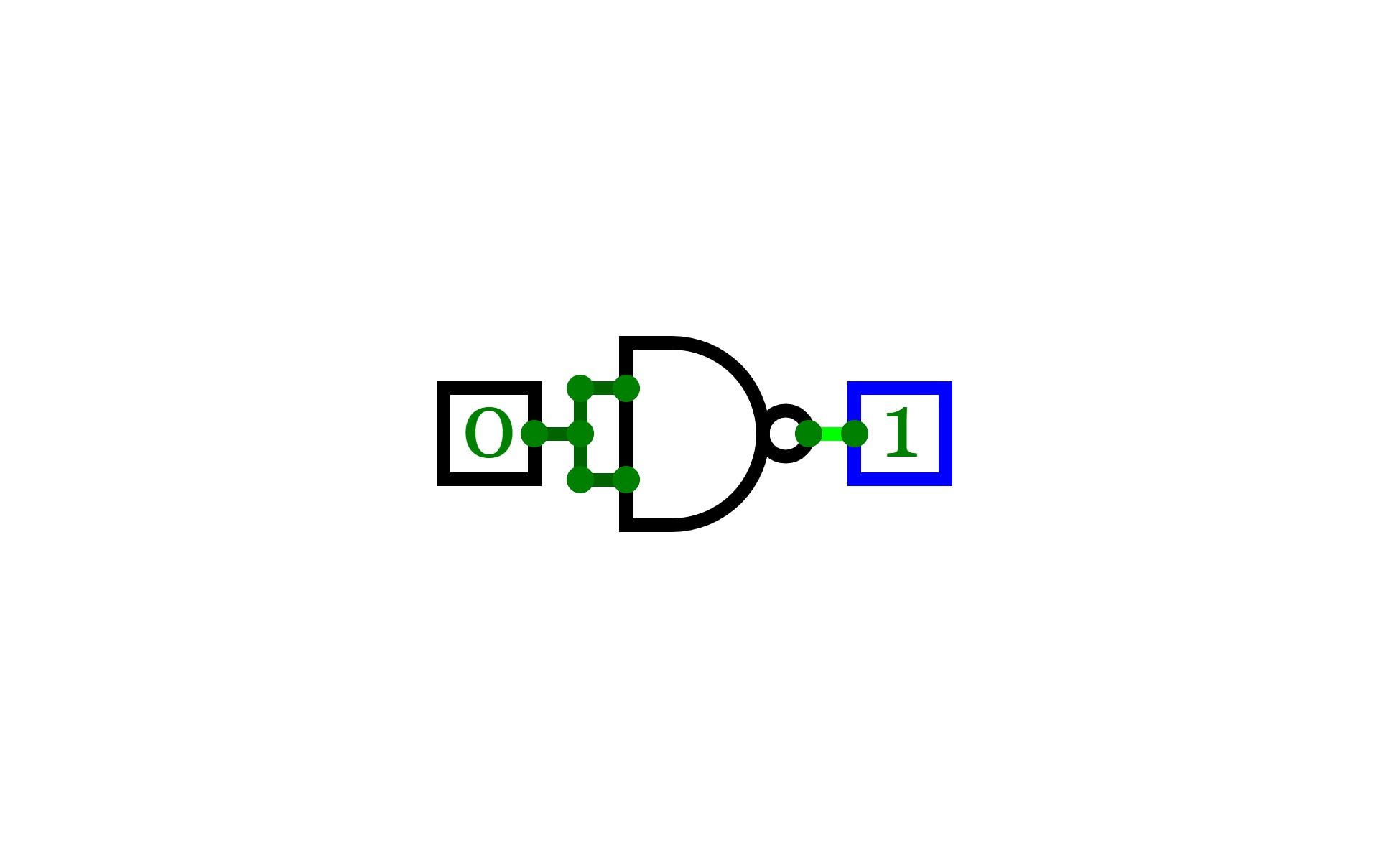

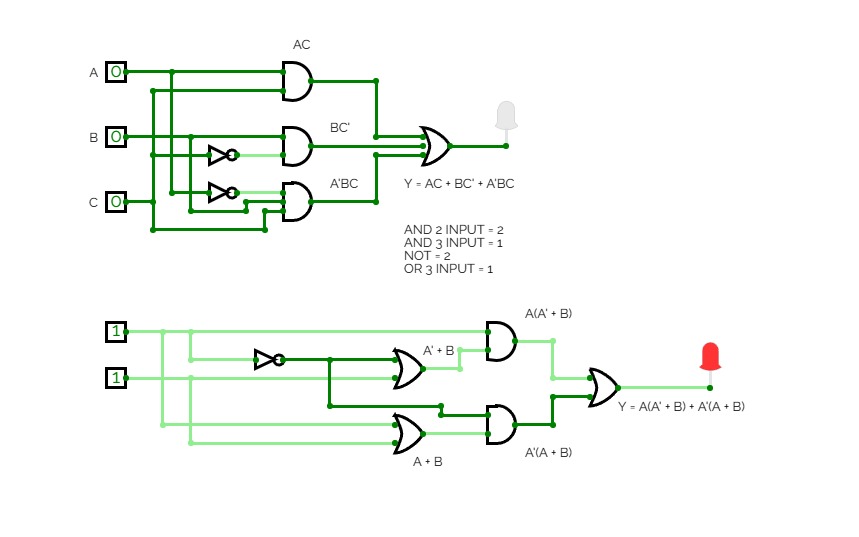

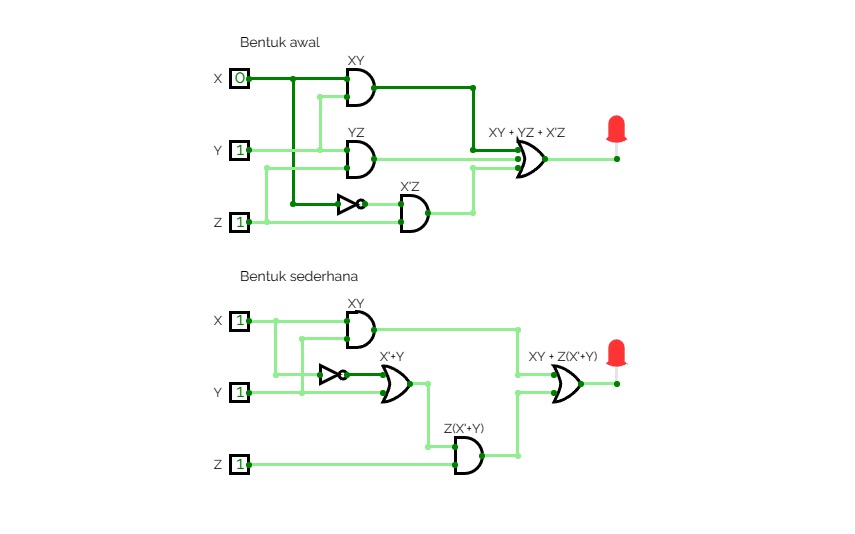

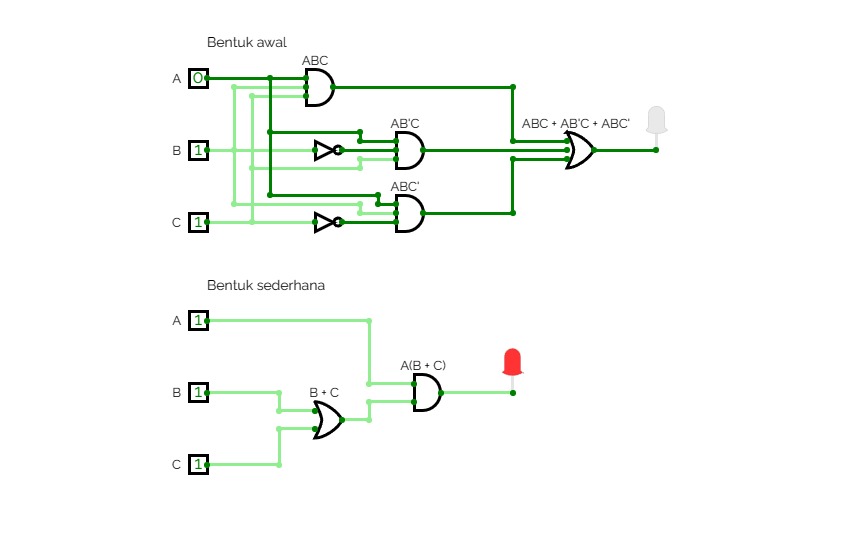

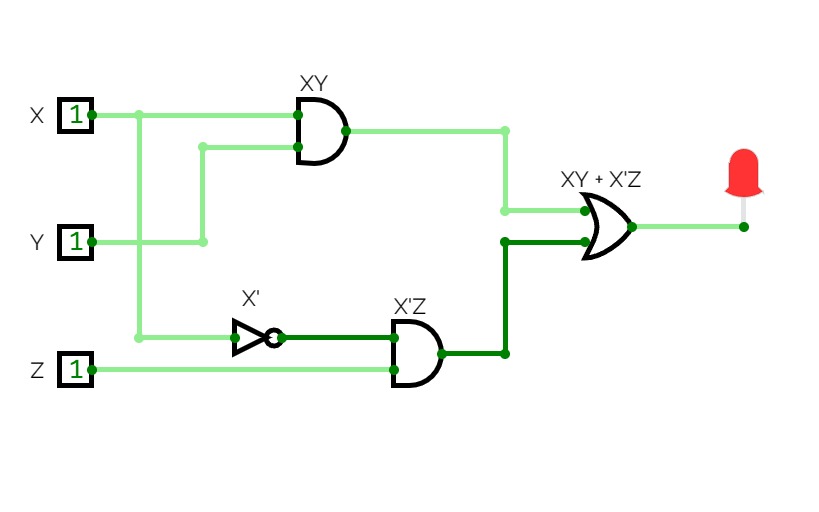

Logic Gate Challenges

Logic Gate ChallengesSimplify logic gates using truth tables and Karnaugh mapping to find a reduced SOP expression and circuit.