CyberTruck

CyberTruckRizan_Gate01

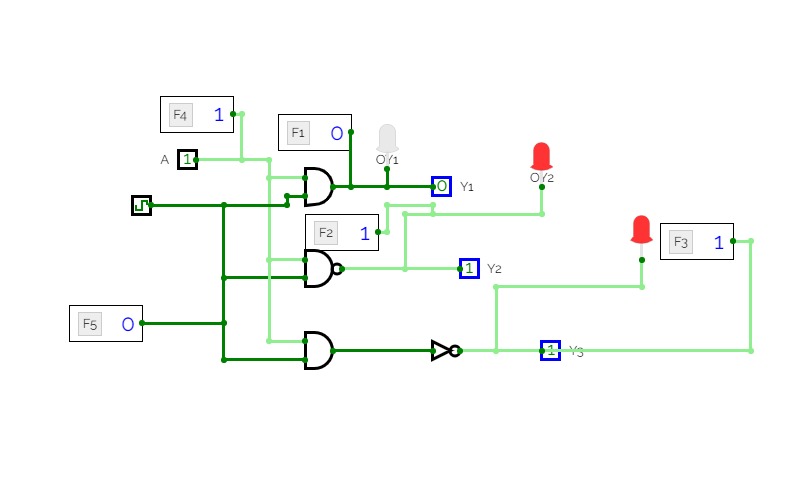

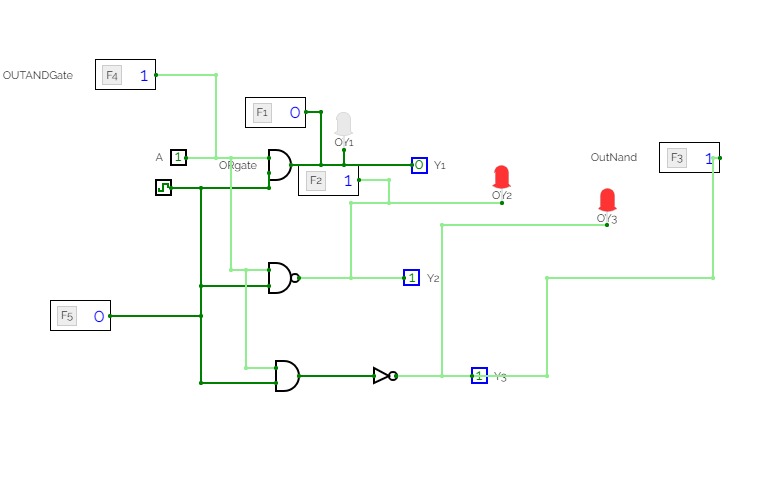

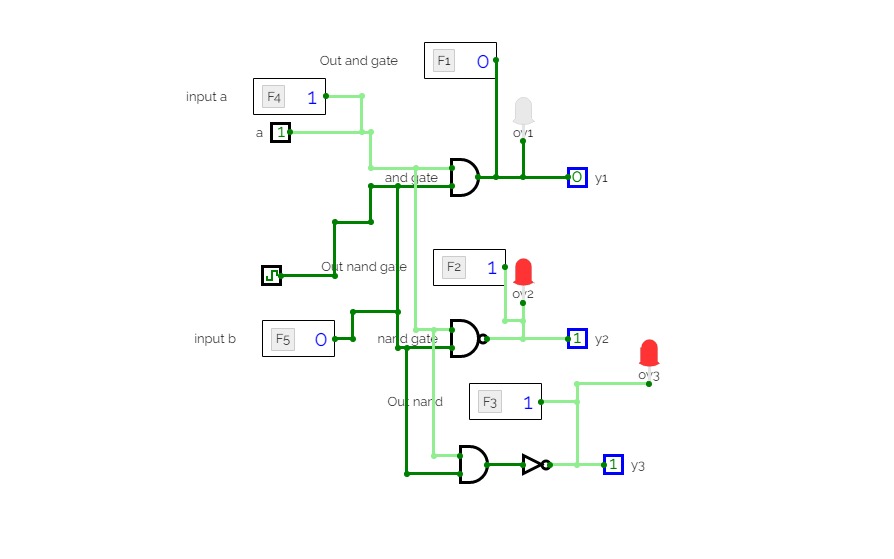

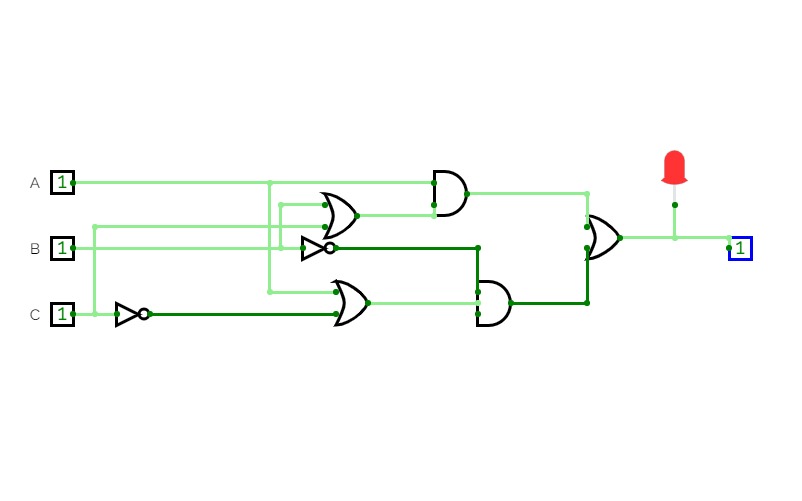

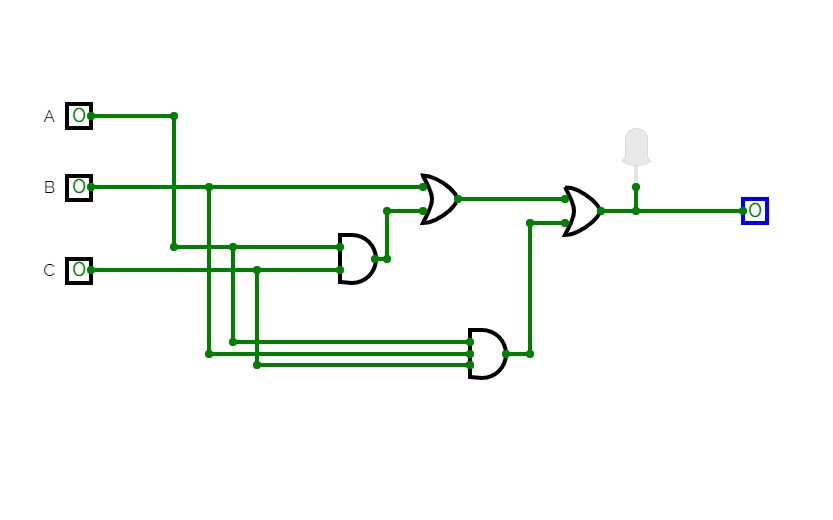

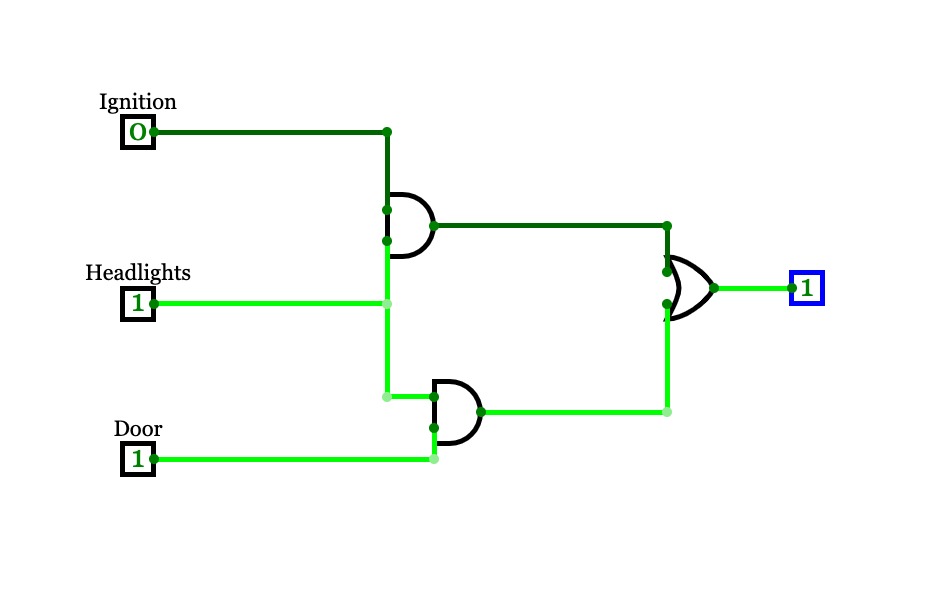

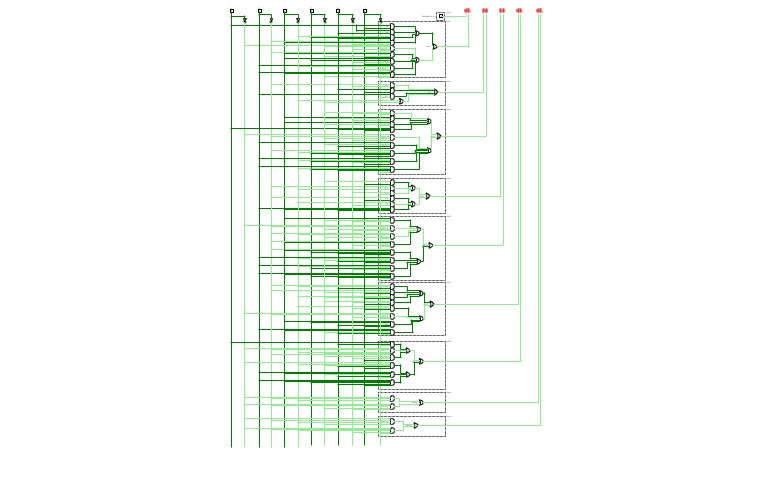

Rizan_Gate01AND & OR Gates

1.) Study of Logic Gates

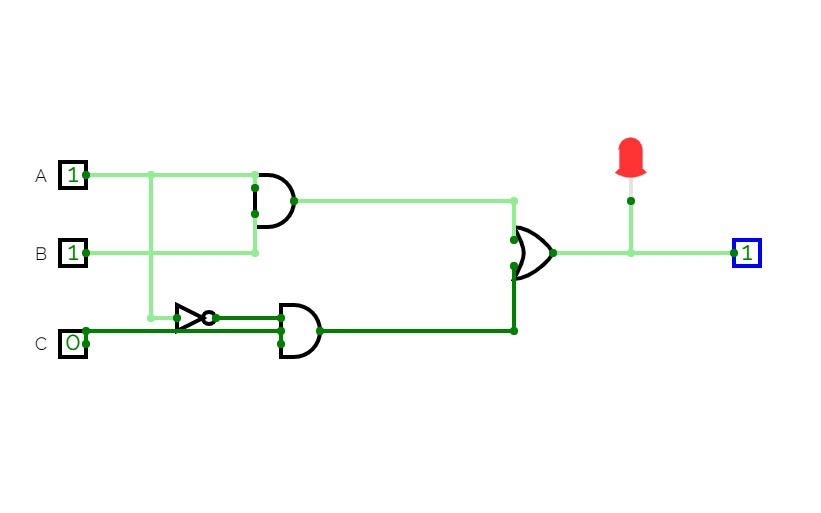

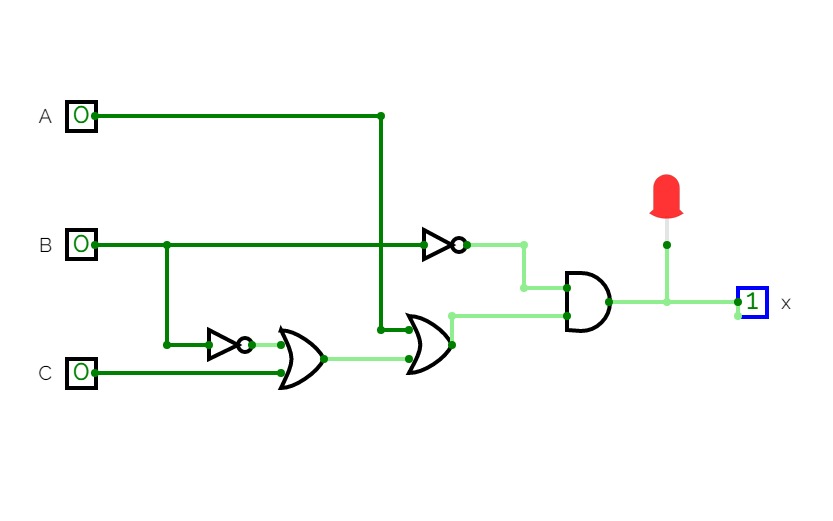

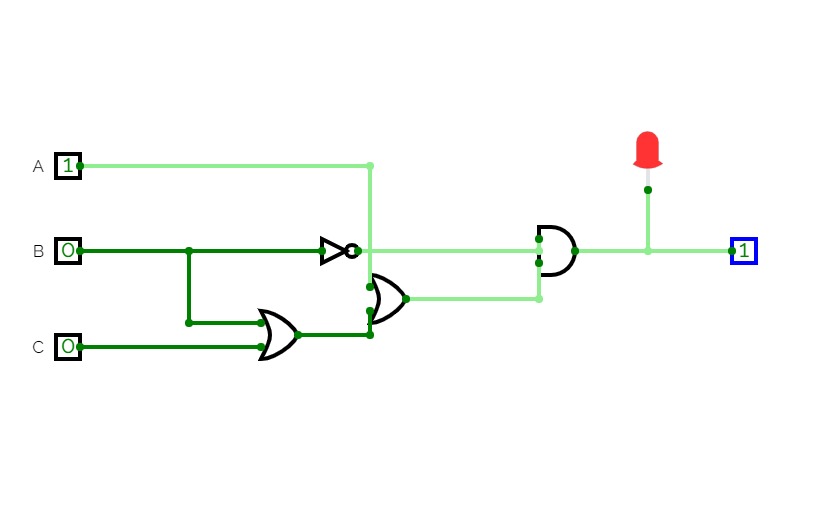

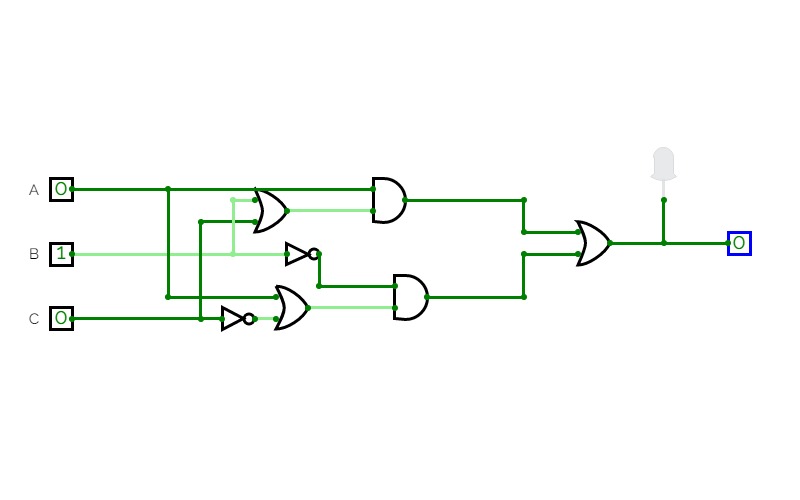

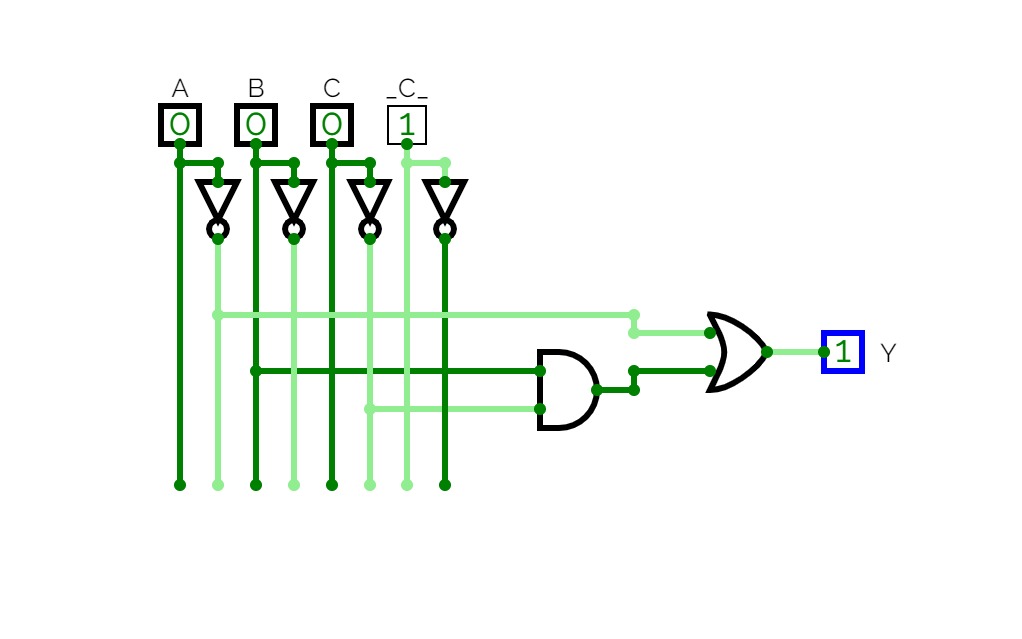

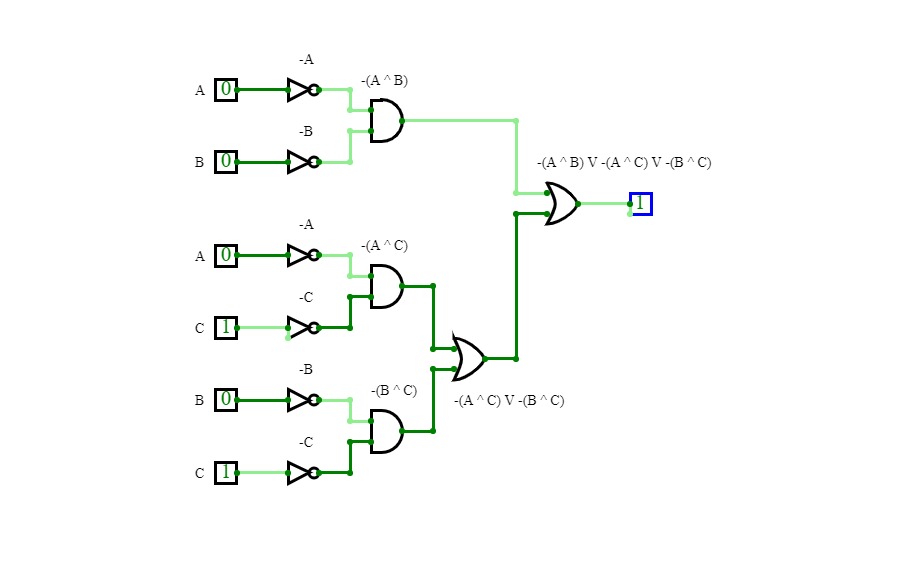

1.) Study of Logic GatesExperiment-3.1: De Morgan's Laws (1st Theorem) using the logic gates.

Experiment-3.1: De Morgan's Laws (1st Theorem) using the logic gates.Assignment 1

Assignment 1Morse Code

Morse CodeLogic

LogicLogic

LogicLogic

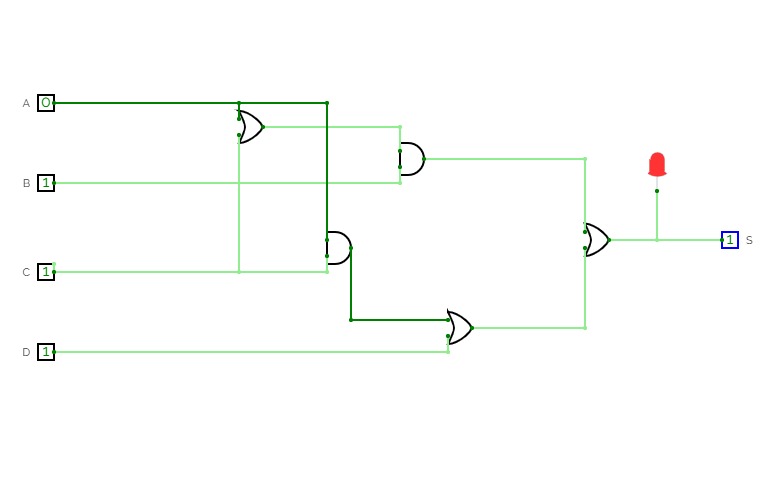

Logiclap1.1

lap1.1Lab1.1

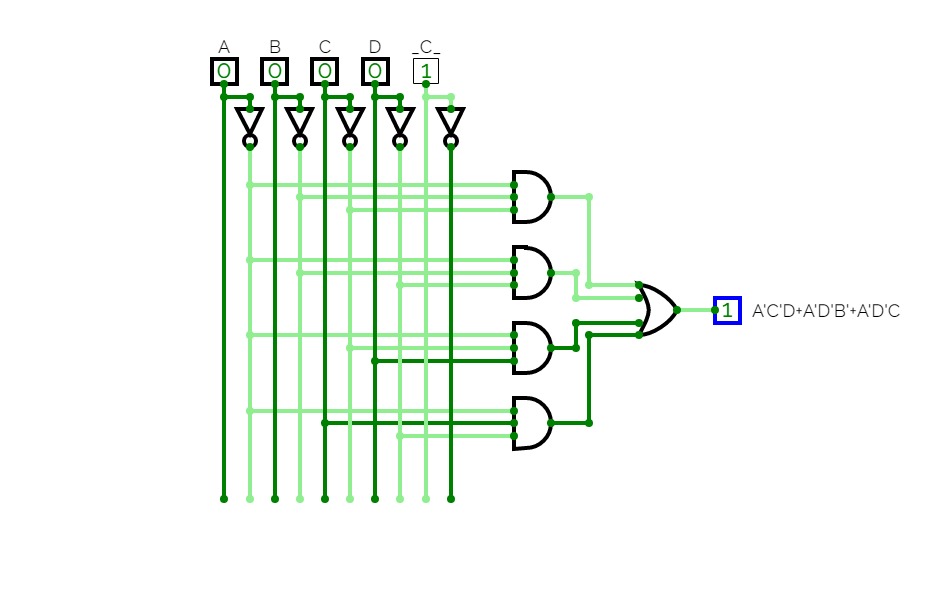

Lab1.1lap1.2

lap1.2Lab1.2

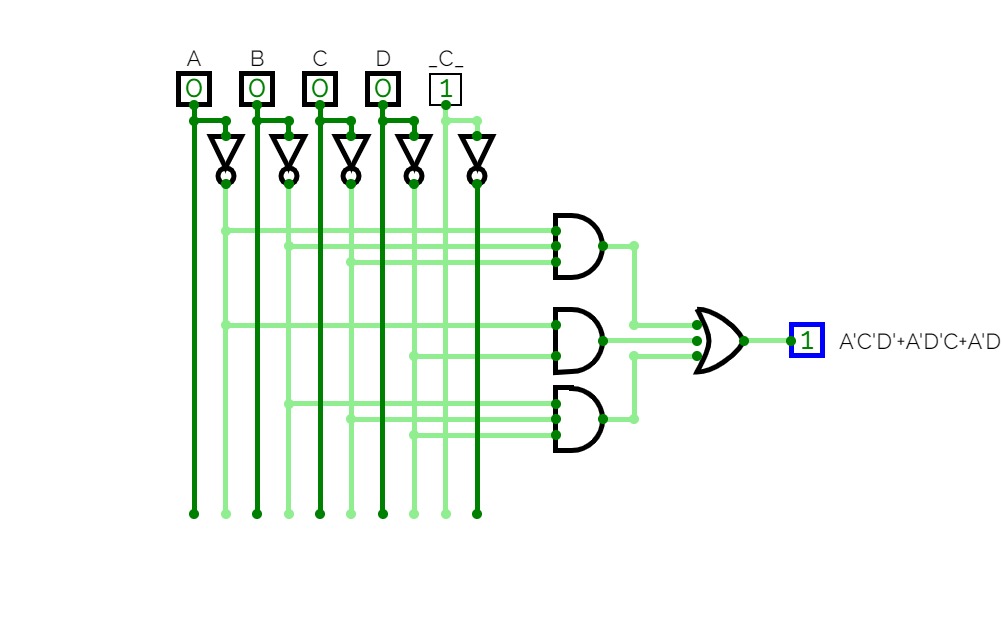

Lab1.2lap1.3

lap1.3Lab1.3

Lab1.3Iyh

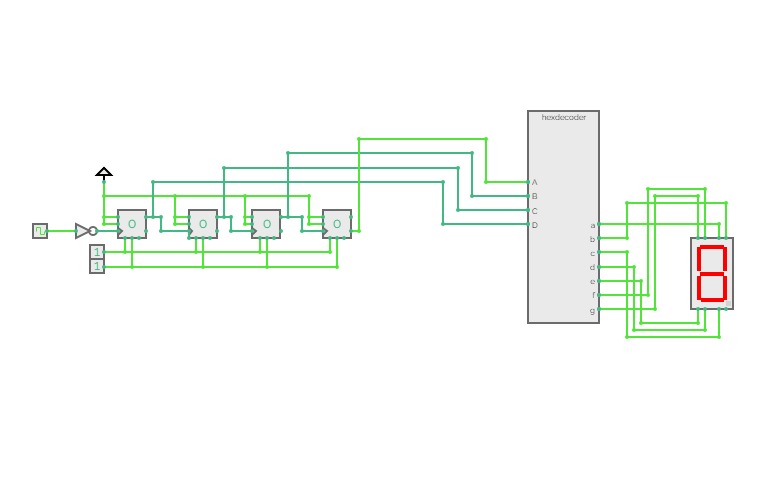

IyhLab2

Lab2Lab2.1

Lab2.1Lab2.2

Lab2.2Lab2.3

Lab2.3lap2

lap2Lab2.4

Lab2.4Lab2.5

Lab2.5lab3

lab3Lab3

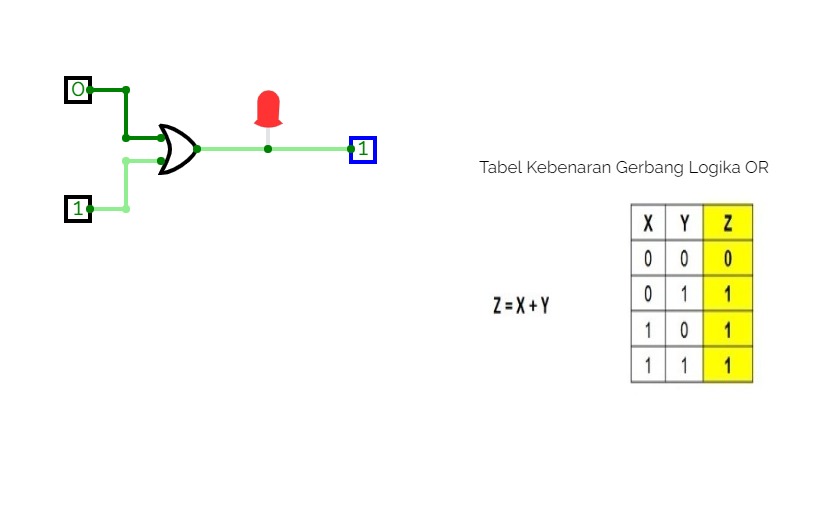

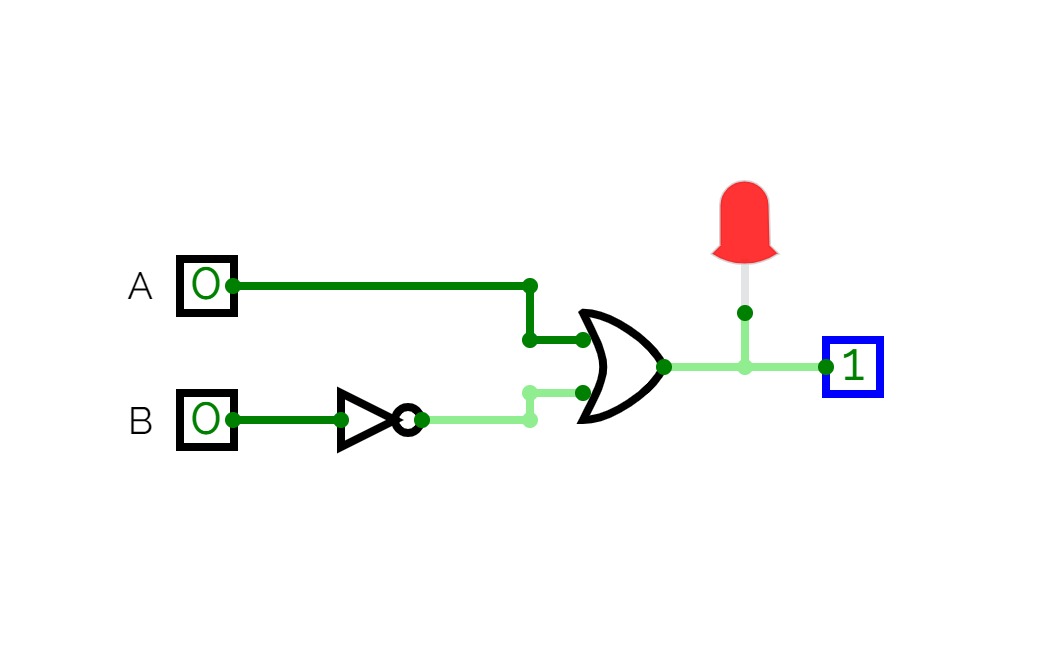

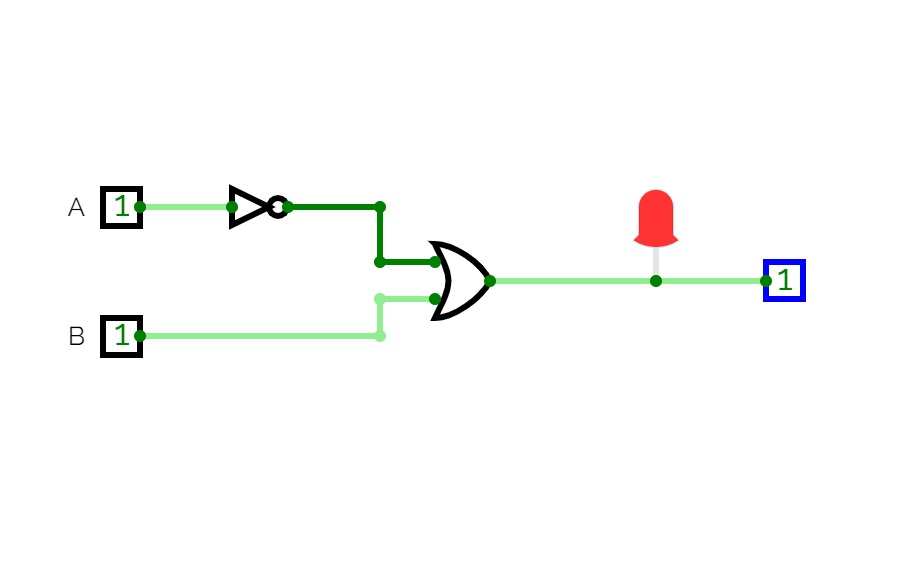

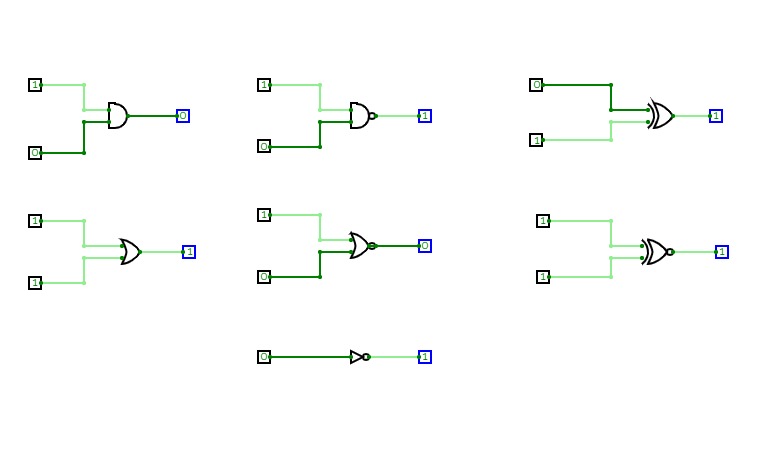

Lab3Gerbang Logika OR

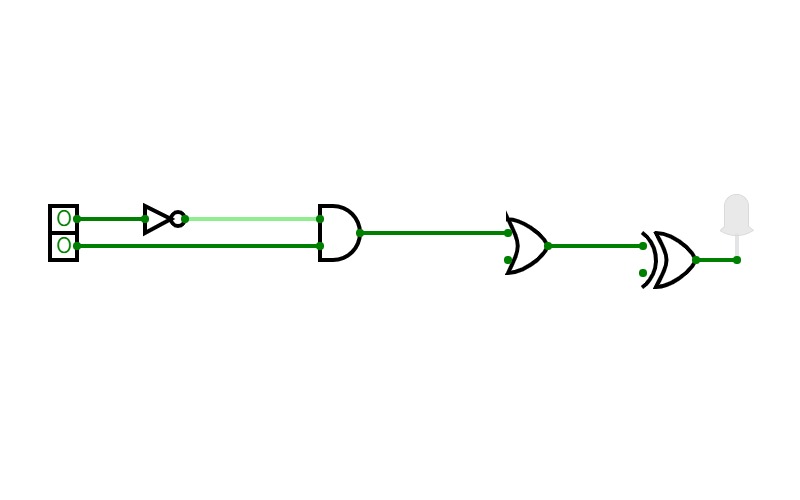

Gerbang Logika ORGerbang Logika OR ini memerlukan dua input untuk menghasilkan satu output. Gerbang Logika OR ini akan menghasilkan output 1 jika semua atau salah satu input merupakan bilangan biner 1. Sedangkan output akan menghasilkan 0 jika semua inputnya adalah bilangan biner 0.

Berikut adalah simulasi gerbang logika dasar OR :

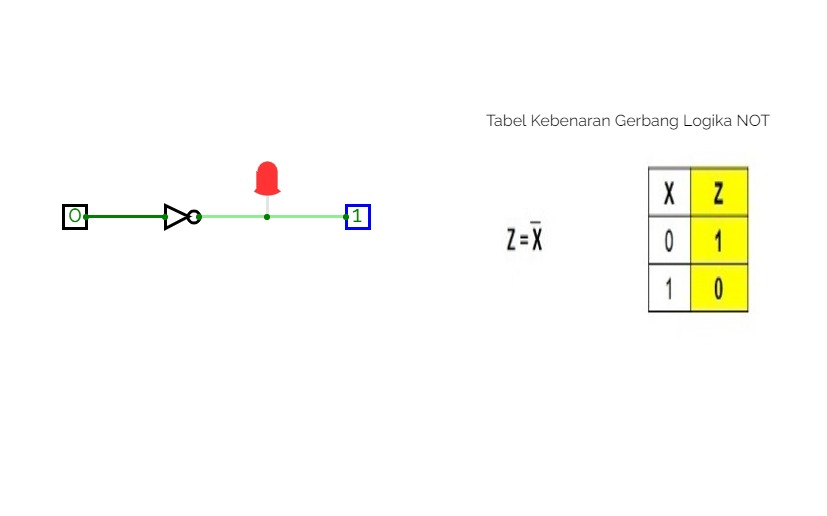

Gerbang Logika NOT

Gerbang Logika NOTGerbang Logika NOT ini berfungsi sebagai pembalik keadaan. Jika input bernilai 1 maka outputnya akan bernilai 0 dan begitu juga sebaliknya.

Berikut adalah simulasi gerbang logika dasar NOT :

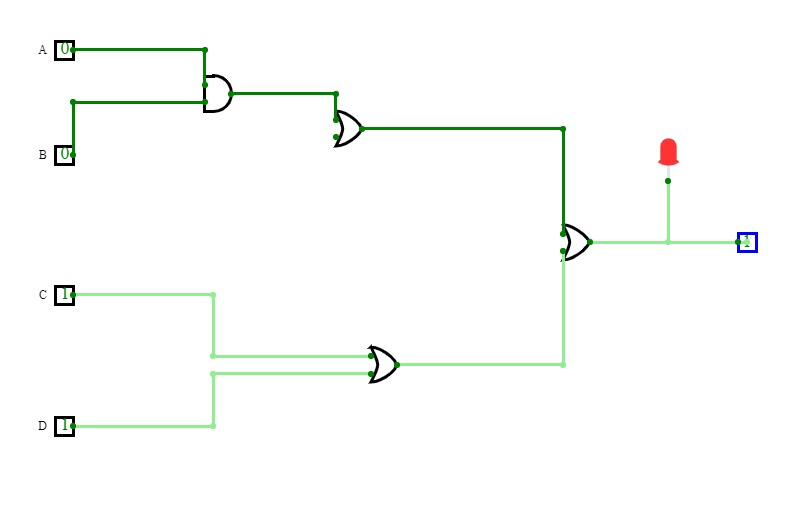

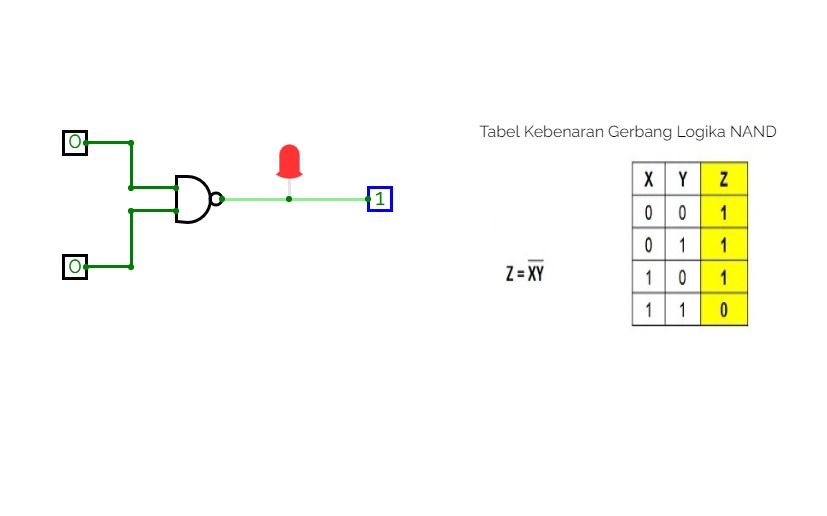

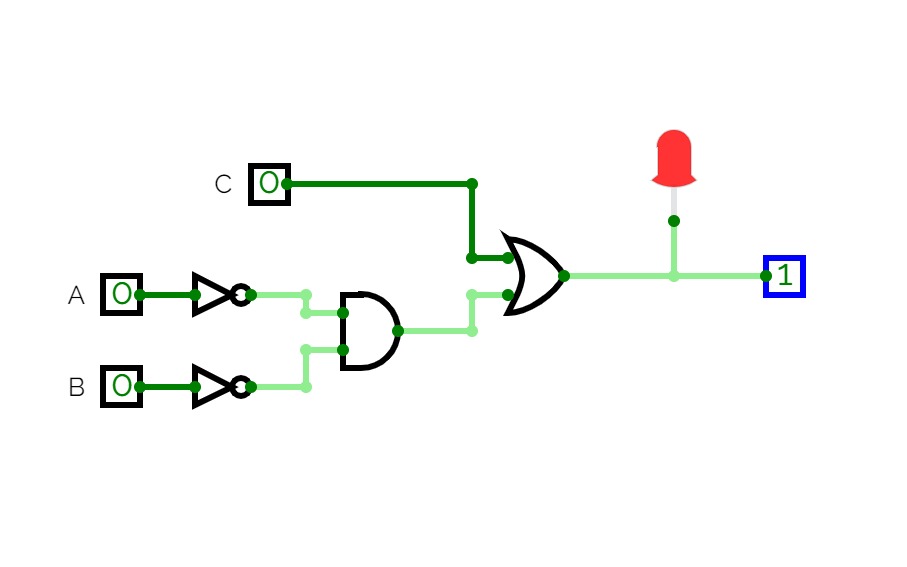

Gerbang Logika NAND

Gerbang Logika NANDGerbang Logika NAND ini adalah gabungan dari gerbang AND dan gerbang NOT. Karena itu output yang dihasilkan dari gerbang NAND ini adalah kebalikan dari gerbang AND.

Berikut adalah simulasi gerbang logika dasar NAND :

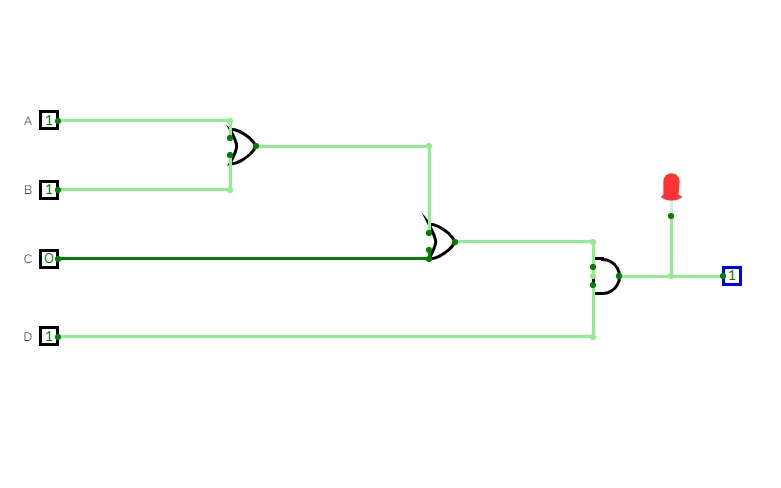

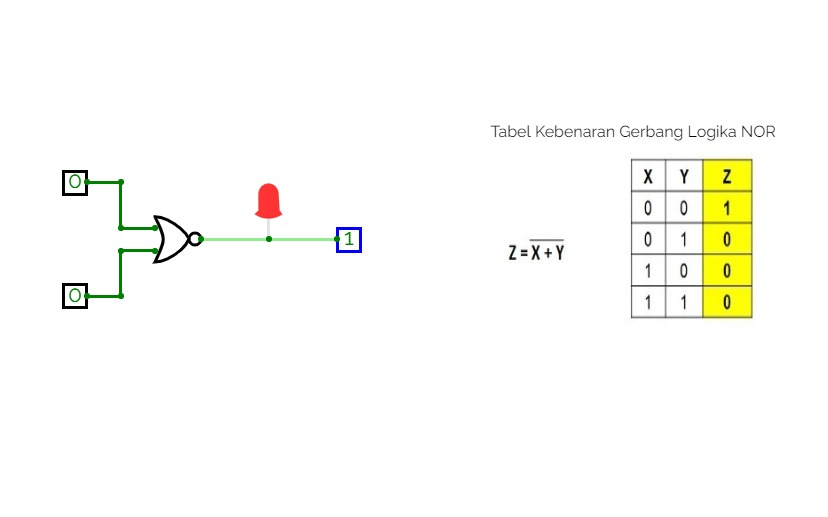

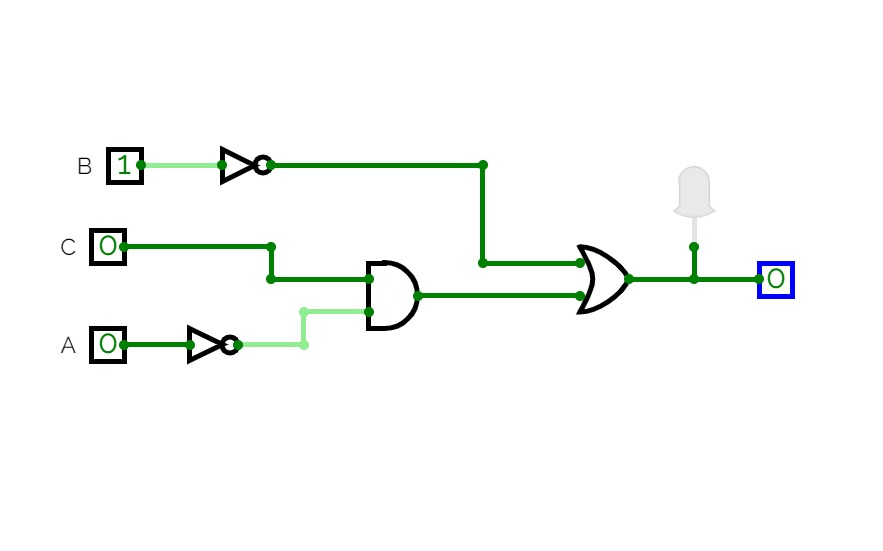

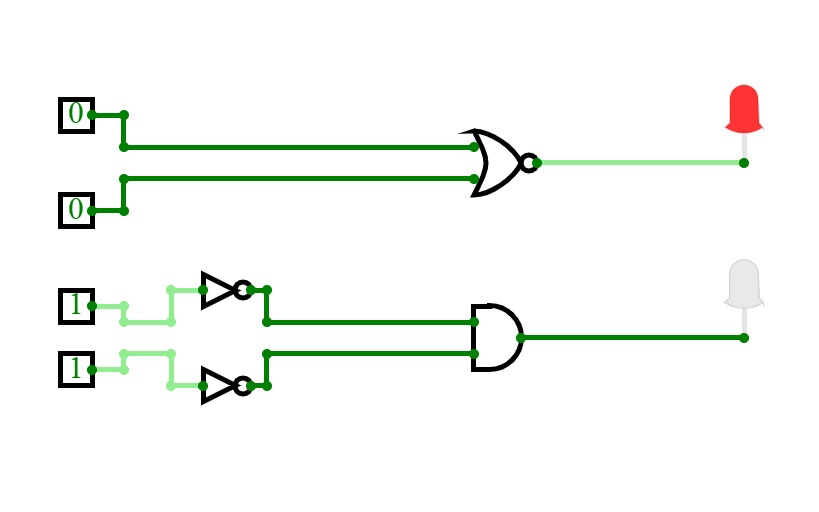

Gerbang Logika NOR

Gerbang Logika NORGerbang Logika NOR ini adalah gabungan dari gerbang OR dan gerbang NOT. Sehingga output yang dihasilkan dari gerbang NOR ini adalah kebalikan dari gerbang OR.

Berikut adalah simulasi gerbang logika dasar NOR :

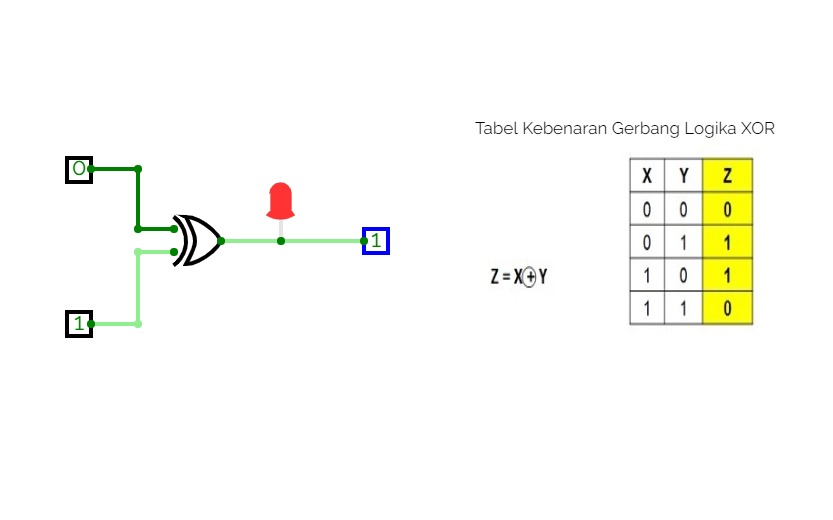

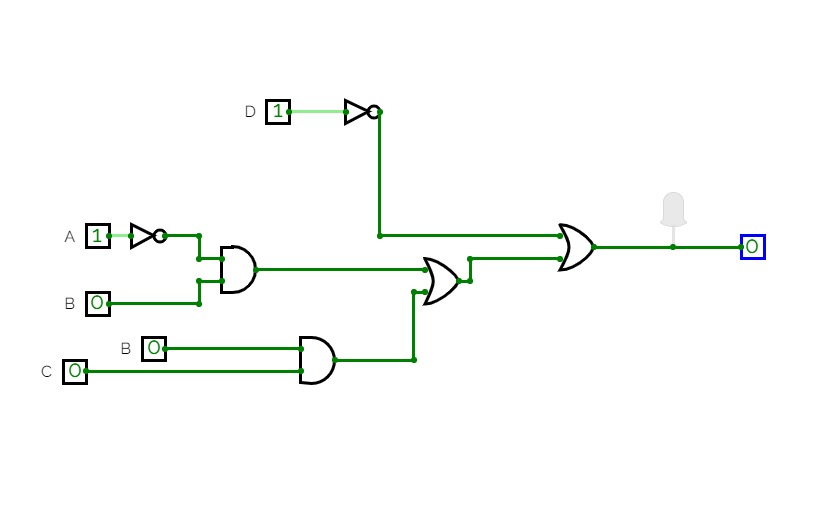

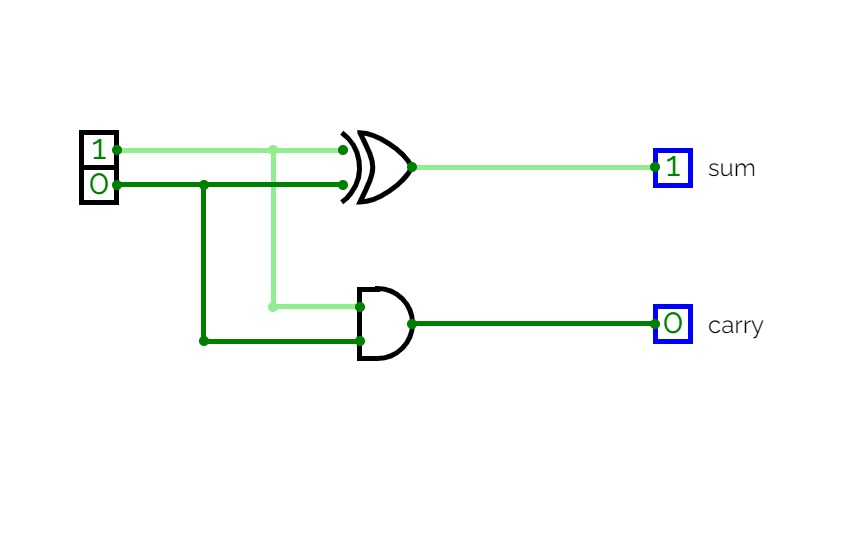

Gerbang logika XOR

Gerbang logika XORGerbang Logika XOR ini memerlukan dua input untuk menghasilkan satu output. Jika input berbeda (misalkan: input A=1, input B=0) maka output yang dihasilkan adalah bilangan biner 1. Sedangkan jika input adalah sama maka akan menghasilkan output dengan bilangan biner 0.

Berikut adalah simulasi gerbang logika dasar XOR :

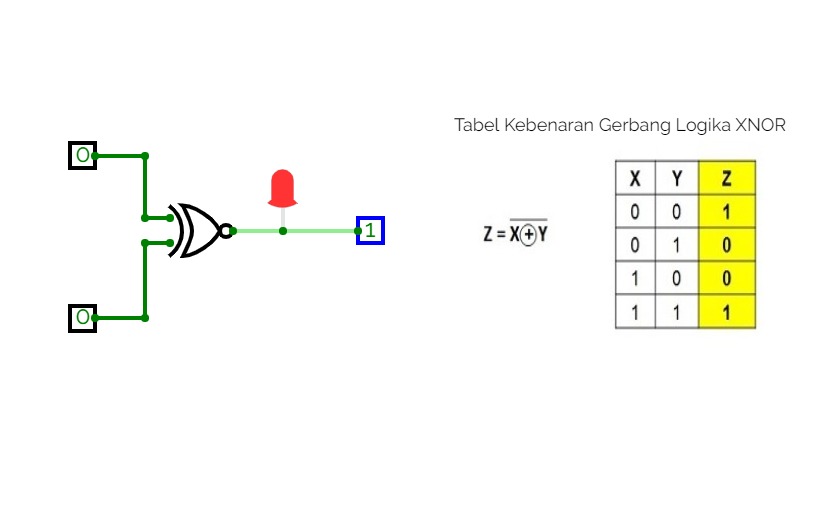

Gerbang Logika XNOR

Gerbang Logika XNORGerbang Logika XNOR ini memerlukan dua input untuk menghasilkan satu output. Jika input berbeda (misalkan: input A=1, input B=0) maka output yang dihasilkan adalah bilangan biner 0. Sedangkan jika input adalah sama maka akan menghasilkan output dengan bilangan biner 1.

Berikut adalah simulasi gerbang logika dasar XNOR :

LAP3

LAP3lap4

lap4Untitled

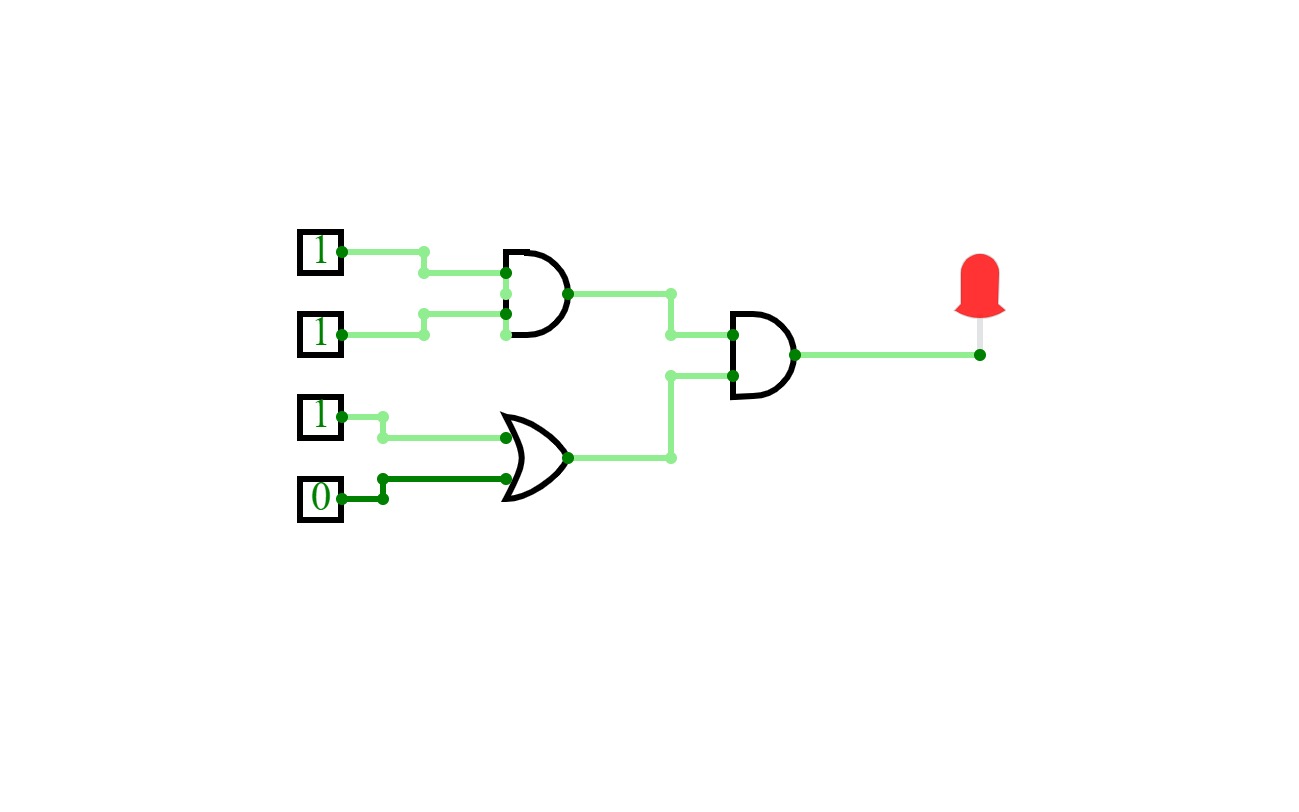

UntitledFinal 1

Final 1final test

final testFinal1.2

Final1.2Final 1.3

Final 1.3Final2.1

Final2.1Final2.2

Final2.2Final2.3

Final2.3Final3.2

Final3.2Final3.1

Final3.1Final

FinalTest

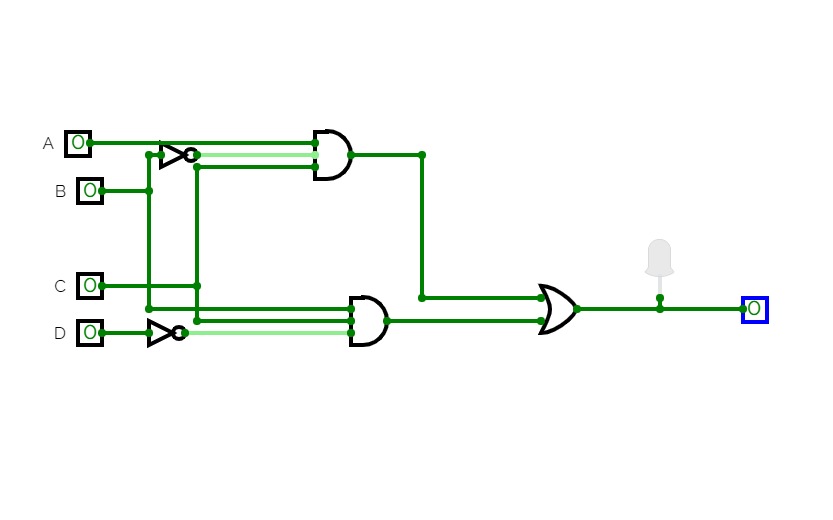

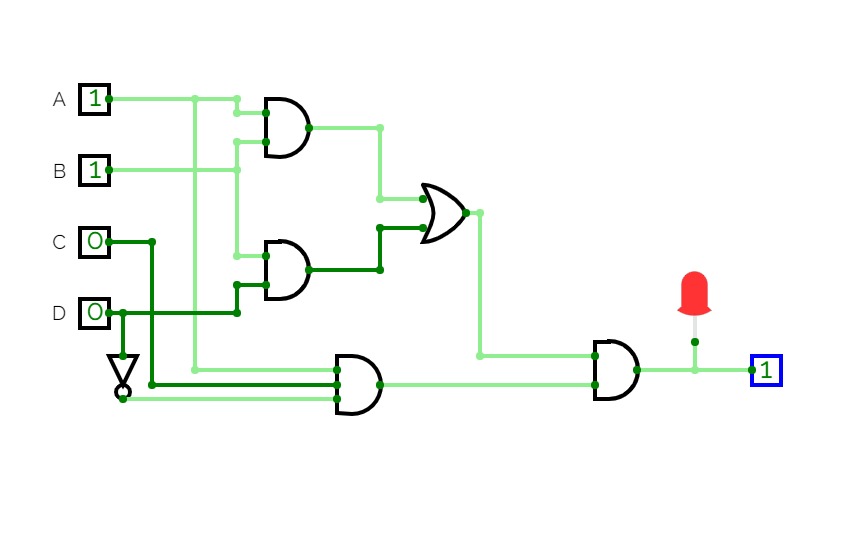

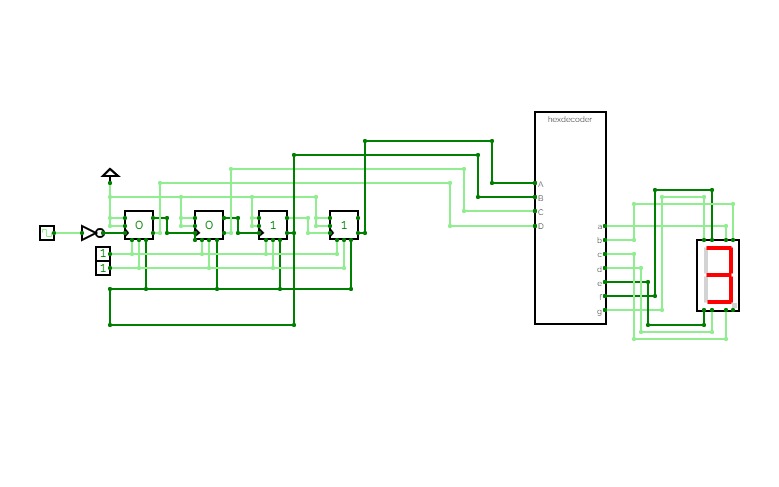

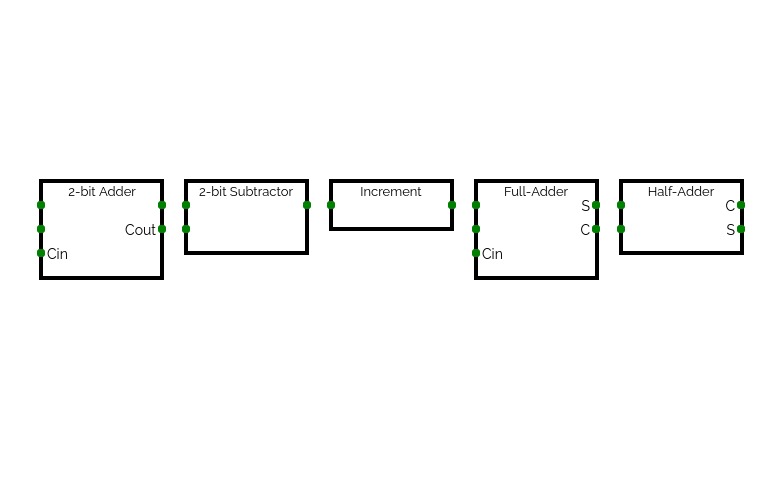

Testfull adder

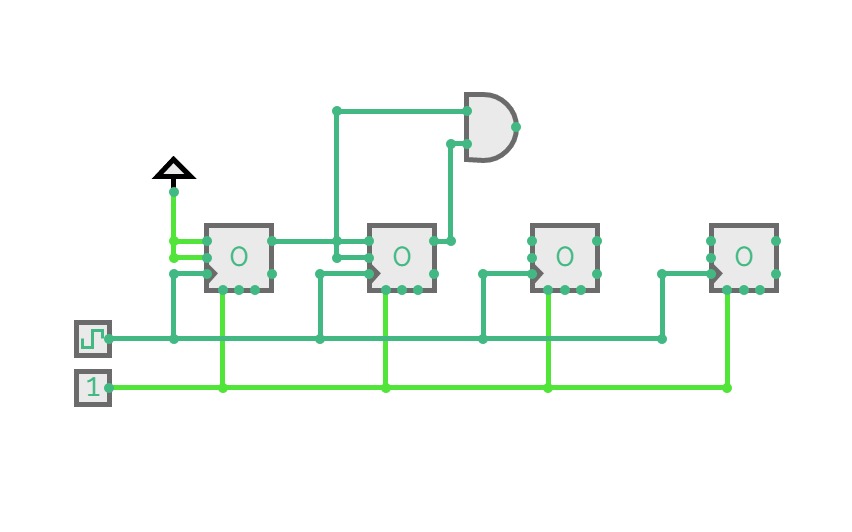

full adderhalf adder

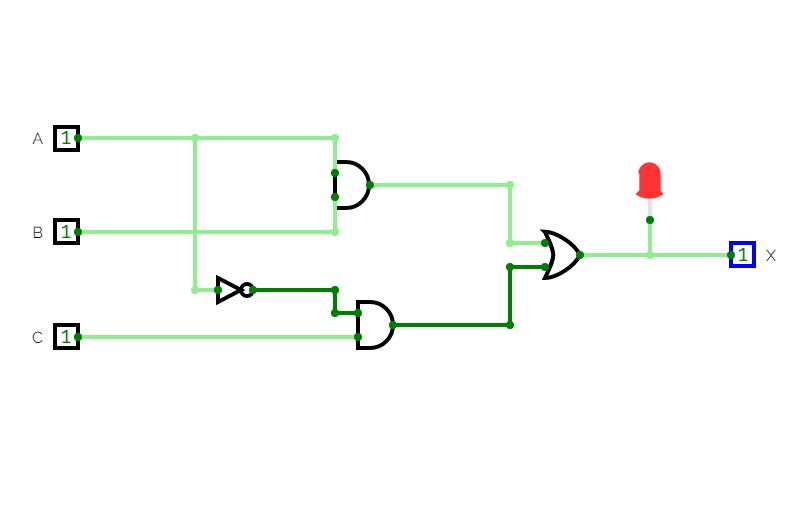

half adderSimple Logic Gate Arithmetic

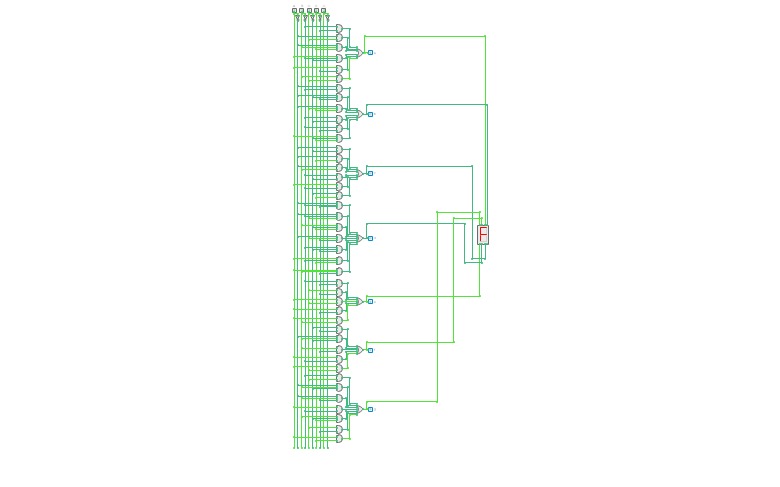

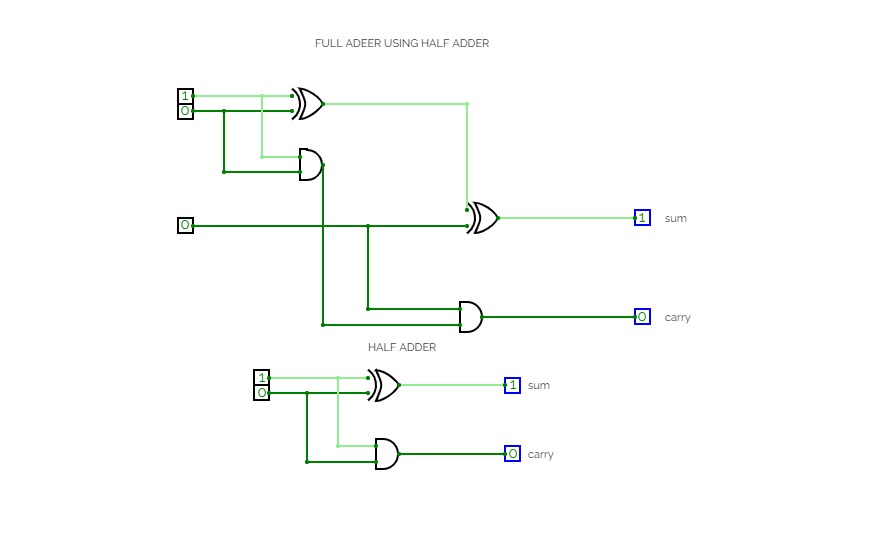

Simple Logic Gate Arithmetic3*8 Decoder

3*8 DecoderFull Subtractor

Full SubtractorA full subtractor is a digital circuit that subtracts two binary bits, accounting for a borrow input, and produces a difference and a borrow output. It has three inputs (minuend, subtrahend, borrow-in) and two outputs (difference and borrow-out).

1-Bit ALU

1-Bit ALUA 1-bit ALU performs basic arithmetic and logic operations on single-bit inputs.

.png)