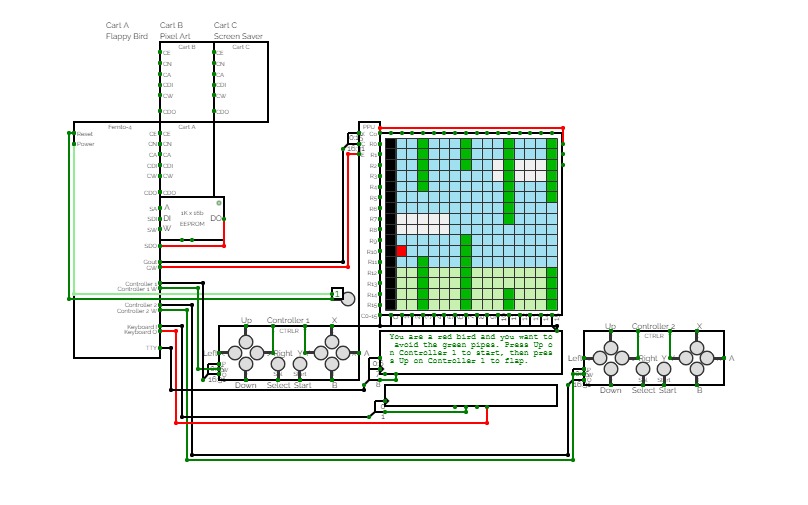

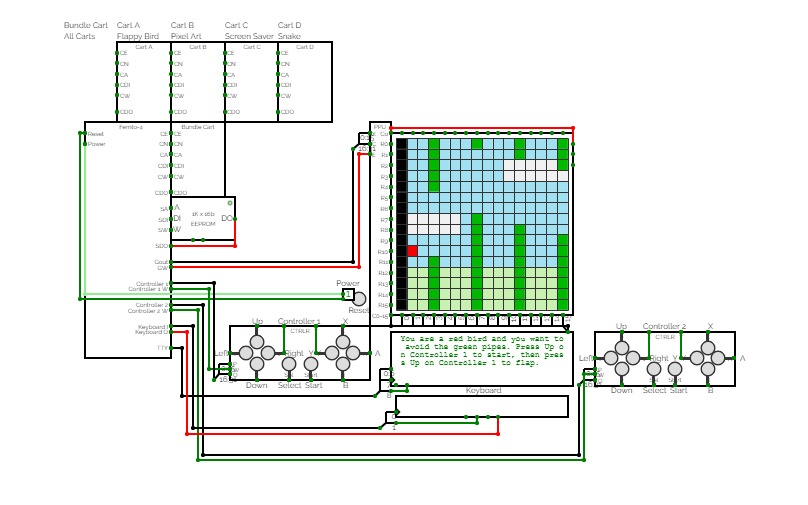

Femto-4v1.2 (Computer)

Femto-4v1.2 (Computer)Latest versions of the 256-Series, including the Femto-4:

https://circuitverse.org/users/4699/projects/256-series

A 16-bit computer/maybe console inspired thing, the Femto-4. This is a fork from the main branch to keep a semi-functional version around. This project was started around November 2020.

Currently runs:

Cart A: Flappy Bird

Cart B: Some Pixel Art

Cart C: Screensaver

Assembler:

https://repl.it/@Sanderokianstfe/Femto-4-Assembler#DeveloperGuide.txt

Features:

Immediate, direct and indirect memory access

Jumps and conditional Jumps

16-bit address space

Switchable Memory Banks, allowing for a standard Cart to hold up to 512kx16b of data

An ALU capable of logical operators, addition, subtraction and shift left

Easy to add to buses

"Fast Execution" - Can run more than one instruction per clock cycle

16x16 pixel display

Inputs, both "controllers" and keyboards

"Faster Execution" - Runs instructions on both edges of the clock pulse

Random number generator

Text outputs

An ALU capable of shift right, multiplying, dividing, and other specialised functions

Stack

Assembler (written in an external program)

Save memory

Two pre-written carts to play with

Fixed code controlled graphics updates

Made Bootloader clear TTY, Keyboard, and Controller Pushed

Fixed Register ALU instructions

Updated Cart A and Cart B to make use of the Register ALU instructions

Updates:

Another pre-written cart to play with

Updated the sprite-art cart to respond to the start button on both controllers.

Will have:

More pre-written carts

Bug fixes

Do fork the project and write your own code for it! If you want more information on how to do so read the Developer Guide in the assembler.

Note:

The Flappy Bird high score is mine. If you want to save your own scores permanently you will have to fork it.

General Architecture:

The Femto-4 has variable length instructions that are comprised of multiple 16-bit chunks. First the OP Code of the instruction is read, and then depending on the OP Code, additional pieces of data may be read for the operands. This allows execution to become incorrectly offset, which can lead to the execution of garbage if the PC is jumped to an incorrect address. This is usually fine, since the OP Code space is so empty that the data will likely be passed one at a time until the next valid instruction. Data is read through the standard data retrieval system (which is handy since its design is so universal and easy to add to) making this architecture a Von Neuman architecture as opposed to a Harvard architecture, like my previous, worse, computer. The MAR always specifies the address being read to or written from, whilst the MDR always holds the data being written. Data from the data out bus can be written to any special register during the instruction. OP Codes and operands are all 16-bits, which is a bit wasteful in terms of OP Code usage, however it was easier to implement this way, and so that is what I went with (and there are a lot of ALU processes).

Memory Mapping:

The 16-bit address space of the Femto-4 is memory mapped, with all data being stored somewhere in the address space. The last 48kx16b of memory (all addresses starting with 01, 10, or 11) are dedicated to the cart memory. This is where the interchangeable program would be stored, allowing programs to be easily changed by changing carts. (However, currently there are currently only two carts). The carts have 32 16kx16b EEPROM/RAM chips, which can be switched between during execution by writing to address 00cc. This gives each cart 512kx16b of memory to play with. In theory, additional memory can be added in a cart by creating a similar system on the inside of the cart, which would allow it to swap between even more EEPROM/RAM chips. The initial 16kx16b are therefore mapped to everything else, including a fixed "work" RAM chip that cannot be switched out, the bootloader, the PPU data, general use registers, the, stack, inputs, outputs, and special use registers.

"Fast Execution":

Execution at the fastest clock speed (one pulse every 50ms, or 20Hz) is terribly slow, and would make reasonable graphics effectively impossible. Due to this, the Femto-4 includes several execution modes that allow the computer to run much faster. There are two registers involved in this, address 00ca, the mode register, and address 00cb, the protection register. When the two least significant bits of the mode register are low, the computer runs normally, executing 1 instruction per clock pulse. When it is set high however, the computer enters fast execution on the rising edge, where it executes multiple instructions per clock pulse. This is achieved by looping a rising edge monostable circuit into a falling edge monostable circuit, producing a loop that will pulse indefinitely until the looping line is written high to by some external factor. Stopping the loop is critical since leaving the loop running will stop CircuitVerse's execution, due to it going over the stack limit of the execution. "Fast execution" is always paused by a 0x0000 OP Code, which ensures that the computer will not attempt to "fast execute" memory that has not been written to. It is also paused by the OP Code 0x0001. Setting the 3 bit of the mode register high will enable protection. This will ensure that computer only executes as many instructions as the value in the protection register. This protects execution by ensuring that the loop will always pause before the cycle limit is reached. Since some operations are far more complex than other operations, the maximum number of instructions per clock pulse is variable, and testing should always be conducted to ensure that the limit is not reached. Due to this, for games that need regular graphics updates, it is recommended that protection is not used, and instead the pauses are fully code controlled. Setting the 2nd bit of the mode register high will enable the clock to run fast execution on the falling edge of the clock as well, doubling execution speed. On the other end of the mode register are the graphics mode. The highest two bits give the graphics update mode, 00 for falling edge only (normal speed), 01 for dual edge (double speed), 10 for every other clock pulse (half speed), and 11 for code controlled, where the 0x0001 OP Code is required to update the graphics. The third most significant bit is the graphics disable bit. Setting it high stops updating the graphics. The mode and protection values are only updated on the rising edge of the clock pulse, and therefore there should always be pauses before and after any execution mode or protection change.

Graphics:

The Femto-4 is capable of driving a 16x16 15bit direct colour screen. It has space for 32 "sprites" which are rectangles with an assigned colour. Currently, every time the clock pulses low, the screen is refreshed. When using dual-edge "Faster Execution", the falling edge should only be used to execute game code, since writing graphics data as the screen is being drawn may mess up the graphics. These 32 "sprites" have their data stored in the PPU RAM in the following format: The first 16 bits are the corners of the rectangle, with each coordinate being 4 bits. The coordinates are ordered x1 x2 y1 y2. The next 16 bits are the sprites colour, with the first 15 bits being used for 15 bit direct colour, and the last bit being used to enable or disable drawing the sprite. Since the screen is not wiped every time it is refreshed, the background must be sprite to ensure that the screen is fully wiped before the rest of the sprites are drawn on. Control of this allows carts to draw a single frame over multiple updates, allowing the 32-sprite limit to be bypassed. The "sprites" are drawn in memory order, with the "sprite" with the largest address always being drawn last and therefore on top, of all other "sprites". This is achieved by using the exact same monostable clock system as "Fast Execution", which reads off all the sprite data and draws them to the screen in a single clock pulse. This can loop more times safely than the main CPU since it has less dependencies which dramatically increase the simulation's stack usage.

ALU:

The basic ALU was inspired by the ALU-74LS181. It was designed to flexibly change between various operations by changing an additional piece of data which is bundled in the OP Code. This allows a single ALU to handle all the required processes, such as the basic binary logic operations, shift left, adding, and subtracting. This is unlike my previous computer which had different chips for each operation it could do. The Femto-4 also can multiply, divide, shift right, shift left/right by a specified number of bits, and perform operations designed to work with the Femto-4's graphics data.

Conditional Jumps:

The Femto-4 can perform immediate and direct jumps depending on the flags, a specified bit of the accumulator, and the clock. The flag jumps allow for comparisons to be made. There are three flags, the carry, the most significant bit in the accumulator, and if the accumulator value is 0, the equals flag. By performing A-B, we can compare A and B by looking at the flags. If the equals flag is true, then A=B, since A-B = 0. If the most significant bit is 0, then the number is positive or 0 (by two's complement) and therefore A>=B. The comparison is not entirely correct for numbers in two's complement (a large positive number and a large negative number when subtracted can yield a positive number), but for small values it works well. Whilst we cannot directly check A<=B using A-B in this design, we can simply flip the subtraction to B-A to do so.

The accumulator bit testing is mainly used to check for controller inputs. Since each button in the controller is mapped to one bit, bit testing that bit effectively allows us to check if a button has been pressed. In theory a similar test could be performed using an AND instruction, and checking if the result is equal to 0 or not.

The jump on clock is there to ensure that we can jump execution on the right clock pulse, which ensures that graphics can be updated on the edge of execution.

Timing:

This computer is timed using several standard delay chips. The pulse length running in to the computer is about 10k units long. Therefore, different parts an instruction are separated by 20k unit delays. Further control of timings inside these periods is achieved through 1k "On Delays", which have a 1k delay turning on, but a 0k delay turning off, ensuring that pulses do not bleed into the next pulse. For more information see here: https://circuitverse.org/users/4699/projects/circuitverse-delay-introduction.

Other Notes:

The memory wrappers allow external chips to interact with the main data control system, in this case used for RNG, controllers, the keyboard, and driving the text output.

For more information, please read the developer guide found in the Femto-4's Assembler, or just post a comment and ask me.

This is a secret to everybody, unless you found it.

Femto-4v1.1 (Computer)

Femto-4v1.1 (Computer)Latest versions of the 256-Series, including the Femto-4:

https://circuitverse.org/users/4699/projects/256-series

A 16-bit computer/maybe console inspired thing, the Femto-4. This is a fork from the main branch to keep a semi-functional version around. This project was started around November 2020.

Currently runs:

Cart A: Flappy Bird

Cart B: Some Pixel Art

Assembler:

https://repl.it/@Sanderokianstfe/Femto-4-Assembler#DeveloperGuide.txt

Features:

Immediate, direct and indirect memory access

Jumps and conditional Jumps

16-bit address space

Switchable Memory Banks, allowing for a standard Cart to hold up to 512kx16b of data

An ALU capable of logical operators, addition, subtraction and shift left

Easy to add to buses

"Fast Execution" - Can run more than one instruction per clock cycle

16x16 pixel display

Inputs, both "controllers" and keyboards

"Faster Execution" - Runs instructions on both edges of the clock pulse

Random number generator

Text outputs

An ALU capable of shift right, multiplying, dividing, and other specialised functions

Stack

Assembler (written in an external program)

Save memory

One pre-written cart to play with

Updates:

Another pre-written cart

Fixed code controlled graphics updates

Made Bootloader clear TTY, Keyboard, and Controller Pushed

Fixed Register ALU instructions

Updated Cart A and Cart B to make use of the Register ALU instructions

Will have:

More pre-written carts

Bug fixes

Do fork the project and write your own code for it! If you want more information on how to do so read the Developer Guide in the assembler.

Note:

The Flappy Bird high score is mine. If you want to save your own scores permanently you will have to fork it.

General Architecture:

The Femto-4 has variable length instructions that are comprised of multiple 16-bit chunks. First the OP Code of the instruction is read, and then depending on the OP Code, additional pieces of data may be read for the operands. This allows execution to become incorrectly offset, which can lead to the execution of garbage if the PC is jumped to an incorrect address. This is usually fine, since the OP Code space is so empty that the data will likely be passed one at a time until the next valid instruction. Data is read through the standard data retrieval system (which is handy since its design is so universal and easy to add to) making this architecture a Von Neuman architecture as opposed to a Harvard architecture, like my previous, worse, computer. The MAR always specifies the address being read to or written from, whilst the MDR always holds the data being written. Data from the data out bus can be written to any special register during the instruction. OP Codes and operands are all 16-bits, which is a bit wasteful in terms of OP Code usage, however it was easier to implement this way, and so that is what I went with (and there are a lot of ALU processes).

Memory Mapping:

The 16-bit address space of the Femto-4 is memory mapped, with all data being stored somewhere in the address space. The last 48kx16b of memory (all addresses starting with 01, 10, or 11) are dedicated to the cart memory. This is where the interchangeable program would be stored, allowing programs to be easily changed by changing carts. (However, currently there are currently only two carts). The carts have 32 16kx16b EEPROM/RAM chips, which can be switched between during execution by writing to address 00cc. This gives each cart 512kx16b of memory to play with. In theory, additional memory can be added in a cart by creating a similar system on the inside of the cart, which would allow it to swap between even more EEPROM/RAM chips. The initial 16kx16b are therefore mapped to everything else, including a fixed "work" RAM chip that cannot be switched out, the bootloader, the PPU data, general use registers, the, stack, inputs, outputs, and special use registers.

"Fast Execution":

Execution at the fastest clock speed (one pulse every 50ms, or 20Hz) is terribly slow, and would make reasonable graphics effectively impossible. Due to this, the Femto-4 includes several execution modes that allow the computer to run much faster. There are two registers involved in this, address 00ca, the mode register, and address 00cb, the protection register. When the two least significant bits of the mode register are low, the computer runs normally, executing 1 instruction per clock pulse. When it is set high however, the computer enters fast execution on the rising edge, where it executes multiple instructions per clock pulse. This is achieved by looping a rising edge monostable circuit into a falling edge monostable circuit, producing a loop that will pulse indefinitely until the looping line is written high to by some external factor. Stopping the loop is critical since leaving the loop running will stop CircuitVerse's execution, due to it going over the stack limit of the execution. "Fast execution" is always paused by a 0x0000 OP Code, which ensures that the computer will not attempt to "fast execute" memory that has not been written to. It is also paused by the OP Code 0x0001. Setting the 3 bit of the mode register high will enable protection. This will ensure that computer only executes as many instructions as the value in the protection register. This protects execution by ensuring that the loop will always pause before the cycle limit is reached. Since some operations are far more complex than other operations, the maximum number of instructions per clock pulse is variable, and testing should always be conducted to ensure that the limit is not reached. Due to this, for games that need regular graphics updates, it is recommended that protection is not used, and instead the pauses are fully code controlled. Setting the 2nd bit of the mode register high will enable the clock to run fast execution on the falling edge of the clock as well, doubling execution speed. On the other end of the mode register are the graphics mode. The highest two bits give the graphics update mode, 00 for falling edge only (normal speed), 01 for dual edge (double speed), 10 for every other clock pulse (half speed), and 11 for code controlled, where the 0x0001 OP Code is required to update the graphics. The third most significant bit is the graphics disable bit. Setting it high stops updating the graphics. The mode and protection values are only updated on the rising edge of the clock pulse, and therefore there should always be pauses before and after any execution mode or protection change.

Graphics:

The Femto-4 is capable of driving a 16x16 15bit direct colour screen. It has space for 32 "sprites" which are rectangles with an assigned colour. Currently, every time the clock pulses low, the screen is refreshed. When using dual-edge "Faster Execution", the falling edge should only be used to execute game code, since writing graphics data as the screen is being drawn may mess up the graphics. These 32 "sprites" have their data stored in the PPU RAM in the following format: The first 16 bits are the corners of the rectangle, with each coordinate being 4 bits. The coordinates are ordered x1 x2 y1 y2. The next 16 bits are the sprites colour, with the first 15 bits being used for 15 bit direct colour, and the last bit being used to enable or disable drawing the sprite. Since the screen is not wiped every time it is refreshed, the background must be sprite to ensure that the screen is fully wiped before the rest of the sprites are drawn on. Control of this allows carts to draw a single frame over multiple updates, allowing the 32-sprite limit to be bypassed. The "sprites" are drawn in memory order, with the "sprite" with the largest address always being drawn last and therefore on top, of all other "sprites". This is achieved by using the exact same monostable clock system as "Fast Execution", which reads off all the sprite data and draws them to the screen in a single clock pulse. This can loop more times safely than the main CPU since it has less dependencies which dramatically increase the simulation's stack usage.

ALU:

The basic ALU was inspired by the ALU-74LS181. It was designed to flexibly change between various operations by changing an additional piece of data which is bundled in the OP Code. This allows a single ALU to handle all the required processes, such as the basic binary logic operations, shift left, adding, and subtracting. This is unlike my previous computer which had different chips for each operation it could do. The Femto-4 also can multiply, divide, shift right, shift left/right by a specified number of bits, and perform operations designed to work with the Femto-4's graphics data.

Conditional Jumps:

The Femto-4 can perform immediate and direct jumps depending on the flags, a specified bit of the accumulator, and the clock. The flag jumps allow for comparisons to be made. There are three flags, the carry, the most significant bit in the accumulator, and if the accumulator value is 0, the equals flag. By performing A-B, we can compare A and B by looking at the flags. If the equals flag is true, then A=B, since A-B = 0. If the most significant bit is 0, then the number is positive or 0 (by two's complement) and therefore A>=B. The comparison is not entirely correct for numbers in two's complement (a large positive number and a large negative number when subtracted can yield a positive number), but for small values it works well. Whilst we cannot directly check A<=B using A-B in this design, we can simply flip the subtraction to B-A to do so.

The accumulator bit testing is mainly used to check for controller inputs. Since each button in the controller is mapped to one bit, bit testing that bit effectively allows us to check if a button has been pressed. In theory a similar test could be performed using an AND instruction, and checking if the result is equal to 0 or not.

The jump on clock is there to ensure that we can jump execution on the right clock pulse, which ensures that graphics can be updated on the edge of execution.

Timing:

This computer is timed using several standard delay chips. The pulse length running in to the computer is about 10k units long. Therefore, different parts an instruction are separated by 20k unit delays. Further control of timings inside these periods is achieved through 1k "On Delays", which have a 1k delay turning on, but a 0k delay turning off, ensuring that pulses do not bleed into the next pulse. For more information see here: https://circuitverse.org/users/4699/projects/circuitverse-delay-introduction.

Other Notes:

The memory wrappers allow external chips to interact with the main data control system, in this case used for RNG, controllers, the keyboard, and driving the text output.

For more information, please read the developer guide found in the Femto-4's Assembler, or just post a comment and ask me.

This is a secret to everybody, unless you found it.

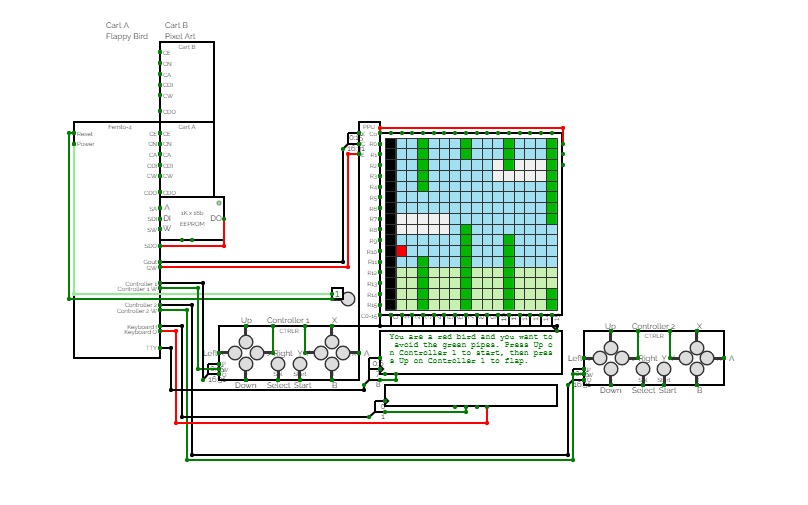

Femto-4v2.6 (Computer)

Femto-4v2.6 (Computer)A 16-bit computer/maybe console inspired thing, the Femto-4. This will be the main branch and backups will be forks from it. This project was started around November 2020.

Currently runs:

- Cart A: Flappy Bird

- Cart B: Some Pixel Art

- Cart C: Screensaver

- Cart D: Snake

- Cart E: Phemton Demonstrations

- Cart F: Competitive Snake

- Cart G: Tic Tac Toe

- Cart H: Connect 4

- Cart I: NIM

- Cart J: Bad Apple

- Bundle Cart: All carts in one

- Cart 2A: 32x32 Snake

- Cart 2B: 32x32 Competitive Snake

- Cart 2C: 32x32 Pixel Art

- Cart 2D: 32x32 Bad Apple

- Bundle Cart 2: All 32x32 carts in one

Assembler:

Compiler:

- https://github.com/Comerstar/PhemtonCompiler/blob/main/PhemtonLiteCompiler/PhemtonDeveloperGuide.txt

The 256-Series:

Full screen Notes:

For some reason, the Femto-4v2.6 only is having issues around caching previous subcircuits. Should you need to use something to unbind key entries from the full screen button, toggle the clock. Previous versions are completely unaffected.

Cart Notes:

Cart A:

- The first cart written for the Femto-4.

Cart B:

- The sprites in the cart are:

- A: Femto-4 Logo.

- B: Madeline from Celeste.

- C: Madeline from Celeste (again).

- D: Part of you aka Badeline from Celeste.

- E: A strawberry from Celeste.

- F: Standing Mario from Super Mario Bros.

- G: Jumping Mario from Super Mario Bros.

- H: Standing Mario from Super Mario Bros 3.

- I: Running Mario from Super Mario Bros 3.

- J: Sanderokian (my own character).

Cart C:

- Enter anything into the keyboard to randomise the colours.

- Enter r into the keyboard to reset the colours.

Cart D:

- WASD Pad is recommended.

- Game settings (enter the letter before starting the game to use the setting):

- e: toggle whether crashing into the edges results in a game over.

- The two modes (with/without edge collisions) have two separate high scores.

- w: change the snake's colour scheme to white.

- r: change the snake's colour scheme to red.

- y: change the snake's colour scheme to yellow.

- o: change the snake's colour scheme to orange.

- p: change the snake's colour scheme to purple.

- a: change the snake's colour scheme to aqua.

- g: change the snake's colour scheme to green.

- b: change the snake's colour scheme to blue.

- m: change the snake's colour scheme to magenta.

- 1: change the snake's colour scheme to pink.

- 2: change the snake's colour scheme to light blue.

- 3: change the snake's colour scheme to the challenge colour scheme with an invisible body.

- 0: randomise the snake's colour scheme.

Cart E:

- The test codes in the cart are:

- 1: Hello World.

- 2: Single Operator Calculator.

- 3: Exponentiation Calculator.

- 4: Fibonacci Calculator.

- 5: Keyboard to TTY Test.

- 6: Keyboard to TTY LDI LID Test.

- 7: Keyboard to TTY LII Test.

- 8: Keyboard to TTY LIA Test.

Cart F:

- WASD Pad is essentially required.

- Game settings (enter the letter before starting the game to use the setting):

- e: toggle whether crashing into the edges results in a game over.

- w: toggle whether the number of wins each player has is tracked.

- s: toggle whether the total score each player has scored is tracked.

- d: display the total wins and total scored.

- r: reset the tracked statistics.

Cart G:

- The small light in the corner indicates which player's turn it is.

- When it is dimmed, it means that the computer is processing that player's turn.

- Game settings (enter the letter before starting the game to use the setting):

- w: toggle whether the number of wins each player has is tracked.

- s: toggle automatic start player swapping. d: display the wins each player has.

- r: reset the wins each player has.

Cart H:

- The bar at the top indicates which player's turn it is.

- When it is dimmed, it means that the computer is processing that player's turn.

- Game settings (enter the letter before starting the game to use the setting):

- w: toggle whether the number of wins each player has is tracked.

- s: toggle automatic start player swapping.

- d: display the wins each player has.

- r: reset the wins each player has.

Cart I:

- Game settings (enter the letter before starting the game to use the setting):

- w: toggle whether the number of wins each player has is tracked.

- s: toggle automatic start player swapping.

- d: display the wins each player has.

- r: reset the wins each player has.

- i: display the game instructions.

- c: toggle the whether player 2 is played by the computer.

Cart J:

- Plays Bad Apple

- There are no further controls

Cart 2A:

- The options are the same as Cart D.

Cart 2B:

- The options are the same as Cart F.

Cart 2C:

- The sprites in the cart are:

- A: Femto-4 Logo.

- B: Sanderokian (my own character).

- C: Alstran (my own character).

Cart 2D:

- Plays Bad Apple on the larger screen

- There are no further controls

Features:

- Immediate, direct, & indirect memory access.

- Jumps & conditional jumps.

- 16-bit address space.

- Switchable memory banks, allowing for a standard cart to hold up to 1MB of data.

- An ALU capable of logical operators, addition, subtraction, shift left, shift right, multiplying, dividing, & other specialised functions.

- Fast execution - can run more than one instruction per clock cycle.

- 16x16 pixel display with 32 sprites and 15-bit direct colour.

- 32x32 pixel display with 32 sprites which can have up to 18-bit direct colour.

- Two controllers, a keyboard mapping for the controllers, & a keyboard for text inputs.

- RNG, TTY, stack, & save memory.

- Von Neumann Architecture.

- Assembler & compiler (written in Python).

- Twelve pre-written carts to play with.

Updates:

v1.0:

- Finished the project and added Cart A.

v1.1:

- Added Cart B, some Pixel Art.

- Fixed GRF, & AXR instructions.

- Made Bootloader clear TTY, Keyboard, & Controller Pushed.

- Updated Cart A & Cart B to make use of AXR instructions.

v1.2:

- Added Cart C, a Screensaver.

- Updated Cart B to respond to the start button on both controllers.

v1.3:

- Added Cart D, Snake.

- Moved to new project to fix issues around searching for projects branched from private projects.

- Removed unnecessary EEPROM banks and write lines from all carts.

- Made Reset clear WRAM and the General Registers.

v1.4:

- Fixed Keyboard.

- Added a Bundle Cart that allows you to view all the carts without changing carts (you must reset the console to view another cart).

- Fixed bug in the standard bank design which wrote data to incorrect addresses.

- Fixed contention issue in Mult.

- Added Annotations to the In Debug.

v1.5:

- Added Snake Player.

- Added Reset & Power labels to the relevant buttons.

v2.0:

- Further optimisation to reduce lag/increase execution speed.

- Added more memory access options.

v2.1:

- Further optimisation of the CU.

- Added a keyboard to controller mapping.

v2.2:

- Continued optimisation and overhaul of the CU.

- Removed old CU & compare circuits.

- Added additional stack access instructions.

- Updated the debug versions with the changes, as well as fixing bugs in the debug versions.

- Designed a Logo for the Femto-4.

- Rewrote Cart C to allow the sprites to be viewed in any order, and added the logo to it.

v2.3:

- Introducing Phemton Lite, the first version of the Femto-4's high level languages.

- Added a link to Phemton Lite's compiler.

- Added Cart E to demonstrate code written in Phemton Lite.

- Combined SpecialD & ROMD1, and removed SpecialD & ROMDB.

- Updated Snake code & Bundle code to match the new addresses.

- Added Cart F, a competitive version of Snake.

- Added an additional sprite into Cart B.

- Fixed issues with LII, LXA & LXP instructions.

v2.4:

- Fixed alignment of the upper carts.

- Added Cart G & Cart H, Tic Tac Toe & Connect 4 written in Phemton Lite.

- Added progress lights to Cart G & Cart H.

- Reworked bundle cart to make the code shorter and more efficient for large numbers of carts.

- Made Cart G & Cart H faster.

- Reshuffled Cart E test codes and added 2 Cart E test codes, exponentiation & Fibonacci calculation.

- Added game options to Cart D, Cart F, Cart G, & Cart H.

- Updated Cart C to allow the colours to be randomised.

- Added optional colour schemes for Cart D.

- Fixed Snake Player.

- Remade the multiply and divide circuits to take advantage of the inbuilt adders.

- Removed old MultM and DivM circuits.

v2.5:

- Further optimisation of the CU.

- Optimisation of the fast execution clocks for the computer, the graphics, & the WASD Pad.

- Fixed debug versions' issues with Phemton conditionals and added optimisations to the debug versions.

- Added 32x32 screen PPU.

- Added Cart 2A, Cart 2B, & Cart 2C, 32x32 versions of Snake, Competitive Snake, & Pixel Art.

- Added Cart I, NIM written in Phemton Lite.

v2.6

- Added the ability to directly write sprites to the PPU during execution.

- Significantly optimised the CU by removing unnecessary subcircuits.

- Introduced significant quantities of lazy evaluation to further improve performance.

- Added Cart J, and Cart 2D, which both play Bad Apple.

- The Femto-4 can now be added to the set of things that plays Bad Apple.

Future Updates:

- More pre-written carts.

- Bug fixes.

- Adding an optimiser to the compiler.

- Phemton Full.

- Phemton Plus.

Do fork the project and write your own code for it! If you want more information on how to do so read the Developer Guide in the assembler.

Note: The Flappy Bird high score and the Snake high score are mine. If you want to save your own scores permanently you will have to fork the project.

The Femto-4

General Architecture: The Femto-4 is a 16-bit, Von Neumann architecture computer with variable length instructions that are comprised of multiple 16-bit words. It has many features associated with CISCs, such as variable length instructions, and multicycle indirect loads, however operates like a RISC, with each instruction taking exactly 1 clock cycle. This was done to give the Femto-4 power whilst keeping its construction simple. First the OP code of the instruction is read, and then depending on the OP code, additional pieces of data may be read for the operands. This allows execution to become incorrectly offset, which can lead to the execution of garbage if the PC is jumped to an incorrect address. This is usually fine, since the OP code space is so empty that the data will likely be passed one at a time until the next valid instruction. Instructions are read from main memory, making this architecture a Von Neumann architecture as opposed to a Harvard architecture. The MAR always specifies the address being read to or written from, whilst the MDR always holds the data being written. Data from the data out bus can be written to most special registers during the instruction. OP codes and operands are all 16-bits. The large OP code size was chosen due to the high number of ALU instructions. There are approximately 500 interpretable OP codes that the computer can handle.

Memory Mapping: The 16-bit address space of the Femto-4 is memory mapped, with all data being stored somewhere in the address space. The last 48kx16b of memory (all addresses starting with 0b01, 0b10, or 0b11) are dedicated to the cart memory. This is where the interchangeable program would be stored, allowing programs to be easily changed by changing carts. The carts have 32 16kx16b EEPROM/RAM chips, which can be switched between during execution by writing to address 0x00cc. This gives each cart 512kx16b of memory to play with. In theory, additional memory can be added in a cart by creating a similar system on the inside of the cart, which would allow it to swap between even more EEPROM/RAM chips. The initial 16kx16b are therefore mapped to everything else, including a fixed WRAM chip that cannot be switched out, the bootloader, the PPU data, general registers, the stack, inputs, outputs, and a few special registers, such as the protect, mode, and flag registers.

Fast Execution: Execution at the fastest clock speed (one pulse every 100ms, or 10Hz, which is defined as the clock changing state every 50ms, or at a rate of 20Hz) is terribly slow, and would make reasonable graphics effectively impossible. Due to this, the Femto-4 includes several execution modes that allow the computer to run much faster. There are two registers involved in this, address 0x00ca, the mode register, and address 0x00cb, the protect register. When the two least significant bits of the mode register are low, the computer runs normally, executing 1 instruction per clock pulse. When bit 0 is set high, the computer enters fast execution on the rising edge, where it executes multiple instructions per clock pulse. This is achieved by looping an inverter into itself, producing a loop that will pulse indefinitely until the looping line is stopped by some external factor. Stopping the loop is critical since leaving the loop running will stop CircuitVerse's execution, due to it going over the stack limit of the execution. Fast execution is always paused by a 0x0000 and 0x0001 OP Code. Bit 2 enables falling edge fast execution, which can be done with rising edge fast execution producing dual edge fast execution. Setting the third bit of the mode register high will enable protection. This will ensure that computer only executes as many instructions as the value in the protect register. This protects execution by ensuring that the loop will always pause before the cycle limit is reached. Since some operations are far more complex than other operations, the maximum number of instructions per clock pulse is variable, and testing should always be conducted to ensure that the limit is not reached. Due to this, for games that need regular graphics updates, it is recommended that protection is not used, and instead the pauses are fully code controlled. On the other end of the mode register are the graphics mode. The highest two bits give the graphics update mode, 0b00 for falling edge only (normal speed), 0b01 for dual edge (double speed), 0b10 for every other clock pulse (half speed), and 0b11 for code controlled, where the 0x0001OP Code is required to update the graphics. The third most significant bit is the graphics disable bit. Setting it high stops updating the graphics, reducing lag by prevent the graphics fast execution loop from running. The mode and protection values are only updated on the rising edge of the clock pulse, and therefore there should always be pauses before and after any execution mode or protection change. By default, the Femto-4 executes with a protection value of 16, to allow the carts to run smoothly, however, depending on the instructions being used, that number can be raised to 64.

Graphics (16x16): The Femto-4 is capable of driving a 16x16 15-bit direct colour screen. It has space for 32 sprites which are rectangles with an assigned colour. All the sprites are drawn to the screen whenever a graphics update occurs, depending on the graphics mode. When using dual-edge fast execution, the falling edge should only be used to execute game code, since writing graphics data as the screen is being drawn may mess up the graphics. These 32 sprites have their data stored in the PPU RAM in the following format: The first 16 bits are the corners of the rectangle, with each coordinate being 4 bits. The coordinates are ordered x coordinate 1 (4), x coordinate 2 (4), y coordinate 1 (4), y coordinate 2 (4). The second coordinates are offset up by 1, to allow the full screen to be drawn to, such that the dimensions of the rectangle are (x2 - x1) + 1 and (y2 - y1) + 1. The next 16 bits are the sprites colour, with the first 15 bits being used for 15-bit direct colour, and the last bit being used to enable or disable drawing the sprite. The last bit is important to ensure that blank sprites are not drawn to the screen. Since the screen is not wiped every time it is refreshed, the background must be a sprite to ensure that the screen is fully wiped before the rest of the sprites are drawn on. Control of this allows carts to draw a single frame over multiple updates, allowing the 32-sprite limit to be bypassed (see how Snake works). The sprites are drawn in memory order, with the sprite with the largest address always being drawn last and therefore on top, of all other sprites. This is achieved by using the exact same system as fast execution, which reads off all the sprite data and draws them to the screen in a single clock pulse. This can loop more times safely than the main CPU since it has less dependencies which dramatically decreases the simulation's stack usage.

Graphics (32x32): The Femto-4 can also drive a 32x32 screen, with sprites able to be drawn through 3 different modes. The 32x32 screen PPU treats the addresses as one combined 32-bit value, with the value with the smaller address going first. The first 3 bits of the 32 bits define the mode. Only the values 1, 2, 3, correspond to actual sprites, whilst the rest are not drawn to the screen. Mode 1 splits the remaining 29-bit space as the following: unused (1), x coordinate (5), y coordinate (5), red (6), green (6), blue (6). Mode 2 splits the 29-bit space in the following way: x coordinate 1 (5), x coordinate 2 (5), y coordinate 1 (5), y coordinate 2 (5), red (3), green (3), blue (3). Mode 3 splits the 29-bit space in the following way: unused (3), x coordinate (5), y coordinate (5), red (5), green (5), blue (5), alpha/transparency (1). As with the 16x16 screen, Mode 2's second coordinates are offset by 1 resulting in rectangles having the dimensions of (x1 - x2) + 1 and (y1 - y2) + 1. Mode 3 is designed to allow the colours used in the 16x16 screen to be the same, making converting code between the two versions easier. The update mechanism is the same as 16x16 screen.

ALU: The basic ALU was inspired by the ALU-74LS181. It was designed to flexibly change between various operations by changing an additional piece of data which is bundled in the OP code. This allows a single ALU to handle all the required processes, such as the basic binary logic operations, shift left, adding, and subtracting, reducing the number of circuits required, as well as the logic required to decide which instruction to use. The Femto-4 also can multiply, divide, shift right, shift left/right by a specified number of bits, and perform operations designed to work with the computer's graphics data.

Conditional Jumps: The Femto-4 can perform immediate and direct jumps depending on the flags, a specified bit of the accumulator, and the clock. The flag jumps allow for comparisons to be made. There are three flags, the carry, the most significant bit in the accumulator, and if the accumulator value is 0, the equals flag. By performing A-B, we can compare A and B by looking at the flags. If the equals flag is true, then A=B, since A-B = 0. If the most significant bit is 0, then the number is positive or 0 (by two's complement) and therefore A>=B. The comparison is not entirely correct for numbers in two's complement (a large positive number and a large negative number when subtracted can yield a positive number), but for small values it works well. Whilst we cannot directly check A<=B using A-B in this design, we can simply flip the subtraction to B-A to do so. The accumulator bit testing is mainly used to check for controller inputs. Since each button in the controller is mapped to one bit, bit testing that bit effectively allows us to check if a button has been pressed. A similar test could be performed using an AND instruction, and checking if the result is equal to 0 or not. Bit testing is most useful for testing an input from both controllers, since it can cut out an additional instruction. The jump on clock is there to ensure that we can jump execution on the right clock pulse, which ensures that graphics can be updated on the edge of execution.

Timing: The computer is timed using several standard delay chips. The pulse length running in to the computer is about 10k units long. Therefore, different parts an instruction are separated by 20k unit delays. Further control of timings inside these periods is achieved through 1k "On Delays", which have a 1k delay turning on, but a 0k delay turning off, ensuring that pulses do not bleed into the next pulse. These pulses can tell registers to write and what source to write from, enable the read and write lines, update the ALU, and update the stack Each instruction is separate by 600k of delay in fast execution. For more information on how delay works see here: https://circuitverse.org/users/4699/projects/circuitverse-delay-introduction.

Keyboard Mapping: The Femto-4's keyboard controller mapping was created using a specialised chip. This chip used the fast execution loop to take 15 inputs from a keyboard and map the inputs to button presses on the controllers. Since the buttons are updated several times in a clock pulse, the keyboard controller cannot handle held buttons. The keyboard mapping is designed to work with both controllers, allowing two player games to be feasible on the computer.

Assembly: The Femto-4 has an assembler that converts assembly written in a .txt into hex values in a .txt that can be copied and loaded into the EEPROM banks for storage. The assembler can handle symbol assignment, as well as assigning addresses in the code symbols to make handling jumps easier. For full details on the Femto-4's assembly language view the assembly developer guide.

Phemton: Phemton is the Femto-4's high level language, with a compiler to compile it's code into Femto-4 assembly. Phemton handles variable memory assignment, basic array assignment, if, elif, else statments, while loops, for loops, and functions. Phemton Lite is the only compiler complete, and lacks an optimiser. Phemton Lite has the concept of local scope only when compiling. All uniquely identified variables are given a global address. This reduces the runtime load since the computer does not need to decide where the variables need to go during run time. Future planned additions include generated code optimisations and optimisers, Phemton Full, which has dynamic memory assignment, and Phemton Plus, which adds additional types for floats and longs. For more details view Phemton's developer guide.

Other Notes: The memory wrappers allow external chips to interact with the main data control system, in this case used for RNG, controllers, the keyboard, and driving the text output. This makes it easy to additional chips to the computer. All assembly and Phemton code can be found in the project for the Femto-4's assembler and compiler respectively. The save data cart must be located outside of the Femto-4 circuit to ensure that its contents are automatically saved. Sorry about all the copies of this computer clogging up the top of the search results.

For more information, please read the developer guide found in the Femto-4's Assembler, or just post a comment and ask me.

This is a secret to everybody, unless you found it.

Femto-4v1.5 (Computer)

Femto-4v1.5 (Computer)Latest versions of the 256-Series, including the Femto-4:

https://circuitverse.org/users/4699/projects/256-series

A 16-bit computer/maybe console inspired thing, the Femto-4. This is a branch to keep a functional version around. This project was started around November 2020.

Currently runs:

Cart A: Flappy Bird

Cart B: Some Pixel Art

Cart C: Screensaver

Cart D: Snake

Bundle Cart: All carts in one

Assembler:

https://repl.it/@Sanderokianstfe/Femto-4-Assembler#DeveloperGuide.txt

Features:

Immediate, direct and indirect memory access

Jumps and conditional Jumps

16-bit address space

Switchable Memory Banks, allowing for a standard cart to hold up to 512kx16b of data

An ALU capable of logical operators, addition, subtraction, shift left, shift right, multiplying, dividing, and other specialised functions

Easy to add to buses

"Fast Execution" - Can run more than one instruction per clock cycle

"Faster Execution" - Runs instructions on both edges of the clock pulse

16x16 pixel display with 32 "Sprites" and 15-bit direct colour

Inputs, both "controllers" and keyboards

Random number generator

Text outputs

Stack

Von Neumann Architecture

Assembler (written in an external program)

Save memory

Four pre-written carts to play with

Previous Updates:

Fixed code controlled graphics updates

Made Bootloader clear TTY, Keyboard, and Controller Pushed

Fixed Register ALU instructions

Updated Cart A and Cart B to make use of the Register ALU instructions

Updated the Cart B to respond to the start button on both controllers

Moved to new project to fix issues around searching for projects branched from private projects

Removed unnecessary EEPROM banks from all carts

Removed unnecessary write lines leading to EEPROMs in carts, preventing code from being overwritten during execution

Made Reset clear WRAM and the General Registers

Fixed Keyboard

Added a Bundle Cart that allows you to view all the carts I have made without changing carts (you must reset the console to view another cart)

Fixed bug in standard bank design which wrote data to incorrect addresses

Fixed contention issue with multiplying

Added Annotations to the In Debug

Updates:

Added Snake Player

Added Reset and Power Labels to the relevant buttons

Will have:

More pre-written carts

Bug fixes

Do fork the project and write your own code for it! If you want more information on how to do so read the Developer Guide in the assembler.

Note:

The Flappy Bird high score and the Snake high score are mine. If you want to save your own scores permanently you will have to fork the project.

General Architecture:

The Femto-4 is a 16-bit computer with variable length instructions that are comprised of multiple 16-bit words. First the OP Code of the instruction is read, and then depending on the OP Code, additional pieces of data may be read for the operands. This allows execution to become incorrectly offset, which can lead to the execution of garbage if the PC is jumped to an incorrect address. This is usually fine, since the OP Code space is so empty that the data will likely be passed one at a time until the next valid instruction. Data is read through the standard data retrieval system (which is handy since its design is so universal and easy to add to) making this architecture a Von Neumann architecture as opposed to a Harvard architecture, like my previous, worse, computer. The MAR always specifies the address being read to or written from, whilst the MDR always holds the data being written. Data from the data out bus can be written to any special register during the instruction. OP Codes and operands are all 16-bits, which is a bit wasteful in terms of OP Code usage, however it was easier to implement this way, and so that is what I went with (and there are a lot of ALU processes).

Memory Mapping:

The 16-bit address space of the Femto-4 is memory mapped, with all data being stored somewhere in the address space. The last 48kx16b of memory (all addresses starting with 01, 10, or 11) are dedicated to the cart memory. This is where the interchangeable program would be stored, allowing programs to be easily changed by changing carts. The carts have 32 16kx16b EEPROM/RAM chips, which can be switched between during execution by writing to address 00cc. This gives each cart 512kx16b of memory to play with. In theory, additional memory can be added in a cart by creating a similar system on the inside of the cart, which would allow it to swap between even more EEPROM/RAM chips. The initial 16kx16b are therefore mapped to everything else, including a fixed "work" RAM chip that cannot be switched out, the bootloader, the PPU data, general use registers, the, stack, inputs, outputs, and special use registers.

"Fast Execution":

Execution at the fastest clock speed (one pulse every 100ms, or 10Hz, which is defined as the clock changing state every 50ms, or at a rate of 20Hz) is terribly slow, and would make reasonable graphics effectively impossible. Due to this, the Femto-4 includes several execution modes that allow the computer to run much faster. There are two registers involved in this, address 00ca, the mode register, and address 00cb, the protection register. When the two least significant bits of the mode register are low, the computer runs normally, executing 1 instruction per clock pulse. When it is set high however, the computer enters fast execution on the rising edge, where it executes multiple instructions per clock pulse. This is achieved by looping a rising edge monostable circuit into a falling edge monostable circuit, producing a loop that will pulse indefinitely until the looping line is written high to by some external factor. Stopping the loop is critical since leaving the loop running will stop CircuitVerse's execution, due to it going over the stack limit of the execution. "Fast execution" is always paused by a 0x0000 OP Code, which ensures that the computer will not attempt to "fast execute" memory that has not been written to. It is also paused by the OP Code 0x0001. Setting the 3 bit of the mode register high will enable protection. This will ensure that computer only executes as many instructions as the value in the protection register. This protects execution by ensuring that the loop will always pause before the cycle limit is reached. Since some operations are far more complex than other operations, the maximum number of instructions per clock pulse is variable, and testing should always be conducted to ensure that the limit is not reached. Due to this, for games that need regular graphics updates, it is recommended that protection is not used, and instead the pauses are fully code controlled. Setting the 2nd bit of the mode register high will enable the clock to run fast execution on the falling edge of the clock as well, doubling execution speed. On the other end of the mode register are the graphics mode. The highest two bits give the graphics update mode, 00 for falling edge only (normal speed), 01 for dual edge (double speed), 10 for every other clock pulse (half speed), and 11 for code controlled, where the 0x0001 OP Code is required to update the graphics. The third most significant bit is the graphics disable bit. Setting it high stops updating the graphics, reducing lag by reducing the number of changing outputs. The mode and protection values are only updated on the rising edge of the clock pulse, and therefore there should always be pauses before and after any execution mode or protection change.

Graphics:

The Femto-4 is capable of driving a 16x16 15bit direct colour screen. It has space for 32 "sprites" which are rectangles with an assigned colour. All the sprites are drawn to the screen whenever a graphics update occurs, depending on the graphics mode. When using dual-edge "Faster Execution", the falling edge should only be used to execute game code, since writing graphics data as the screen is being drawn may mess up the graphics. These 32 "sprites" have their data stored in the PPU RAM in the following format: The first 16 bits are the corners of the rectangle, with each coordinate being 4 bits. The coordinates are ordered x1 x2 y1 y2. The next 16 bits are the sprites colour, with the first 15 bits being used for 15 bit direct colour, and the last bit being used to enable or disable drawing the sprite. Since the screen is not wiped every time it is refreshed, the background must be a sprite to ensure that the screen is fully wiped before the rest of the sprites are drawn on. Control of this allows carts to draw a single frame over multiple updates, allowing the 32-sprite limit to be bypassed (see how Snake works). The "sprites" are drawn in memory order, with the "sprite" with the largest address always being drawn last and therefore on top, of all other "sprites". This is achieved by using the exact same monostable clock system as "Fast Execution", which reads off all the sprite data and draws them to the screen in a single clock pulse. This can loop more times safely than the main CPU since it has less dependencies which dramatically decreases the simulation's stack usage.

ALU:

The basic ALU was inspired by the ALU-74LS181. It was designed to flexibly change between various operations by changing an additional piece of data which is bundled in the OP Code. This allows a single ALU to handle all the required processes, such as the basic binary logic operations, shift left, adding, and subtracting. This is unlike my previous computer which had different chips for each operation it could do. The Femto-4 also can multiply, divide, shift right, shift left/right by a specified number of bits, and perform operations designed to work with the Femto-4's graphics data.

Conditional Jumps:

The Femto-4 can perform immediate and direct jumps depending on the flags, a specified bit of the accumulator, and the clock. The flag jumps allow for comparisons to be made. There are three flags, the carry, the most significant bit in the accumulator, and if the accumulator value is 0, the equals flag. By performing A-B, we can compare A and B by looking at the flags. If the equals flag is true, then A=B, since A-B = 0. If the most significant bit is 0, then the number is positive or 0 (by two's complement) and therefore A>=B. The comparison is not entirely correct for numbers in two's complement (a large positive number and a large negative number when subtracted can yield a positive number), but for small values it works well. Whilst we cannot directly check A<=B using A-B in this design, we can simply flip the subtraction to B-A to do so.

The accumulator bit testing is mainly used to check for controller inputs. Since each button in the controller is mapped to one bit, bit testing that bit effectively allows us to check if a button has been pressed. In theory a similar test could be performed using an AND instruction, and checking if the result is equal to 0 or not.

The jump on clock is there to ensure that we can jump execution on the right clock pulse, which ensures that graphics can be updated on the edge of execution.

Timing:

This computer is timed using several standard delay chips. The pulse length running in to the computer is about 10k units long. Therefore, different parts an instruction are separated by 20k unit delays. Further control of timings inside these periods is achieved through 1k "On Delays", which have a 1k delay turning on, but a 0k delay turning off, ensuring that pulses do not bleed into the next pulse. These pulses can tell registers to write and what source to write from, enable the read and write lines, update the ALU, and update the stack. For more information on how delay works see here: https://circuitverse.org/users/4699/projects/circuitverse-delay-introduction.

Other Notes:

The memory wrappers allow external chips to interact with the main data control system, in this case used for RNG, controllers, the keyboard, and driving the text output. This makes it easy to additional chips to the computer.

For more information, please read the developer guide found in the Femto-4's Assembler, or just post a comment and ask me.

This is a secret to everybody, unless you found it.

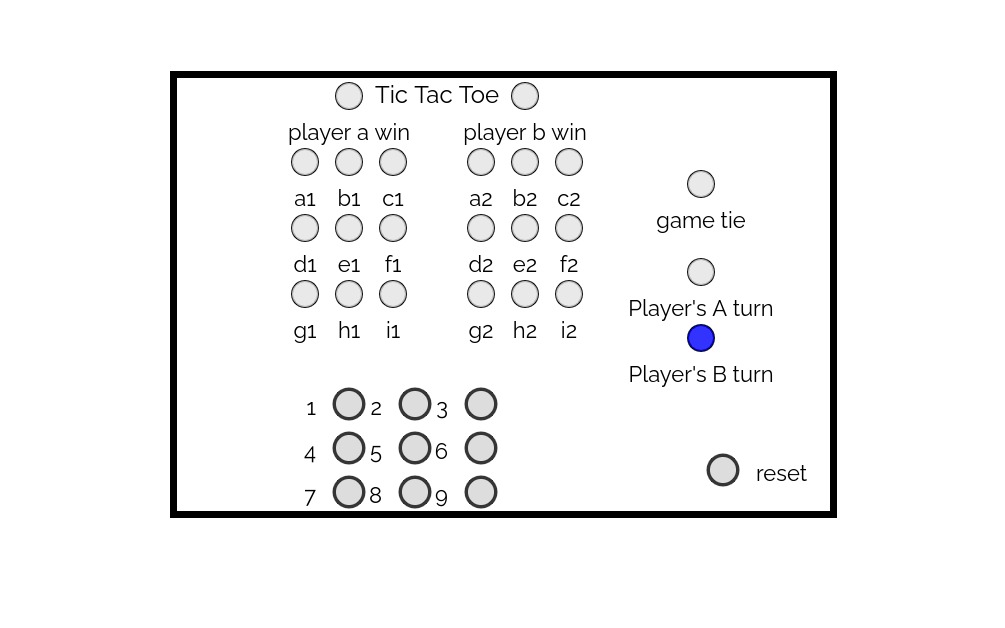

Tic Tac Toe Game Machine

Tic Tac Toe Game MachineMade this for fun.

Worked hard on it+has no more glitches!

Stuff (never added to tic tac toe projects other than mine):

A 2 split-screen to see both players' boards.

That' all!

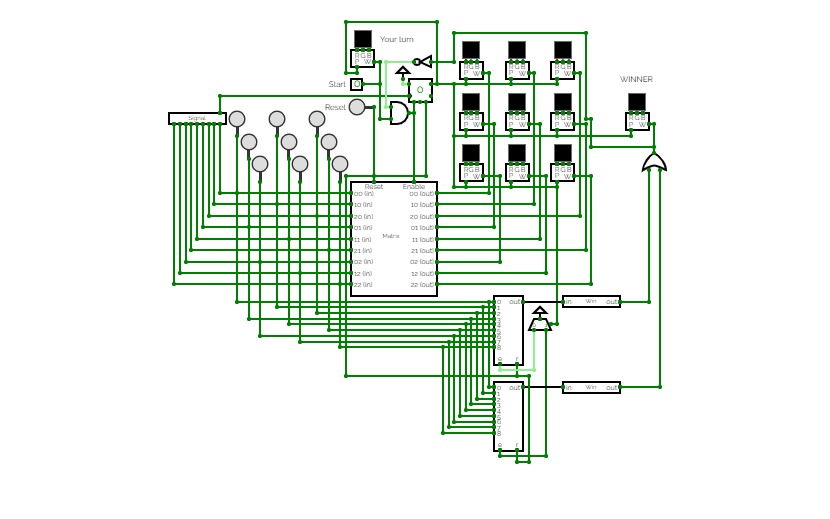

Tic Tac Toe

Tic Tac ToeThis is my version of Tic Tac Toe

I hope you like it :)

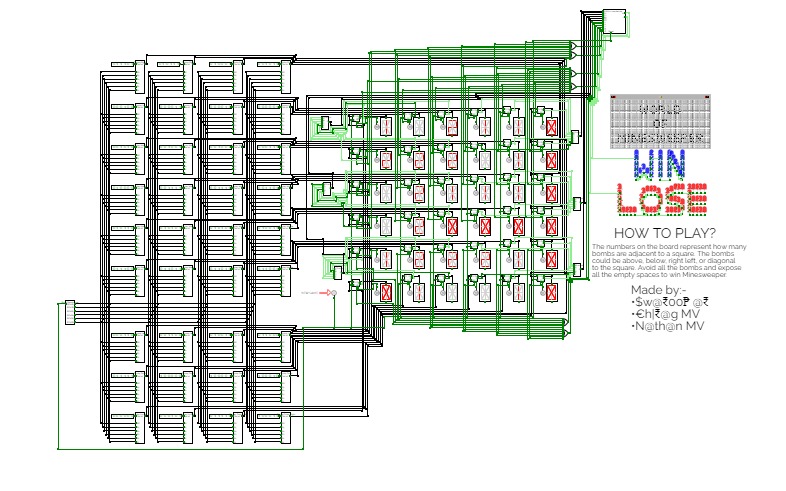

MineSweeper

MineSweeperMinesweeper: The game

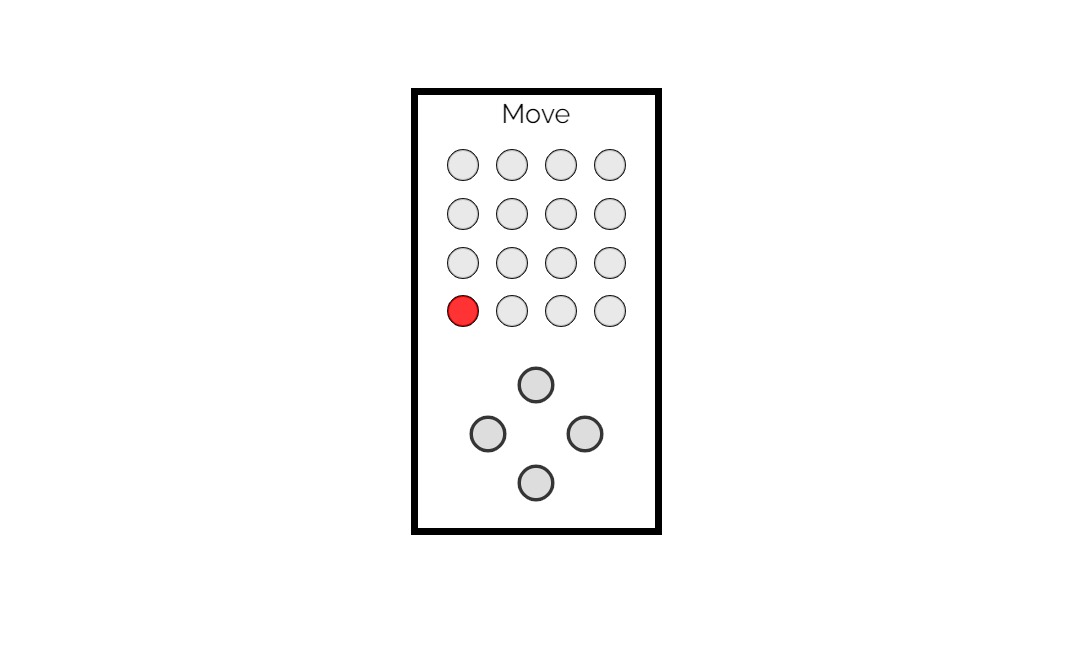

CB PPU

CB PPUCB PPU

CB stands for "Color Burst"

This is a graphics processor/screen driver for 8-bit CPUs.

It works with 16x16 screens or under.

It has a sprite system that has 16 slots.

Most of this description you can find in the project.

Update Notes:

V1 (2024, April 30):

Frame buffer works! Implemented single pixel drawing.

V2 (2024, May 2):

Tinting and Grayscale color operations are added to the pixel drawer. But further development on this is scrapped due to being inefficient.

V3 (2024, May 15) Release 1:

First release of Color Burst! Yipee!!!

Anyways, full flag register, instructions, sprites, and background!

REGISTERS

FLG:

The Flag register for effects.

Op:

The chosen operation (writing to it executes the operation)

Pos1:

Used interchangeably but usually a position (changes based on OP)

Pos2:

Used interchangeably but usually a position (changes based on OP)

SPos:

The Position of the currently selected Sprite

S:

The Slot used for table and sprite updates

BK:

The background color (RRRGGBBB)

CLR register:

This holds the color register for stuff (RRRGGBBB)

FLAG Register

AECg BGRM

M = Pos1, Pos2 OR Pos, Dim

R = Adds 32 to r channel from then on (Tint Red)

G = Adds 32 to g channel from then on (Tint Green)

B = Adds 32 to b channel from then on (Tint Blue)

g = Uses CLR as grayscale value from then on

C = Nothing?

E = Disable background

A = Graphics update by clock or manual

INSTRUCTION SET

00: NOP

01: Flip - Invokes a Graphics update (32 units)

02: Disable Sprite - Disables the sprite at slot S

03: Enable Sprite - Enables the sprite at slot S

04: CreateSp - Creates a sprite using Pos1 as position, Pos2 as dim or pos, C as color

05: UpdateSpPos - Changes the position of sprite at S into Pos1

06: UpdateSpDim - Changes dim of sprite at S to Pos2

07: UpdateSpClr - Changes the color of sprite at S to C

08: Scroll - Adds to the Sprite positions based on Pos1 (32 units)

GUIDE

In order to enable RTX, set the C flag to 1. (JOKE)

--QNA--

Q: Why is it called PPU?

A: It's called that because PPU stands for Picture Processing Unit. I used this name because by naming it a GPU it would sound more powerful than it actually is. Also the NES' graphics processor calls itself PPU as well.

Q: Why in the heck would you make this?

A: Because I wanted to make Graphical games on my CPU projects.

Q: What happens if you scroll it past the side?

A: It will wrap the coordinates around which might make a weird effect due to how the sprites are drawn.

Q: Can it work with 4K?

A: Maybe... Just kidding, it's impossible to drive anything over 16x16 due to the coordinates being only 4 bits each.

--Format--

Color on Color Burst is specified as

RRRGGBBB

This means that there's an unequal distribution of green in comparison with other colors. Unfortunately in order to achieve full use of the 8 bits, I have decided to make greennot as precise. These colors are also shifted in order to fit the 24 bit depth additive color that drives the screen.

Position and Dimensions are specified as

XXXXYYYY

This means that this PPU will only drive a 16x16 or smaller screen.

--Sprites--

Anyways you can make a total of 16 different sprites. Each sprite is well, a rectangle. By the M flag you can select whether you want to specify each sprite as Position and Dimension or Position and Position. It uses the POS1 and POS2 Register for this operation. If you try to use a value over 16 on the S register, it will wrap. Also, sprites are drawn bottom to top so sprite 16 would be on top and 1 on bottom.

--Background--

Each graphics update, the screen is erased and replaced with the background color. In order to change this color, update the BK register. The erasing and updating can be disabled though by using the E flag so that you could theoretically have more than 16 sprites. You can of course read the position from the selected Sprite as well using SPOS.

--Effects--

There are a few effects to choose from on here. Tint Red, Tint Green, Tint Blue, and grayscale. These instructions are controlled by the flag register as R,G,B,g. In order to use them, just set them to 1. Also the tint operations add 32 to the channels by default but future versions of this PPU could have a register to change that.

--Instructions--

Instructions are triggered upon writing to the register. There are 8 instructions. Flip just updates the screen with new data. Scroll just uses the value of POS1 in order to update every sprite by adding it to the position. (This takes 32 units). Other instructions are explained in the set well.

--Other--

If you want to update the graphics by clock instead of instruction, you can change A to 1 and then you can choose a clock speed for the updates (Keep in mind that the clock must last for over 32 units due to graphics updates taking that long.

PLANS

Possible memory maps:

Consider a possible frame buffer implementation.

Without PPU:

Byte 1: Position

(On position write, it will verify pixel write)

Byte 2-4: RGB 24 bit value

With PPU 8-bit color:

two bit perlast two bits should be apply mode (add, sub, replace, or mult) nah it's too hard.

Or use a 4 bit hue, 2 bit saturation, and 2 bit value.

HSV would be too hard due to having to decrease the differnce between each color

Or maybe make a custom byte based color pallete for 8 bit color using boxes (x = r, y = g, box# = b) wait hold on that'll still be inconsistent.

Just use three bit values for colors except green (2 bits)

On overflow, it will do nothing.Sprites are drawn based on slot order. (Except on creation and update)

Full 24 bit color is impractical.

Function method:

OPS:

SetColor (RGB) - Set Color Register

SetPOS (PP) - Set POS Registers

DrawRect - Draws a rectangle starting at POS1 then ending at POS2 using Color

DrawCircle (R) - Draws a circle using POS1, R, and Color

DrawLine - Draws a line using Color, POS1, POS2

SetPixel (P) - Draws a pixel at X,Y

SavSprite (SD) - Saves a sprite to memory at slot S with length and width and the Color

LodSPrite (SP) - Loads a sprite at S at XY

ReadSprite (S) - Reads the length and width of the sprite and outputs it

ReadSpriteClr (S) - Reads color of sprite and outputs it

MM:

Byte 1: OP

Byte 2-4: Arguments

Byte 5-7: Output

Register Method:

OPS:

DrawPix - Draws C at Pos1

DrawLine - Draws C line using Pos1 and Pos2

DrawRect - Draws C rect using Pos1 and Pos2

SaveTbl - Uses Pos1 and C for a table entry and saves it to slot S

LoadTbl - Uses S reg to draw an instance of a table entry to Pos1

SetBack - Sets a color for the background using C

Erase - Erases all updates to background but keeps sprites.

CreateSp - Creates a sprite using Pos1 as position, Pos2 as table slot,

Enable Sprite - Draws the sprite at slot S

Disable Sprite - Erases the sprite at slot S

UpdateSpPos - Changes the position of sprite at S into Pos1

UpdateSpClr - Changes the color of sprite at S to C

Scroll - Adds to the Sprite positions based on Pos1 (Also erases everything)

MM:

Byte 1: C reg

Byte 2: Pos1 reg

Byte 3: Pos2 reg

Byte 4: SPos (R)

Byte 5: S reg

Byte 6: OP (W)

Byte 7: Flag reg

Docs:

Flag:MRGB gCEAM = Pos1, Pos2 OR Pos, Dim

R = Adds 10 to r channel from then on

G = Adds 10 to g channel from then on

B = Adds 10 to b channel from then on

g = Uses r value as grayscale value from then on

C = Enables clipping for sprite placing.

E = Automatically erases a sprite after position update

A = Graphics update by clock or manual

C register: This holds the color register for stuff (RRRGGBBB)

Pos1: Used interchangeably but usually a position (changes based on OP)

Pos2:Used interchangeably but usually a position (changes based on OP)

SPos:

The Position of the currently selected SpriteS:

The Slot used for table and sprite updates

Op:The chosen operation (writing to it executes the operation)

-Chose register method for v1.

V2 is near impossible unless updates are always done. (Could be done on a regular circuit sim)-

V1.1:

Adds frame flip feature so that you wouldn't see screen updates.

V2:

V2 is more similar to a NES type PPU.

Each slot is 2x2 and there's background and sprites.

Table of instance-able tiles are created.

Sprite table is created

Background table is createPallette table is also created.

Sprite hits are also detected.Frame-based instead of canvas.

MM:

OPS:

STbl -

LTbl -

CreateSp - Uses Pos1 as position, Pos2 as table slot, then S as slot

UpdateSp - Updates the sprite position using Pos1 and S as slot

EnableSP - Enables or disables a sprite using S as slot and Pos1 as argument (bit0)

SetBack - Pos1 as table position for tile and then S as the table slot.

VO:OPS:Flip - Invokes a Graphics update (32 units)

CreateSp - Creates a sprite using Pos1 as position, Pos2 as table slot, C as color

Enable Sprite - Enables the sprite at slot S

Disable Sprite - Disables the sprite at slot S

UpdateSpPos - Changes the position of sprite at S into Pos1

UpdateSpDim - Changes dim of sprite at S to Pos2

UpdateSpClr - Changes the color of sprite at S to C

Scroll - Adds to the Sprite positions based on Pos1 (32 units)

MM:

Byte 1: C reg

Byte 2: Pos1 reg

Byte 3: Pos2 reg

Byte 4: SPos (R)Byte 5: S reg

Byte 6: OP (W)

Byte 7: Flag reg

Byte 8: Back reg

Docs:

Flag:MRGB gCEAM = Pos1, Pos2 OR Pos, DimR = Adds 10 to r channel from then onG = Adds 10 to g channel from then on

B = Adds 10 to b channel from then on

g = Uses r value as grayscale value from then on

C =

E = Disable background

A = Graphics update by clock or manual

C register: This holds the color register for stuff (RRRGGBBB)

Pos1: Used interchangeably but usually a position (changes based on OP)

Pos2:Used interchangeably but usually a position (changes based on OP)

SPos:

The Position of the currently selected Sprite

S:

The Slot used for table and sprite updates

Op:

The chosen operation (writing to it executes the operation)

Back:

The background color

Femboy-8

Femboy-8

FEMBOY-8

Functional Electronic Machine Binary Operator Yes

8-bit CPU

Working on a NEW CPU: Femboy-16!

ASSEMBLER:

https://output.jsbin.com/wutikij

GPU:

https://circuitverse.org/users/214464/projects/cb-ppu

INSTRUCTION SET:

00: NOP - Nothing

01: HLT - Halt program

02: OUT [id] - Output the accumulator out of an output

03: LDI A, [d8] - Loads immediate 8 bit word into the accumulator

04: MOV [r], A - Move register to accumulator

05: MOV A, [r] - Move accumulator to register

06: INC [r] - Increment a register

07: DEC [r] - Decrememt a register

08: ADD [r], A - Add the accumulator from a register

09: SUB [r], A - Subtract the accumulator from a register

0A: AND [r], A - And the register and accumulator

0B: IOR [r], A - OR the register and accumulator

0C: XOR [r], A - XOR the register and accumulator

0D: NOT [r] - NOT a register

0E: SRR [r] - Barrel shift accumulator right

0F: SRL [r] - Barrel shift accumulator left

10: JUP [d8] - Jump to a location

11: JPP [r] - Jump to a register value

12: JPL A, [d8] - Jump if accumulator is less than 0

13: JZO A, [d8] - Jump if accumulator is 0

14: JPG A, [d8] - Jump if accumulator is greater than 0

15: JLE A, [d8] - Jump if accumulator is less than or equal to 0

16: JGE A, [d8] Jump if accumulator is greater than or equal to 0

17: JNZ A, [d8] Jump if accumulator is not 0

18: CLR [r] - Clear a register

19: INP [id] - Store INPUT id in accumulator

1A: MOV pA, [r] - Move the value at address A register r

1B: MOV [r], pA - Move register r into address A

1C: MOV [p], A - Move a value in a pointer to the accumulator

1D: MOV A, [p] - Move the accumulator to a location

1E: MLT [r], A - Multiply register r by the accumulator

1F: DIV [r], A - Divide register r by accumulator

REGISTERS:

00: REGISTER 1

01: REGISTER 2

02: REGISTER 3

04: REGISTER 4

05: ZERO FLAG (R)

06: PC (R)

07: ALU Result (R)

Update Notes:

V4:

So this is the 4th iteration of my CPU lol... I added a few programs for you all to try out and you can even use an assembler now!

V5:

Long time since I updated this... But I've added a GPU! It's called "Color burst" and you can go try out some premade programs I have added on it! There's an assembler guide with GPU dev guide and I encourage you all to go try and make some graphical programs! Also more docs can be found on it's project page.

To-Do:

Increase amount of registers to 8

Make a simple command line

Make a simple operating system for the CPU