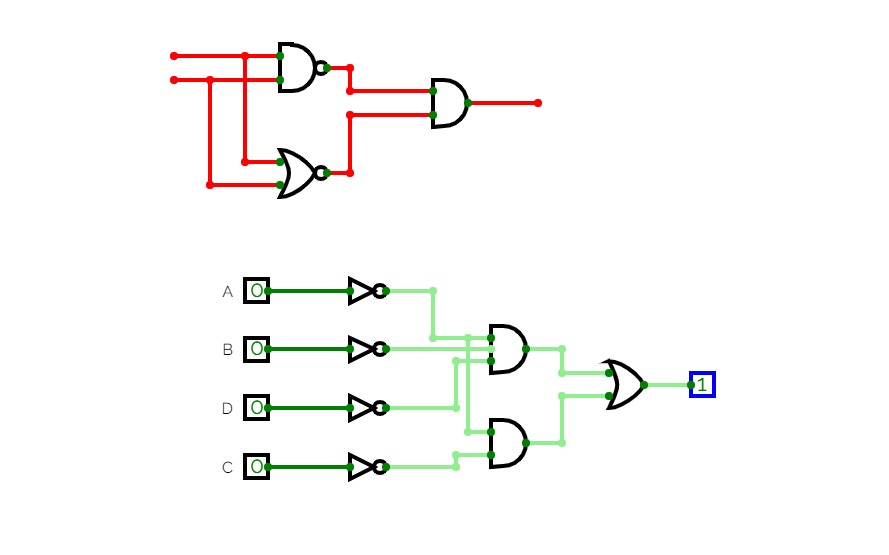

experement 2 2,3,4,5, question 2061008

experement 2 2,3,4,5, question 2061008question no ; 2,3,4,5

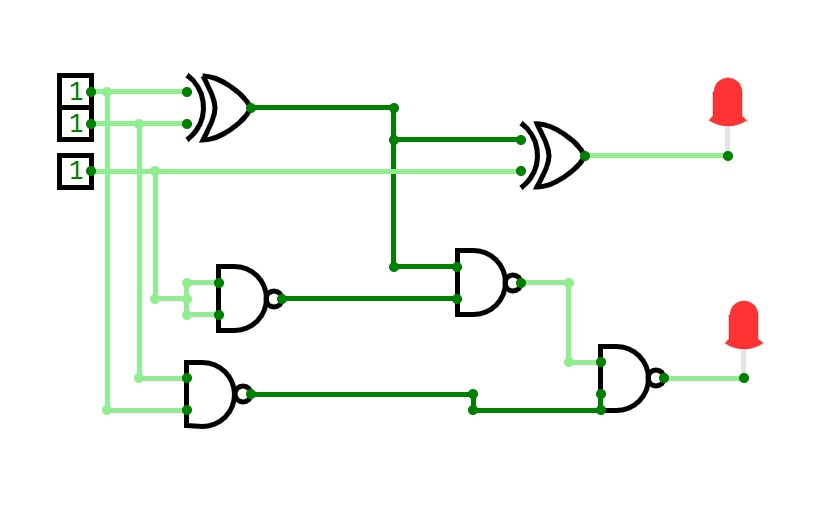

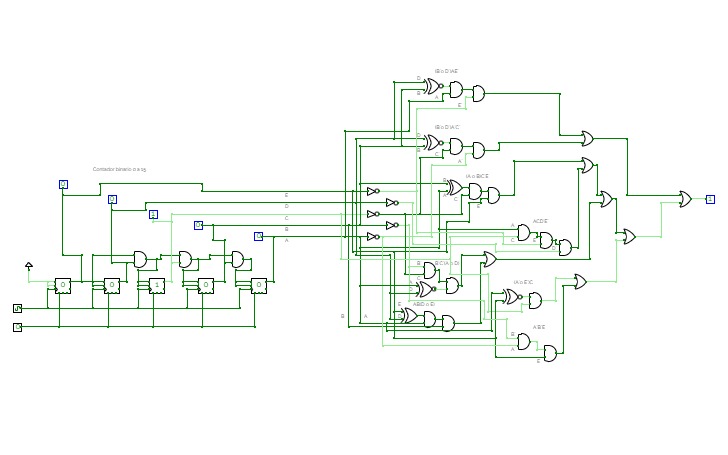

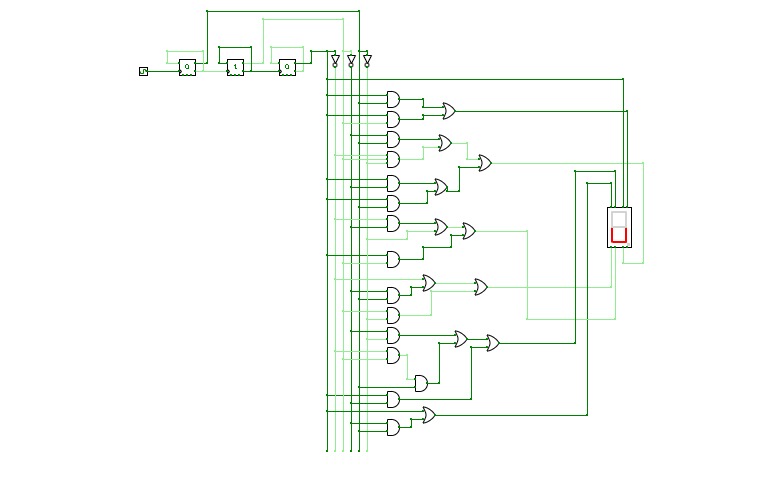

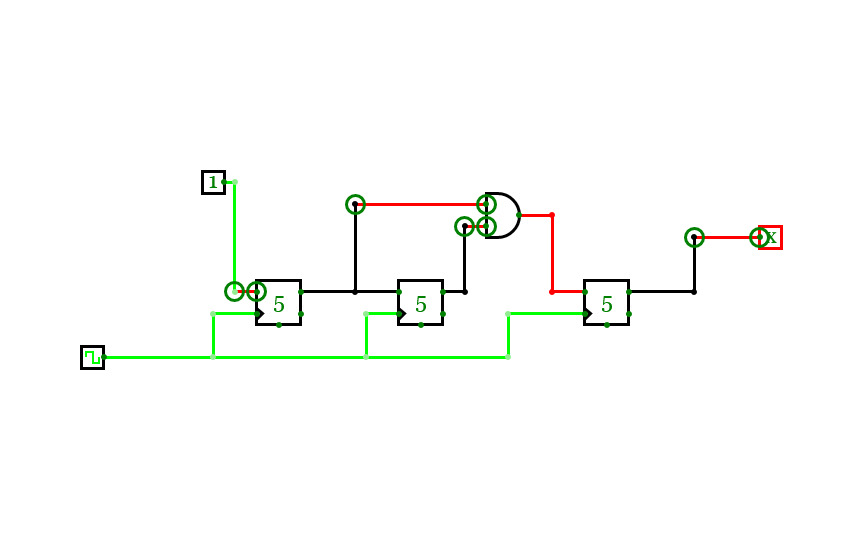

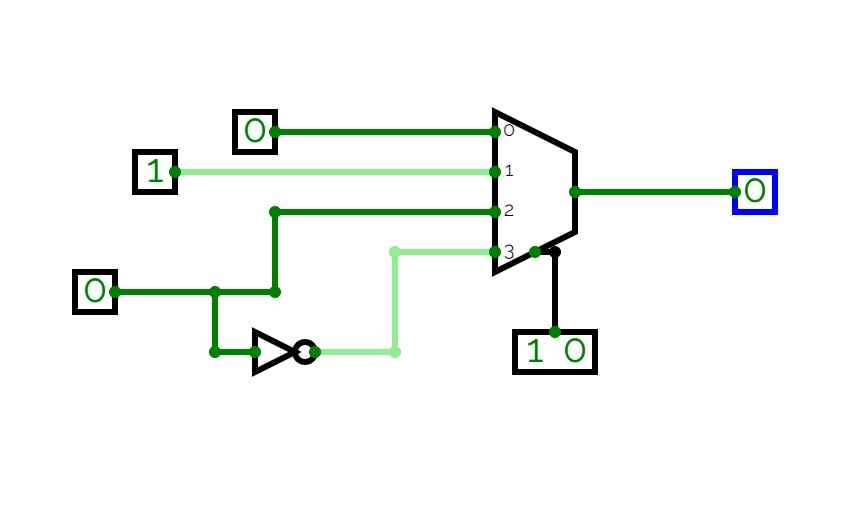

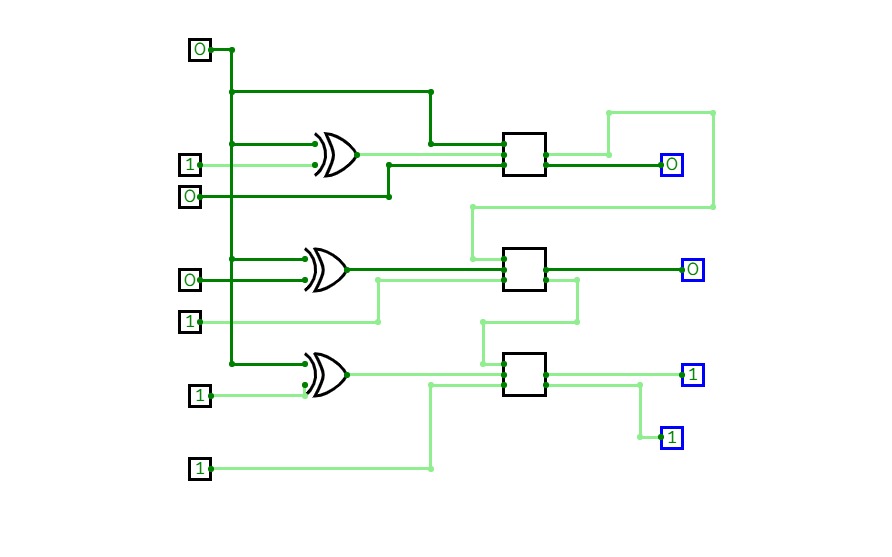

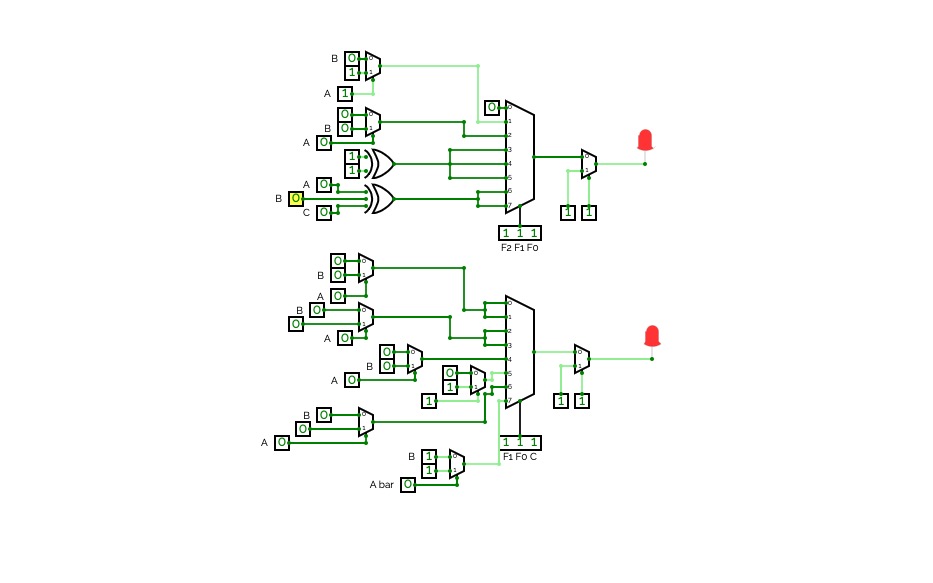

3 bit counter

3 bit counter3 bit counter

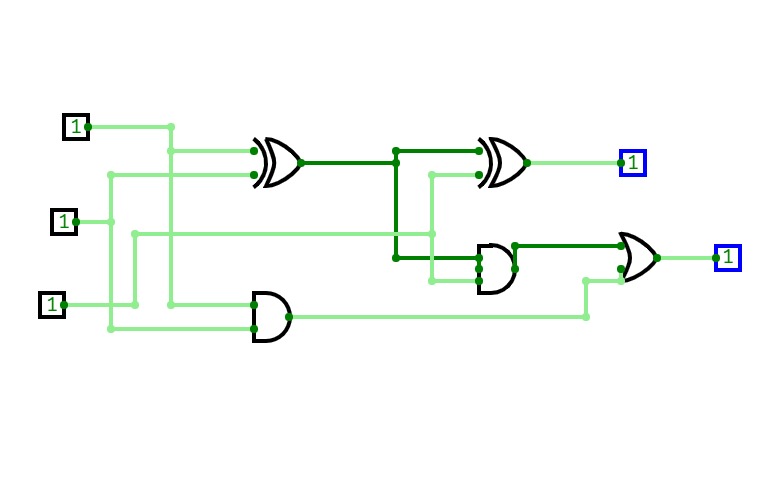

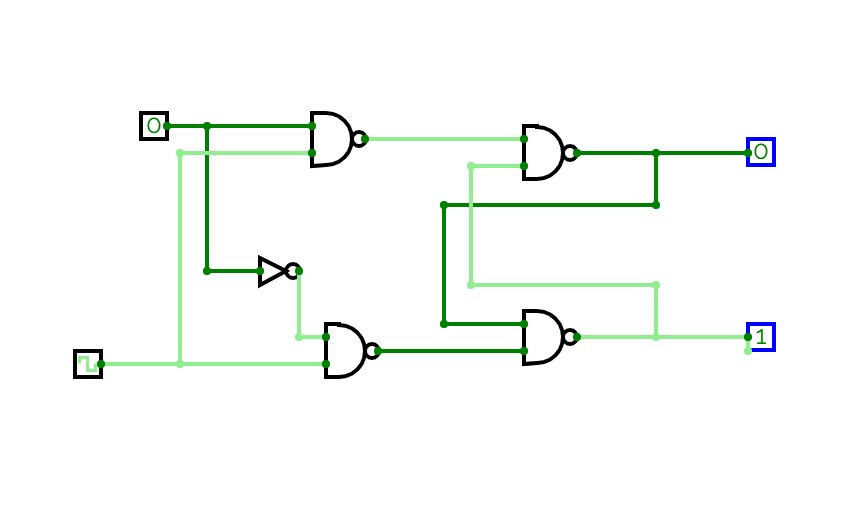

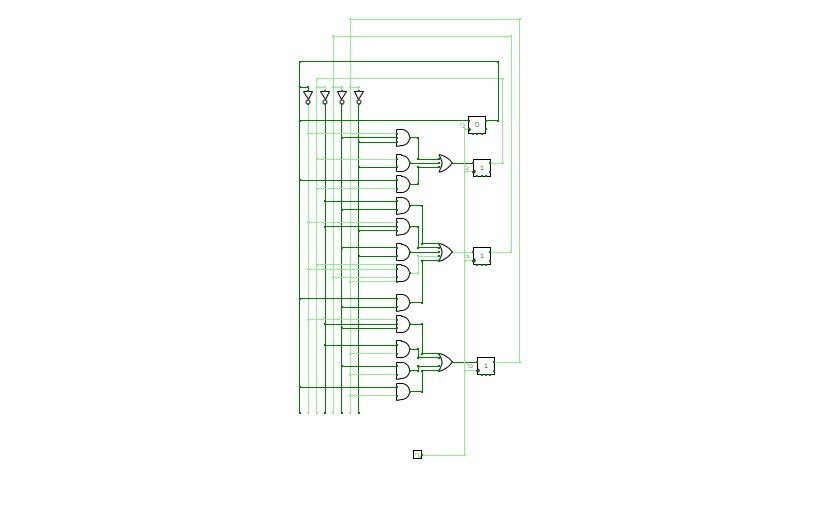

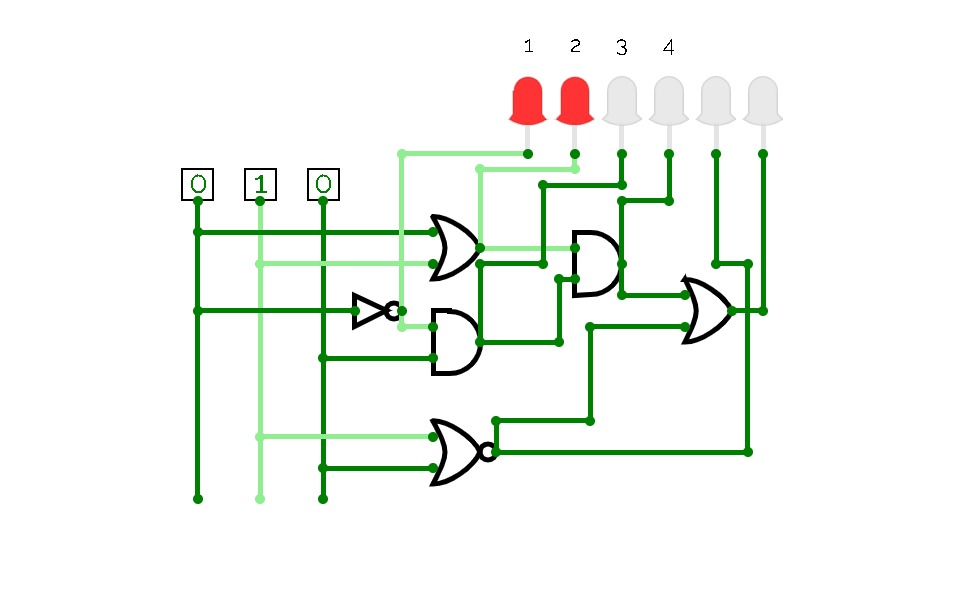

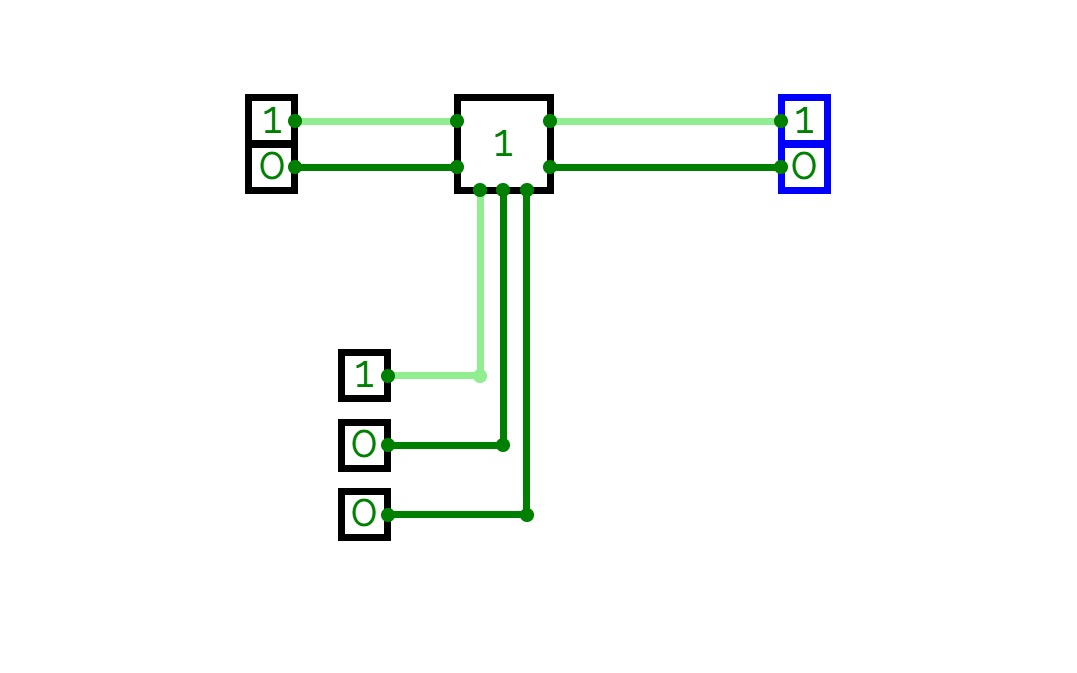

Practical 3

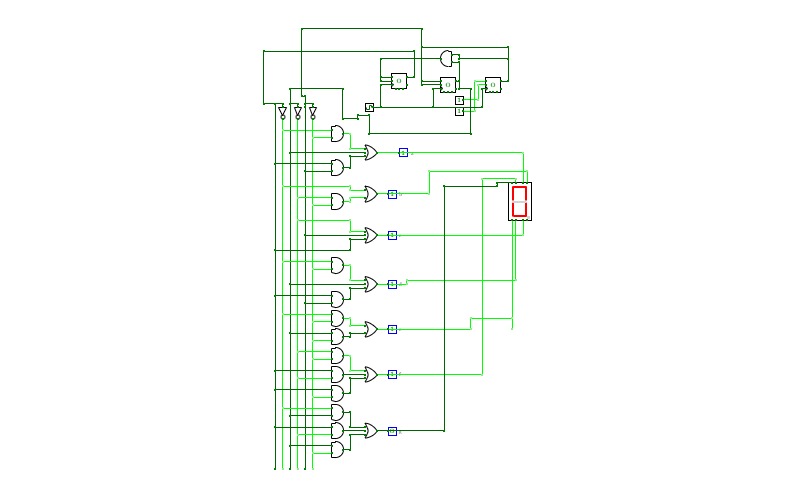

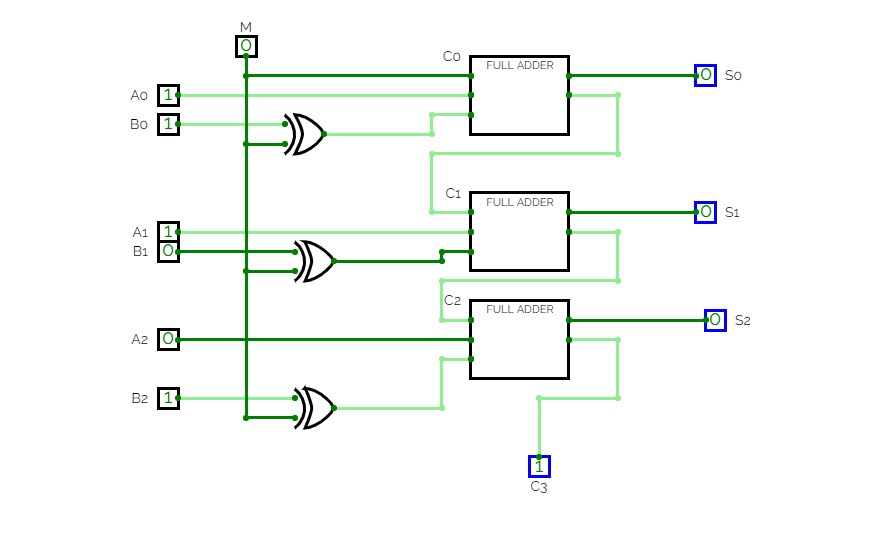

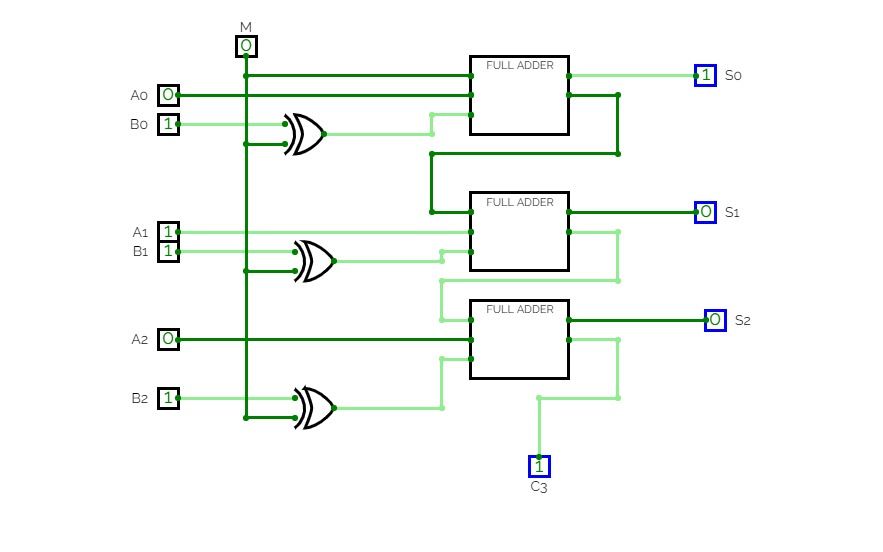

Practical 3AIM : IMPLEMENT 3-BIT PARALLEL BINARY ADDER/SUBTRACTOR

practical 3

practical 3AIM:IMPLEMENT 3BIT PARALLEL BINARY ADDER/SUBTRACTOR

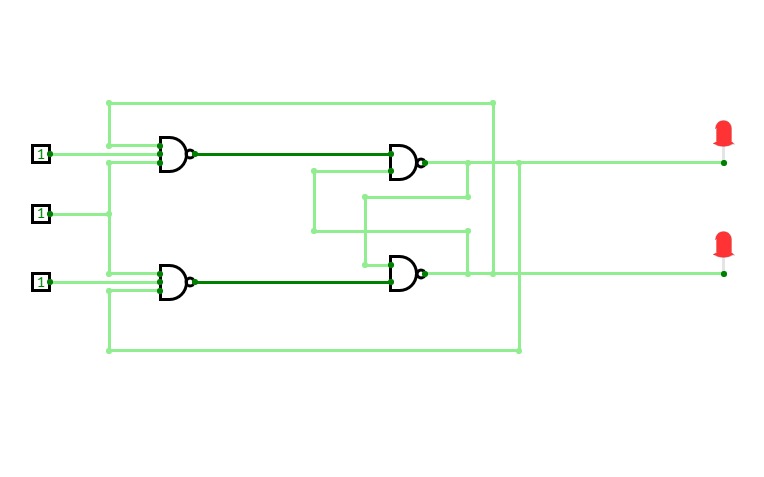

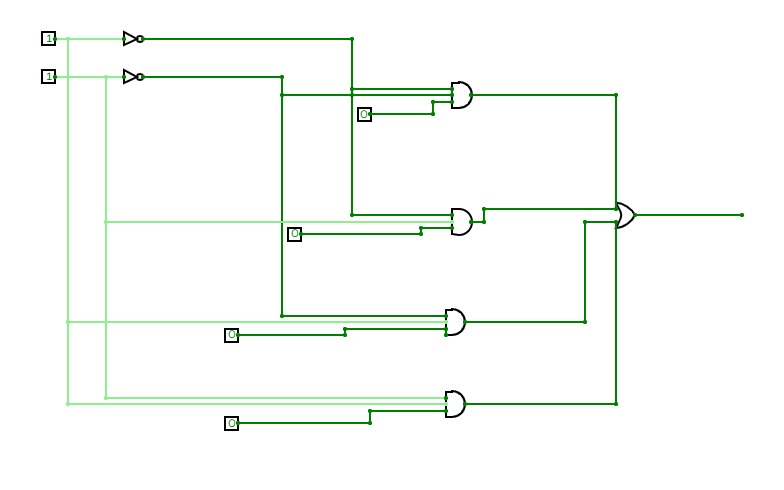

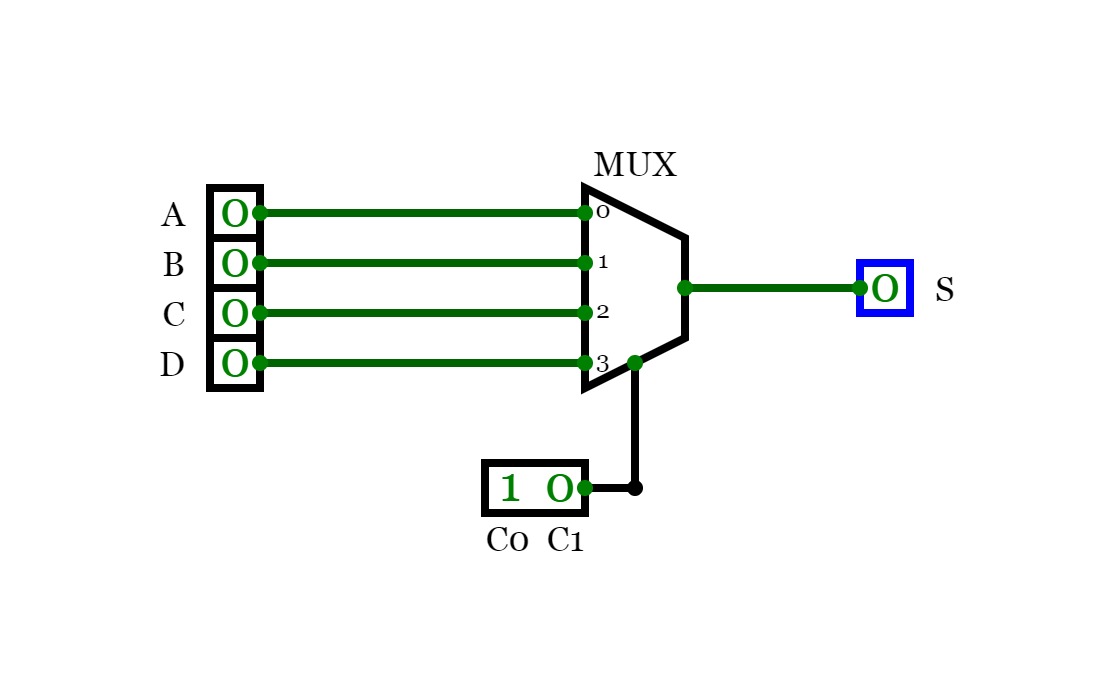

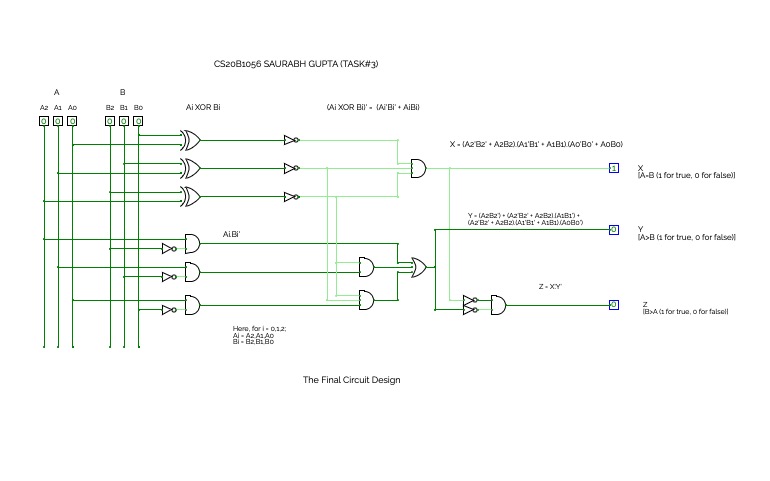

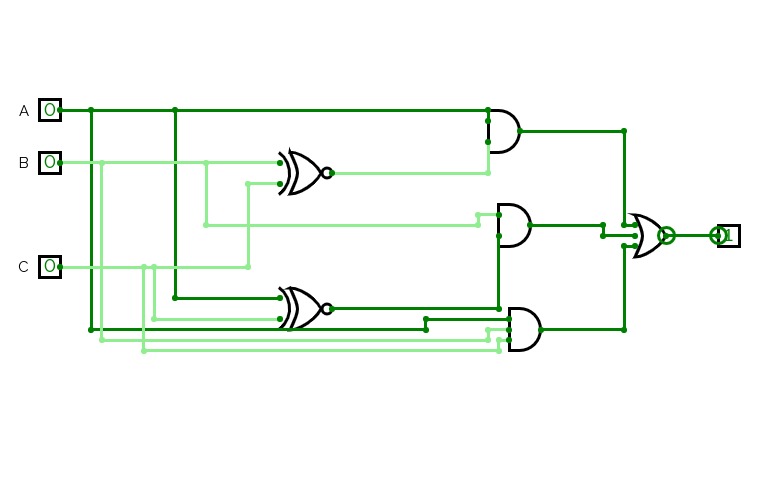

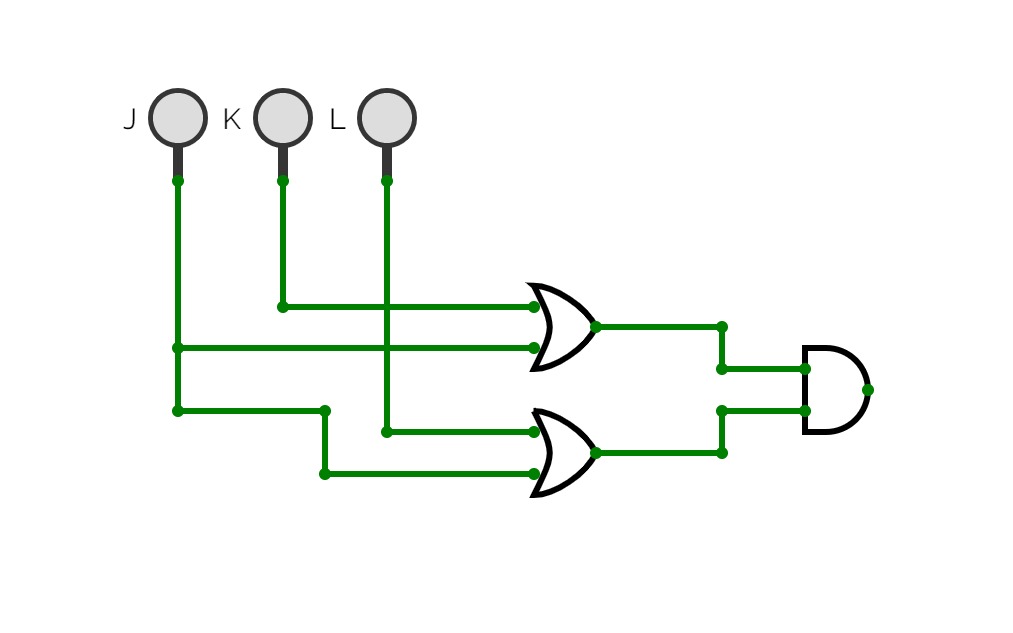

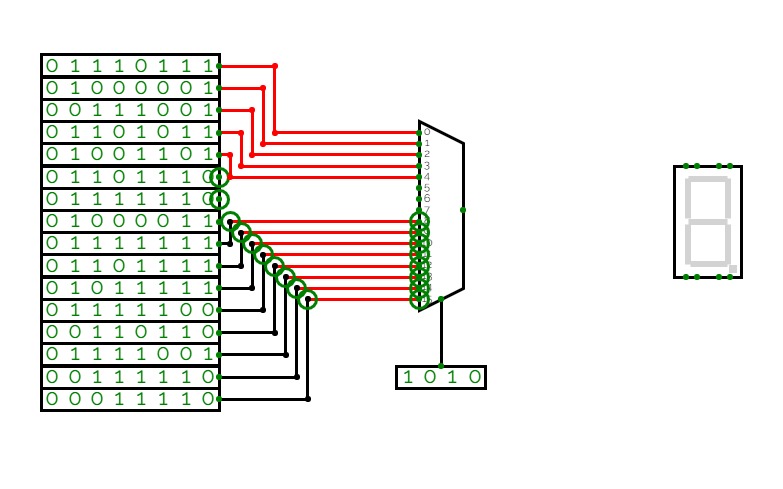

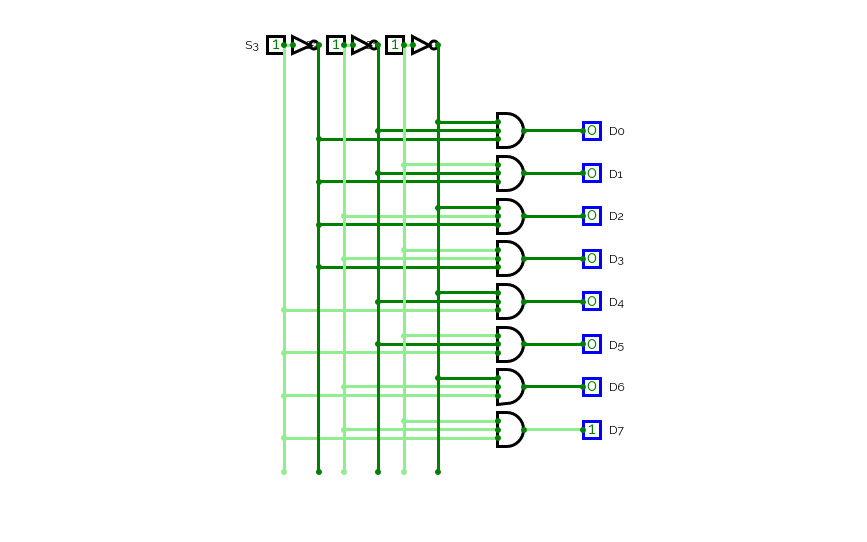

DSD Lab Assignment 2 (Task #3) - 3 Bit Magnitude Comparator

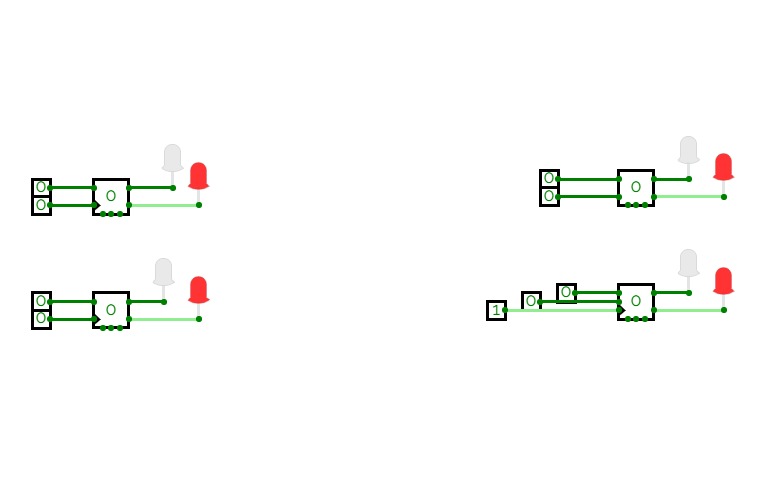

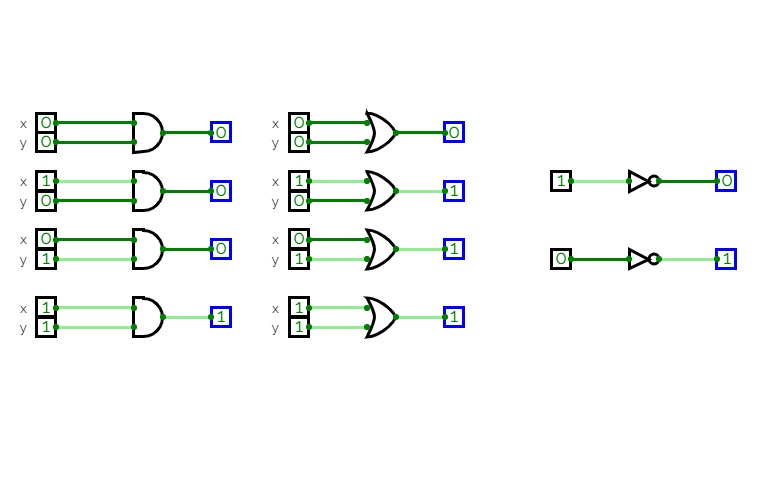

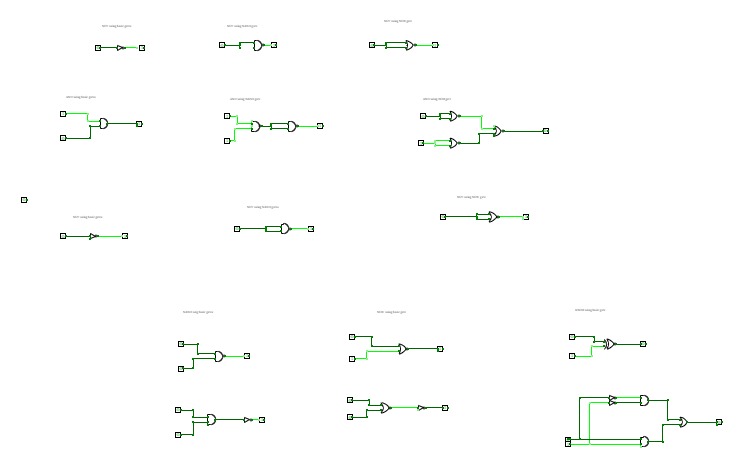

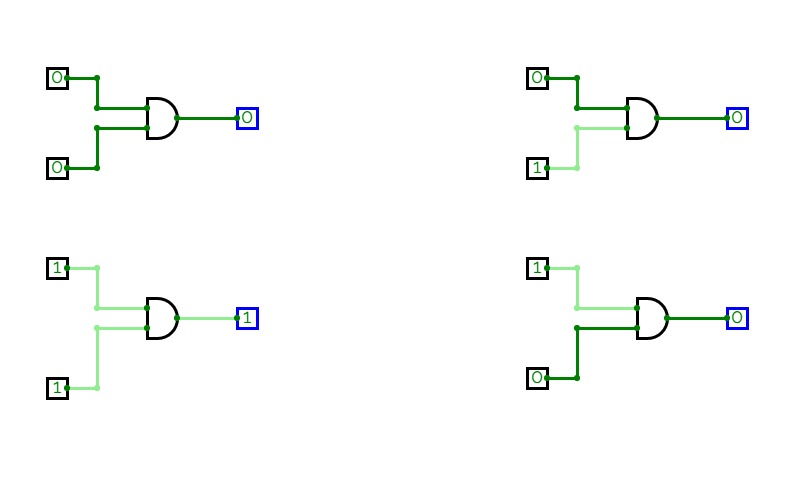

DSD Lab Assignment 2 (Task #3) - 3 Bit Magnitude Comparatorhis is a NOT-AND gate which is equal to an AND gate followed by a NOT gate. The outputs of all NAND gates are high if any of the inputs are low. The symbol is an AND gate with a small circle on the output. The small circle represents inversion.

This is a NOT-OR gate which is equal to an OR gate followed by a NOT gate. The outputs of all NOR gates are low if any of the inputs are high. The symbol is an OR gate with a small circle on the output. The small circle represents inversion.

The NOT gate is an electronic circuit that produces an inverted version of the input at its output. It is also known as an inverter. If the input variable is A, the inverted output is known as NOT A.

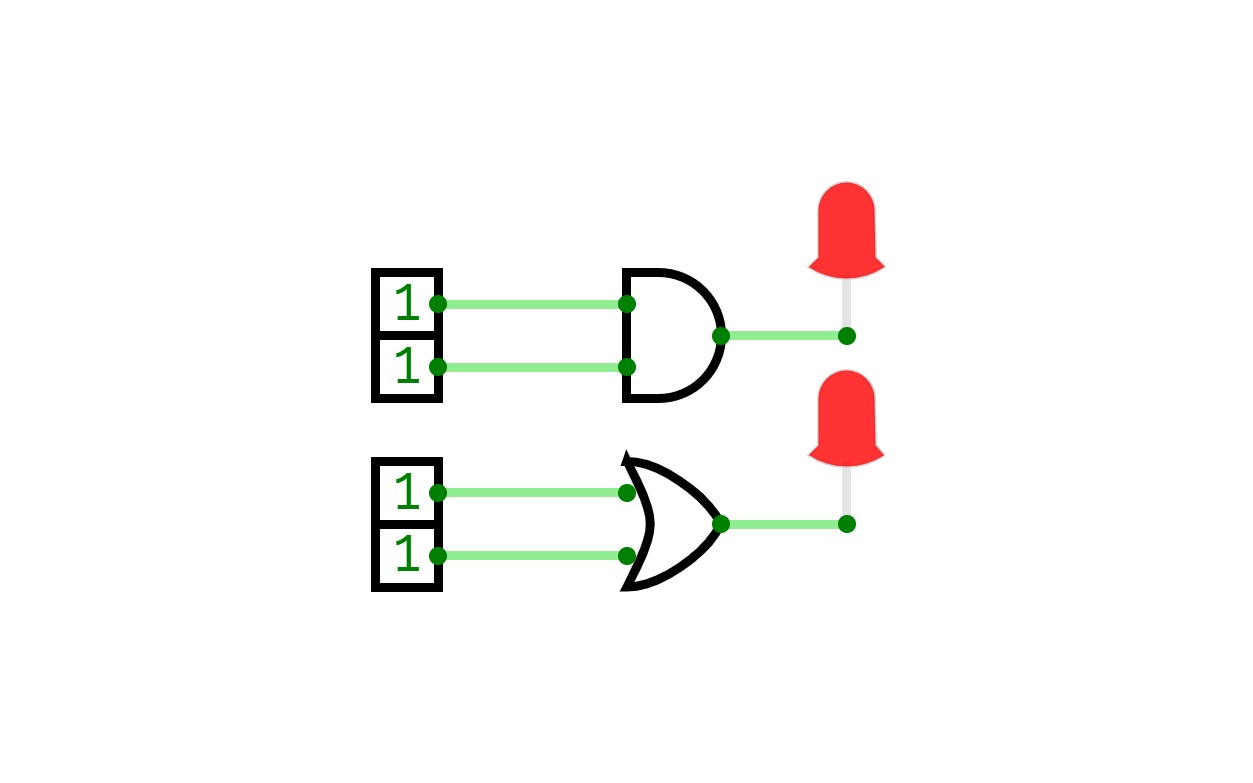

The 'Exclusive-OR' gate is a circuit which will give a high output if either, but not both of its two inputs are high. An encircled plus sign (⊕) is used to show the Ex-OR operation.

The 'Exclusive-NOR' gate circuit does the opposite to the EX-OR gate. It will give a low output if either, but not both of its two inputs are high. The symbol is an EX-OR gate with a small circle on the output. The small circle represent

_11zon.jpg)