Rakshitha

Member since: 2 years

Educational Institution: presidency university banglore

Country: India

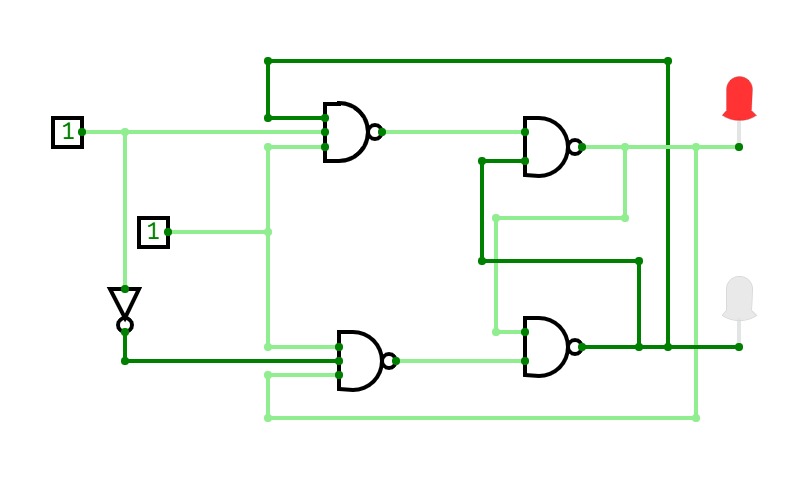

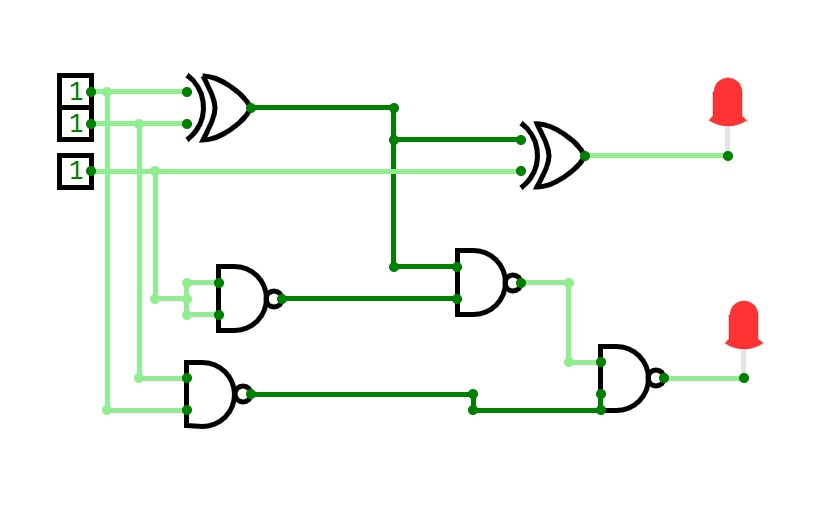

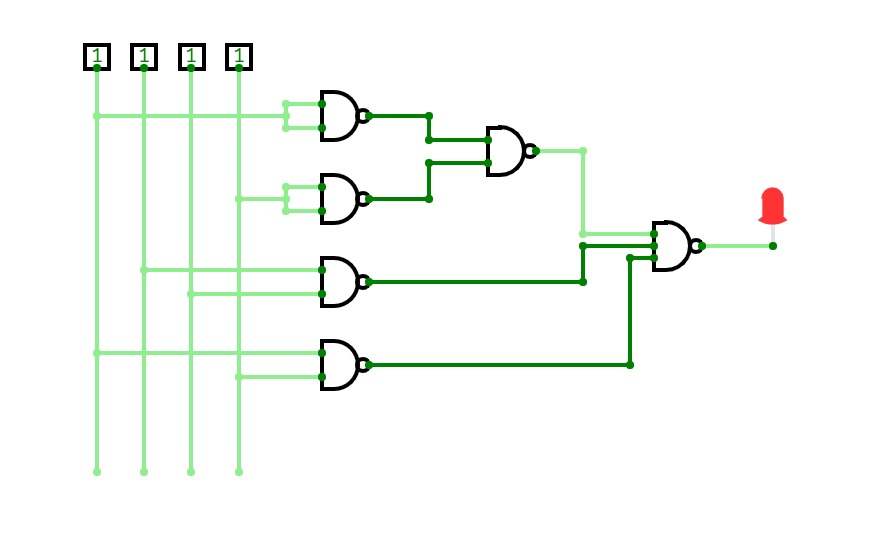

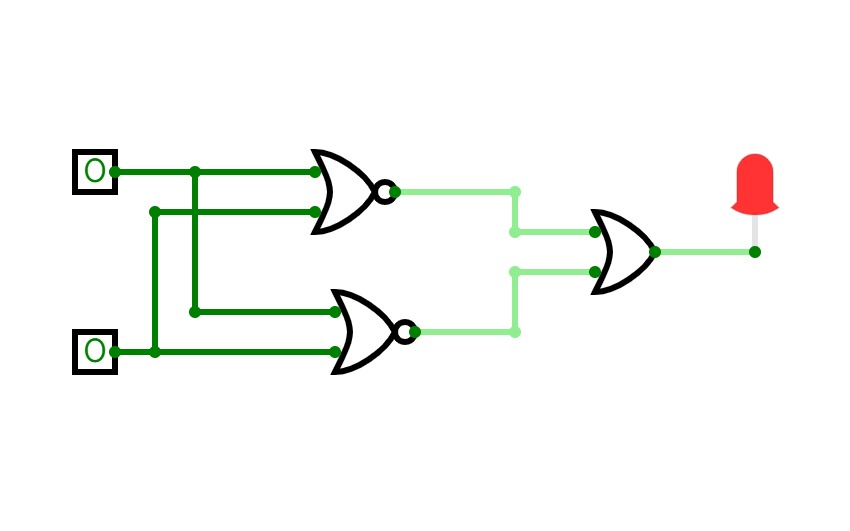

full adder

full adder

exp 2

exp 2

LEVEL 2 DEMUX

LEVEL 2 DEMUX

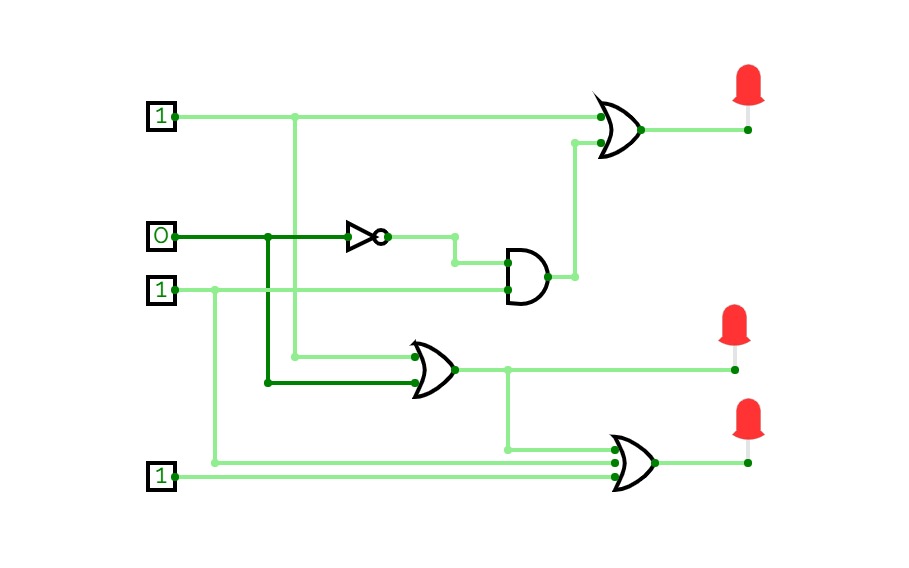

full subtractor

full subtractor

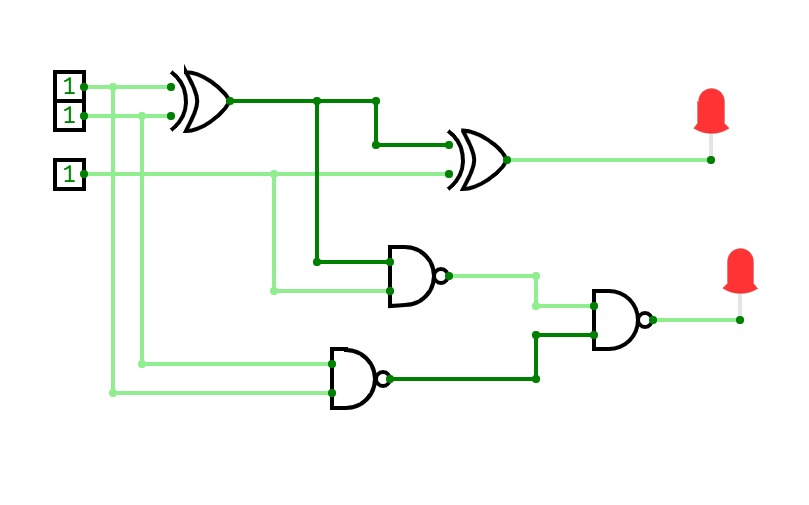

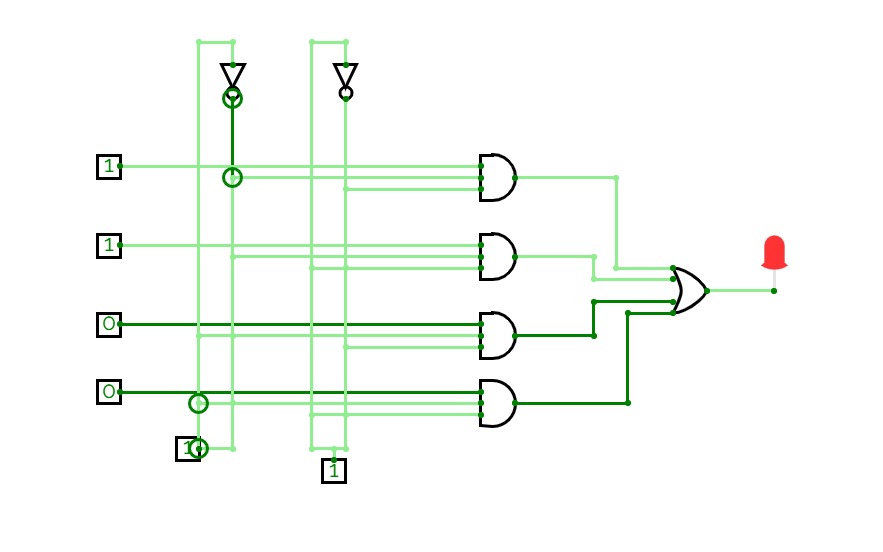

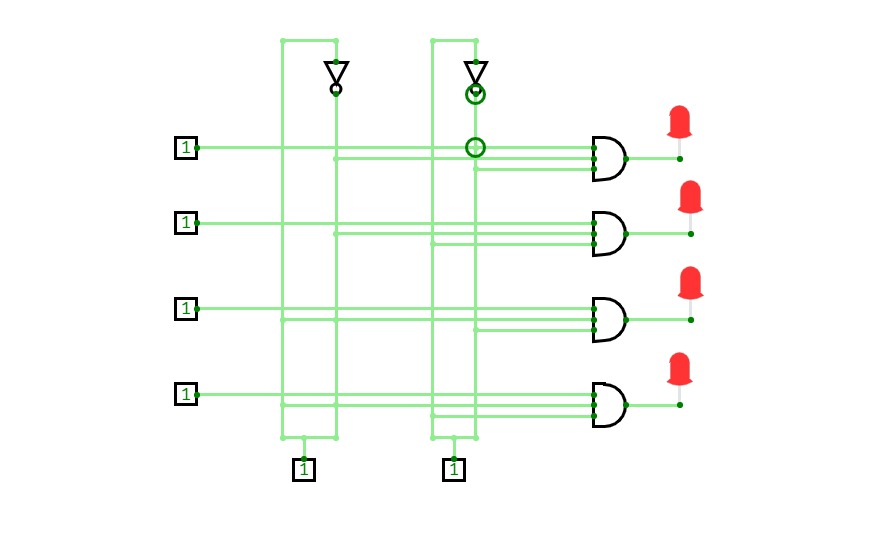

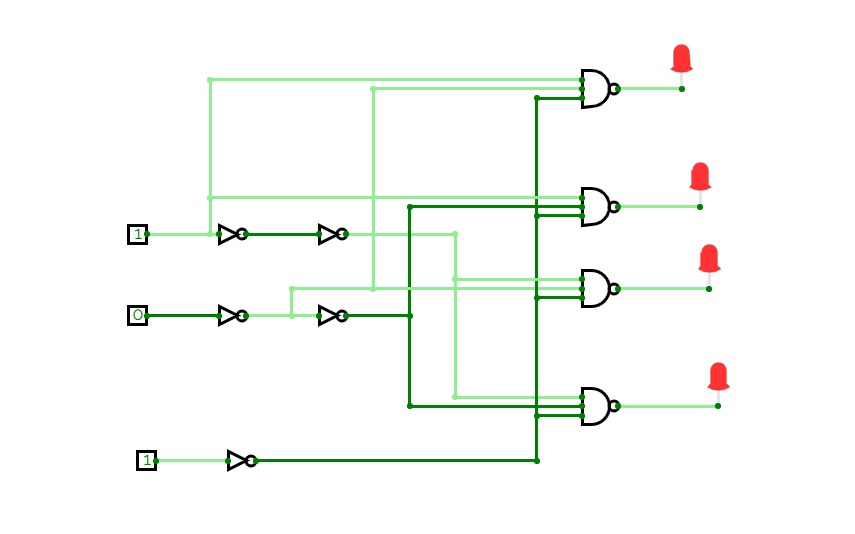

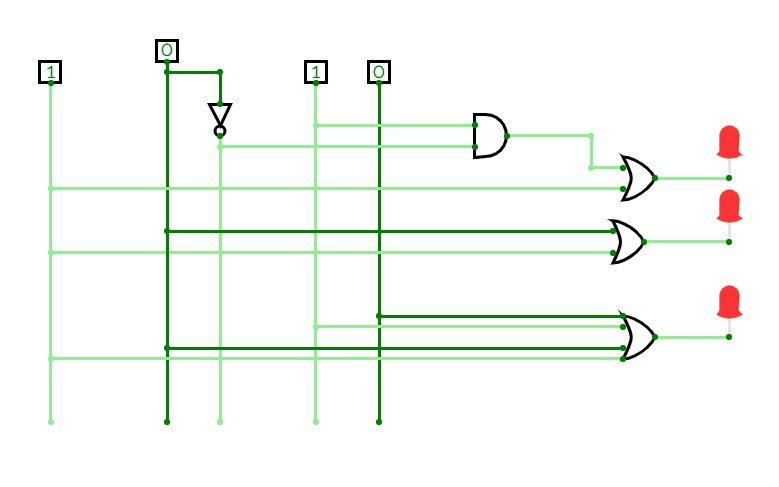

2 to 4 decoder

2 to 4 decoder

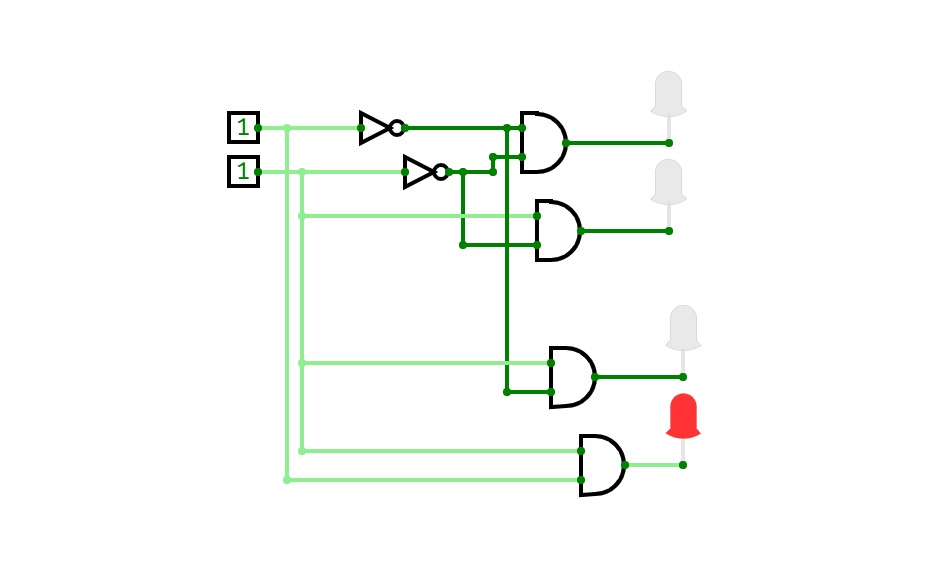

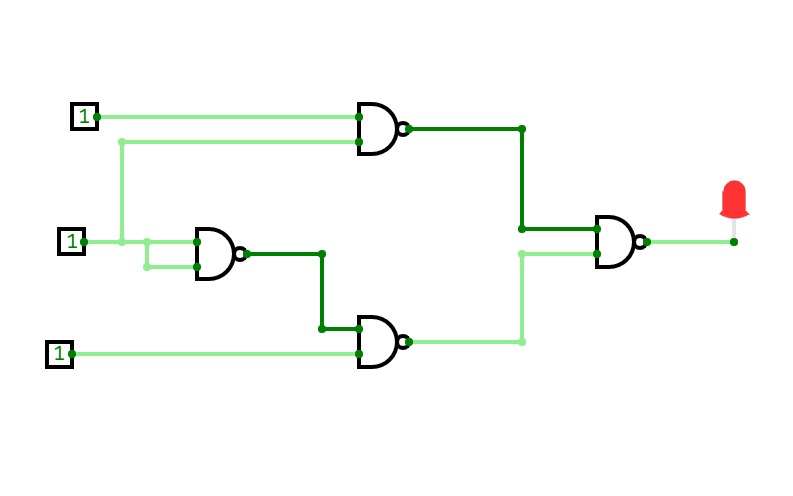

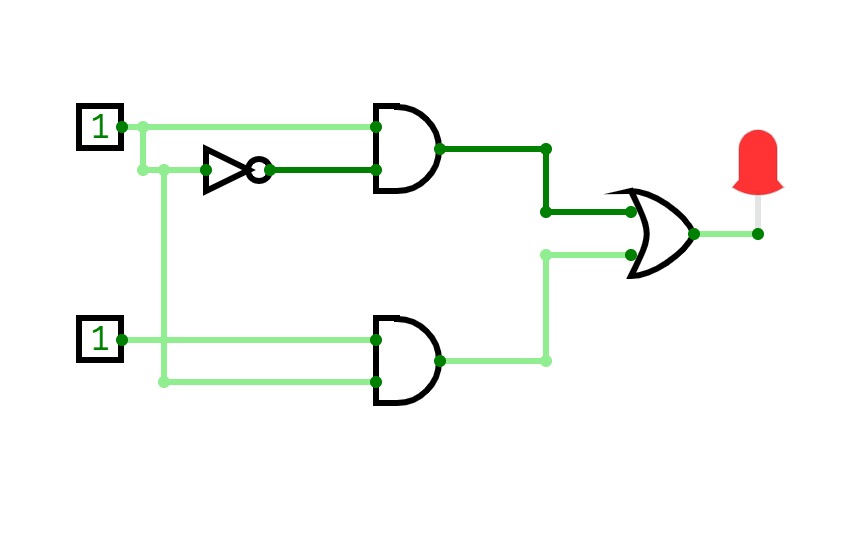

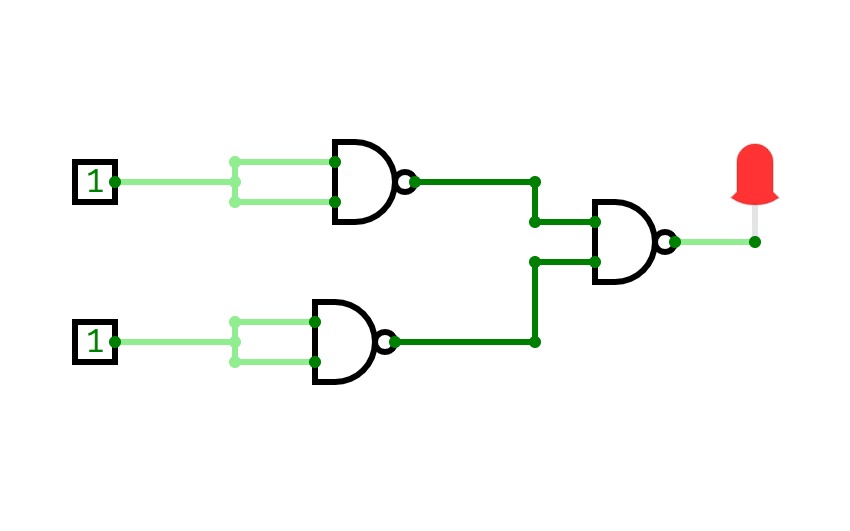

level 2 half adder using nand gate only

level 2 half adder using nand gate only

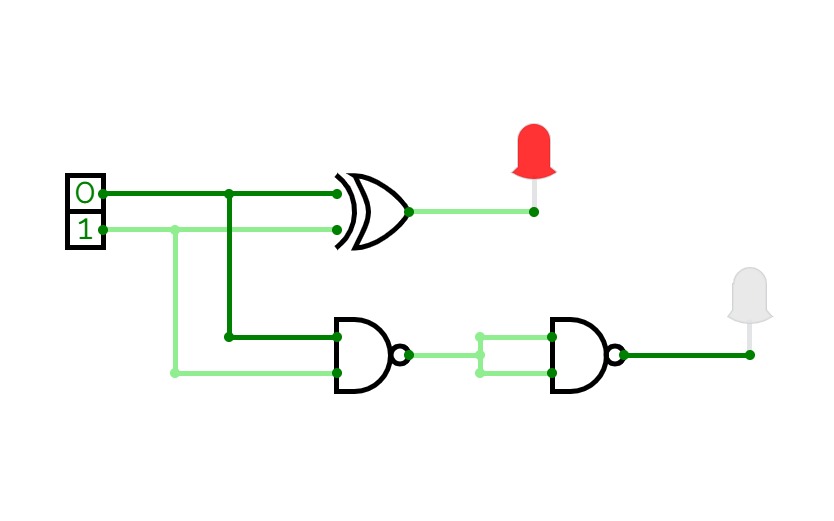

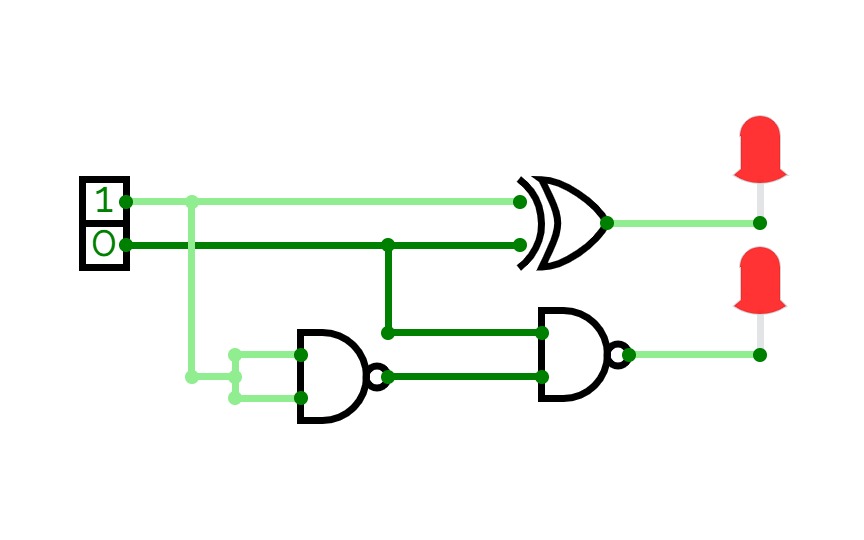

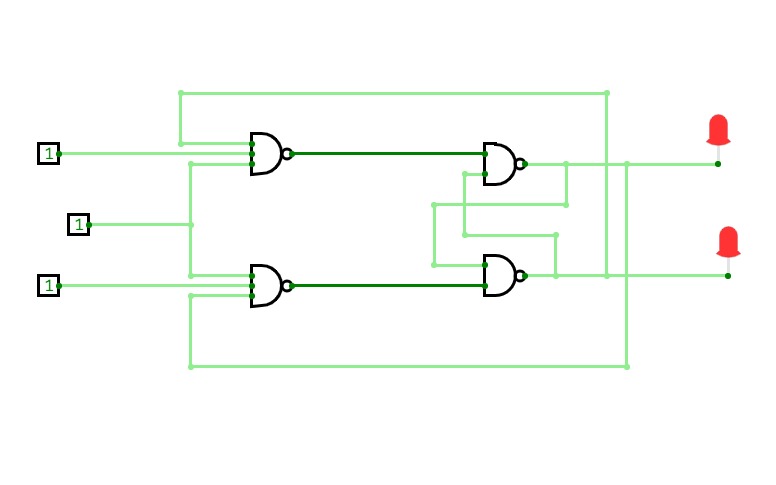

half adder using XOR and NAND gate

half adder using XOR and NAND gate

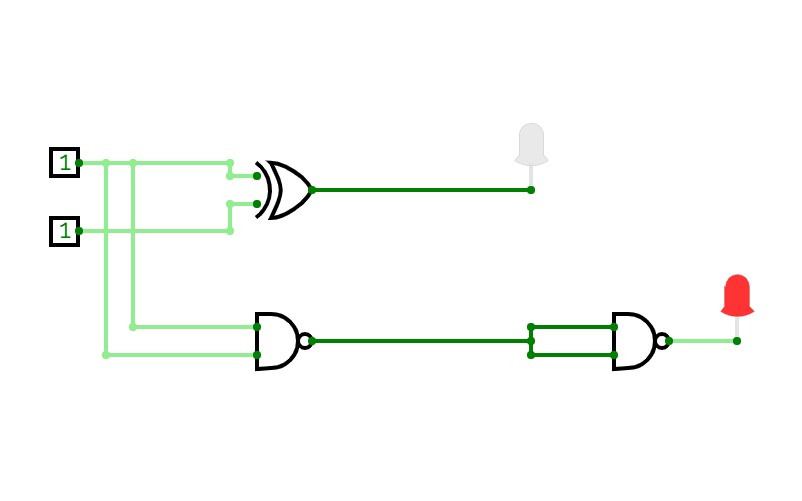

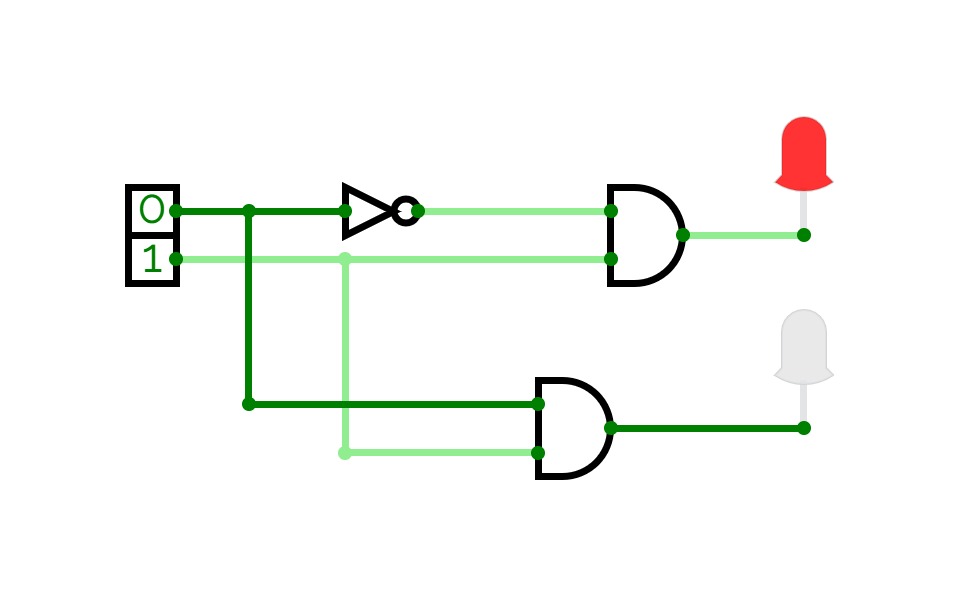

half subtractor using XOR and NANAD Gates

half subtractor using XOR and NANAD Gates

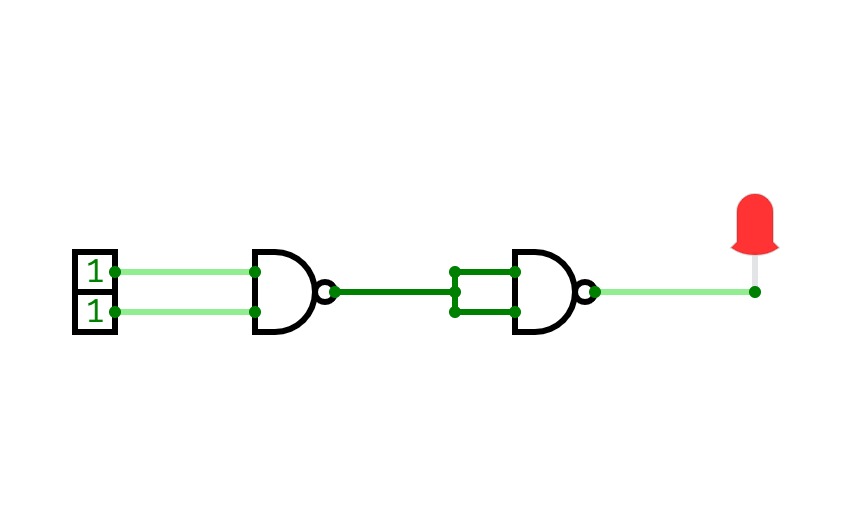

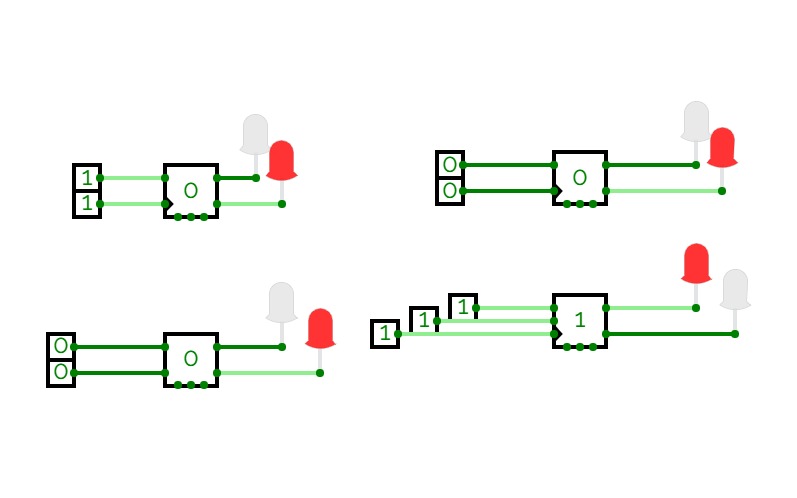

AND gate using NAND gate

AND gate using NAND gate

4:1 MUX using basic gates and XOR gate

4:1 MUX using basic gates and XOR gate

DEMUX

DEMUX

DEMULTIPLEXER

DEMULTIPLEXER

LEVEL2- Using universal gate MUX

LEVEL2- Using universal gate MUX

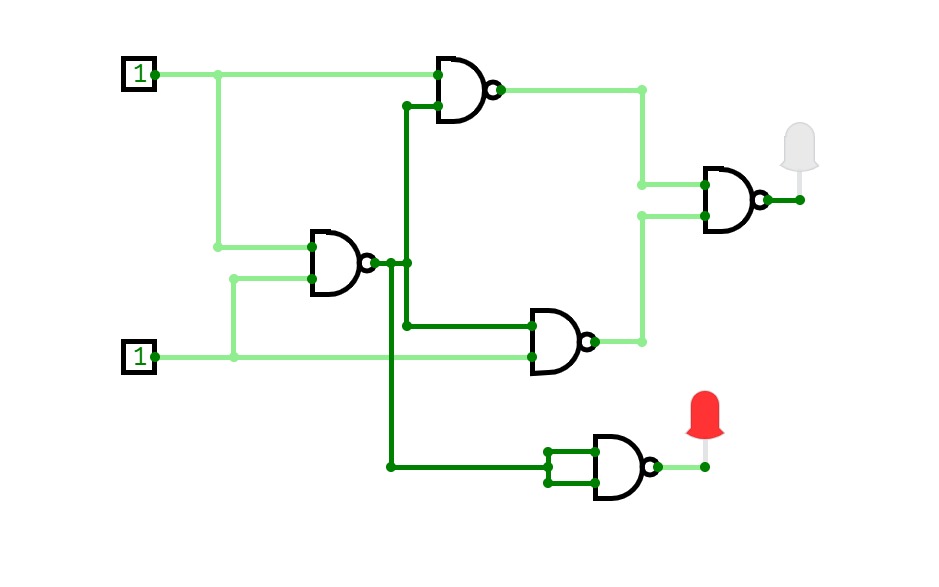

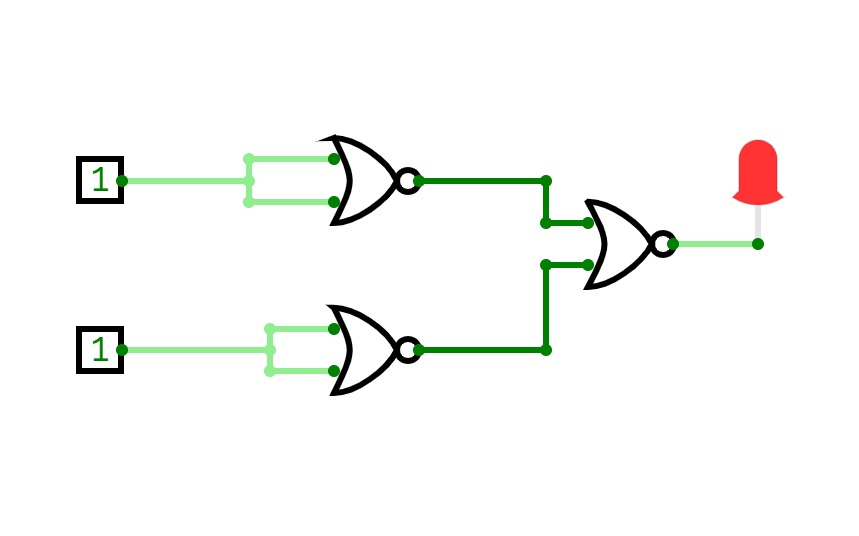

level 2 half subtractor using nand gate only

level 2 half subtractor using nand gate only

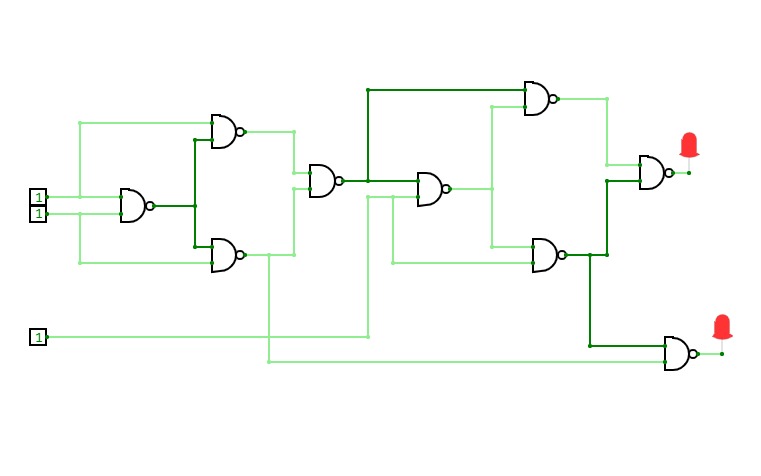

level 2 full subtractor using nand gate only

level 2 full subtractor using nand gate only

exp 3 MUX using basic and XOR gate

exp 3 MUX using basic and XOR gate

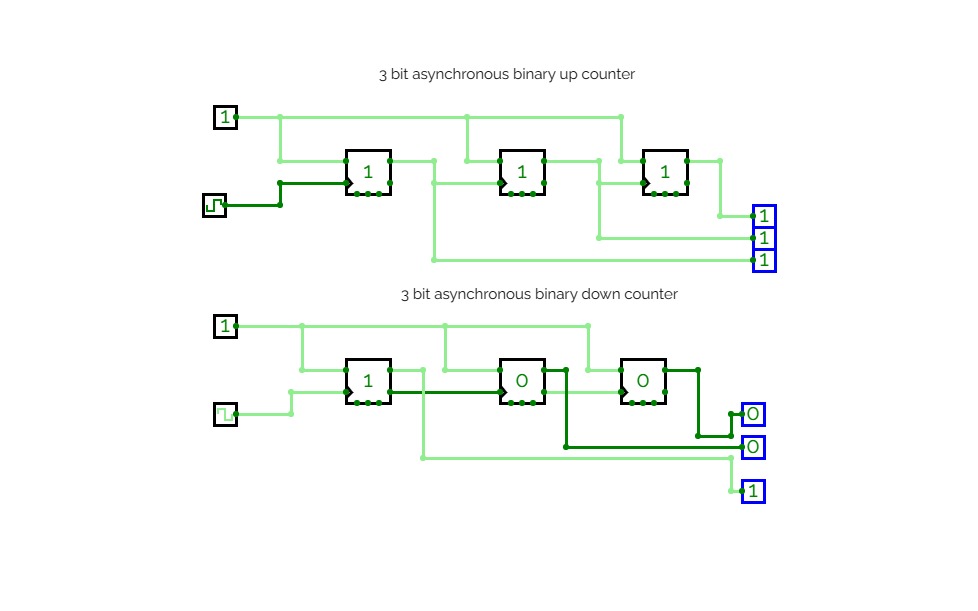

Experiment-8

Experiment-8

Experiment-7

Experiment-7

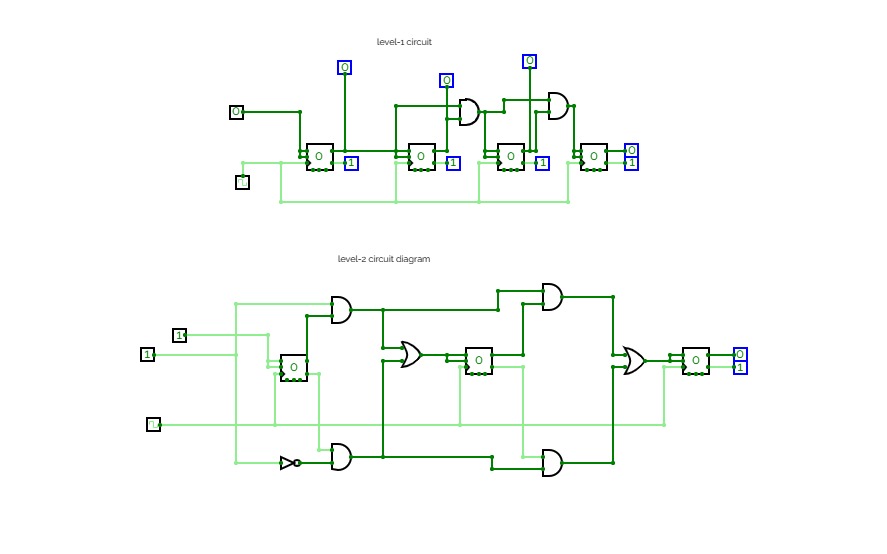

Digital of logic diagram using basic gates

Digital of logic diagram using basic gates

exp 5: design of logic diagram using NAND gates

exp 5: design of logic diagram using NAND gates

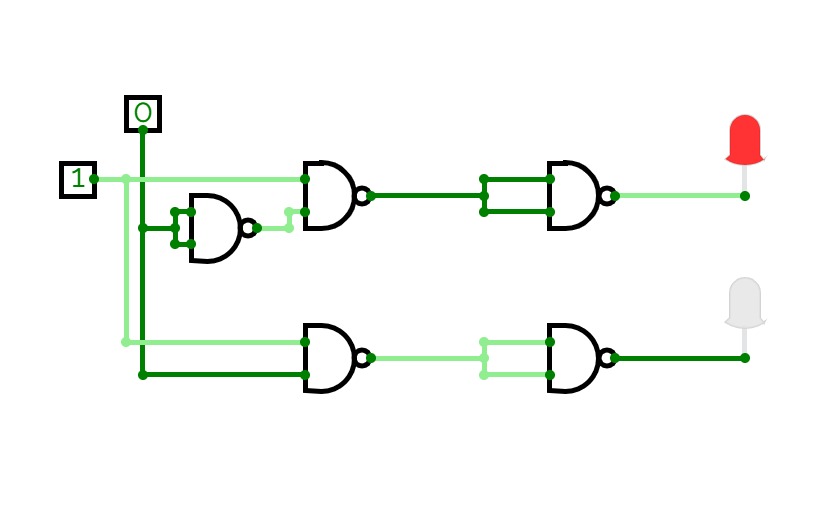

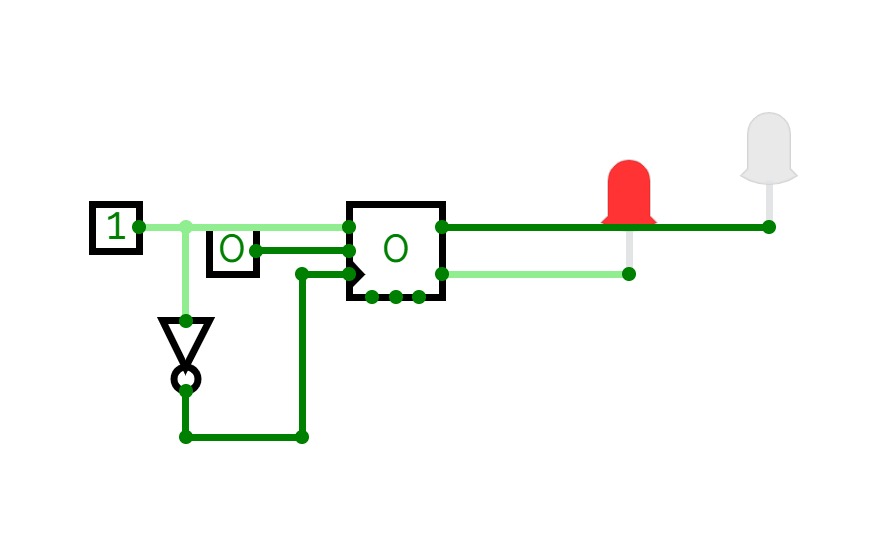

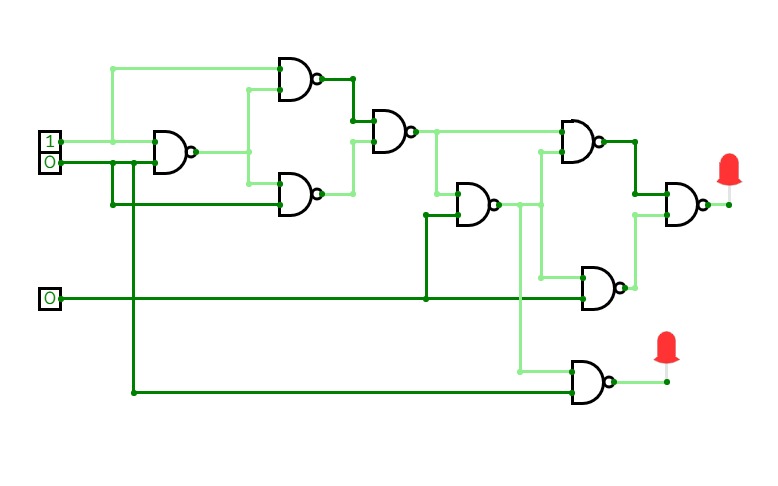

level 2:exp 6 JK To D Flip-flop conversion

level 2:exp 6 JK To D Flip-flop conversion

LEVEL 2 DEMUX USING UNIVERSAL GATE

LEVEL 2 DEMUX USING UNIVERSAL GATE

LEVEL 2: Priority encoder

LEVEL 2: Priority encoder

OR gate using NOR gate

OR gate using NOR gate

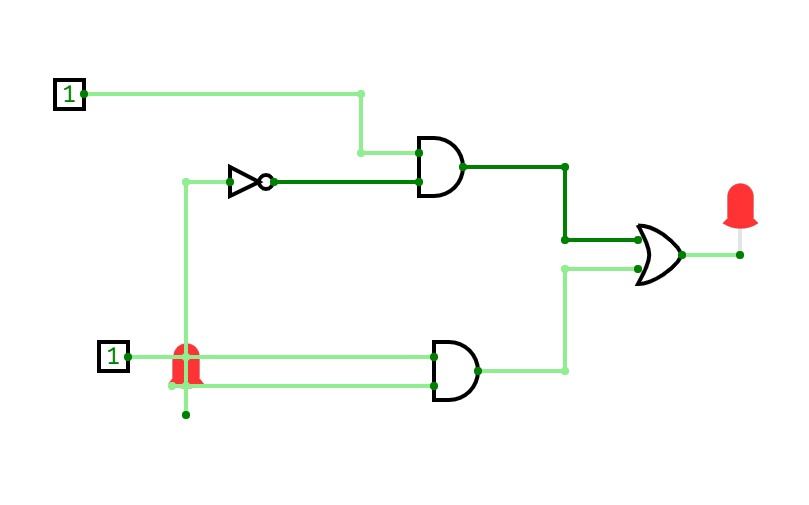

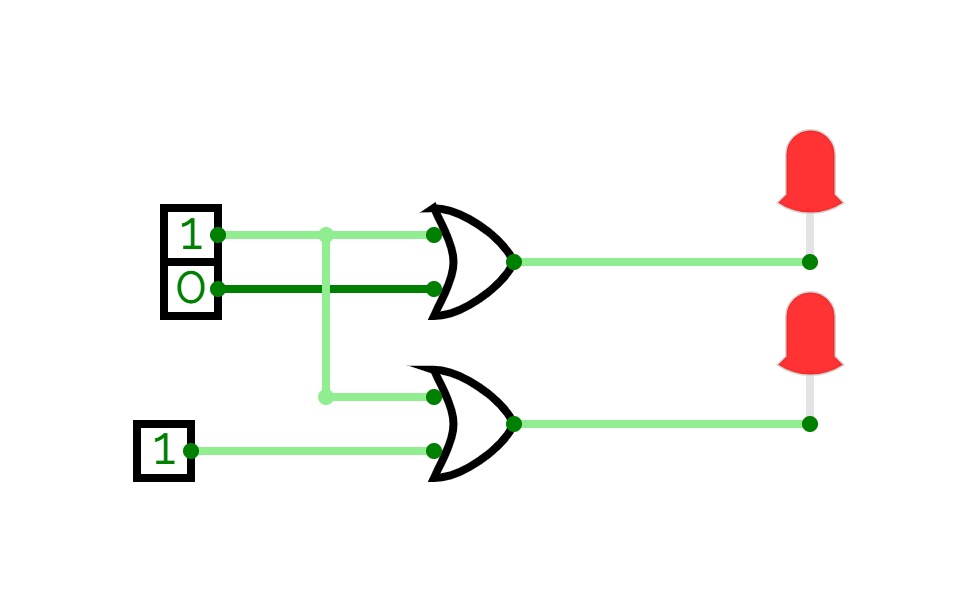

2-to-1 multiplexer

2-to-1 multiplexer

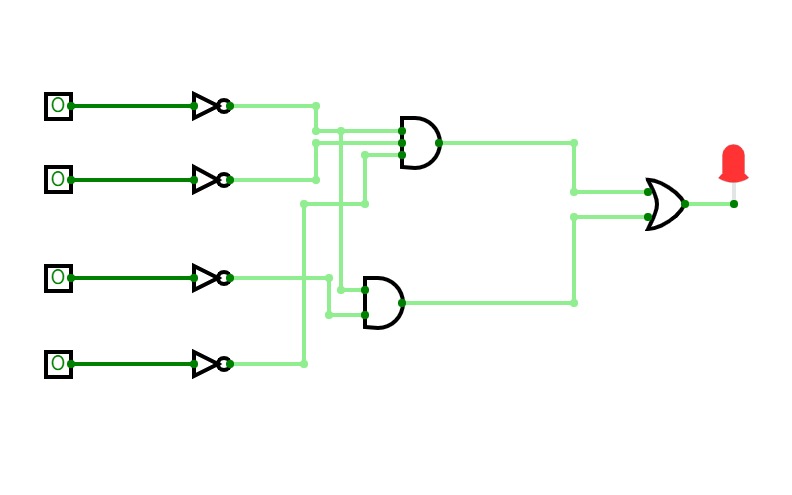

4:2 Priority encoder

4:2 Priority encoder

AND Gate using NOR Gate

AND Gate using NOR Gate

MUX USING UNIVERSAL GATE

MUX USING UNIVERSAL GATE

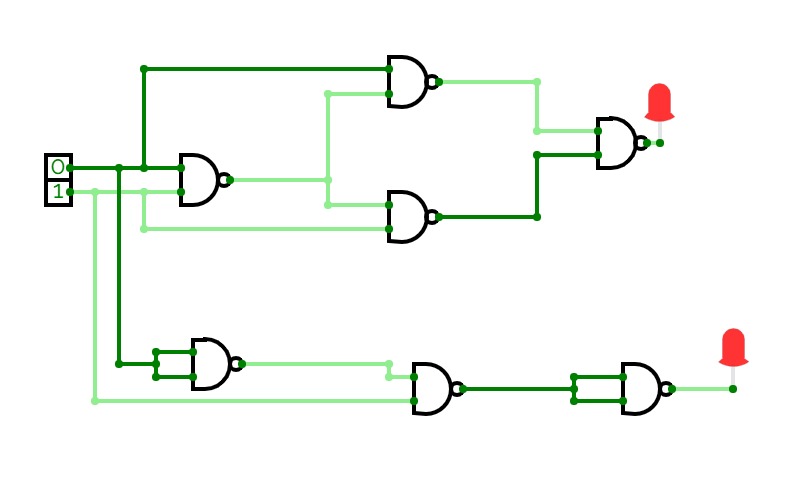

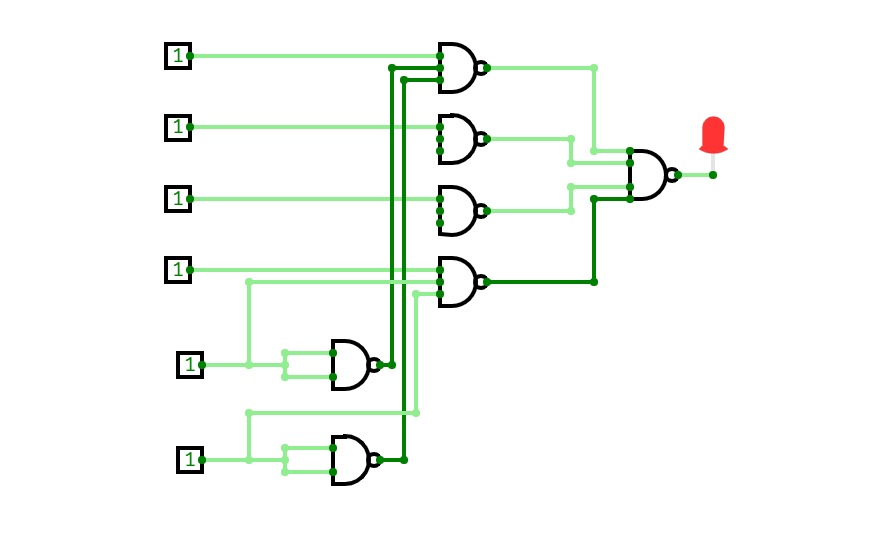

level 2 full adder using nand gate only

level 2 full adder using nand gate only

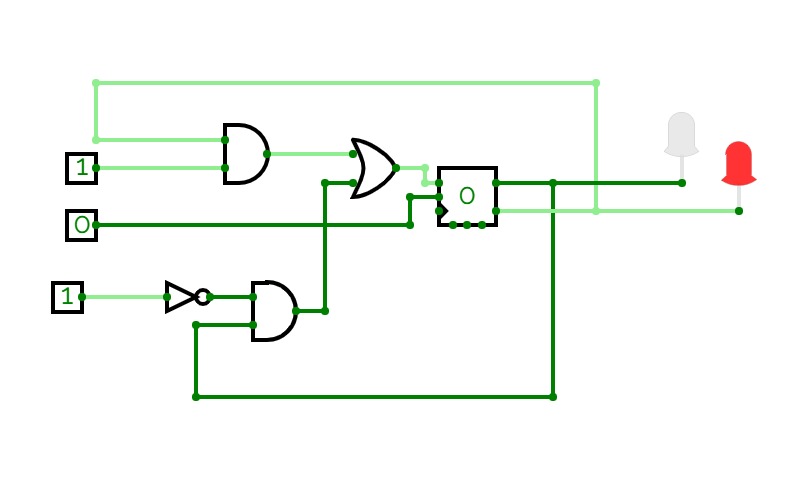

EXP 6: JK Flip-flop implementation using nand gate

EXP 6: JK Flip-flop implementation using nand gate

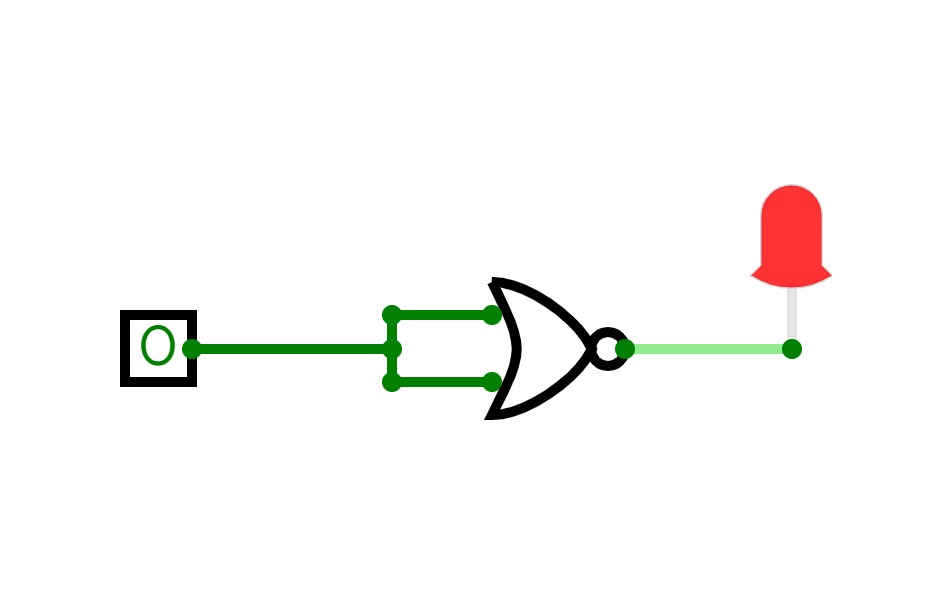

NOT gate using NOR gate

NOT gate using NOR gate

EXP 6: D,T,SR,JK Flip-flops

EXP 6: D,T,SR,JK Flip-flops

exp 6: Conversion of one FF to other

exp 6: Conversion of one FF to other

OR Gate using NAND Gate

OR Gate using NAND Gate

EXP 4...encoder and decoder logic circuits

EXP 4...encoder and decoder logic circuits

EXP 6: JK To D Flip-flop

EXP 6: JK To D Flip-flop