Dhrithi

Member since: 2 years

Educational Institution: Presidency University , Banglore.

Country: India

Untitled

Untitled

D,T,SR,JK Flip flop

D,T,SR,JK Flip flop

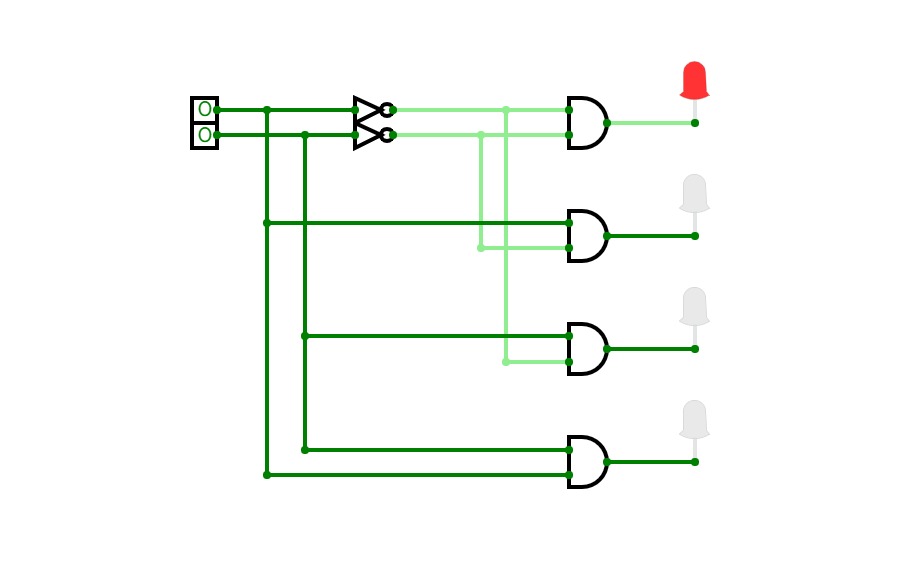

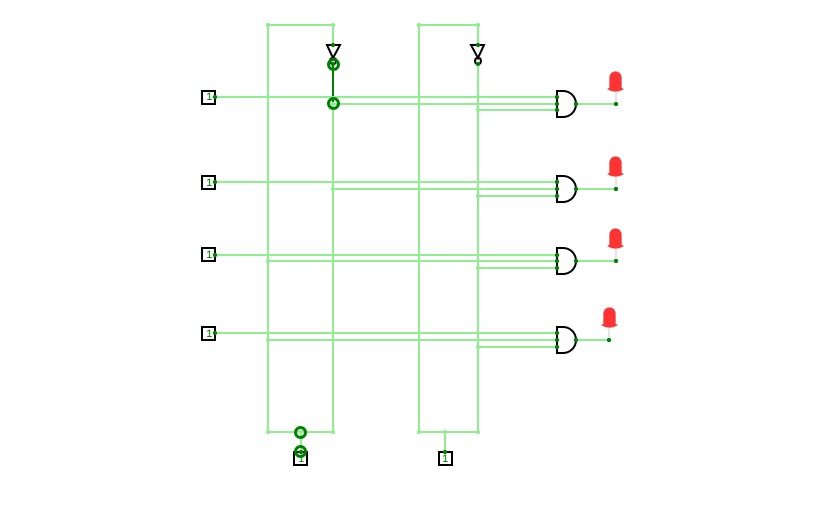

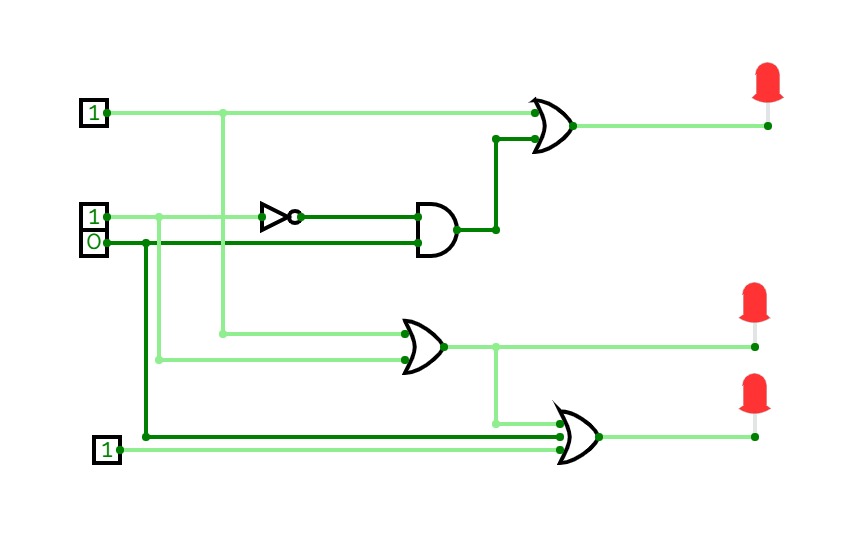

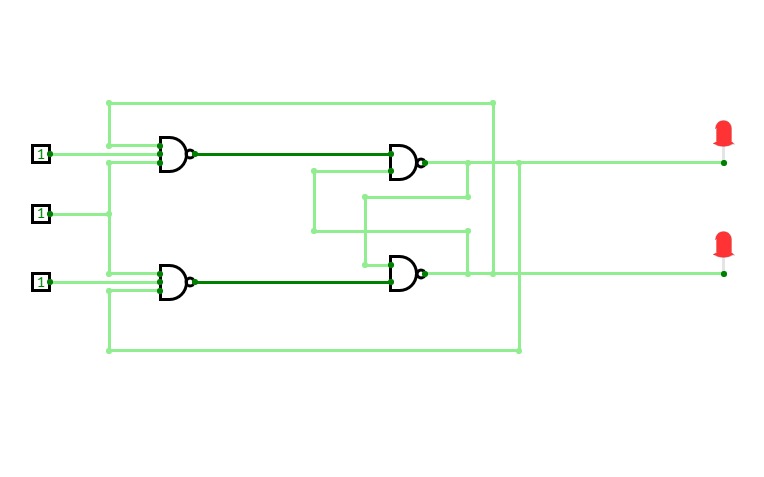

2 to 4 decoder

2 to 4 decoder

4 to 2 decoder

4 to 2 decoder

1 to 4 DE-Multiplexer

1 to 4 DE-Multiplexer

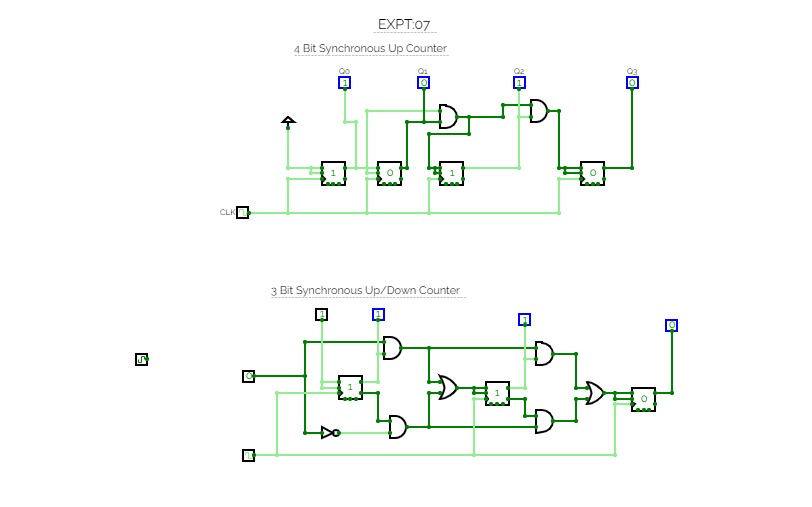

EXPT:07

EXPT:07

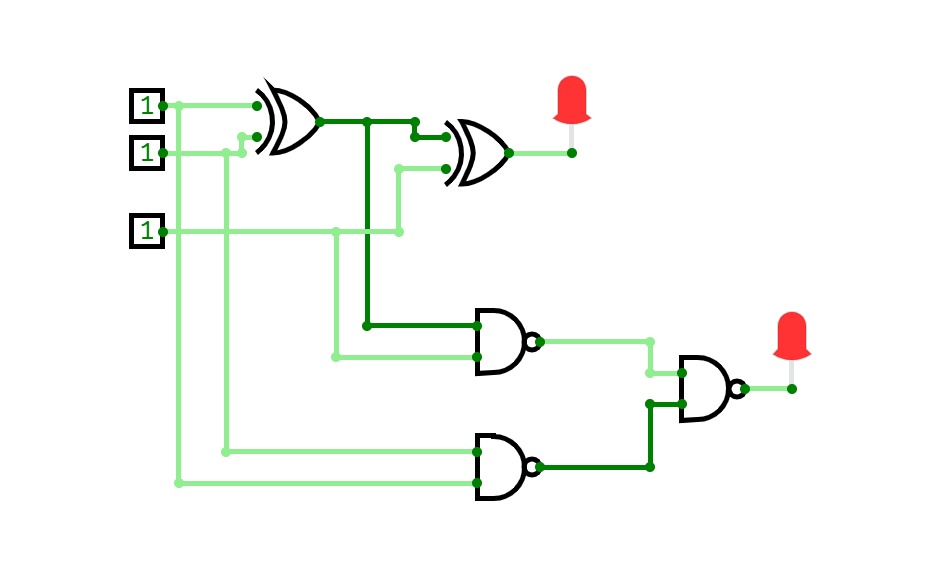

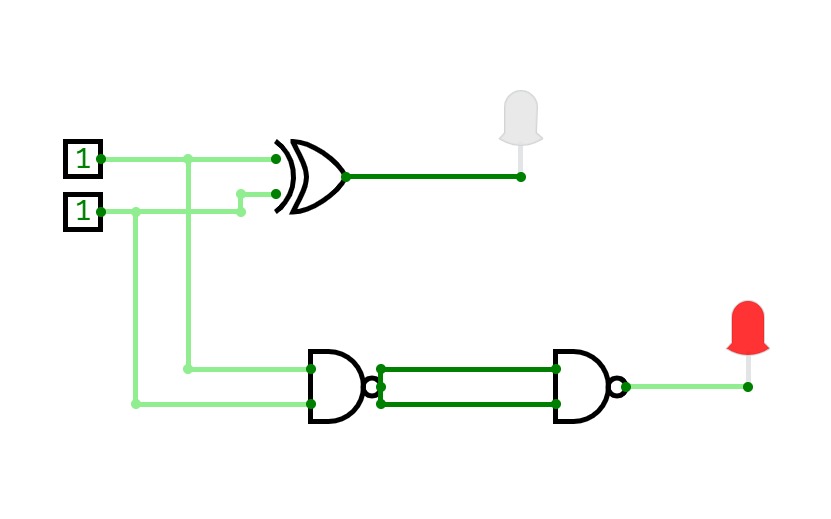

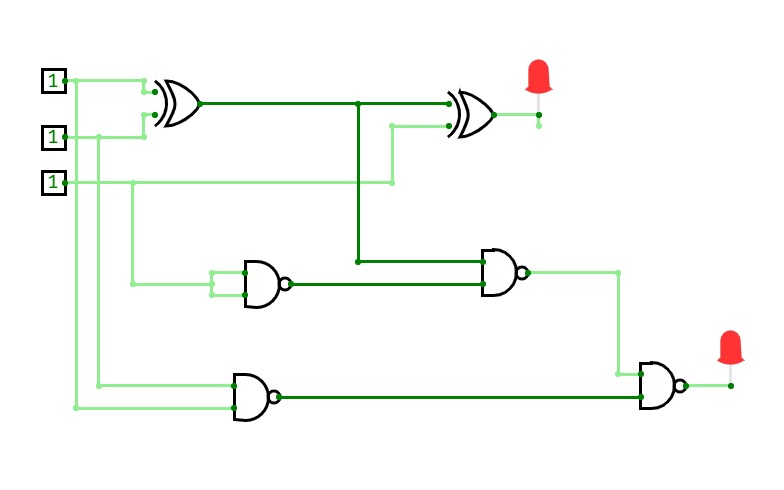

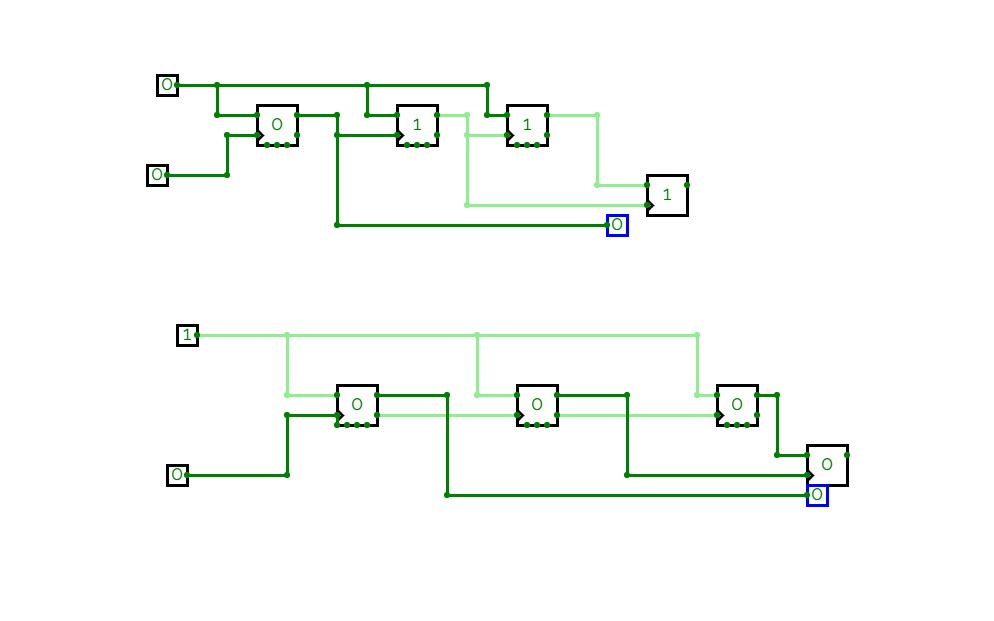

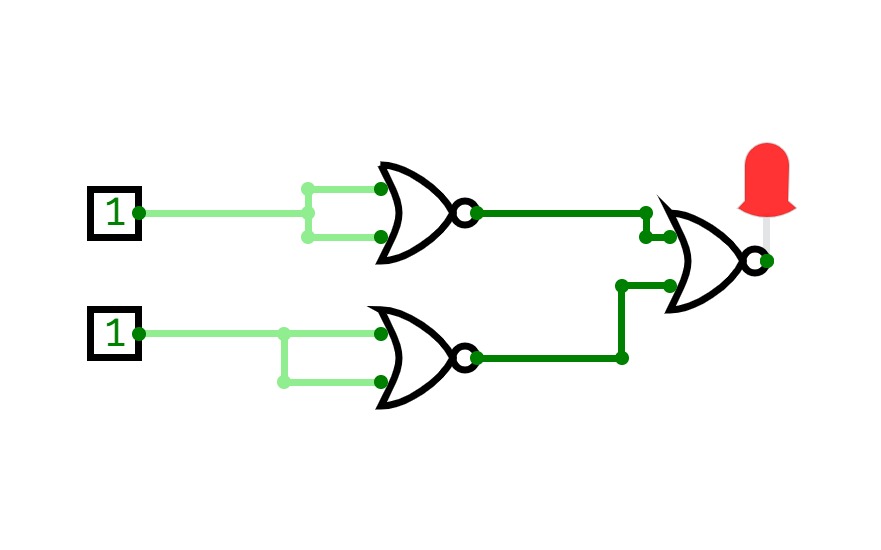

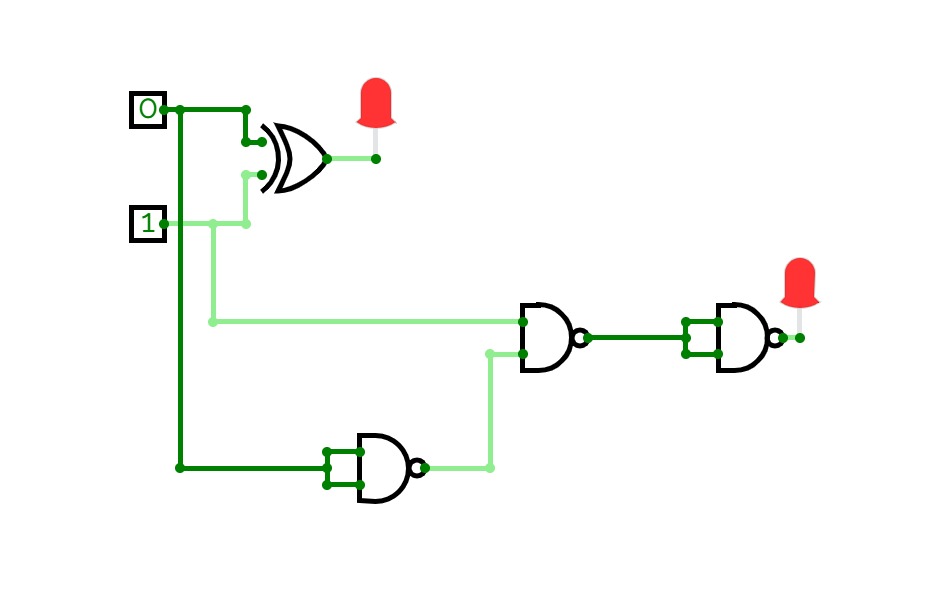

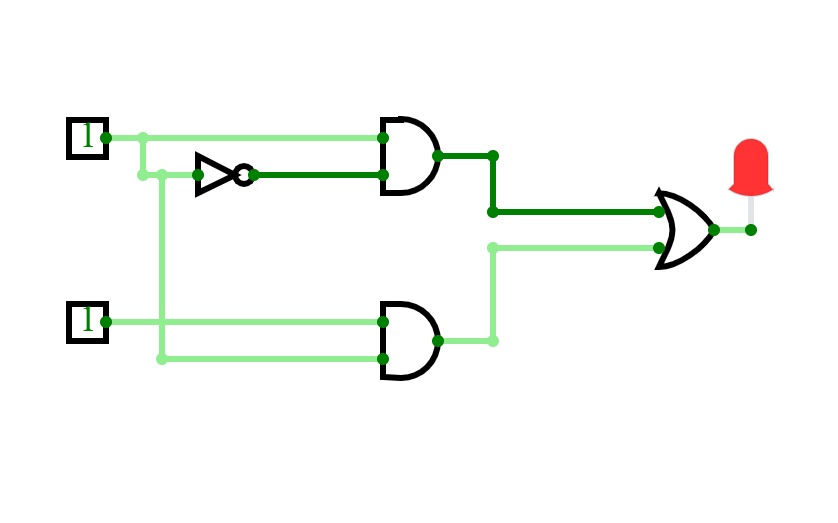

Half adder using XOR and NAND

Half adder using XOR and NAND

Full Subtractor using XOR and NAND

Full Subtractor using XOR and NAND

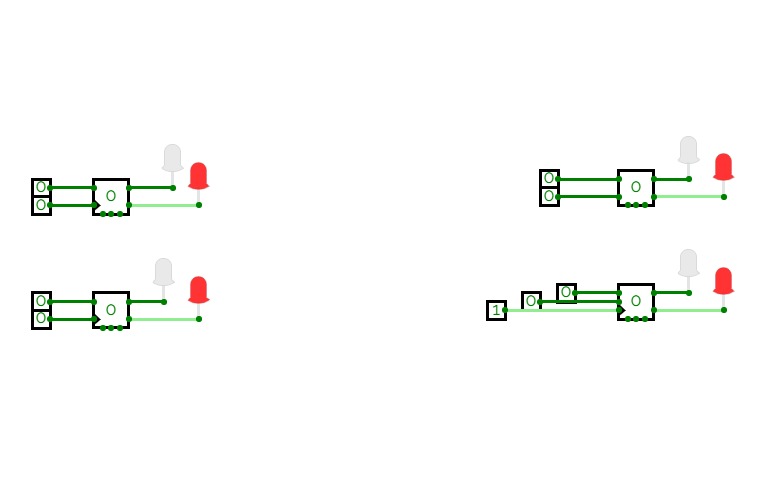

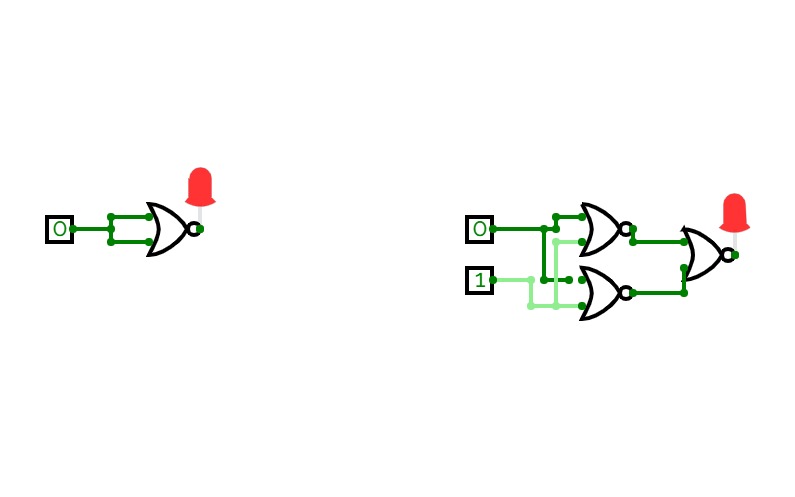

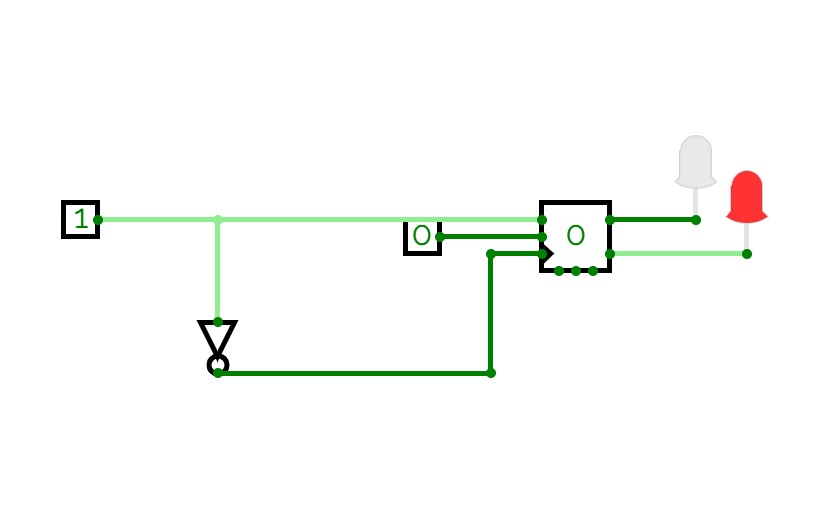

Transformation of nor gate into NOT and OR gate

Transformation of nor gate into NOT and OR gate

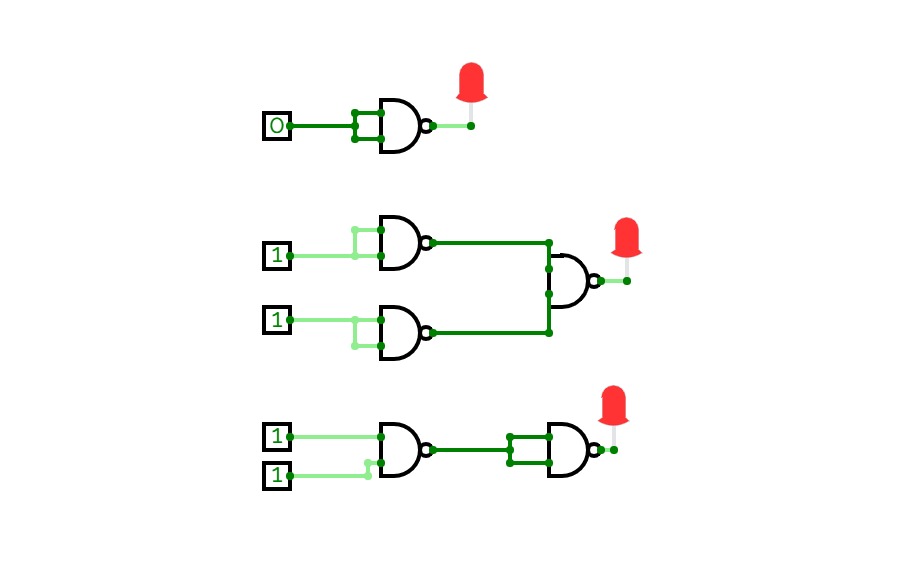

Transformation of NAND gate into NOT,OR and AND gates

Transformation of NAND gate into NOT,OR and AND gates

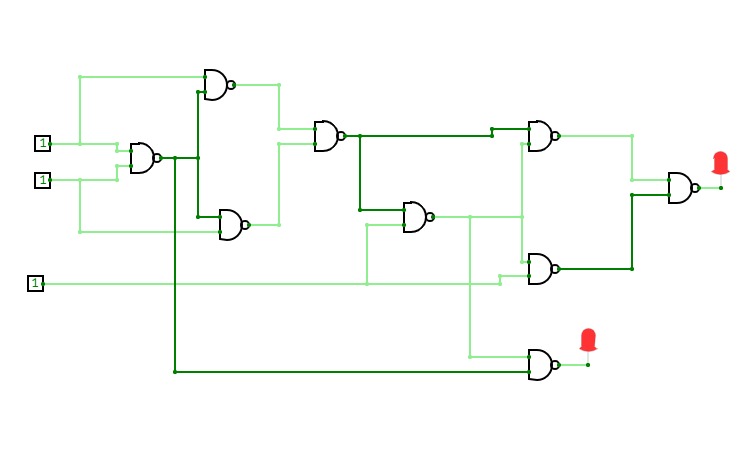

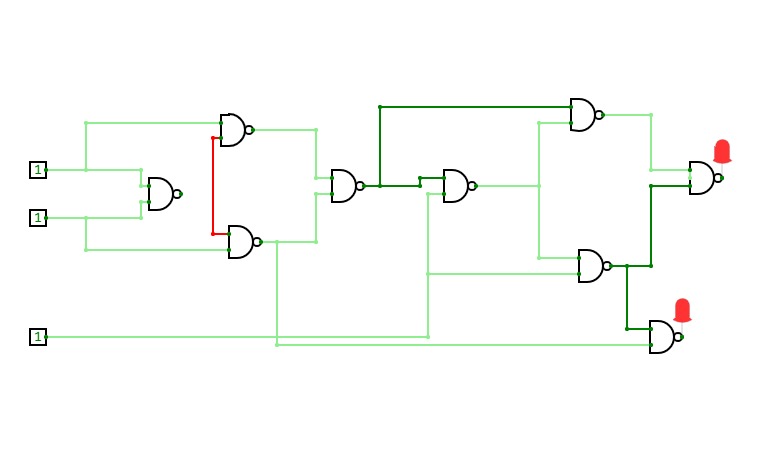

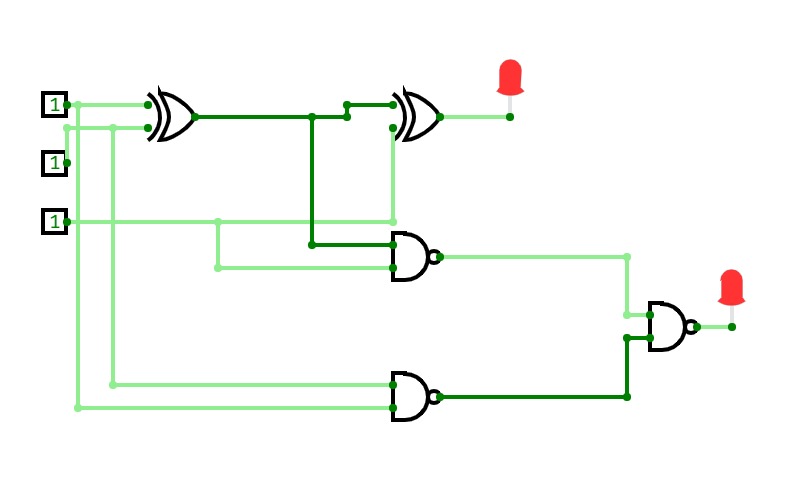

3 bit Full adder using NAND gate

3 bit Full adder using NAND gate

EXP8

EXP8

2 to 1 DEMUX

2 to 1 DEMUX

3 bit Full subtractor using NAND gate

3 bit Full subtractor using NAND gate

3 bit half adder uising NAND gate

3 bit half adder uising NAND gate

Design of Logic Diagram using NAND gate-exp 5

Design of Logic Diagram using NAND gate-exp 5

4 to 2 Priority encoder

4 to 2 Priority encoder

D to JK flip flop conversion

D to JK flip flop conversion

2:1 MUX using universal gate

2:1 MUX using universal gate

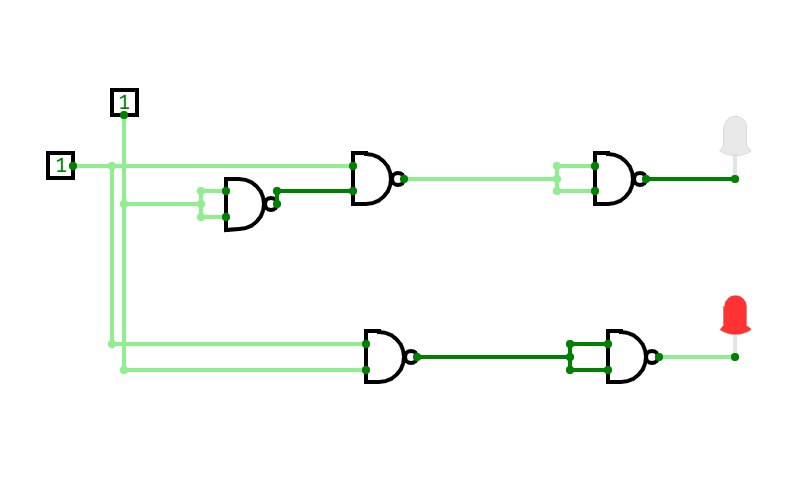

1 to 2 DEMUX

1 to 2 DEMUX

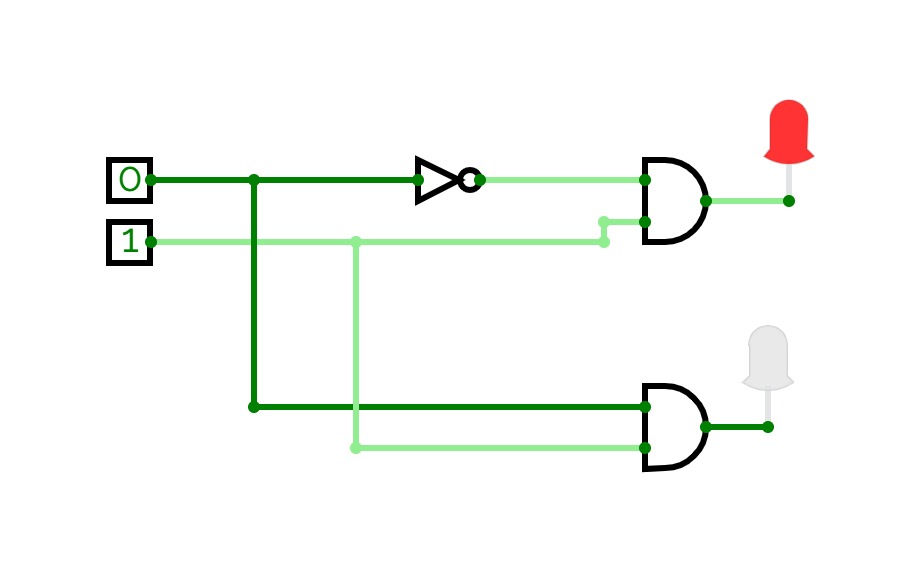

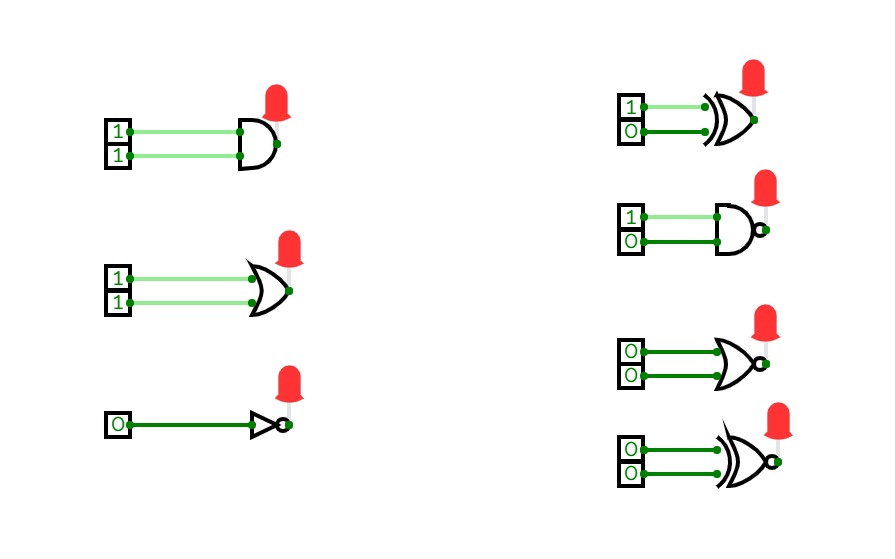

Basic logic gates

Basic logic gates

Transformation of nor gate into AND gate

Transformation of nor gate into AND gate

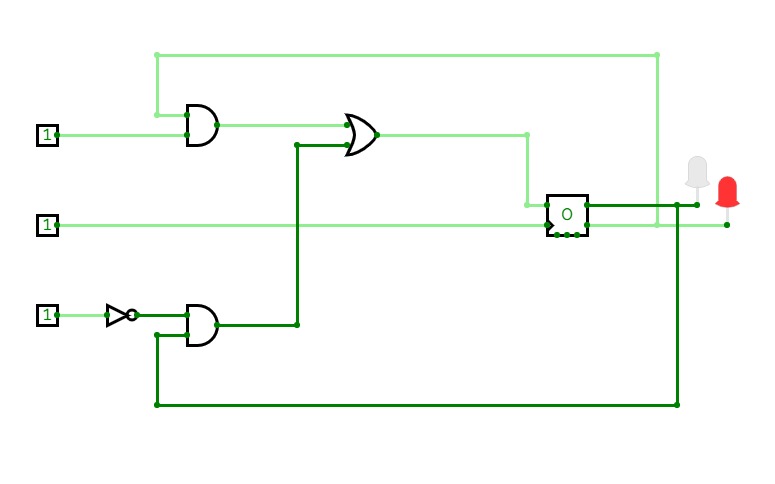

JK to D flip flop conversion

JK to D flip flop conversion

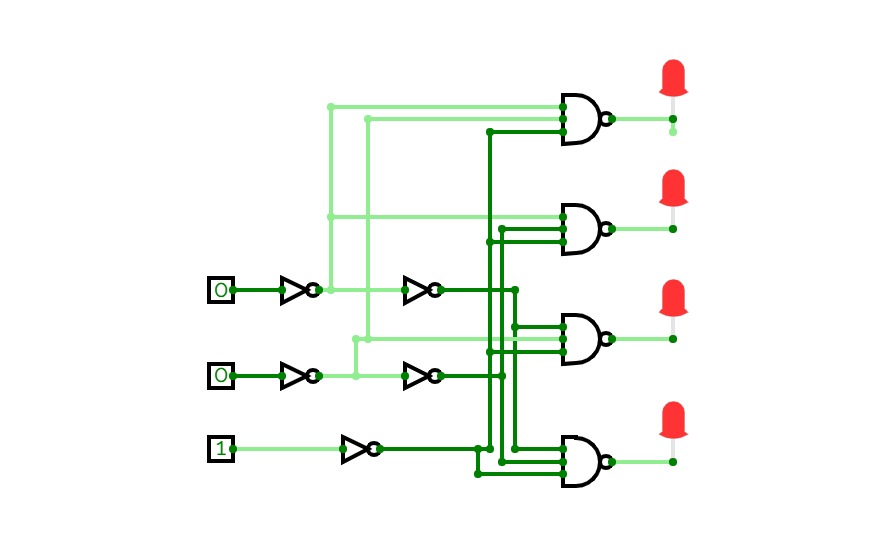

4 to 1 DEMUX

4 to 1 DEMUX

4 to 2 Priority encoder

4 to 2 Priority encoder

Realization of 2:1 MUX using Basic and XOR gate

Realization of 2:1 MUX using Basic and XOR gate

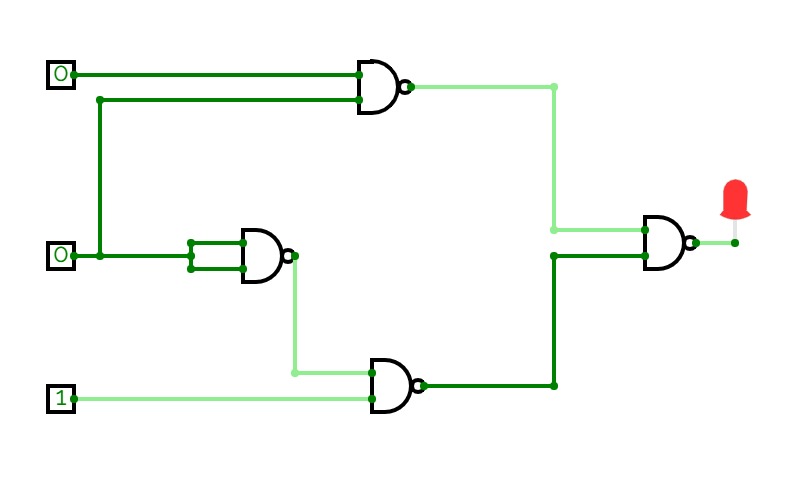

Half subtractor using XOR and NAND

Half subtractor using XOR and NAND

Full adder using XOR and NAND

Full adder using XOR and NAND

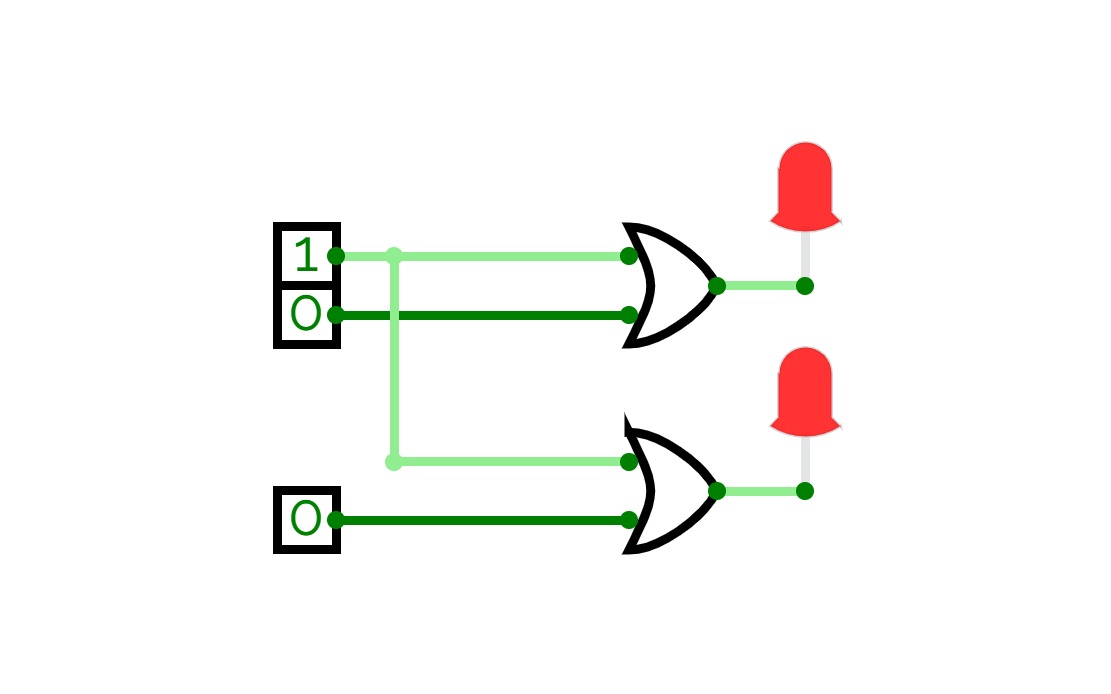

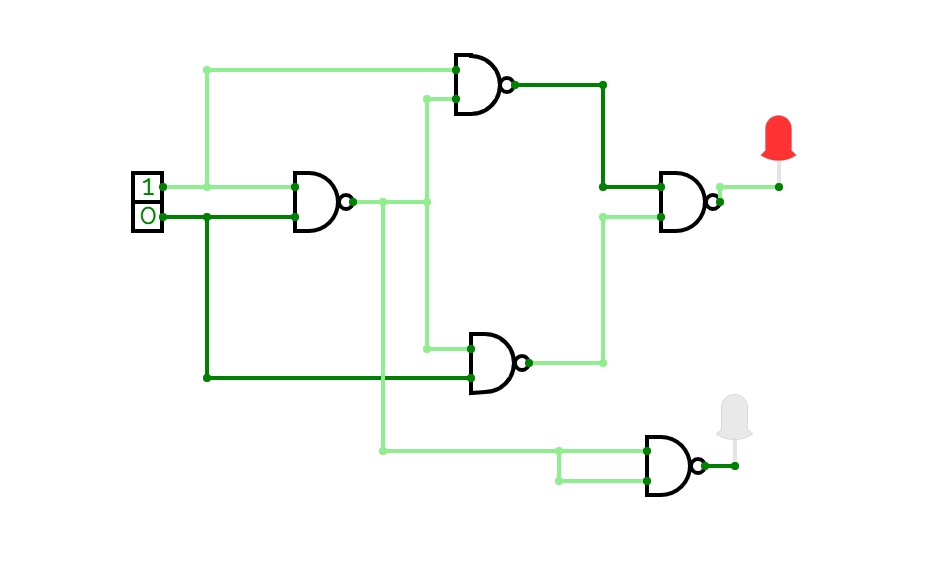

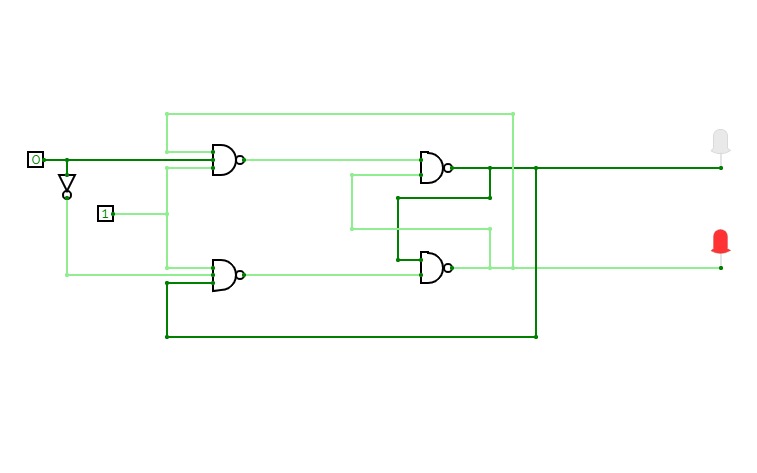

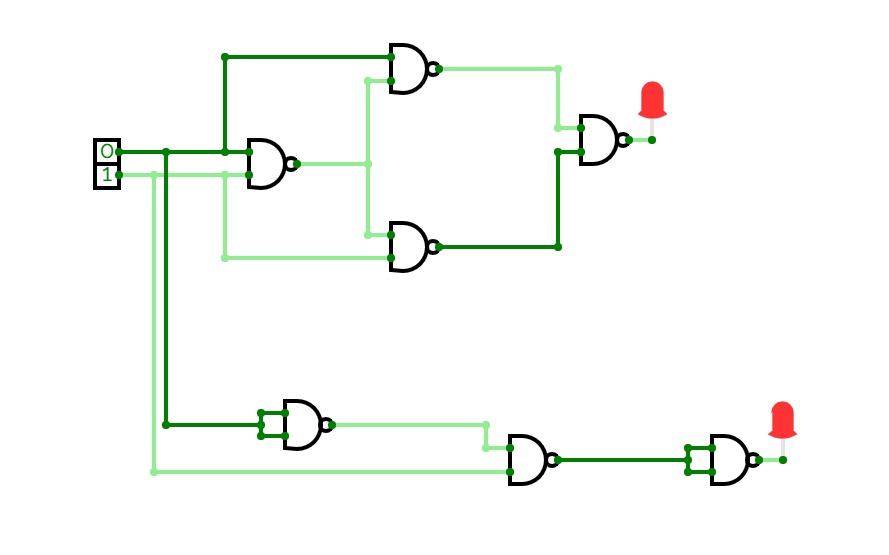

2 to 1 multiplexer

2 to 1 multiplexer

JK to D flip flop implementation using NAND gate

JK to D flip flop implementation using NAND gate

JK flip flop implementation using NAND gate

JK flip flop implementation using NAND gate

4:1 MUX using universal gates

4:1 MUX using universal gates

3 bit half subtractor using NAND gate

3 bit half subtractor using NAND gate

Design of logic diagram using basic gates on online simulator-exp 5

Design of logic diagram using basic gates on online simulator-exp 5

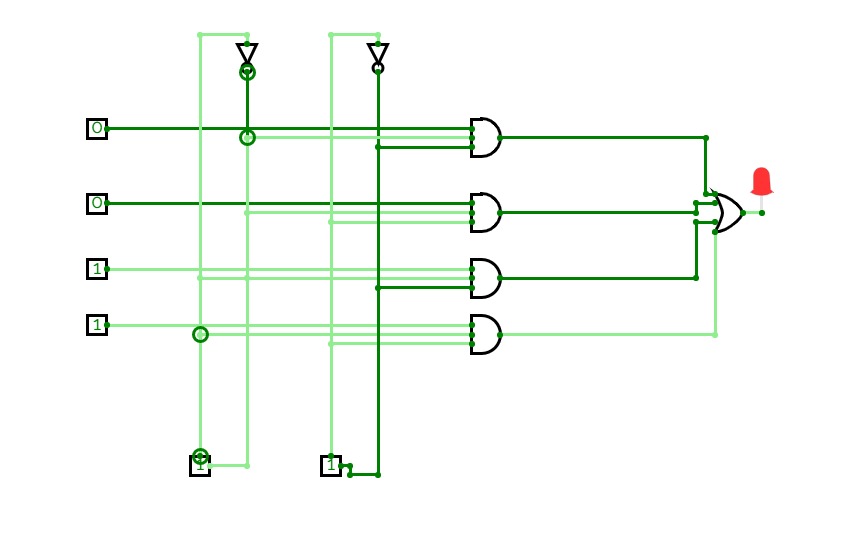

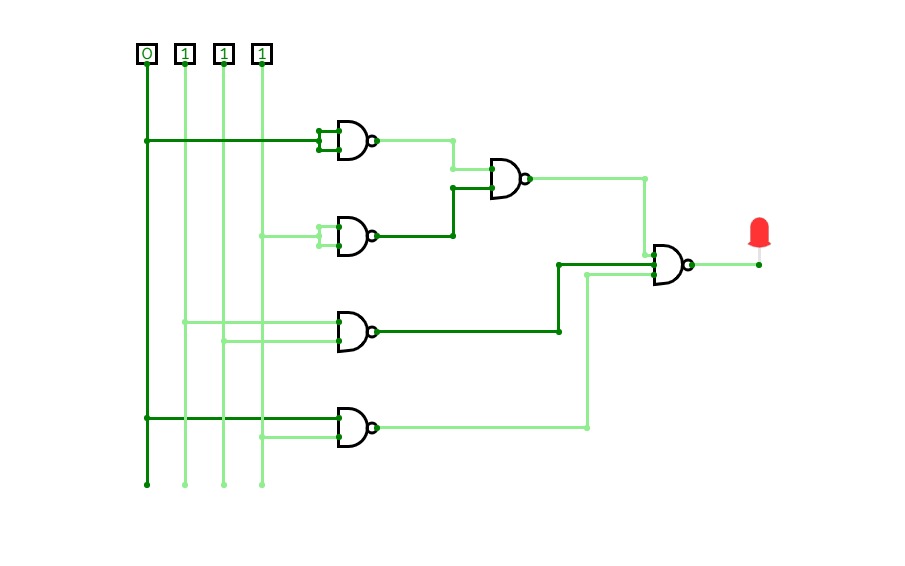

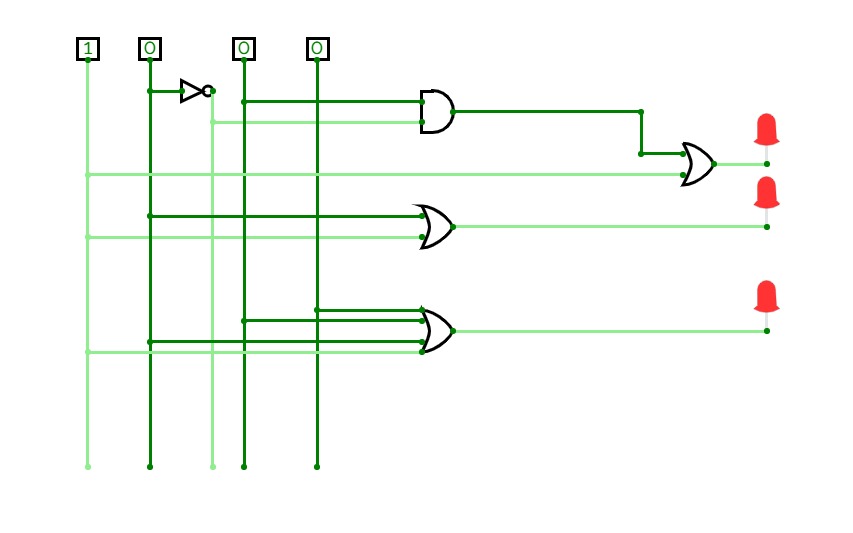

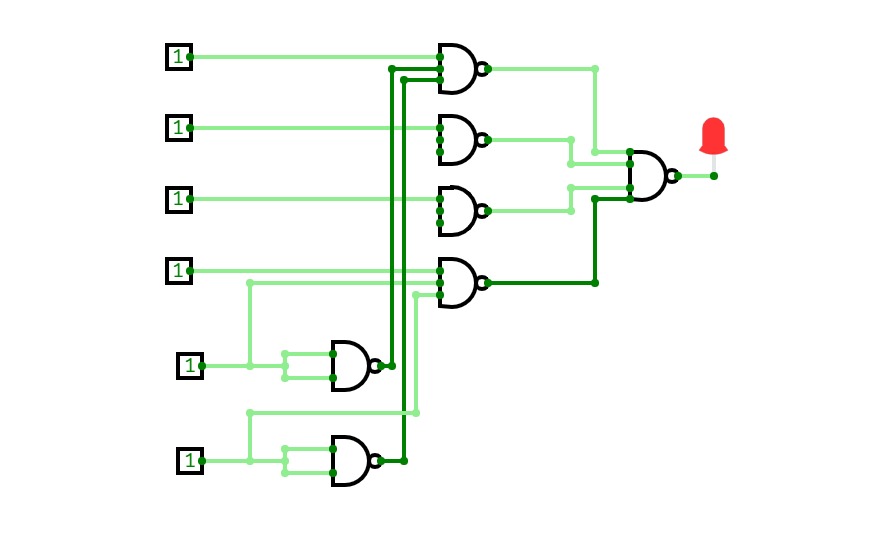

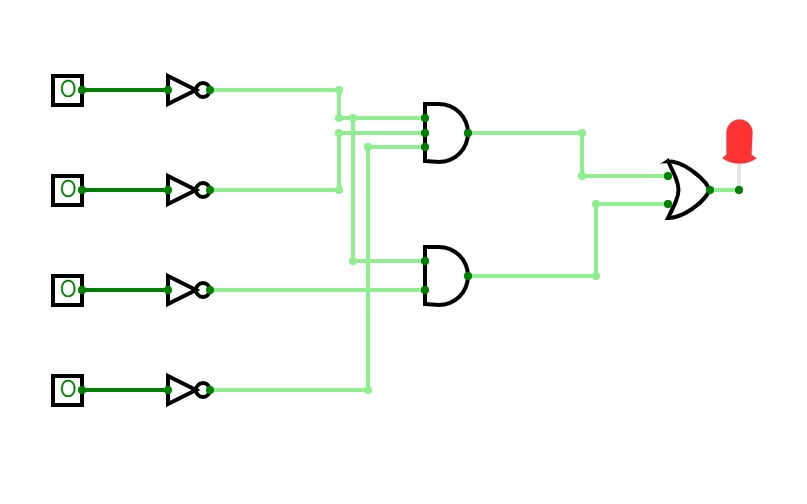

4 to 1 MUX

4 to 1 MUX