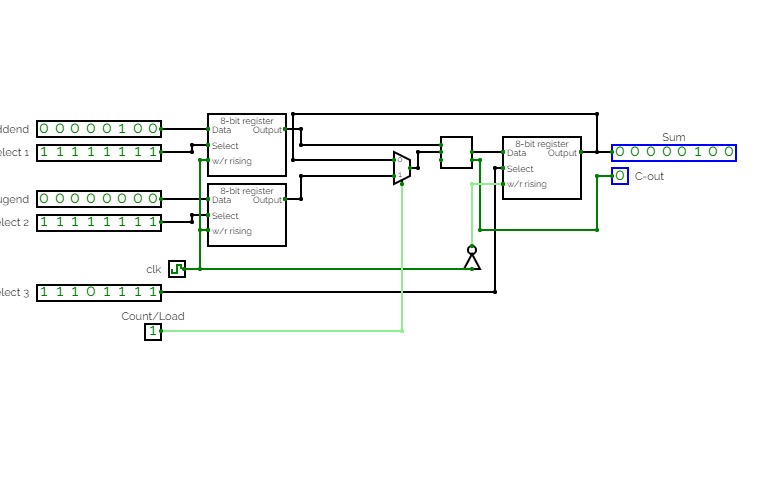

Adjustable 8-bit adder which either loads values from two different registers into an 8-bit adder or sequentially adds the current output value of the adder to the value stored in the first register. Practice for RAM unit application, register creation and organization, bit splitting and compression, and sequential logic.

Project3

Project3An attempt at utilizing memory storage to create some output based on information inputted into ROM block; output changes when ROM enable is toggled while the address input counter changes to change up the sequence of input bits to the registers.

Project2

Project2Practice for utilizing ROM to produce an output based on some sequential input.

WorkingWithRAM

WorkingWithRAMReturning to creations involving the use of RAM units to build larger registers for use with counters and ROM to provide a randomized output