SequentialCircuits_Tutorials

SequentialCircuits_TutorialsDigital Logic Design, Sequential. Combinational Logic, ALU, CPU, Finite State Machine, FSM, State Diagram, State Table, Flip Flops, Registers, Counters

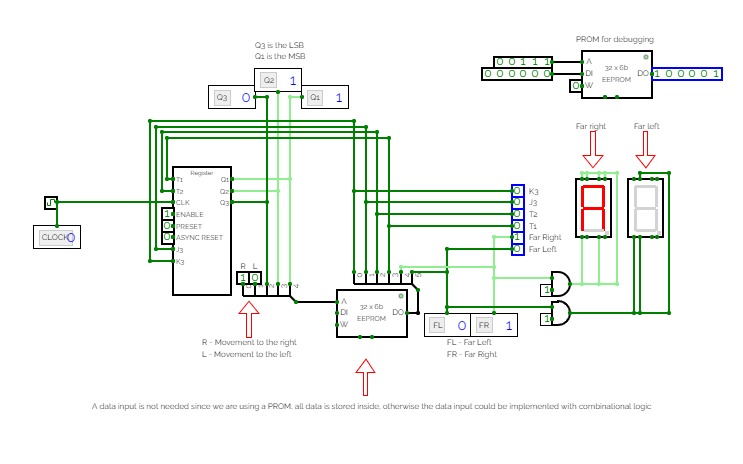

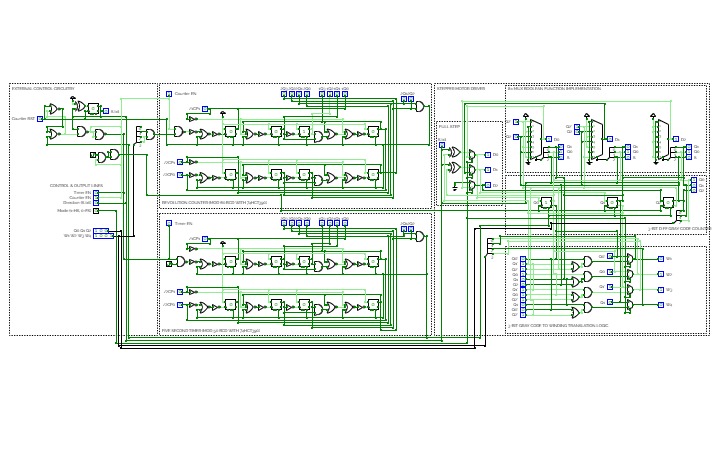

FSM Controller for lateral position of wheelchair

FSM Controller for lateral position of wheelchairThis was the final project for the college course Logic Design. The idea for the project was taken from CSE/EEE 120 Capstone Design Project Spring 2021, ASU, Tempe, Arizona, Prof. of Practice, Steven Millman (NXP).

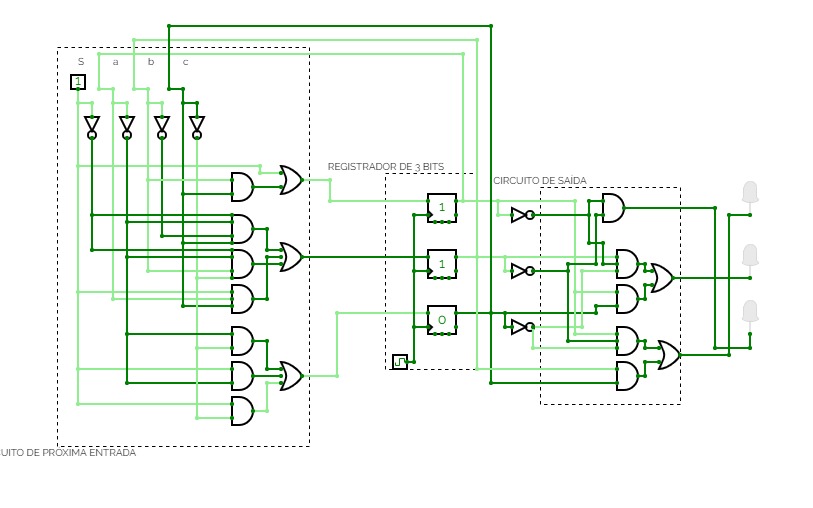

sEMaforo_projeto

sEMaforo_projetoCounter-Clockwise Seven Segment Display

Counter-Clockwise Seven Segment DisplayThe circuit implemented in this project shows light moving in a counter-clockwise direction on a Seven Segment Display (SSD). The given order of states is as follows: a->fa->f->ef->e->de->d->cd->c->bc->b->ab->a.

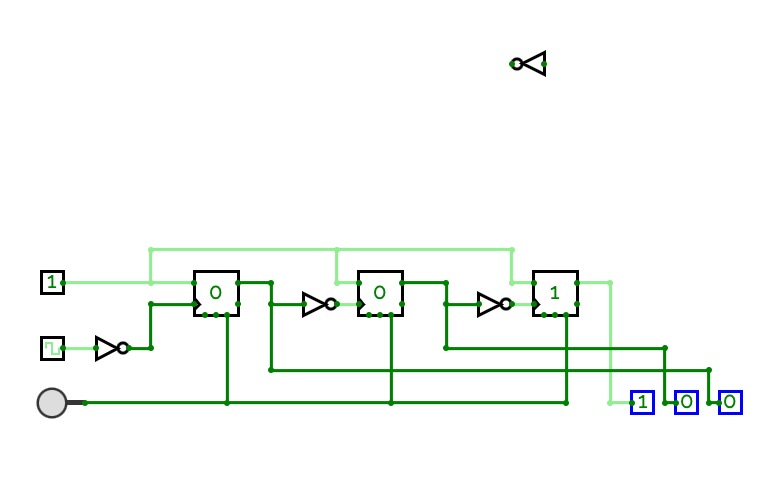

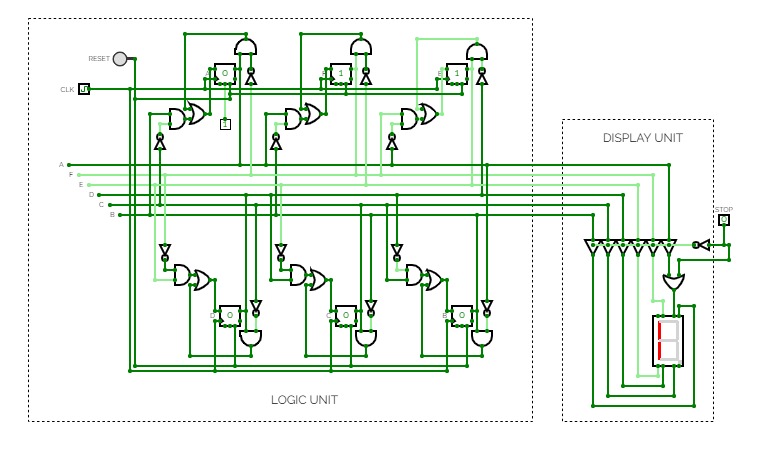

Stepper Motor Driver

Stepper Motor DriverDesign of a half step and full step stepper motor driver using D flip-flops and multiplexers.