JK Flip Flop

JK Flip FlopExperiment No. 9 b: Implementation of flip flops: JK.

Done by:

Saranga K. Mahanta

Sch Id:18-14-038

T Flip Flop

T Flip FlopExperiment No 9 d: Implementation of flip flops: SR, JK, D and T

Done by:

Saranga K. Mahanta

Sch Id: 18-14-038

D Flip Flop

D Flip FlopExperiment No. 9 c: Implementation of flip flops: D flip flop.

Done by:

Saranga K. Mahanta

Scholar Id: 18-14-038

Decade Counter

Decade CounterExperiment No 10: Implement a decade counter using basic gates.

Done by:

Saranga K. Mahanta

Scholar Id: 18-14-038

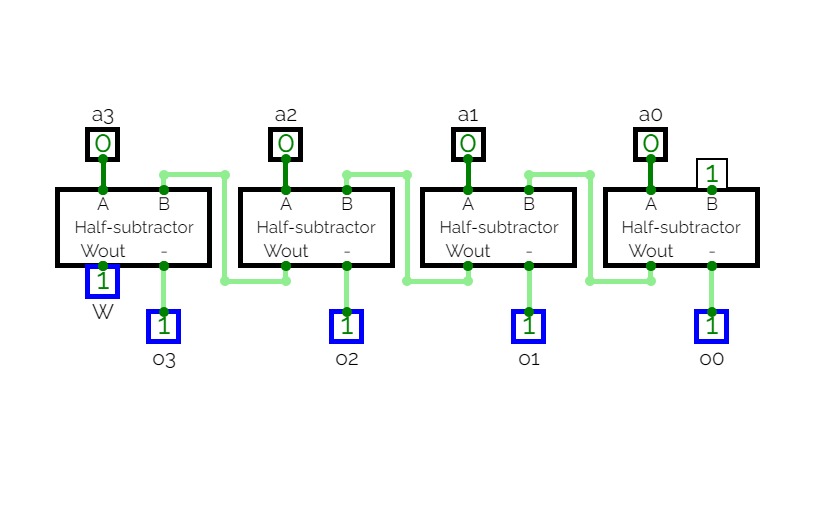

D FF using MUX

D FF using MUXExperiment No 11 c: D flip flop using 2x1 MUXs.

Done by:

Saranga K. Mahanta

Schl Id: 18-14-038

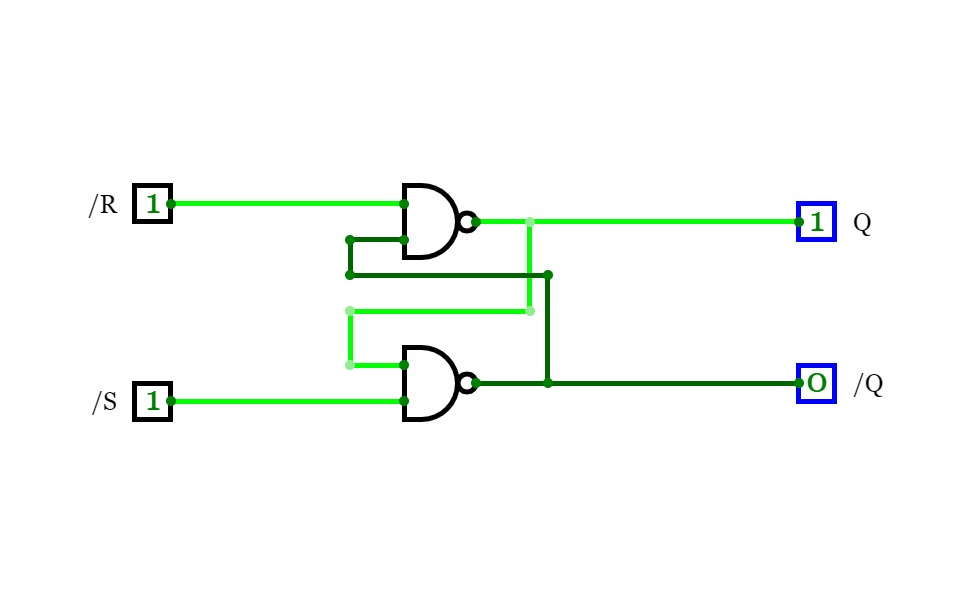

[Sequential] RS Latch

[Sequential] RS LatchThe RS Latch is the first sequential circuit we learned. It 'remembers' which input (/R or /S) was last set to ZERO by outputting on either Q or /Q.

/R = 0 and /S = 0 is an illegal state!

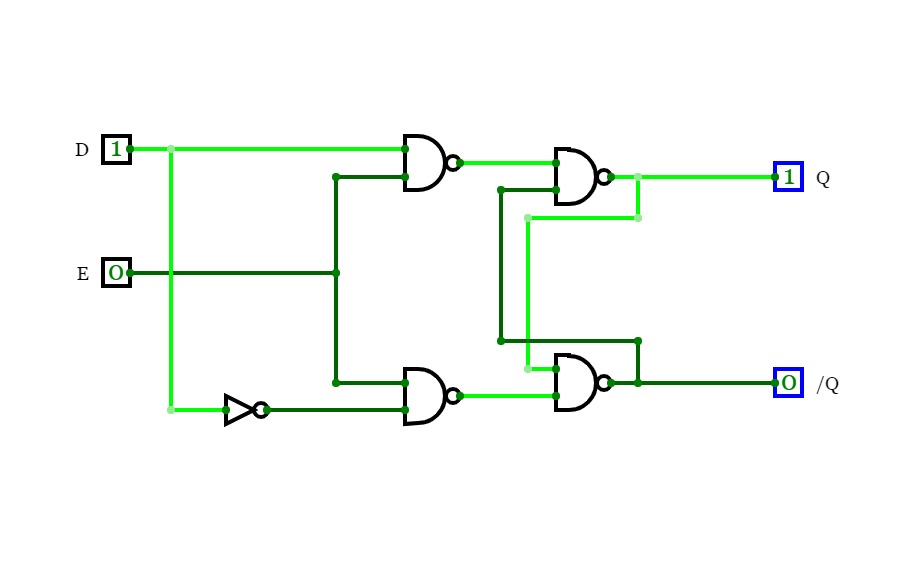

[Sequential] D Latch (Transparent Latch)

[Sequential] D Latch (Transparent Latch)Similar to a gated RS Latch, but Q is set to D when E is 1

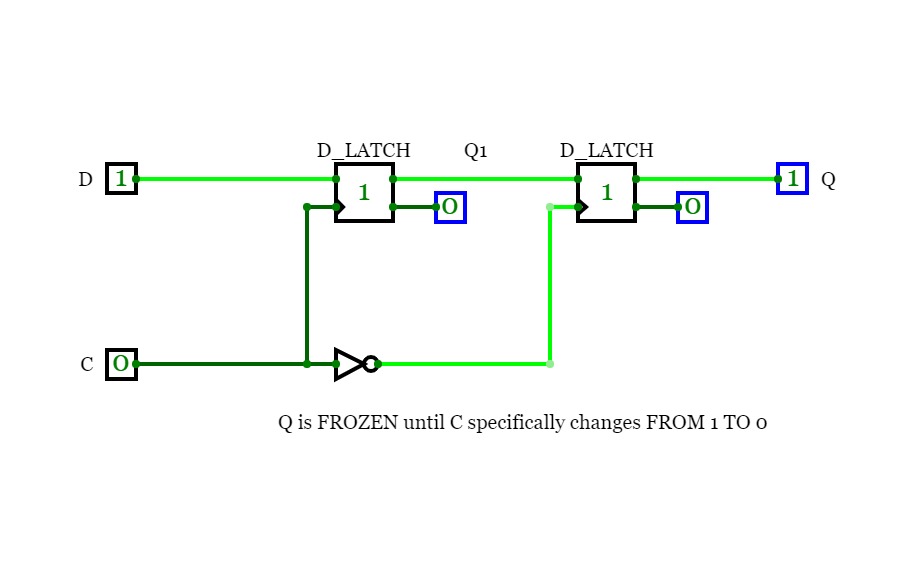

[Sequential] D Flip Flop (Edge Triggered)

[Sequential] D Flip Flop (Edge Triggered)The output Q can only change at the point in time when C (clock) transitions from high to low (1 -> 0)

We say "Q changes on the falling / trailing edge of C"

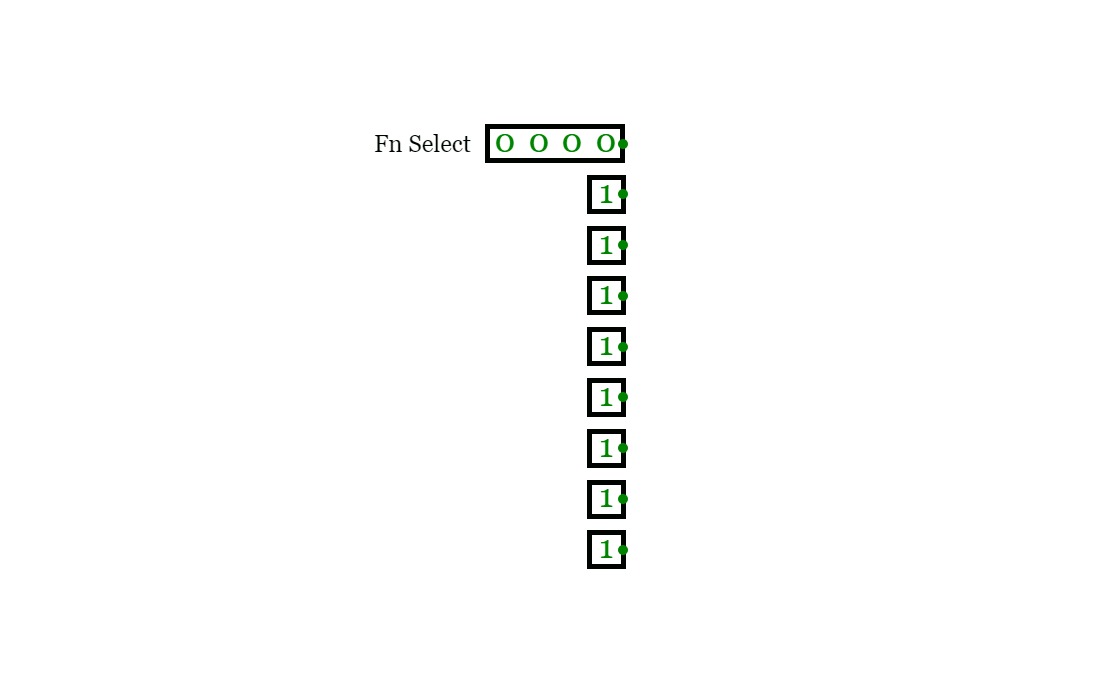

My Processor Design

My Processor DesignA basic ALU design for my personal projects.

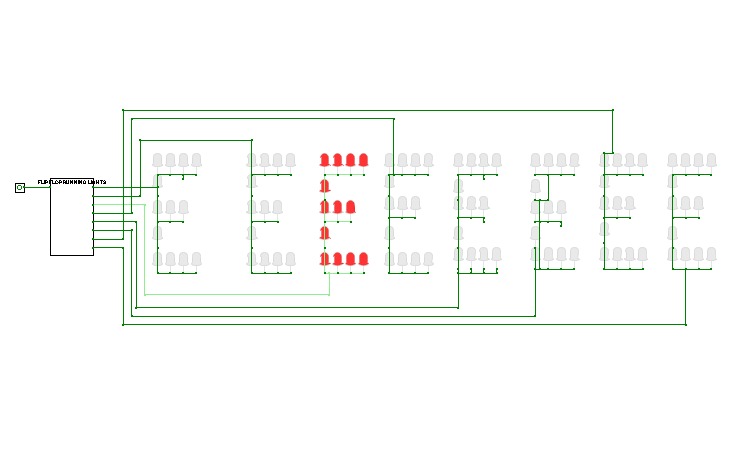

RUnning lights

RUnning lightsRunning lights, Sequential

Tests

Testsbasic D latch

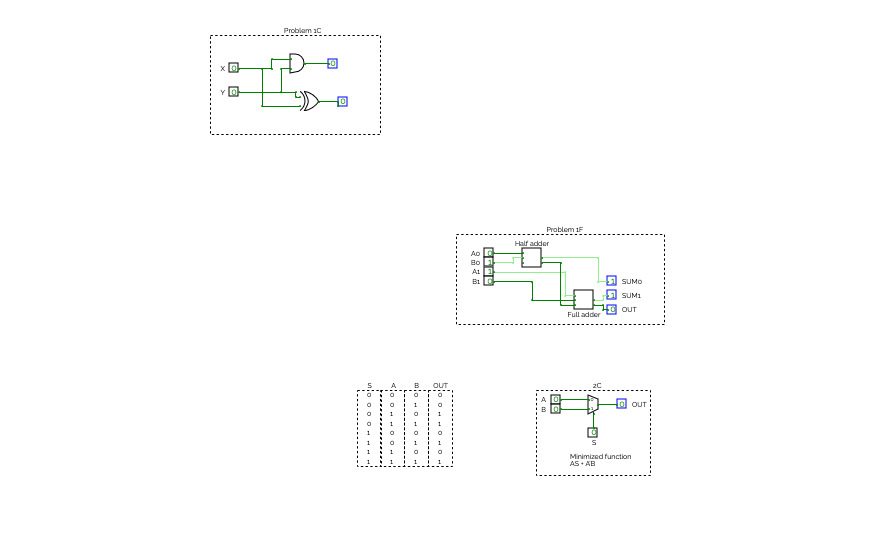

Lab 05

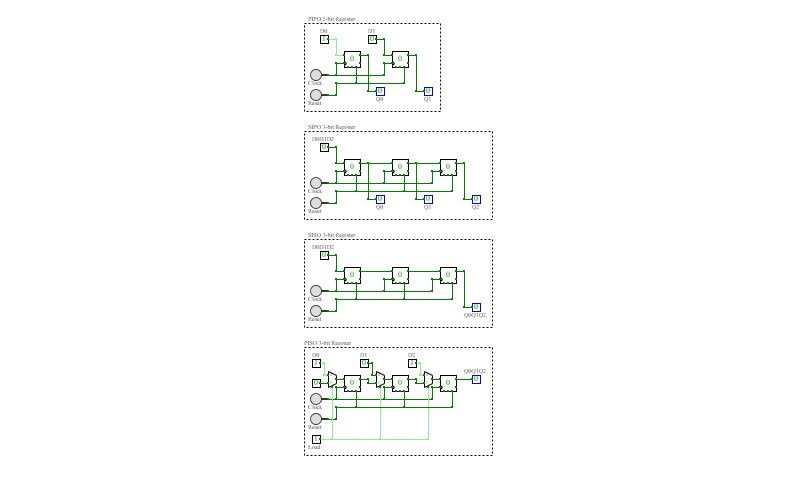

Lab 05Shift Register

Shift RegisterThese contain the D flip-flop Shift Register with all mode of Serial and Parallel Input/Output. It also contain the synchronous and acsynchronous clock.