Enunciado del Problema:

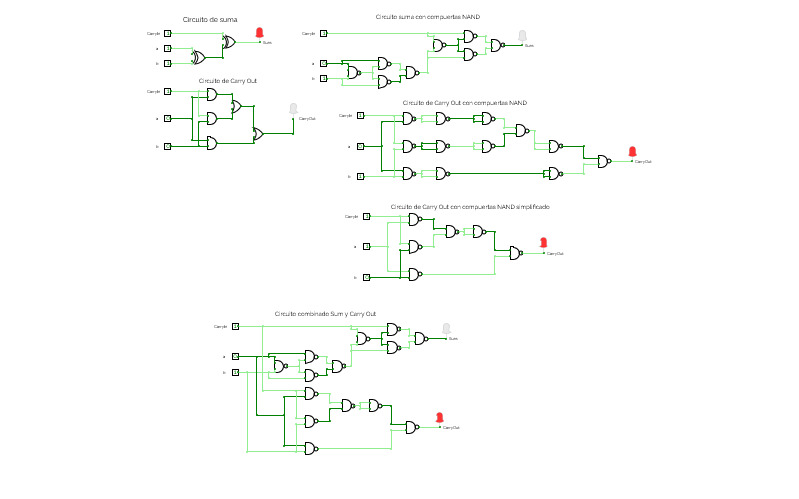

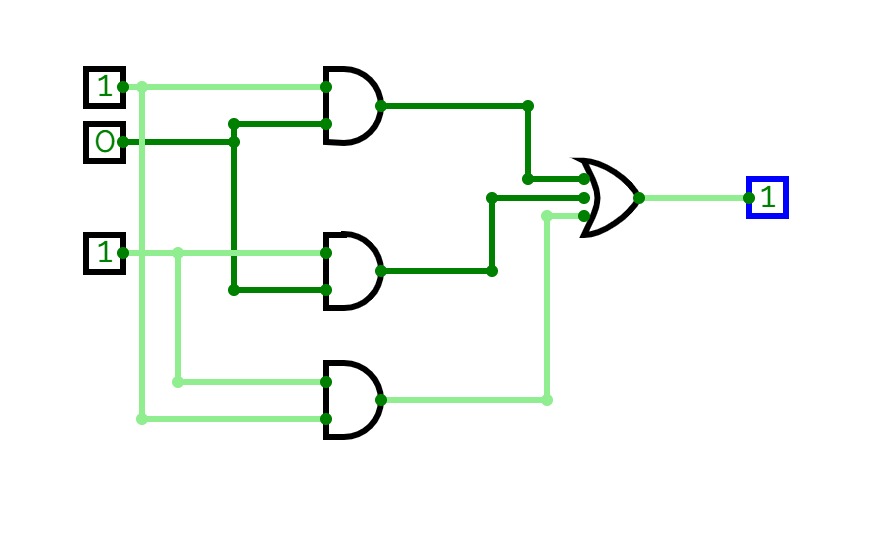

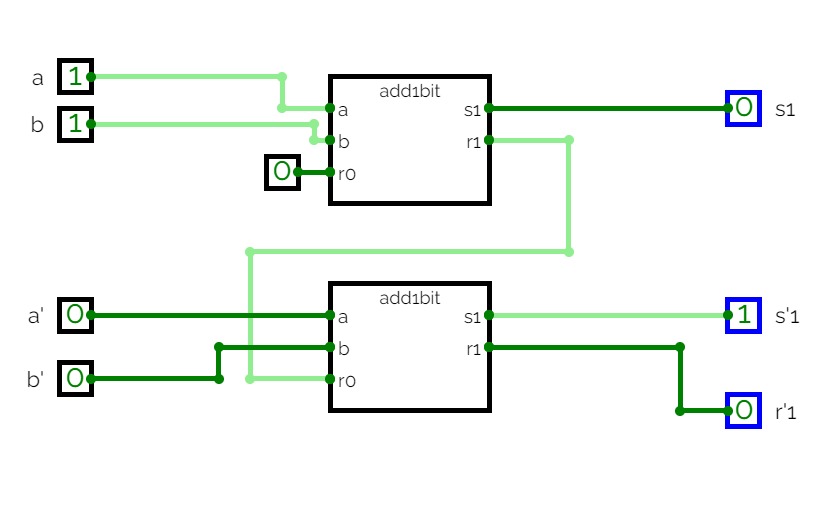

Realizar el diseño de un Sumador Total (Full Adder) de un bit. En el proceso de diseño, se debe considerar tres entradas ( a, b, CarryIn) y dos salidas(Sum, CarryOut).

Para obtener el circuito equivalente con compuertas lógicas utilizar mapas de Karnaugh.

Se podría utilizar el método analizado en clase mediante tablas de

verdad y ecuaciones del álgebra de Boole para contrastar los resultados obtenidos con los mapas de Karnaugh.

Adicionalmente, obtener el equivalente del sumador total con compuertas NAND y verificar el funcionamiento del sumador total en el emulador circuitverse.org.

Nota: En el proceso de diseño, considerar que se podrían utilizar compuertas exclusivas (XOR).

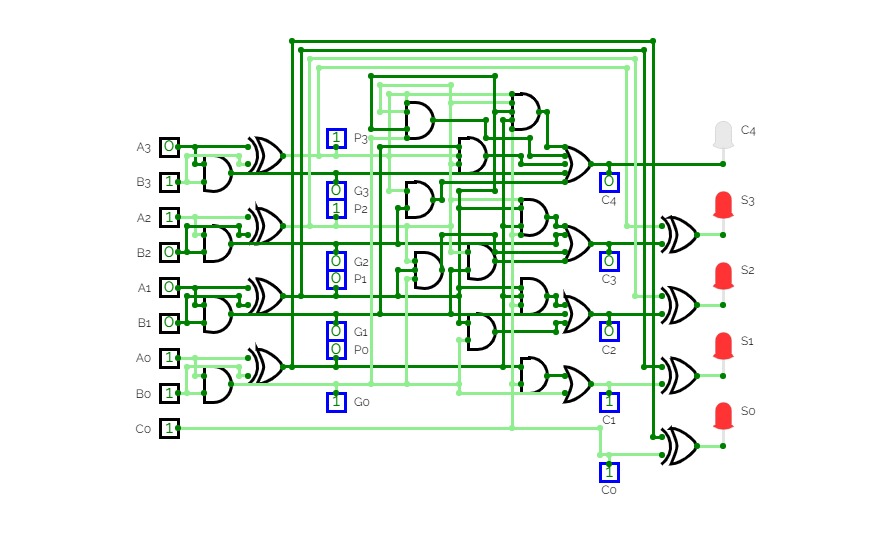

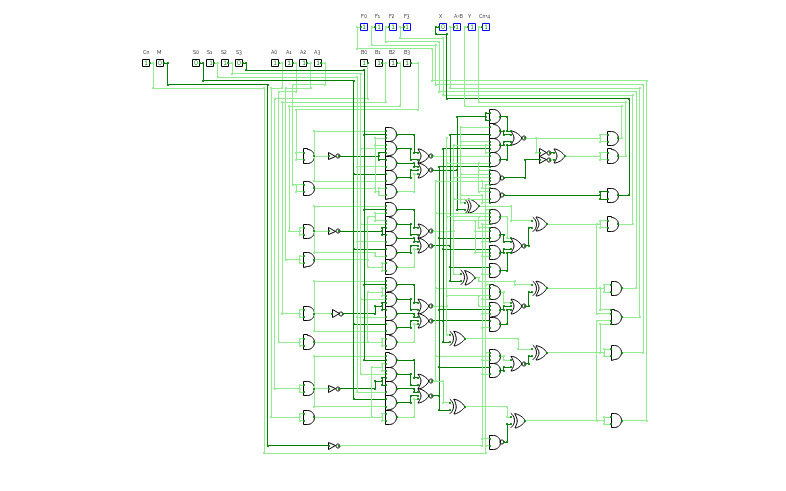

Texas Instruments 74181

Texas Instruments 74181This is a recreation of the eponymous TI circuit for examining it's function. This circuit is an exact copy of the TI chip but with some IO circuitry for visualization. This schematic was created with the intention of using it to debug an emulated version created in a physics sandbox game, Phyzios Studio Pro.