Enunciado del Problema:

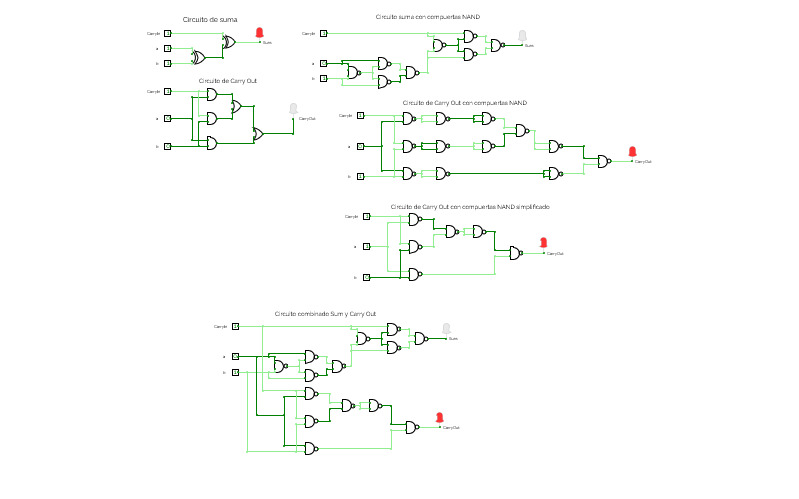

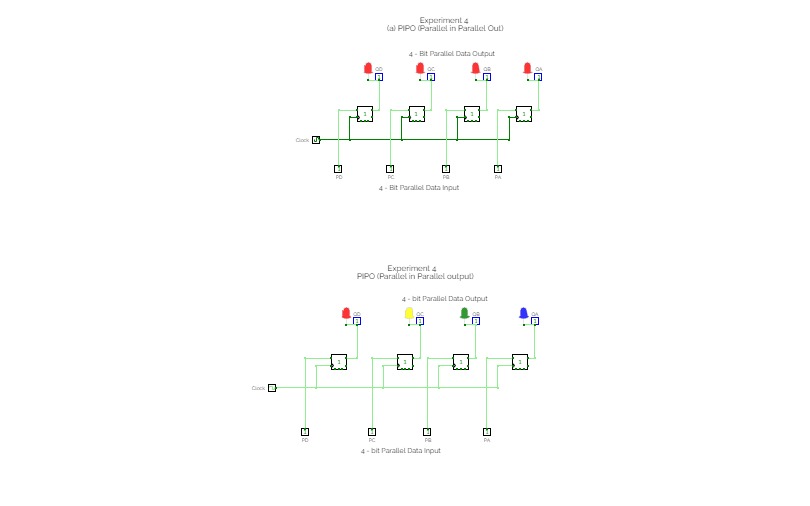

Realizar el diseño de un Sumador Total (Full Adder) de un bit. En el proceso de diseño, se debe considerar tres entradas ( a, b, CarryIn) y dos salidas(Sum, CarryOut).

Para obtener el circuito equivalente con compuertas lógicas utilizar mapas de Karnaugh.

Se podría utilizar el método analizado en clase mediante tablas de

verdad y ecuaciones del álgebra de Boole para contrastar los resultados obtenidos con los mapas de Karnaugh.

Adicionalmente, obtener el equivalente del sumador total con compuertas NAND y verificar el funcionamiento del sumador total en el emulador circuitverse.org.

Nota: En el proceso de diseño, considerar que se podrían utilizar compuertas exclusivas (XOR).