Trit-Buttons

Trit-ButtonsThis CircuitVerse project introduces a Trit-Button designed to test ternary memory in digital logic simulations. The button allows the representation of three logical states (0, 1, and 2) using 2 output bits, providing a practical solution for simulating ternary logic in a traditionally binary environment.

We’ve created three versions of the Trit-Button:

-

Version 1 Balance (Encoding 10, 00, 01):

-

10 = -1, 00 = 0, 01 = 1

-

10 = -1, 00 = 0, 01 = 1

-

Version 2 Unbalance (Encoding 00, 01, 10):

-

00 = 0, 01 = 1, 10 = 2

3. Version 3 Unbalance (Encoding 00, 01, 11): - 00 = 0, 01 = 1, 11 = 2

-

00 = 0, 01 = 1, 10 = 2

All versions are designed to interface with ternary memory and the ALU (Arithmetic Logic Unit) for testing ternary operations in CircuitVerse, which currently only supports binary logic.

This Trit-Button is a critical step in implementing and testing ternary computing concepts within standard simulation tools.

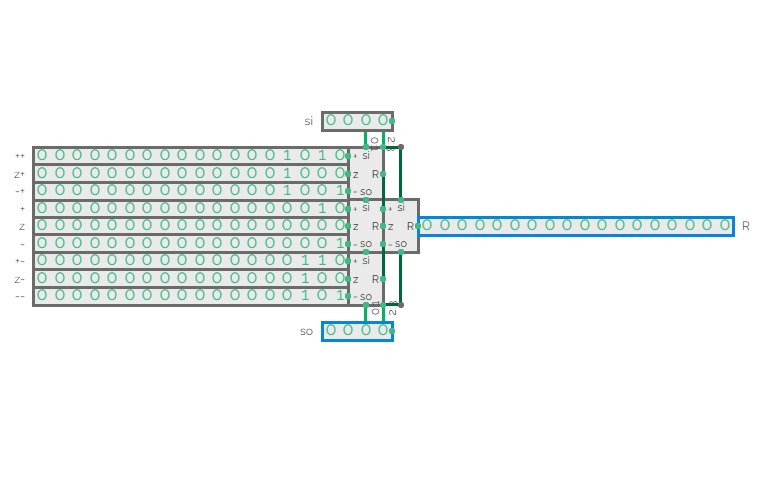

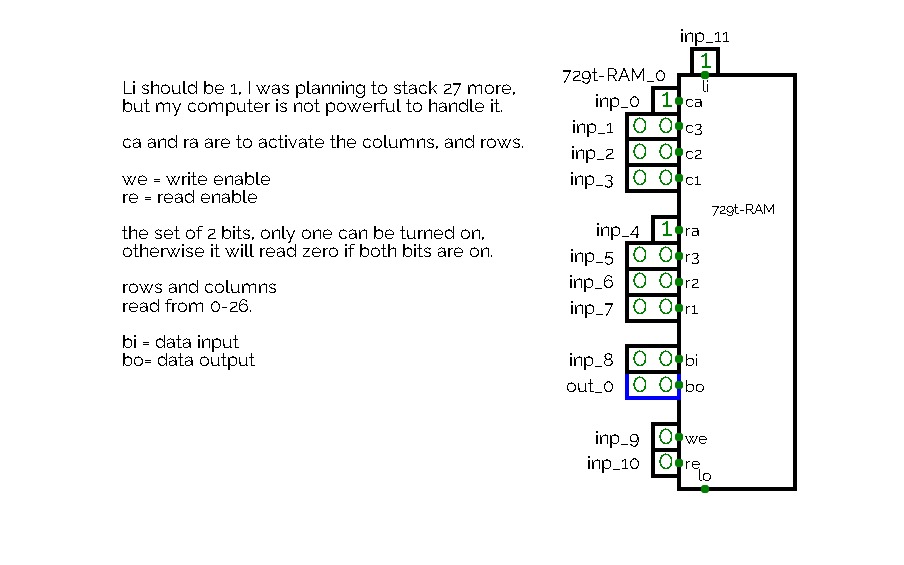

This project showcases a Trit RAM designed for ternary logic simulation within CircuitVerse. The RAM features 729 addresses, arranged in 27 columns and 27 rows, all controlled by 3 trits for both row and column selection. This design represents an efficient approach to ternary memory, pushing the limits of CircuitVerse's simulation capabilities.

While the original goal was to create a RAM with 19,683 addresses, the complexity caused significant performance issues in the simulator, prompting a scaled-down version that operates smoothly on standard hardware.

Key Details:

- Memory Size: 729 addresses (3^6).

- Addressing Scheme: 3 trits each for row and column selection, enabling precise access to memory cells.

- Splitters as Wires: Due to CircuitVerse’s limitations, splitters are treated as single wires to maintain simulation efficiency.

- Performance Optimization: Designed to balance functionality and simulator stability, making it ideal for testing ternary logic concepts like ALUs and memory structures.

This project is an essential building block for advancing ternary computing within a binary-focused simulation tool, paving the way for innovative designs.