t729 CPU - old

t729 CPU - oldt729 is a 6/12-trit balanced ternary processor.

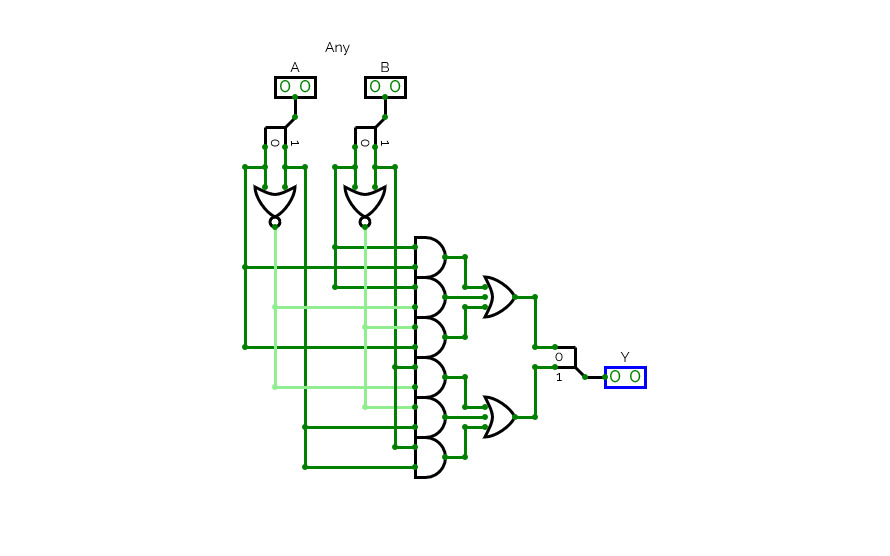

It is built with normal binary logic gates using binary encoded ternary (10, 00, 01) to create the ternary logic gates. While this probably increases complexity, I've not found a logic simulator that does ternary. I tried circuit simulators but working with negative and positive voltages with transistors is kind of a pain and very slow to design. Sure binary encoded ternary is more wire complex but it does only require one voltage and should technically use less power and run faster. Also binary logic gates are super cheap. Using binary logic gates also means the design should work on FPGAs and could in theory get manufactured as a microprocessor.

I've gone with 6-trit = 1 Tryte for my system. 12-trit / 2 Tryte is a "word".

Data and instruction width is 6-trit (729)

Address width is 12-trit (531,441)

The t729 is a hobby project I've been extremely slowly working on for a few years.

It's purely a project for fun. Completely self taught so probably a lot of doing things the wrong way.

Currently I'm mostly hung up on instruction set. It's hard choosing which instructions to have and how to implement them.

Huge thanks to http://homepage.divms.uiowa.edu/~jones/ternary/ for the ternary logic knowledge.

If you would like to add something to the project or point something out please comment or e-mail (gmail*dyne.unlimited)

t729 - Balanced Ternary CPU

t729 - Balanced Ternary CPUt729 is a 6/12-trit balanced ternary processor.

It is built with normal binary logic gates using binary encoded ternary (10, 00, 01) to create the ternary logic gates. While this probably increases complexity, I've not found a logic simulator that does ternary.

I've gone with 6-trit = 1 Tryte for my system. 12-trit / 2 Tryte is a "word".

Data and instruction width is 6-trit (729)

Address width is 12-trit (531,441)

The t729 is a hobby project I've been extremely slowly working on for a few years.

It's purely a project for fun. Completely self taught so probably a lot of doing things the wrong way.

Currently I'm mostly hung up on instruction set. It's hard choosing which instructions to have and how to implement them.

Huge thanks to http://homepage.divms.uiowa.edu/~jones/ternary/ for the ternary logic knowledge.

If you would like to add something to the project or point something out please comment or e-mail (gmail*dyne.unlimited)