A 20bit processor

Done:

In progress:

-Alu

Yet to be done:

-Ram

-Ram address decode logic (Internal, External)

-Interrupts

-Registers

-Resets

-Instruction decode logic

-Transfer hub

-Other stuff

.

.

.

Instruction information:

.

Memory layout:

00000-9ffff: App rom

a0000-ff86e: GP ram

ff86f-ff999: Video ram

ffa00-ffeff: The stack

Notes:

Uses empty stack convention

Uses ascending stack convention

Parameters should be pushed onto the stack before calling the function

Status register goes as following (MSB first): OW, Z, N, E, IntterruptProgress (4bit), ResetProgress (4bit), InterruptAvailable, ResetAvailable, 0b000000

Every mention of "address" refers to the 6-nibble value with address configuration concatenated before the actual memory reference/data

ra1/ra2/ra3 refers to a register or address. The number is to distinguish between different arguments for instructions.

Registers:

Stack Pointer

Instruction

Address

SUM

Status

Instruction step

A

B

Register ids:

Stack Pointer: 0

Instruction: <INTERNAL>

Address: <INTERNAL>

SUM: 1

Status: 2

Instruction step: <INTERNAL>

A: 3

B: 4

fpA: 8

fpB: 9

fpC: a

fpD: b

fpS: c

-Address configuration is concatenated after reg id. Immeadiates and stack pointer indexes are not supported. e.g. 71 is data at B register, 32 is using SUM register as a xxxxx to use $?xxxxx on it.

-fpA through fpD &fpS are floating point registers. Bit functionality is as follows (MSB first): S, EXP (6bit), MAN (13 bit). To calculate the value: (1 + (1-(1/MAN))) * 2^(EXP - 63). -fpA-fpD & fps are incompatible with iadd/isub/idiv/imul/iinc/idec. fpadd/fpfpsub/fpmul/fpdiv/fpinc/fpdec work only on fp registers. They add the actual values, not bits.

-bor/band/bxor do operations on bits, not fpti values, still store binary result in S register.

Register addresses:

Memory page 0: fff00

Memory page 1: fff01

Memory page 2: fff02

Memory page 3: fff03

Address configuration:

-When using on registers, 0x8 as added onto the config

Immeadiate: $#xxxxx (0xxxxx) (Uses data xxxxx)

Address: $@xxxxx (1xxxxx) (Uses data at address xxxxx)

Pointer: $?xxxxx (2xxxxx) (Uses data at address xxxxx and uses $@***** on it)

Stack pointer index: $-xxxxx(%sp) (3xxxxx) (Subtracts xxxxx from stack pointer and uses $?***** on it)

.

.INSTRUCTIONS:

.

mov ra1, ra2:

Stores ra1 into ra2 address (000(ra1)(ra2))

fpti ra1, ra2:

Transfers data at ra1 to ra2 (not bits, value. kinda like "(int) float" in c) (ra1 is encoded in floating point. requires ra1 to be using a fpr or fp address) (001(ra1)(ra2))

itfp (r, fpR), ($Xxxxxx, fpR):

Transfers data at ra1 to ra2 (not bits, value. kinda like "(float) int" in c) (ra1 is encoded in floating point. requires ra2 to be using a fpr or fp address) (002(ra1)(ra2))

bor (ra1,ra2), (ra1, ra2, ra3):

Ors ra1 and ra2 registers, stores result in S register. Updates OW, Z, and N flags in status register (003(r1ID)(r2ID))

Ors ra1 and ra2 registers, stores result in ra3. Updates OW, Z, and N flags in status register (004(r1ID)(r2ID)(r3))

band (ra1, ra2), (ra1, ra2, ra3):

Ands ra1 and ra2, stores result in S register. Updates OW, Z, and N flags in status register (005(r1ID)(r2ID))

Ands ra1 and ra2, stores result in ra3 register. Updates OW, Z and N flags in status register (006(r1ID)$Xxxxxx)

bxor (,r1,r2), (,r1,$Xxxxxx), ($Xxxxxx,r2), ($Xxxxxx,$Yyyyyy):

Xors ra1 and ra2, stores result in S register. Updates OW, Z, and N flags in status register (007(r1ID)(r2ID))

Xors ra1 and ra2, stores result in ra3 register. Updates OW, Z and N flags in status register (008(r1ID)$Xxxxxx)

iadd (,r1,r2), (,r1,$Xxxxxx), ($Xxxxxx,r2), ($Xxxxxx,$Yyyyyy):

Adds r1 and r2 registers, stores result in S register. Updates OW, Z, and N flags in status register (013(r1ID)(r2ID))

Adds r1 register and $xxxxx address, stores result in S register. Updates OW, Z and N flags in status register (014(r1ID)$Xxxxxx)

Adds $xxxxx address and r2 register, stores result in S register. Updates OW, Z and N flags in status register (015$Xxxxxx(r2ID))

Adds $xxxxx and $yyyyy addresses, stores result in S register. Updates OW, Z and N flags in status register (016$XxxxxxYyyyyy)

isub (,r1,r2), (,r1,$Xxxxxx), ($Xxxxxx,r2), ($Xxxxxx,$Yyyyyy):

Subtracts r2 from r1, stores result in S register. Updates OW, Z and N flags in status register (017(r1ID)(r2ID))

Subtracts $xxxxx from r1, stores result in S register. Updates OW, Z and N flags in status register (018(r1ID)$Xxxxxx)

Subtracts r2 from $xxxxx, stores result in S register. Updates OW, Z and N flags in status register (019$Xxxxxx(r2ID))

Subtracts $yyyyy from $xxxxx, stores result in S register. Updates OW, Z and N flags in status register (01a$XxxxxxYyyyyy)

imul (,r1,r2), (,r1,$Xxxxxx), ($Xxxxxx,r2), ($Xxxxxx,$Yyyyyy):

Multiplyes r1 and r2 registers, stores result in S register. Updates OW, Z and N flags in status register (01b(r1ID)(r2ID))

Multiplyes r1 register and $xxxxx address, stores result in S register. Updates OW, Z and N flags in status register (01c(r1ID)$Xxxxxx)

Multiplyes $xxxxx address and r2 register, stores result in S register. Updates OW, Z and N flags in status register (01d$Xxxxxx(r2ID))

Multiplyes $xxxxx and $yyyyy addresses, stores result in S register. Updates OW, Z and N flags in status register (01e$XxxxxxYyyyyy)

idiv (,r1,r2), (,r1,$Xxxxxx), ($Xxxxxx,r2), ($Xxxxxx,$Yyyyyy):

Divides r1 by r2, stores result in S register. Updates E, Z and N flags in status register (01f(r1ID)(r2ID))

Divides r1 by $xxxxx, stores result in S register. Updates E, Z and N flags in status register (020(r1ID)$Xxxxxx)

Divides $xxxxx by r2, stores result in S register. Updates E, Z and N flags in status register (021$Xxxxxx(r2ID))

Divides $xxxxx by $yyyyy, stores result in S register. Updates E, Z and N flags in status register (022$XxxxxxYyyyyy)

iinc $Xxxxxx, r:

Increments address xxxxx (023$Xxxxxx)

Increments register r (024(rID))

idec $Xxxxxx, r:

Decrements address XXXXX (025Xxxxxx)

Decrements register r (026(rID))

fpadd r1,r2:

Adds r1 and r2 registers, stores result in fpS register. Updates OW, Z, and N flags in status register (027(r1ID)(r2ID))

fpsub r1,r2:

Subtracts r2 from r1, stores result in fpS register. Updates OW, Z and N flags in status register (028(r1ID)(r2ID))

fpmul r1,r2:

Multiplyes r1 and r2 registers, stores result in fpS register. Updates OW, Z and N flags in status register (029(r1ID)(r2ID))

fpdiv r1,r2:

Divides r1 by r2, stores result in fpS register. Updates E, Z and N flags in status register (02a(r1ID)(r2ID))

fpinc r:

Increments register r (02b(rID))

fpdec r:

Decrements register r (02c(rID))

phb $Xxxxxx, r:

Increments stack register and sets $-00000(%sp) to $xxxxx (02d)

Increments stack register and sets $-00000(%sp) to r register (02e)

plb $Xxxxxx, r:

Decrements stack register and sets $xxxxx register to $-00000(%sp) (02f)

Decrements stack register and sets r register to $-00000(%sp) (030)

jmp $Xxxxxx, r:

Jumps to $xxxxx address(031Xxxxxx)

Jumps to r register (032(rID))

jow $Xxxxxx, r:

Jumps to $xxxxx address if OW bit is set (033Xxxxxx)

Jumps to r register if OW bit is set (034(rID))

jnow $Xxxxxx, r:

Jumps to $xxxxx address if OW bit is clear (035Xxxxxx)

Jumps to r register if OW is clear (036(rID))

jz $Xxxxxx, r:

Jumps to $xxxxx address if Z bit is set (037Xxxxxx)

Jumps to r register if Z bit is set (038(rID))

jnz $Xxxxxx, r:

Jumps to $xxxxx address if Z bit is clear (039Xxxxxx)

Jumps to r register if Z bit is clear(03a(rID))

jn $Xxxxxx, r:

Jumps to $xxxxx address if N bit is set (03bXxxxxx)

Jumps to r register if N bit is set (03c(rID))

jnn $Xxxxxx, r:

Jumps to $xxxxx address if N bit is clear (03dXxxxxx)

Jumps to r register if N bit is clear(03e(rID))

je $Xxxxxx, r:

Jumps to $xxxxx address if E bit is set (03fXxxxxx)

Jumps to r register if E bit is set(040(rID))

jne $Xxxxxx, r:

Jumps to $xxxxx address if E bit is clear (041Xxxxxx)

Jumps to r register if E bit is clear(042(rID))

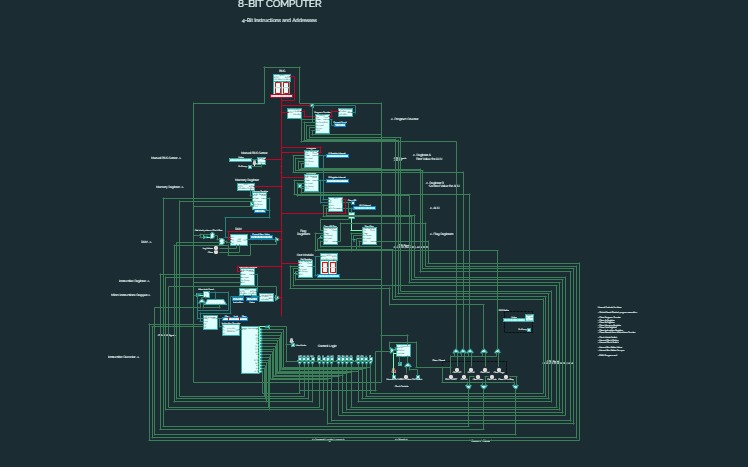

8-Bit Computer with Complex Lanes

8-Bit Computer with Complex LanesFollowed the instruction of the 8-Bit Computer YouTube video series by Ben Eater. I also extended it's functionalities a little bit by upgrading from 16 bytes to 256 bytes of RAM and I added a Micro Step Counter Reset (SCR) instruction signal to allow operations to finish earlier.