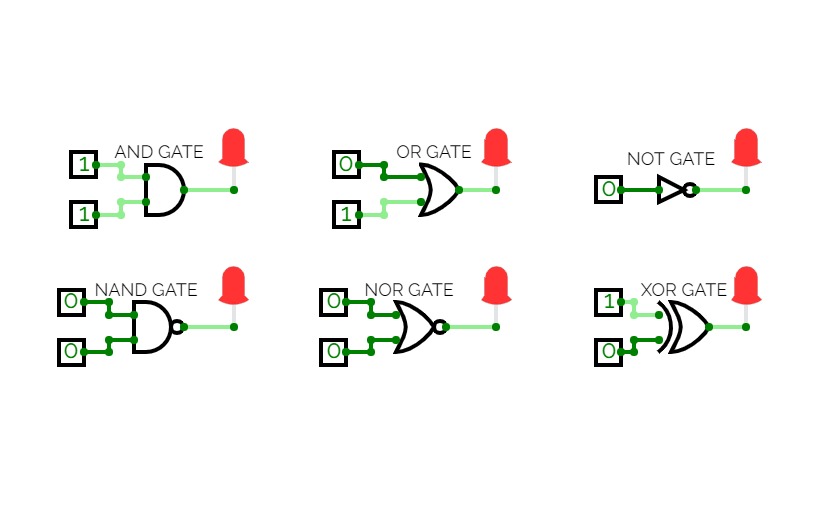

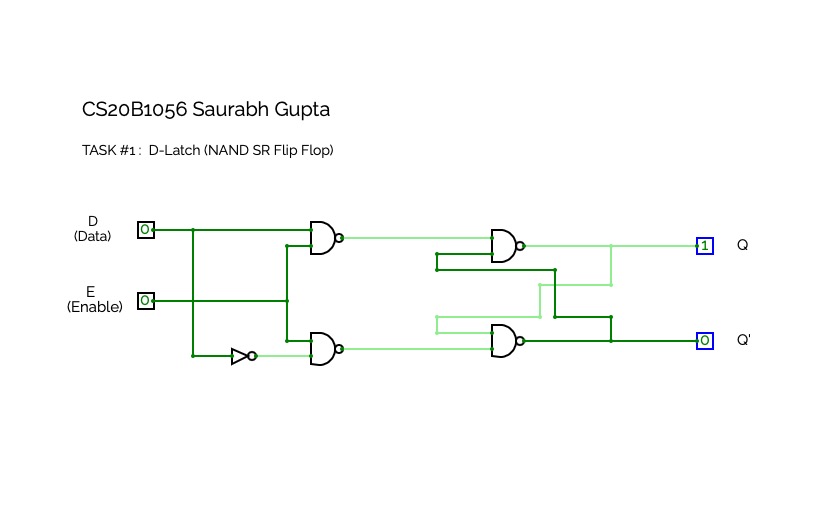

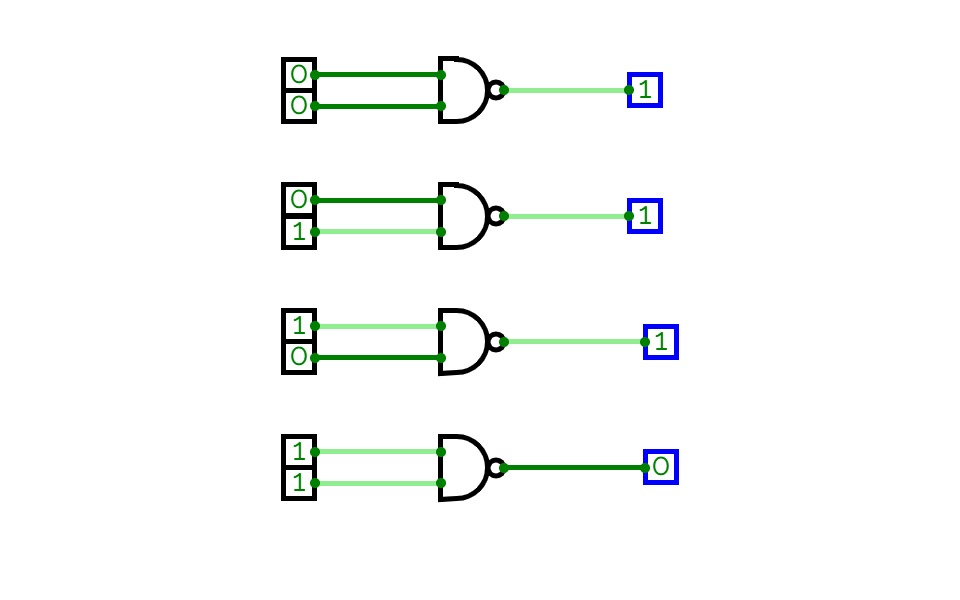

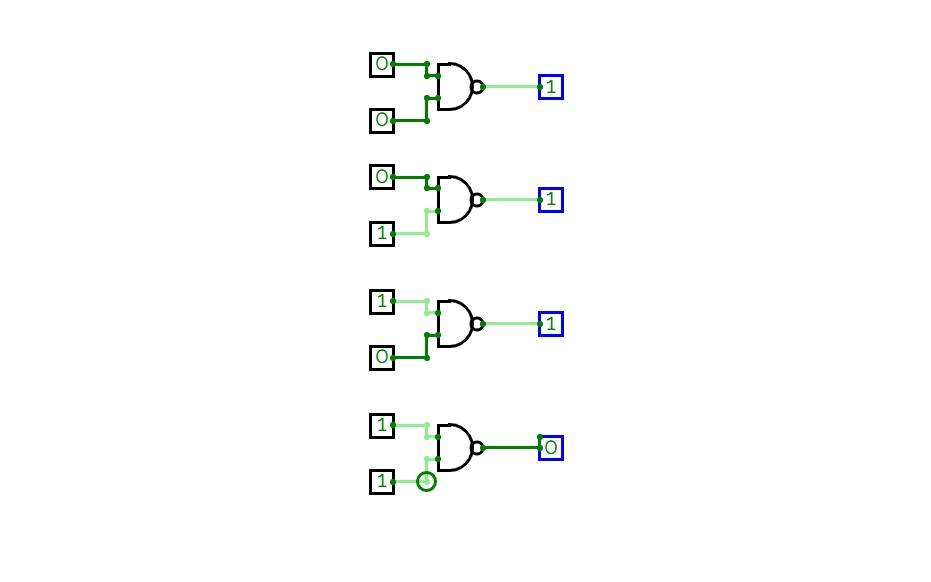

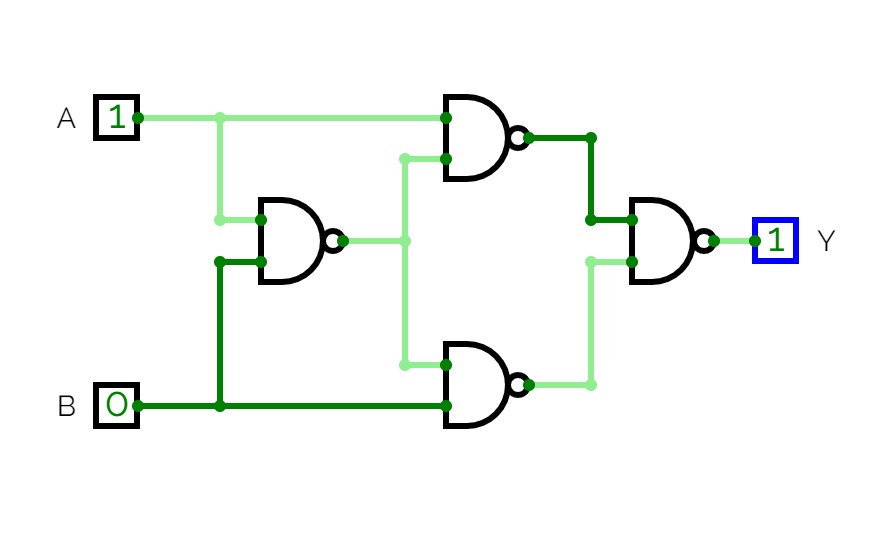

D-Latch (NAND - SR Flip Flop)

D-Latch (NAND - SR Flip Flop){"layout":{"width":100,"height":180,"title_x":50,"title_y":13,"titleEnabled":true},"verilogMetadata":{"isVerilogCircuit":false,"isMainCircuit":false,"code":"// Write Some Verilog Code Here!","subCircuitScopeIds":[]},"allNodes":[{"x":-10,"y":-10,"type":0,"bitWidth":1,"label":"","connections":[12]},{"x":-10,"y":10,"type":0,"bitWidth":1,"label":"","connections":[13]},{"x":30,"y":0,"type":1,"bitWidth":1,"label":"","connections":[20]},{"x":-10,"y":-10,"type":0,"bitWidth":1,"label":"","connections":[14]},{"x":-10,"y":10,"type":0,"bitWidth":1,"label":"","connections":[15]},{"x":30,"y":0,"type":1,"bitWidth":1,"label":"","connections":[21]},{"x":-10,"y":-10,"type":0,"bitWidth":1,"label":"","connections":[16]},{"x":-10,"y":10,"type":0,"bitWidth":1,"label":"","connections":[17]},{"x":30,"y":0,"type":1,"bitWidth":1,"label":"","connections":[22]},{"x":-10,"y":-10,"type":0,"bitWidth":1,"label":"","connections":[18]},{"x":-10,"y":10,"type":0,"bitWidth":1,"label":"","connections":[19]},{"x":30,"y":0,"type":1,"bitWidth":1,"label":"","connections":[23]},{"x":10,"y":0,"type":1,"bitWidth":1,"label":"","connections":[0]},{"x":10,"y":0,"type":1,"bitWidth":1,"label":"","connections":[1]},{"x":10,"y":0,"type":1,"bitWidth":1,"label":"","connections":[3]},{"x":10,"y":0,"type":1,"bitWidth":1,"label":"","connections":[4]},{"x":10,"y":0,"type":1,"bitWidth":1,"label":"","connections":[6]},{"x":10,"y":0,"type":1,"bitWidth":1,"label":"","connections":[7]},{"x":10,"y":0,"type":1,"bitWidth":1,"label":"","connections":[9]},{"x":10,"y":0,"type":1,"bitWidth":1,"label":"","connections":[10]},{"x":10,"y":0,"type":0,"bitWidth":1,"label":"","connections":[2]},{"x":10,"y":0,"type":0,"bitWidth":1,"label":"","connections":[5]},{"x":10,"y":0,"type":0,"bitWidth":1,"label":"","connections":[8]},{"x":10,"y":0,"type":0,"bitWidth":1,"label":"","connections":[11]}],"id":61002421165,"name":"Main","Input":[{"x":480,"y":150,"objectType":"Input","label":"","direction":"RIGHT","labelDirection":"LEFT","propagationDelay":0,"customData":{"nodes":{"output1":12},"values":{"state":0},"constructorParamaters":["RIGHT",1,{"x":0,"y":20,"id":"el3V6iZqskEpCsaggf9Q"}]}},{"x":480,"y":170,"objectType":"Input","label":"","direction":"RIGHT","labelDirection":"LEFT","propagationDelay":0,"customData":{"nodes":{"output1":13},"values":{"state":0},"constructorParamaters":["RIGHT",1,{"x":0,"y":40,"id":"X7LXZtRSIvLIQsPFKKKD"}]}},{"x":480,"y":230,"objectType":"Input","label":"","direction":"RIGHT","labelDirection":"LEFT","propagationDelay":0,"customData":{"nodes":{"output1":14},"values":{"state":0},"constructorParamaters":["RIGHT",1,{"x":0,"y":60,"id":"hs5wbXTYA5nwSLi8jmIc"}]}},{"x":480,"y":250,"objectType":"Input","label":"","direction":"RIGHT","labelDirection":"LEFT","propagationDelay":0,"customData":{"nodes":{"output1":15},"values":{"state":1},"constructorParamaters":["RIGHT",1,{"x":0,"y":80,"id":"VWZtYBpdBQbB2TJwup4d"}]}},{"x":480,"y":310,"objectType":"Input","label":"","direction":"RIGHT","labelDirection":"LEFT","propagationDelay":0,"customData":{"nodes":{"output1":16},"values":{"state":1},"constructorParamaters":["RIGHT",1,{"x":0,"y":100,"id":"8ZQA3eFQQuFfFE1k3xiu"}]}},{"x":480,"y":330,"objectType":"Input","label":"","direction":"RIGHT","labelDirection":"LEFT","propagationDelay":0,"customData":{"nodes":{"output1":17},"values":{"state":0},"constructorParamaters":["RIGHT",1,{"x":0,"y":120,"id":"7TD7ctoPUOu4HaxfjZEo"}]}},{"x":480,"y":390,"objectType":"Input","label":"","direction":"RIGHT","labelDirection":"LEFT","propagationDelay":0,"customData":{"nodes":{"output1":18},"values":{"state":1},"constructorParamaters":["RIGHT",1,{"x":0,"y":140,"id":"9ZOEpcIWLcnimerqS0Dt"}]}},{"x":480,"y":410,"objectType":"Input","label":"","direction":"RIGHT","labelDirection":"LEFT","propagationDelay":0,"customData":{"nodes":{"output1":19},"values":{"state":1},"constructorParamaters":["RIGHT",1,{"x":0,"y":160,"id":"9Me8sGmK2v0nB0TOd6zO"}]}}],"Output":[{"x":700,"y":160,"objectType":"Output","label":"","direction":"LEFT","labelDirection":"RIGHT","propagationDelay":0,"customData":{"nodes":{"inp1":20},"constructorParamaters":["LEFT",1,{"x":100,"y":20,"id":"AjjqZezZRfAr0J4gm52n"}]}},{"x":700,"y":240,"objectType":"Output","label":"","direction":"LEFT","labelDirection":"RIGHT","propagationDelay":0,"customData":{"nodes":{"inp1":21},"constructorParamaters":["LEFT",1,{"x":100,"y":40,"id":"fvV2pMItTBmgVchf651j"}]}},{"x":710,"y":320,"objectType":"Output","label":"","direction":"LEFT","labelDirection":"RIGHT","propagationDelay":0,"customData":{"nodes":{"inp1":22},"constructorParamaters":["LEFT",1,{"x":100,"y":60,"id":"ERq1mtFdMBrywO07dxTb"}]}},{"x":710,"y":400,"objectType":"Output","label":"","direction":"LEFT","labelDirection":"RIGHT","propagationDelay":0,"customData":{"nodes":{"inp1":23},"constructorParamaters":["LEFT",1,{"x":100,"y":80,"id":"FbTZHF8UzgsMtiM1KCpa"}]}}],"NandGate":[{"x":580,"y":160,"objectType":"NandGate","label":"","direction":"RIGHT","labelDirection":"LEFT","propagationDelay":10,"customData":{"constructorParamaters":["RIGHT",2,1],"nodes":{"inp":[0,1],"output1":2}}},{"x":580,"y":240,"objectType":"NandGate","label":"","direction":"RIGHT","labelDirection":"LEFT","propagationDelay":10,"customData":{"constructorParamaters":["RIGHT",2,1],"nodes":{"inp":[3,4],"output1":5}}},{"x":580,"y":320,"objectType":"NandGate","label":"","direction":"RIGHT","labelDirection":"LEFT","propagationDelay":10,"customData":{"constructorParamaters":["RIGHT",2,1],"nodes":{"inp":[6,7],"output1":8}}},{"x":580,"y":400,"objectType":"NandGate","label":"","direction":"RIGHT","labelDirection":"LEFT","propagationDelay":10,"customData":{"constructorParamaters":["RIGHT",2,1],"nodes":{"inp":[9,10],"output1":11}}}],"restrictedCircuitElementsUsed":[],"nodes":[],"scopes":[],"logixClipBoardData":true}