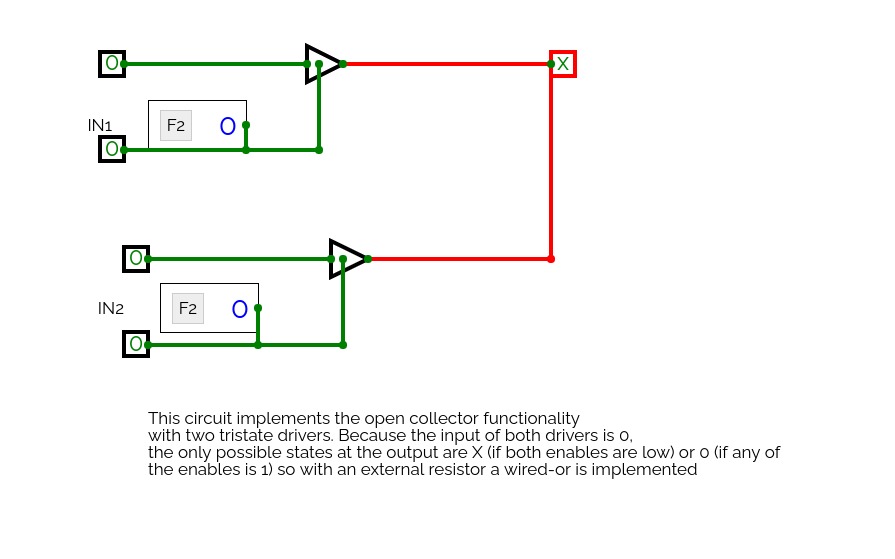

Tristate components are commonly used to implement bus connections, where the signals are effectively OR'ed onto the bus. This doesn't happen in the simulator at present (5th July 2023). There are also no diodes available, which imposes a similar limit upon bus outputs.

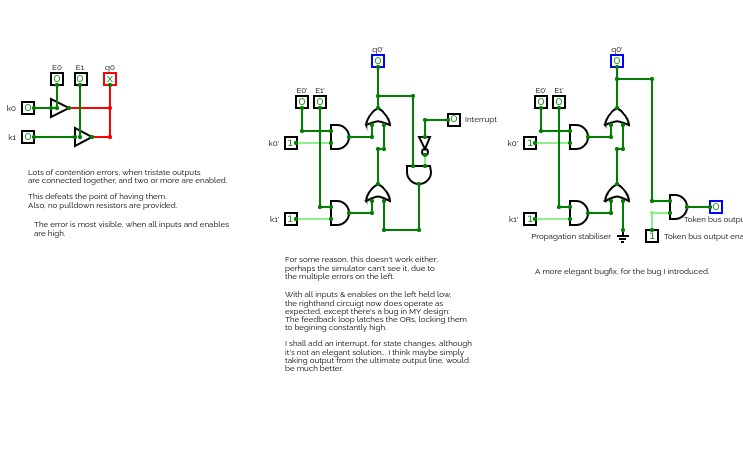

I have included a possible workaround. Note the feedback loop, which is necessary to preserve the ability of bus lines to be tapped at any point. --This introduced a bug of its own though: Any high state latched the ORs high constantly!

I added an interrupt which could be triggered upon an detection of a state change, but this is really inelegant!

Instead, I suggest breaking the loop entirely, and just taking any bus output from the final output of the chain of ORs. This results in twice the number of bus lines, but everything is a compromise while tristate use is unsupported. As long as the compromise works, that should be okay.

For additional clarity, I've added a second version of the OR-chain circuit, with the loop broken, and a token bus output connection.