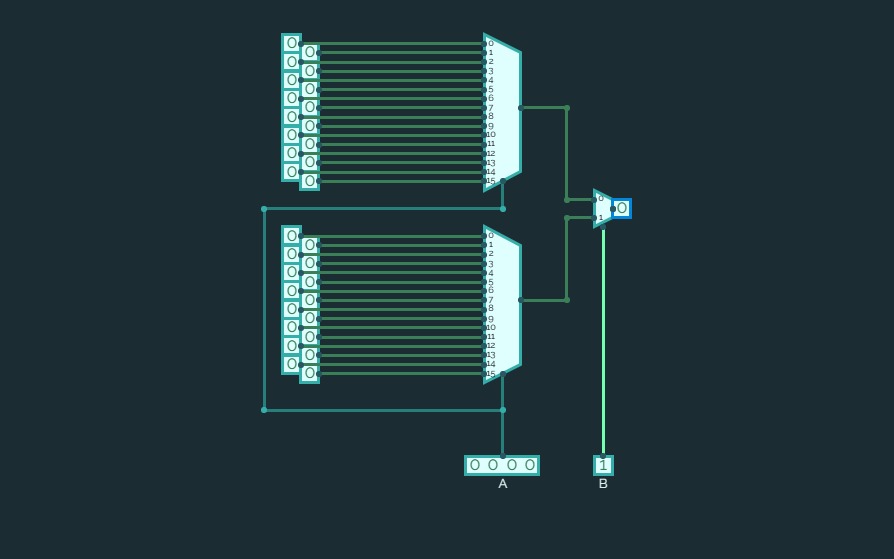

32 : 1 mux using 16 : 1 mux

32 : 1 mux using 16 : 1 muxMid-Term Practice Q2

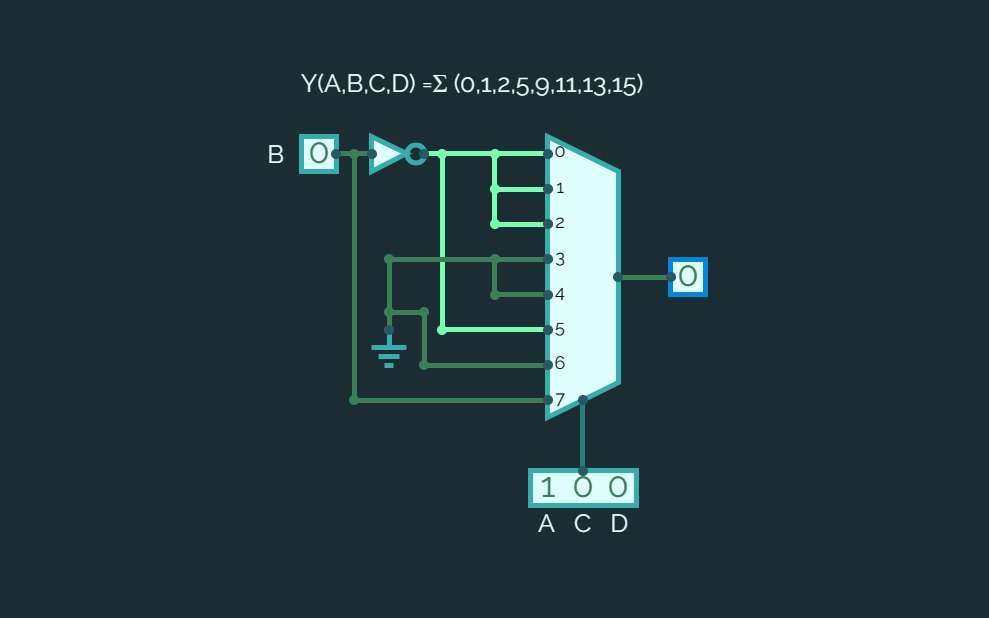

Mid-Term Practice Q2Implement the following logic function using 8 to 1 multiplexer by considering A,C and

D as select lines.

Y(A,B,C,D) =Σ (0,1,2,5,9,11,13,15)

Where A is the MSB bit and D is the LSB bit

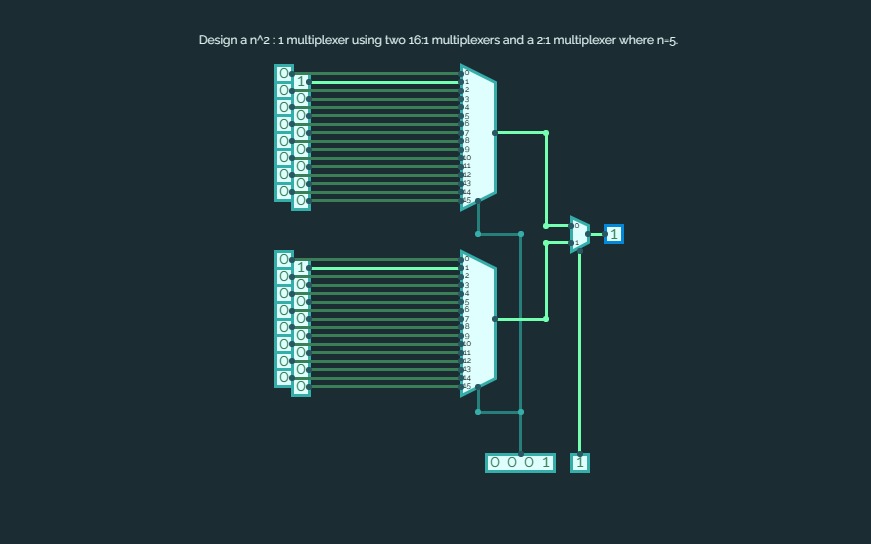

Mid Term Q3

Mid Term Q3Design a n^2 : 1 multiplexer using two 16:1 multiplexers and a 2:1 multiplexer where n=5.

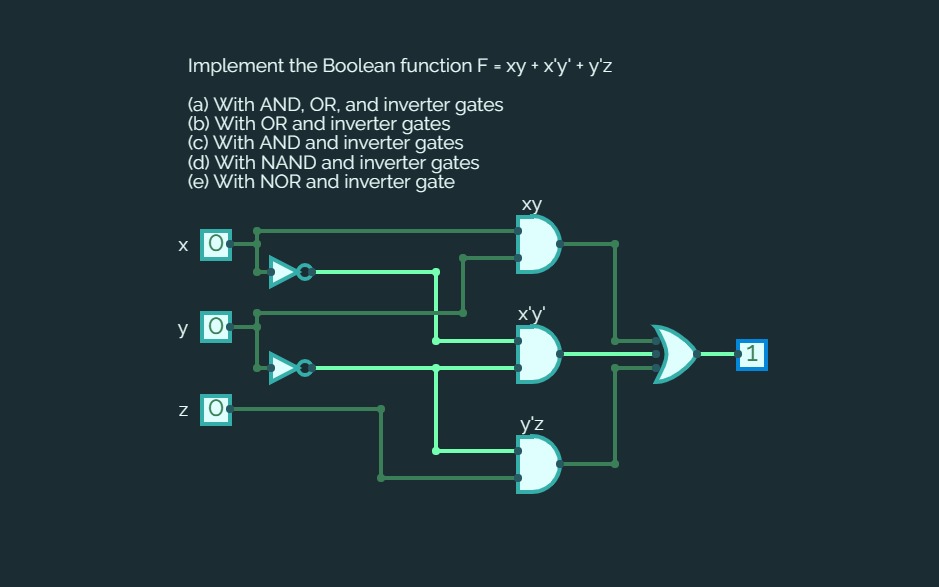

Mid Term Q2

Mid Term Q2Implement the Boolean function F = xy + x'y' + y'z

(a) With AND, OR, and inverter gates

(b) With OR and inverter gates

(c) With AND and inverter gates

(d) With NAND and inverter gates

(e) With NOR and inverter gate

Mid-Term Practice Q6

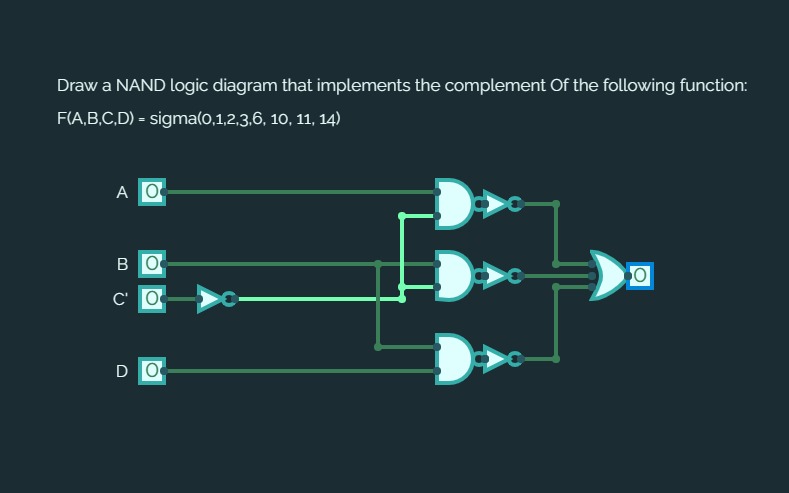

Mid-Term Practice Q6Draw a NAND logic diagram that implements the complement Of the following function:

F(A,B,C,D) = sigma(0,1,2,3,6, 10, 11, 14)