prateek sachan

Member since: 3 years

Educational Institution: Not Entered

Country: Not Entered

HW 4

HW 4

2421 TO 84-2-1

2421 TO 84-2-1

COMMON CATHODE WITH DON'T CARES

COMMON CATHODE WITH DON'T CARES

COMMON ANODE with / without DON'T CARE

COMMON ANODE with / without DON'T CARE

CAT 2 Q2

CAT 2 Q2

Q1 THEORY

Q1 THEORY

hw 5

hw 5

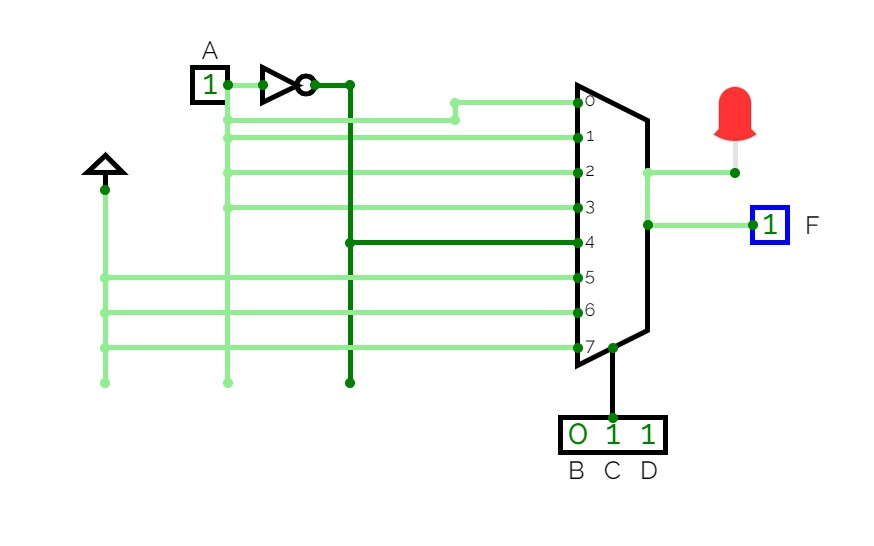

F'16:1 MUX

F'16:1 MUX

8:1 A

8:1 A

C

C

B8X1

B8X1

C1

C1

b1

b1

code1

code1

CODE2

CODE2

CODE3

CODE3

CODE4

CODE4

74LS194 TASK 5

74LS194 TASK 5

3*8 decoder using 2*4

3*8 decoder using 2*4

3*8 DECODER USING TWO 2*4 DECODERS

3*8 DECODER USING TWO 2*4 DECODERS

3 by 8 decoder using only two (2 by 4)

3 by 8 decoder using only two (2 by 4)

4:16 decoder using 3:8

4:16 decoder using 3:8

REG NO USING DECODER

REG NO USING DECODER

HW 4

HW 4

HW -3

HW -3

DLCD THEORY TASK-1

DLCD THEORY TASK-1

DLCD DA1

DLCD DA1

DLCD DA1

DLCD DA1

DLCD DA1

DLCD DA1

task v homework dlcd PIPO SHIFT REGISTER USING DFF

task v homework dlcd PIPO SHIFT REGISTER USING DFF

task 5hw nand gate circuit

task 5hw nand gate circuit

COMMON ANODE WITHOUT DON'T CARES

COMMON ANODE WITHOUT DON'T CARES

CAT 1 Q4

CAT 1 Q4

CAT 1 Q7

CAT 1 Q7

CAT 1 Q7

CAT 1 Q7

CAT 1 Q8

CAT 1 Q8

CAT 1 Q8

CAT 1 Q8

CAT 1 Q5

CAT 1 Q5

CAT 1 Q5

CAT 1 Q5

CAT 2 Q4

CAT 2 Q4

CAT 2 Q5 DECODER CIRCUIT

CAT 2 Q5 DECODER CIRCUIT

CAT 2 Q5 DECODER CIRCUIT

CAT 2 Q5 DECODER CIRCUIT

CAT 2 Q5 - 4:16 Decoder using NOR logic.

CAT 2 Q5 - 4:16 Decoder using NOR logic.

CAT 2 Q7

CAT 2 Q7

CAT 2 Q7

CAT 2 Q7

CAT 2 Q9

CAT 2 Q9

CAT 2 Q8

CAT 2 Q8

CAT 2 Q9

CAT 2 Q9

14 LAB PRACTICE

14 LAB PRACTICE

14 LAB PRACTICE

14 LAB PRACTICE

PRATEEK LAB HW

PRATEEK LAB HW

FAT 20MIC0130

FAT 20MIC0130

3:8 DECODER USING 2:4 DECODER

3:8 DECODER USING 2:4 DECODER

3 by 8 decoder using only two (2 by 4)

3 by 8 decoder using only two (2 by 4)

3:8 DECODER USING 2:4

3:8 DECODER USING 2:4

CAT 1 Q4

CAT 1 Q4

D

D

TASK 3 16:1MUX DESIGN

TASK 3 16:1MUX DESIGN

A1

A1

D

D

Universal Shift Register

Universal Shift Register

CAT 1 Q4

CAT 1 Q4

Q1-SEVEN SEGMENT DECODER TO DISPLAY NAME & REG NO

Q1-SEVEN SEGMENT DECODER TO DISPLAY NAME & REG NO

homework 32:1 using 4:1 mux

homework 32:1 using 4:1 mux

COMMON CATHODE WITHOUT DON'T CARE

COMMON CATHODE WITHOUT DON'T CARE

Design 16:4 Encoder using 4:2 Encoder

Design 16:4 Encoder using 4:2 Encoder

4:16 decoder using 3:8

4:16 decoder using 3:8

DLCD TASK3 16:1 MUX

DLCD TASK3 16:1 MUX

MAG COMPARATOR Q9

MAG COMPARATOR Q9

3:8 DECODER USING 2:4 DECODER

3:8 DECODER USING 2:4 DECODER

74LS194 TASK 5

74LS194 TASK 5

3*8 decoder using 2*4

3*8 decoder using 2*4

3:8 DECODER USING 2:4 DECODER

3:8 DECODER USING 2:4 DECODER

Mid-Term Assignment

Mid-Term Assignment

COMMON CATHODE with / without DON'T CARE

COMMON CATHODE with / without DON'T CARE

Experiment 12 : Verification of truth table of 4 bit bidirectional shift register

Experiment 12 : Verification of truth table of 4 bit bidirectional shift register

COMMON CATHODE with/without DON'T CARES [ 1:16 DE-MULTIPLEXER ]

COMMON CATHODE with/without DON'T CARES [ 1:16 DE-MULTIPLEXER ]

CAT 2 Q2

CAT 2 Q2

CAT 2 Q3

CAT 2 Q3

CAT 2 Q3

CAT 2 Q3

CAT 2 Q4

CAT 2 Q4

CAT 2 Q8

CAT 2 Q8

4:16 decoder using 2:4 decoders

4:16 decoder using 2:4 decoders

PARALLEL ADDER Q8 DA 1

PARALLEL ADDER Q8 DA 1

COMMON ANODE with/without DON'T CARES [1:16 DE-MULTIPLEXER]

COMMON ANODE with/without DON'T CARES [1:16 DE-MULTIPLEXER]

CAT 2 Q5 - 4:16 Decoder using NOR logic.

CAT 2 Q5 - 4:16 Decoder using NOR logic.

COMMON ANODE WITH DON'T CARES 16:1 MUX

COMMON ANODE WITH DON'T CARES 16:1 MUX

32 to 1 mux using 4 to 1 mux

32 to 1 mux using 4 to 1 mux

CAT 1 Q4

CAT 1 Q4

COMMON ANODE WITH DON'T CARES 16:1 MUX

COMMON ANODE WITH DON'T CARES 16:1 MUX

4:16 decoder using 2:4 decoders

4:16 decoder using 2:4 decoders

Design 16:4 Encoder using 4:2 Encoder

Design 16:4 Encoder using 4:2 Encoder

4 bit PIPO shift Register

4 bit PIPO shift Register

Experiment 8

Experiment 8