@Focaspeed

Member since: 2 years

Educational Institution: Self-learning

Country: Switzerland

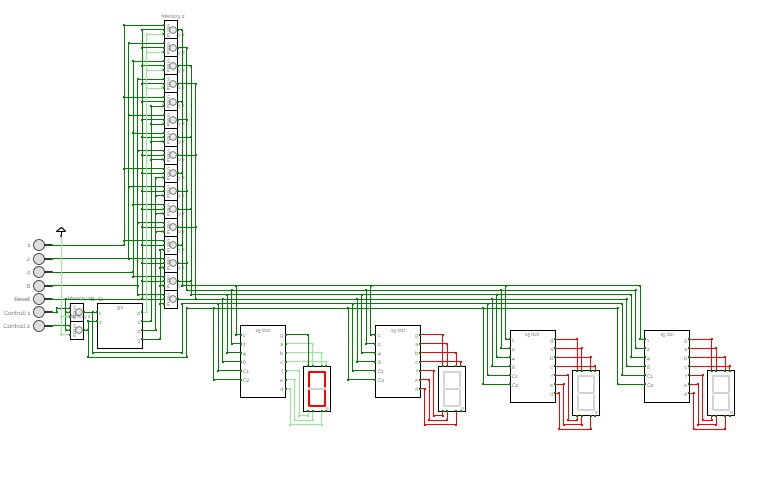

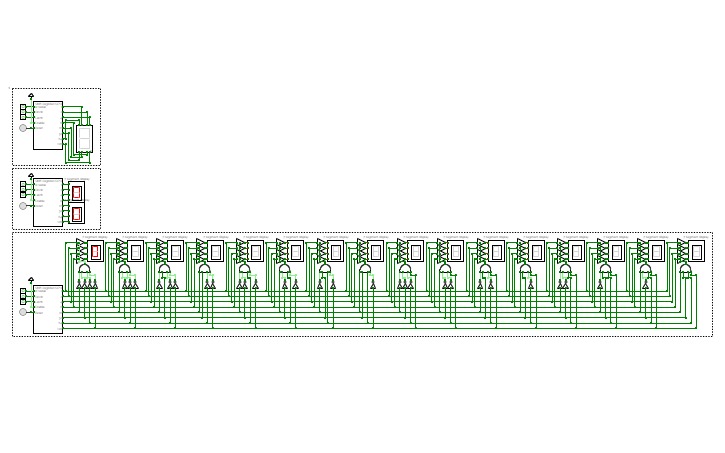

16-Bit Summer

16-Bit Summer

Daten-BUS (4 Bit)

Daten-BUS (4 Bit)

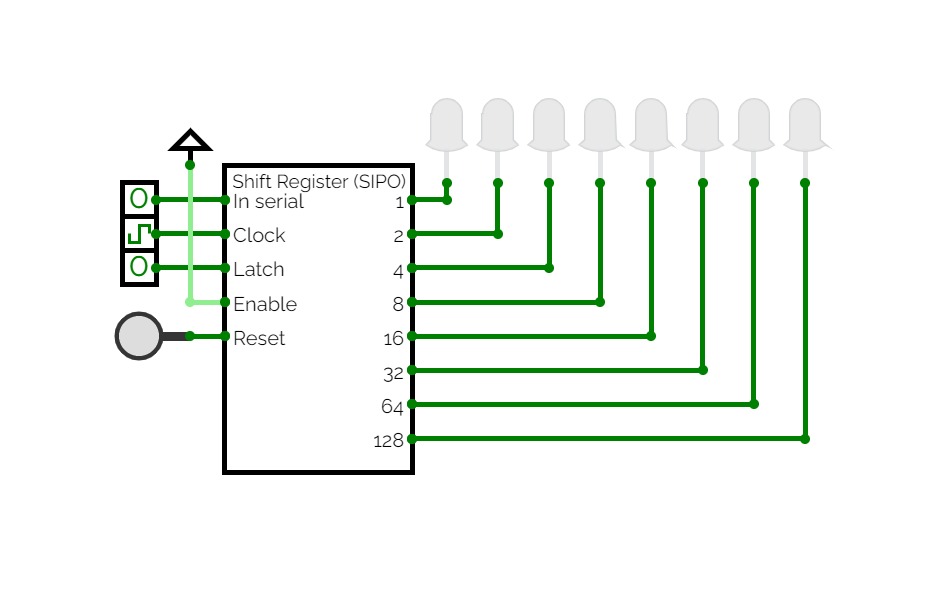

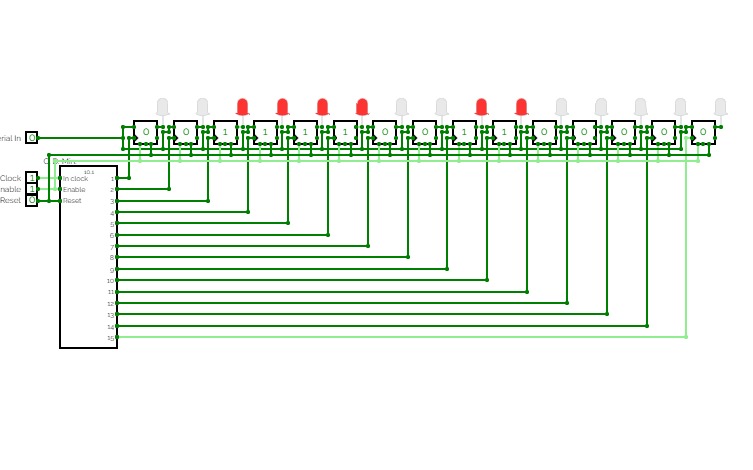

8-Bit Shift Register (SIPO)

8-Bit Shift Register (SIPO)

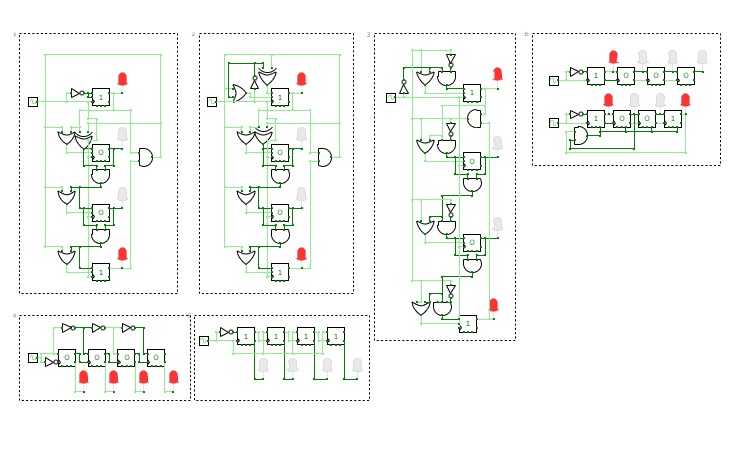

Subcircuits

Subcircuits

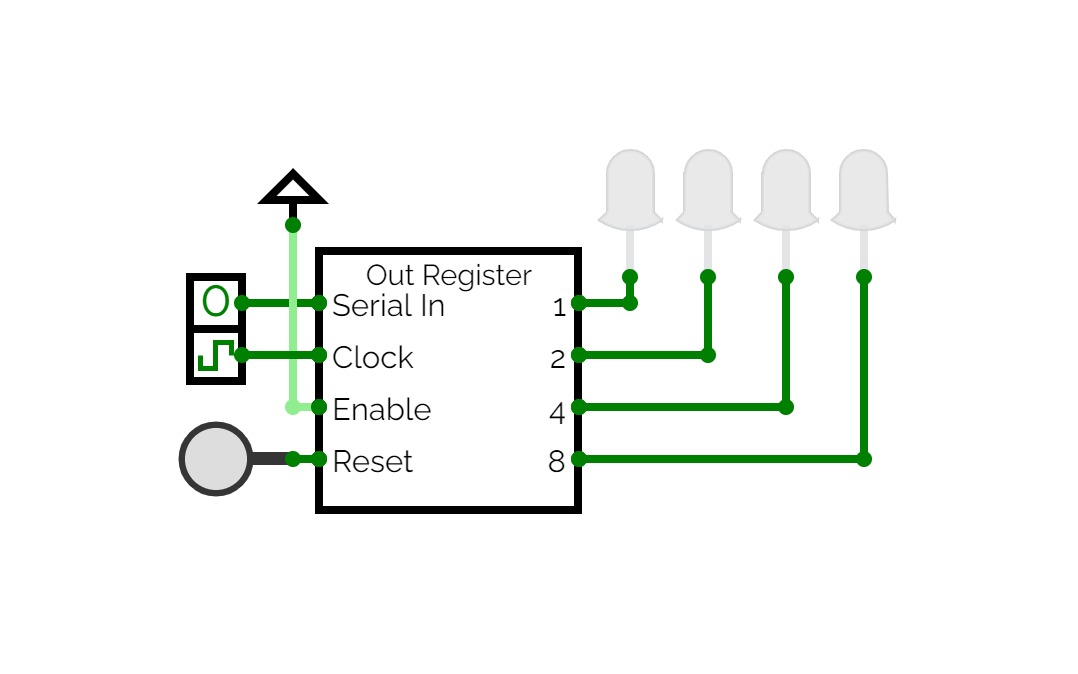

4-Bit Out Register

4-Bit Out Register

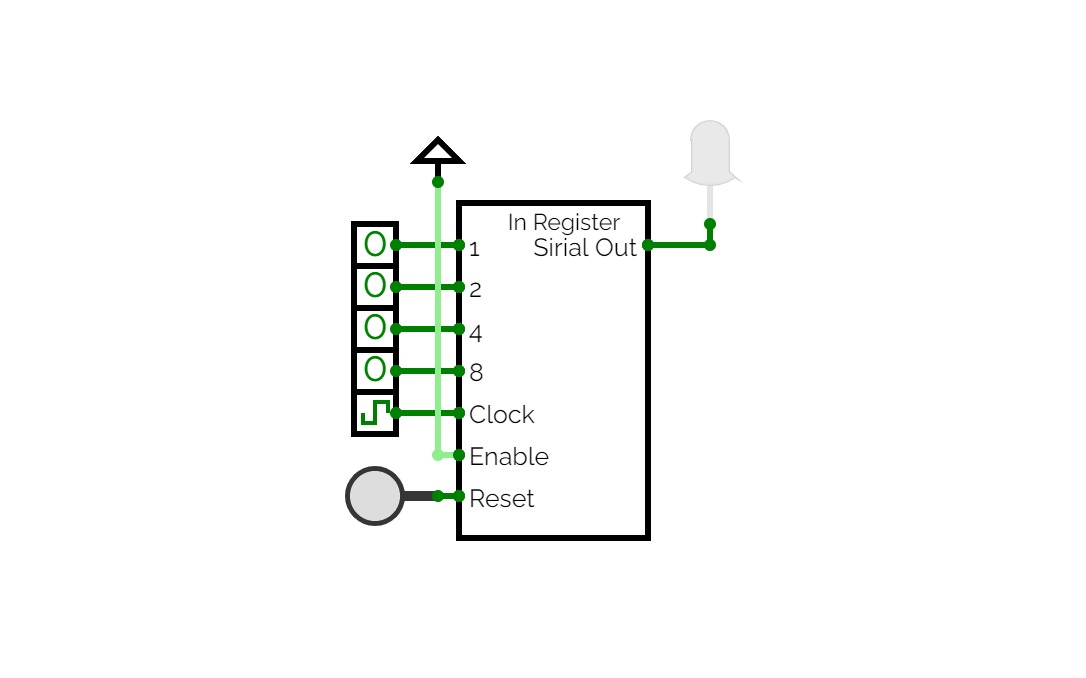

4-Bit Input Register

4-Bit Input Register

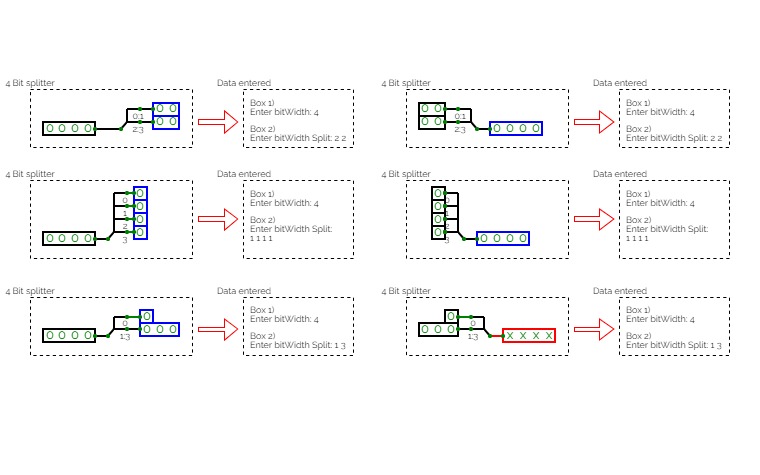

Splitter example

Splitter example

signal controll

signal controll

Counter binary

Counter binary

8-Bit Out Shift Register

8-Bit Out Shift Register

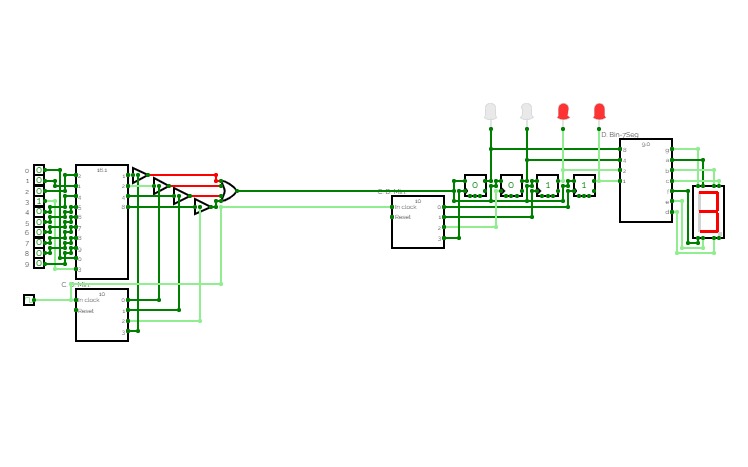

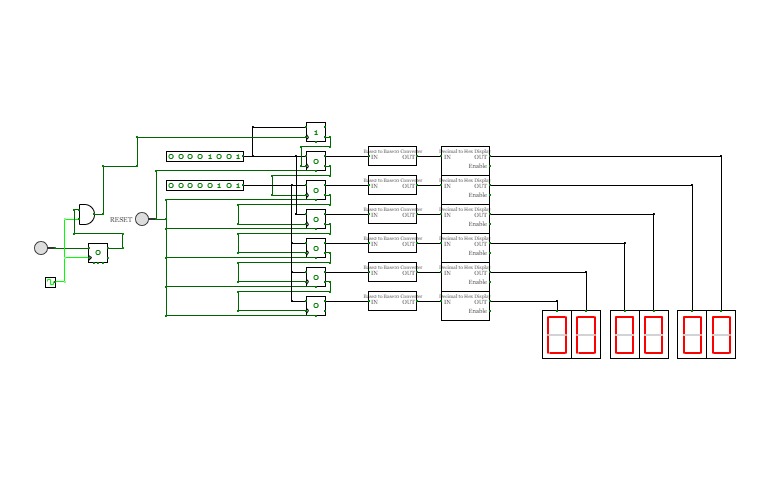

Display 7 segment, drive by Shift Register (SIPO)

Display 7 segment, drive by Shift Register (SIPO)

LED

LED

28BYJ-48 - 5V Stepper Motor driver/ controller

28BYJ-48 - 5V Stepper Motor driver/ controller

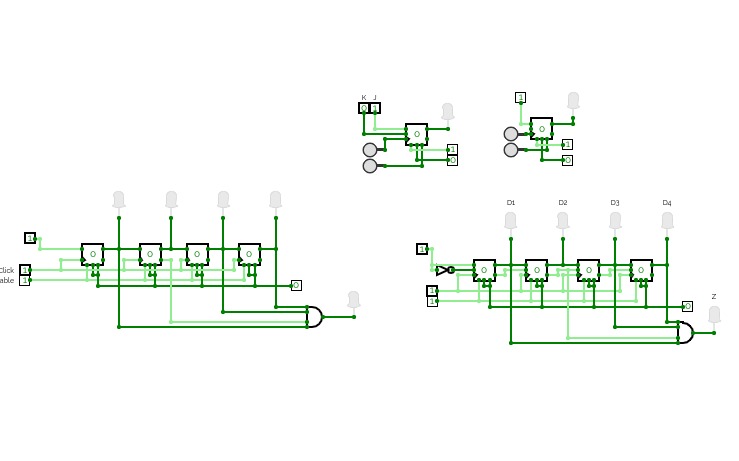

Flip-Flop

Flip-Flop

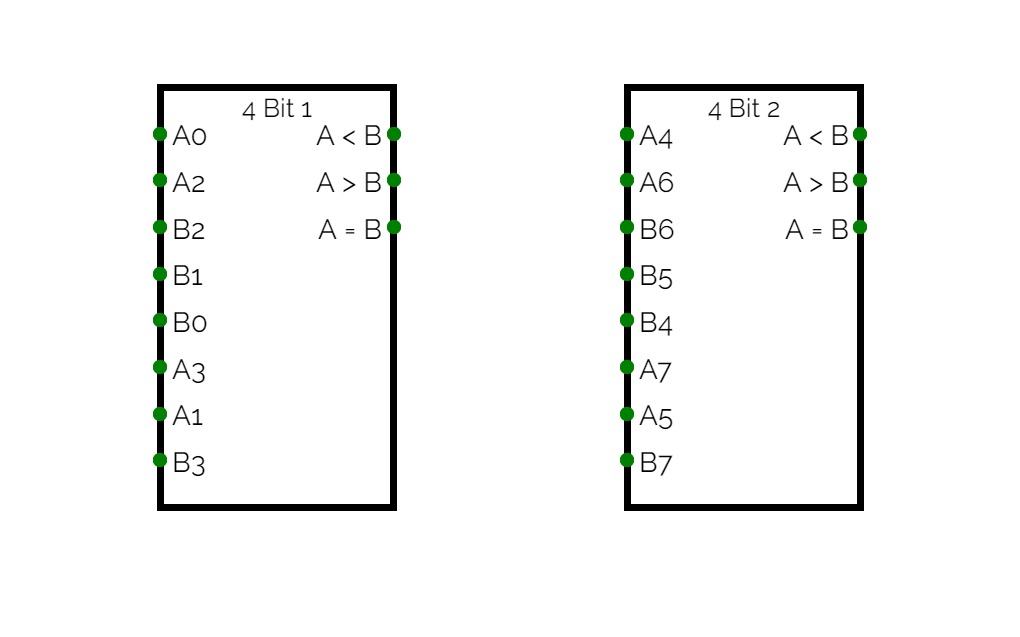

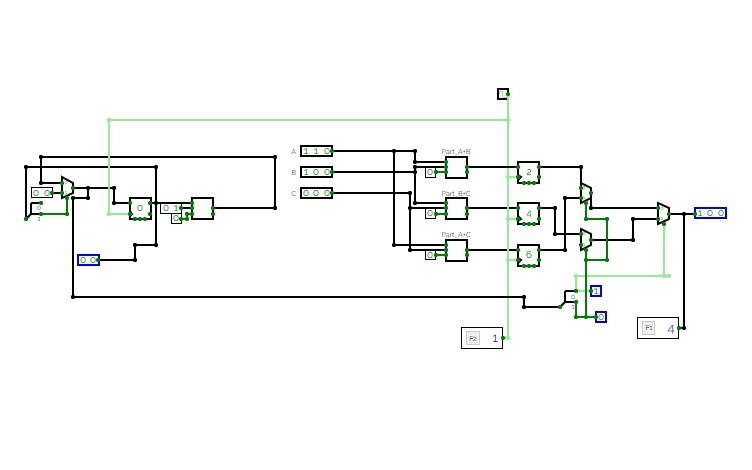

4-Bit modular comparator

4-Bit modular comparator

Keyboard

Keyboard

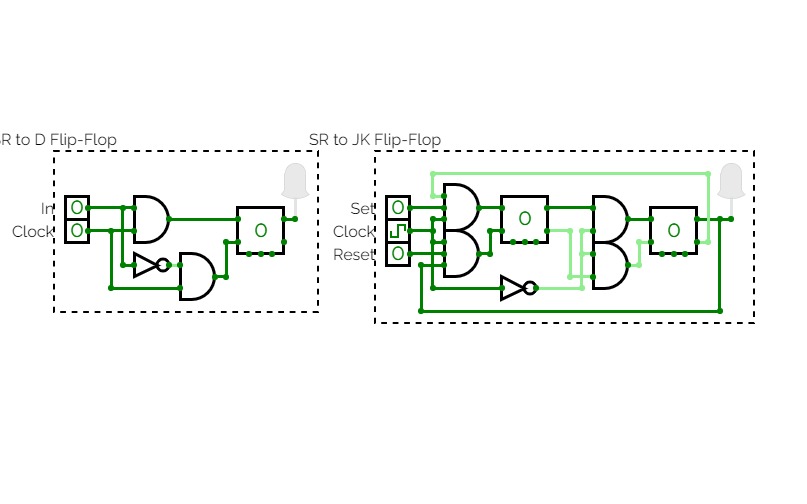

SR Flip Flop to JK and D Flip Flop

SR Flip Flop to JK and D Flip Flop

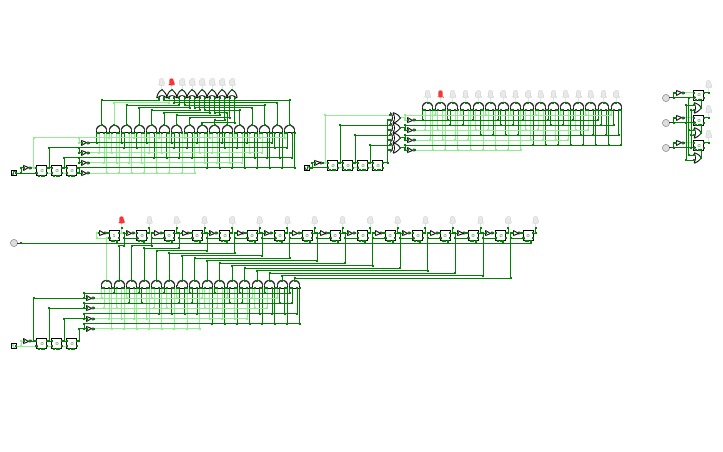

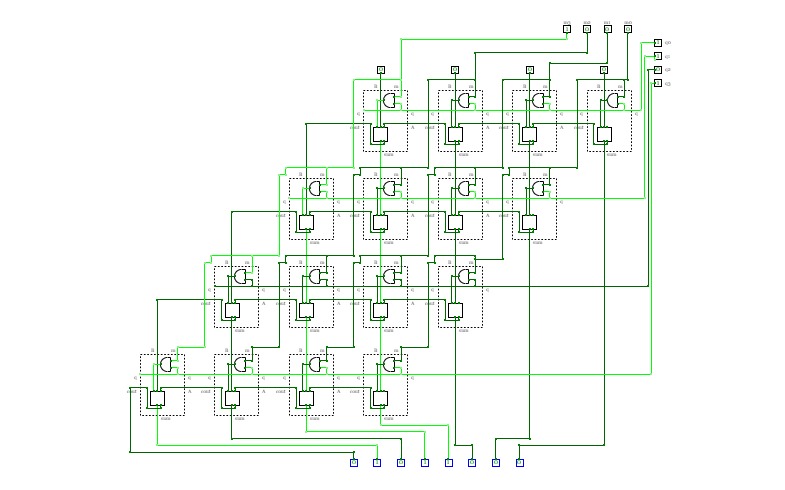

Multiplier

Multiplier

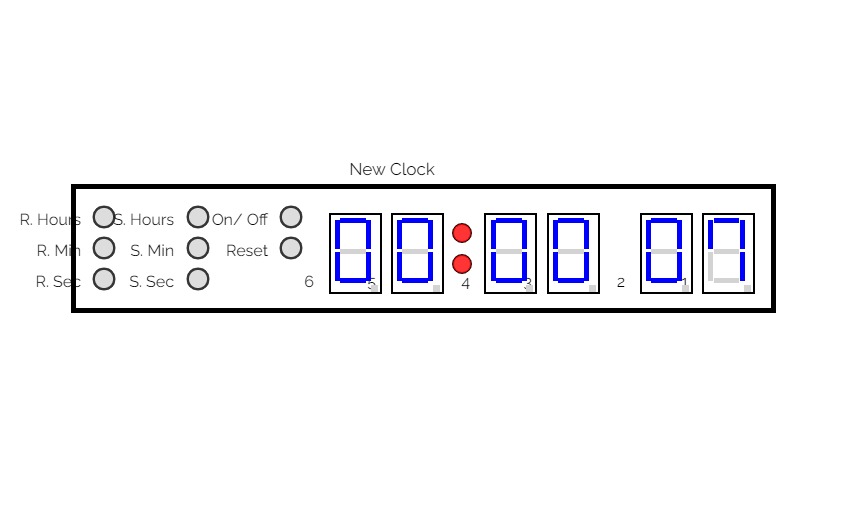

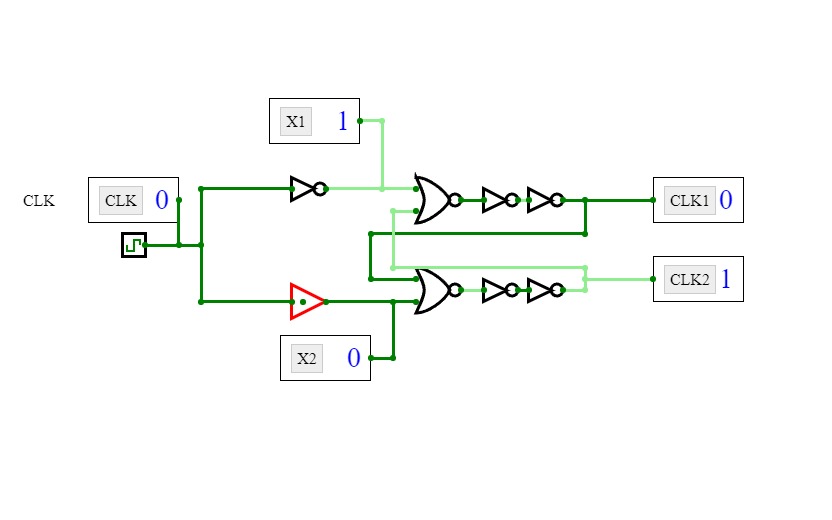

New Clock

New Clock

Subtracter

Subtracter

4-Bit subtraction module

4-Bit subtraction module

4-Bit Adder unit

4-Bit Adder unit

Untitled

Untitled

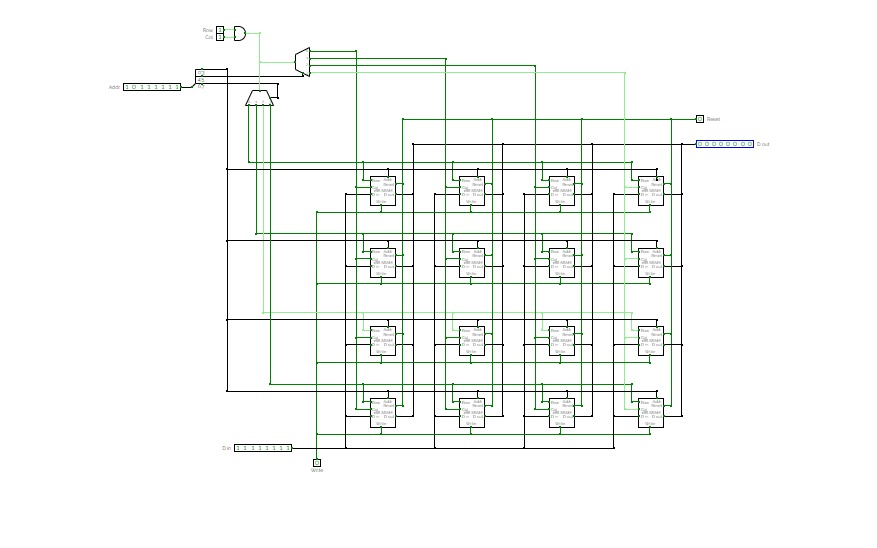

Modular multipler

Modular multipler

4-Bit Subctracter unit

4-Bit Subctracter unit

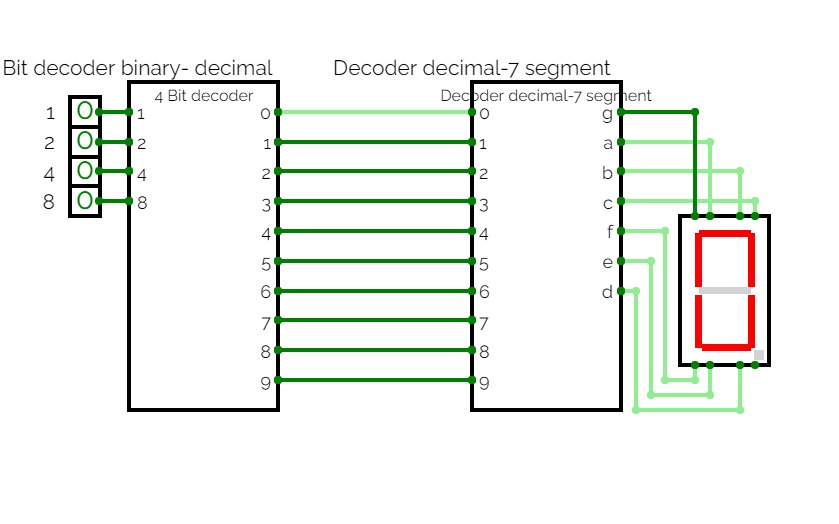

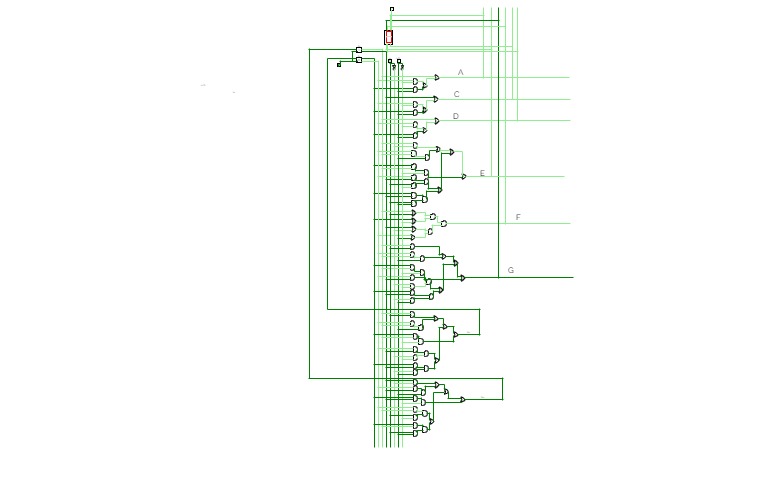

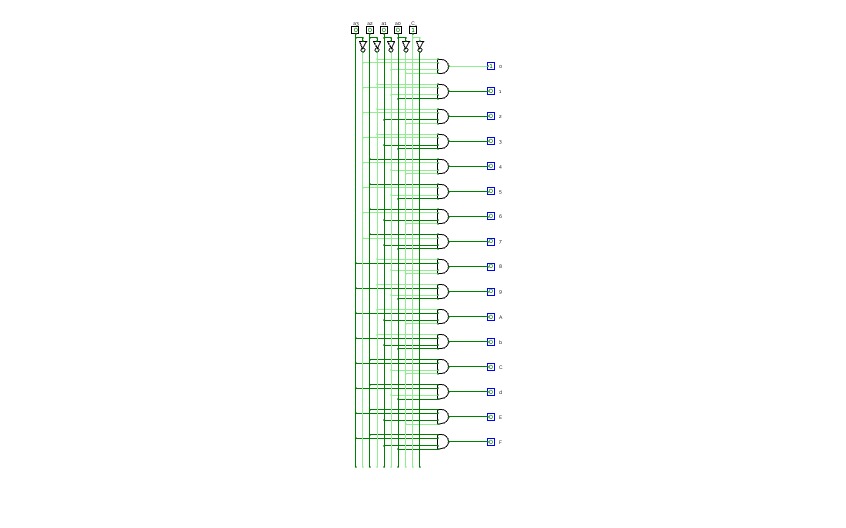

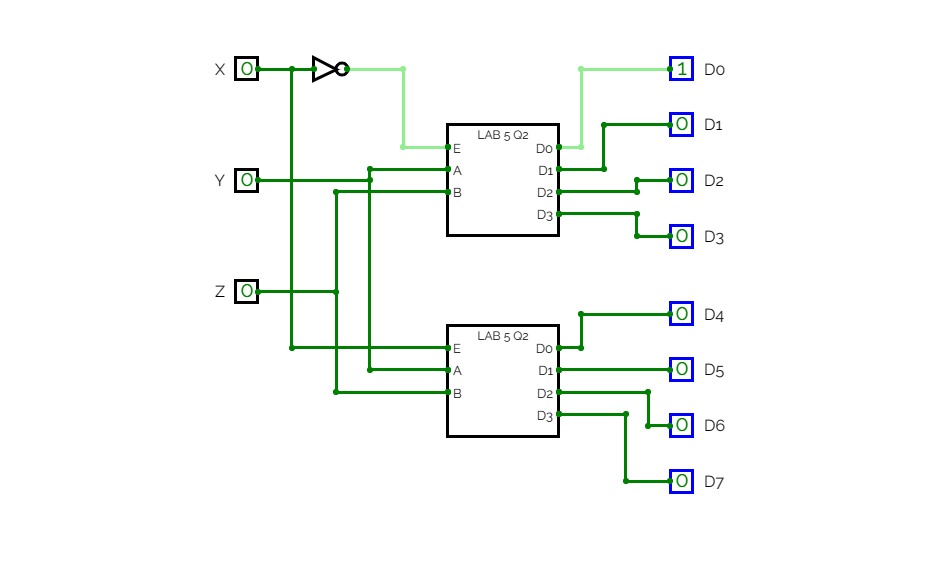

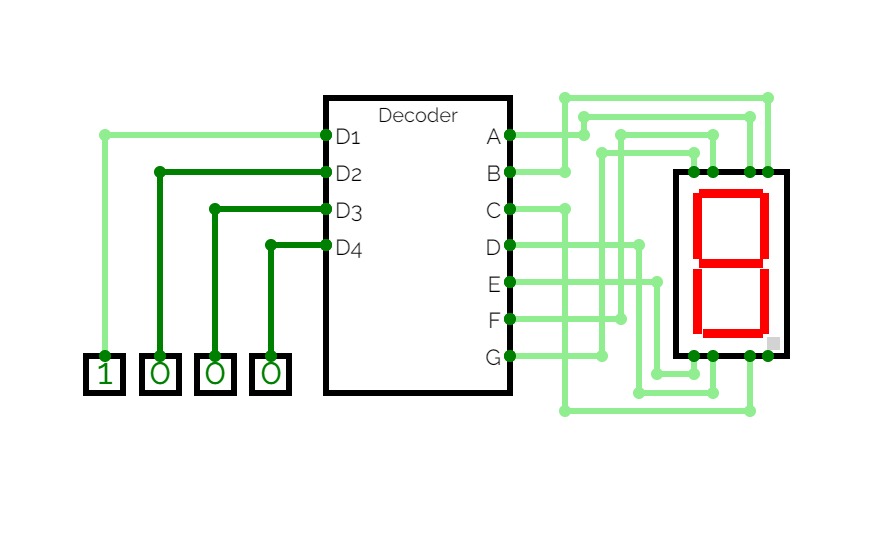

4-Bit modular decoder

4-Bit modular decoder

4-Bit subcircuit decoder example

4-Bit subcircuit decoder example

4-Bit Full Adder

4-Bit Full Adder

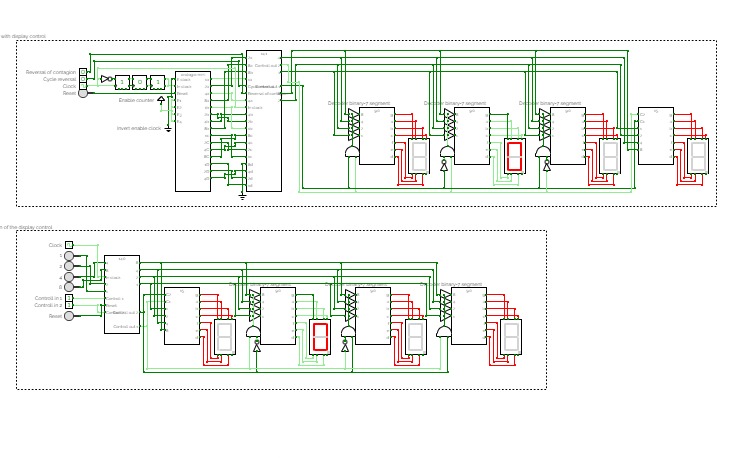

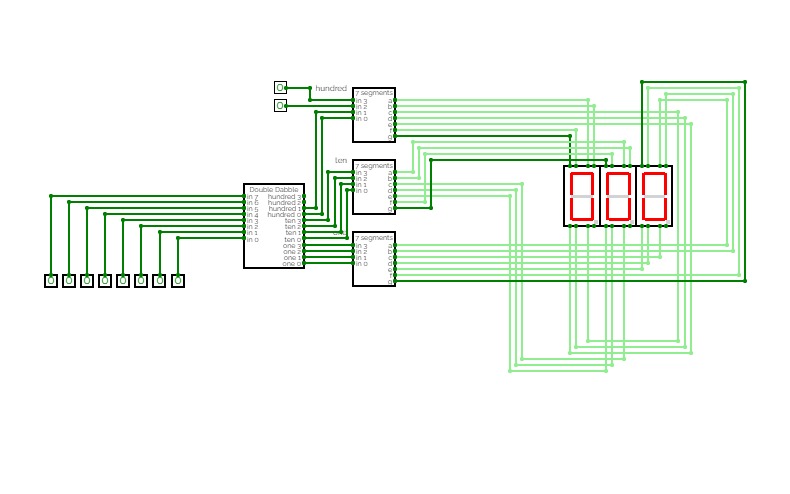

Display

Display

Orologio

Orologio

SAP - 1

SAP - 1

Full Adder From 2 half Adders

Full Adder From 2 half Adders

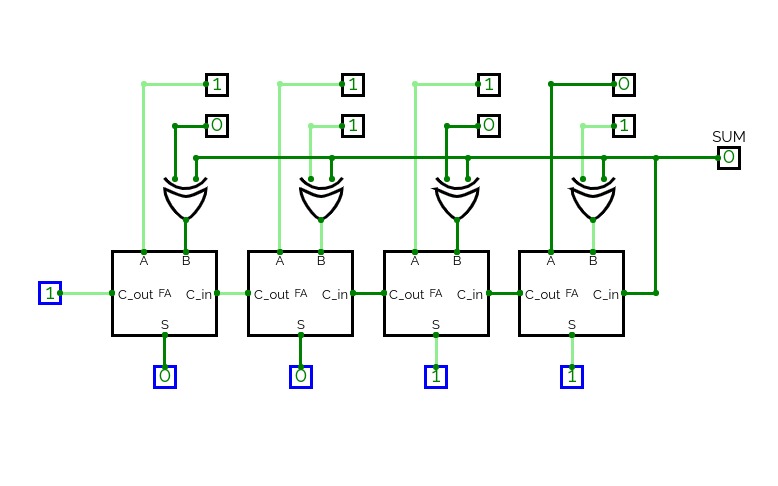

Ripple Carry Adder

Ripple Carry Adder

Keyboard

Keyboard

ALU

ALU

Recreating components using just not gates

Recreating components using just not gates

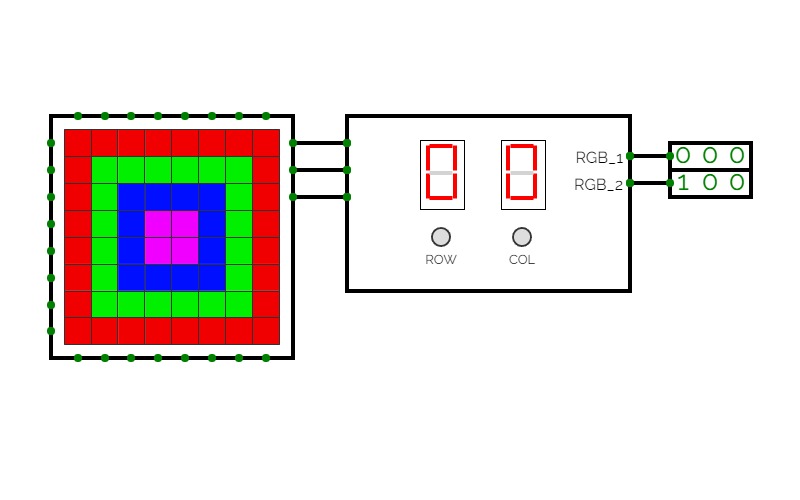

Midterm project(Moving Display)

Midterm project(Moving Display)

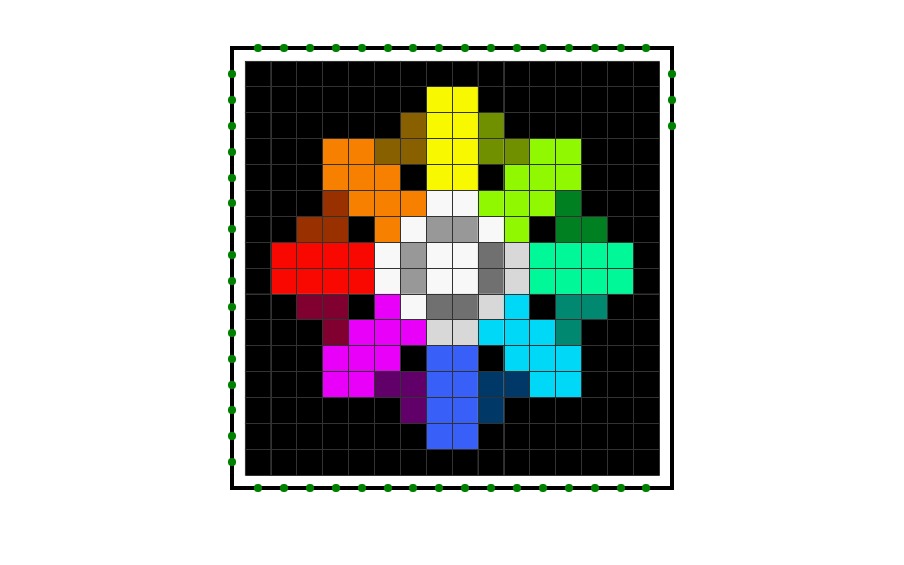

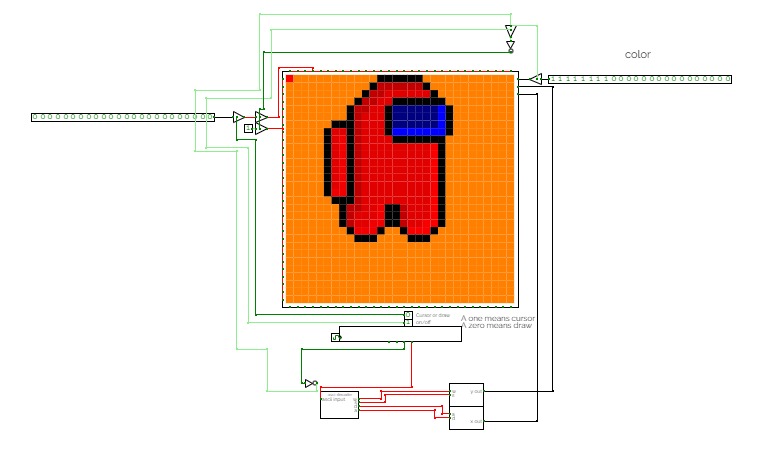

RGB LED Matrix

RGB LED Matrix

Binary Comparator [4-bit]

Binary Comparator [4-bit]

Addition, Subtraction and Multiplication Calculator

Addition, Subtraction and Multiplication Calculator

Encoder, Decoder, and 7-Segment Controller

Encoder, Decoder, and 7-Segment Controller

4-bit Calculator

4-bit Calculator

60 second timer

60 second timer

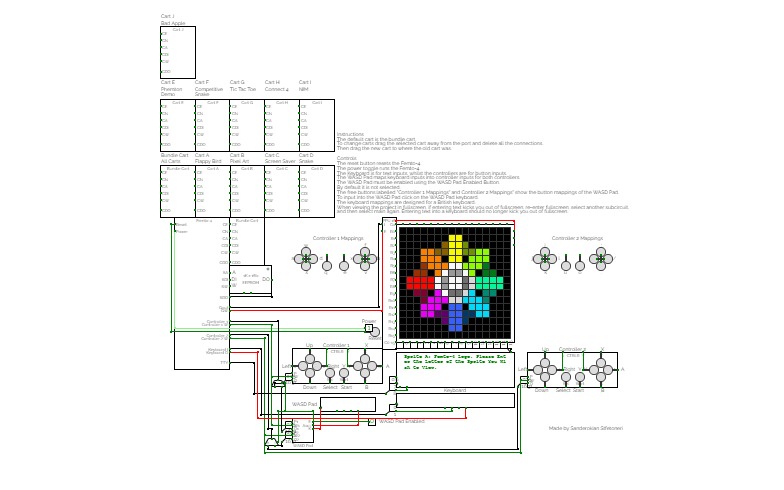

Play Roulette / Programmable Computer

Play Roulette / Programmable Computer

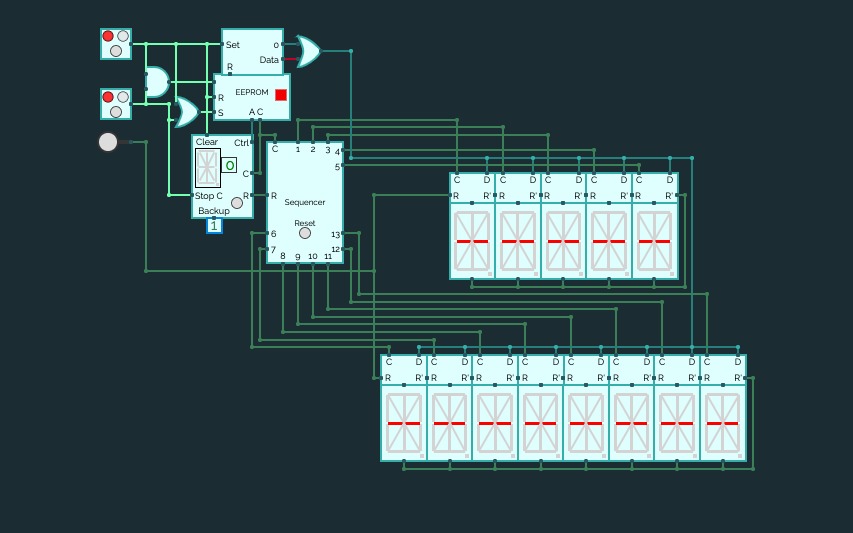

EEPROM Interactive Programmer

EEPROM Interactive Programmer

CPU Microprocessor

CPU Microprocessor

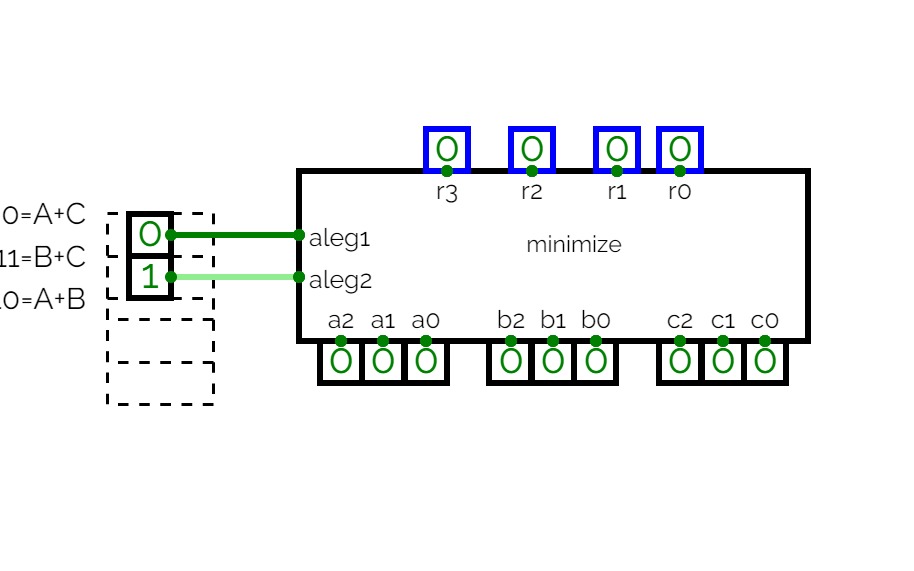

Magnitude Comparator

Magnitude Comparator

TestProject001

TestProject001

4-Bit Multiplication

4-Bit Multiplication

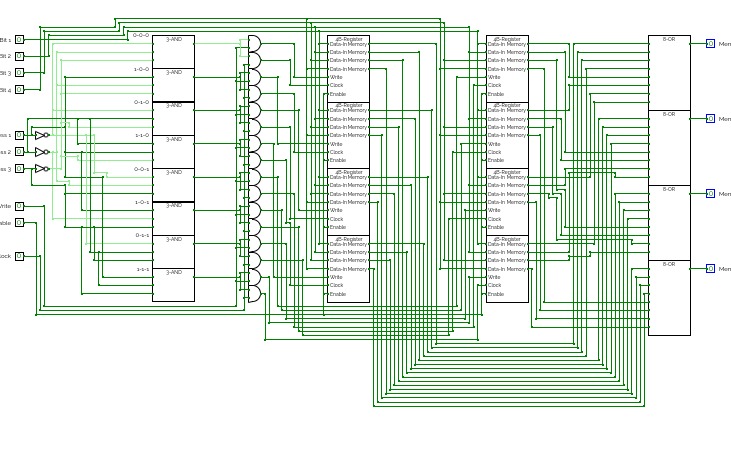

Static RAM

Static RAM

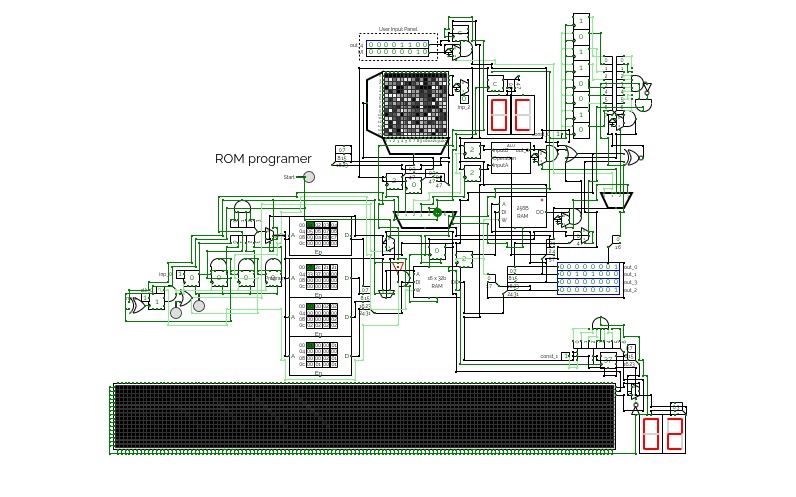

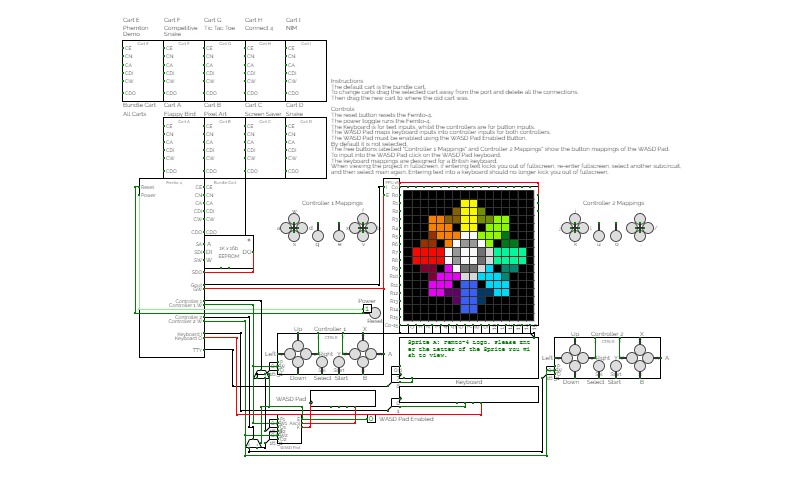

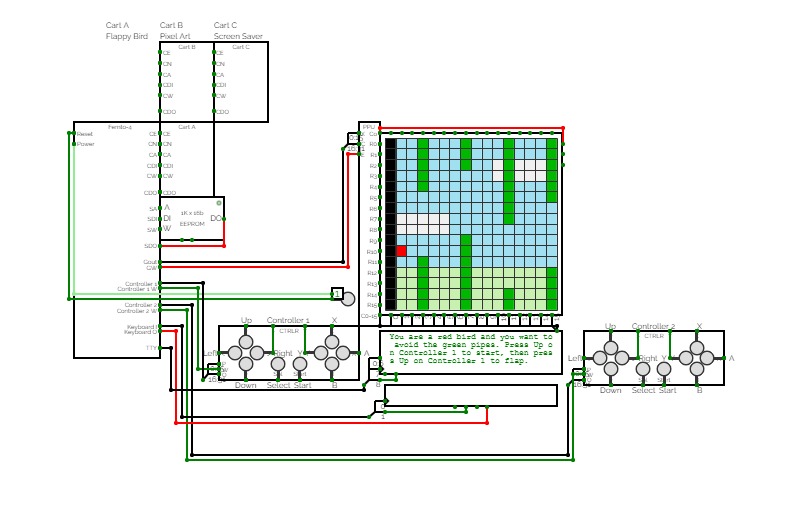

Femto-4v2.6 (Computer)

Femto-4v2.6 (Computer)

8 Bit CPU

8 Bit CPU

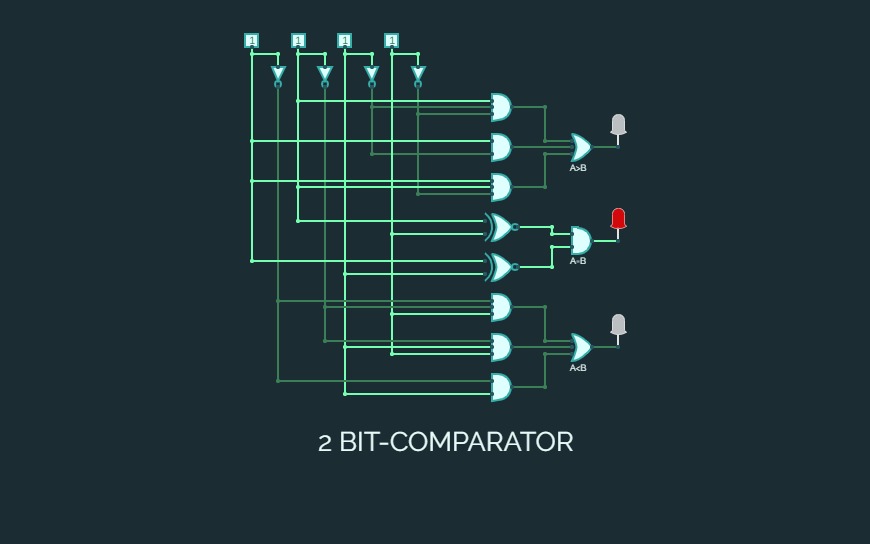

2 bit comparator using basic gates

2 bit comparator using basic gates

ALU parte 1

ALU parte 1

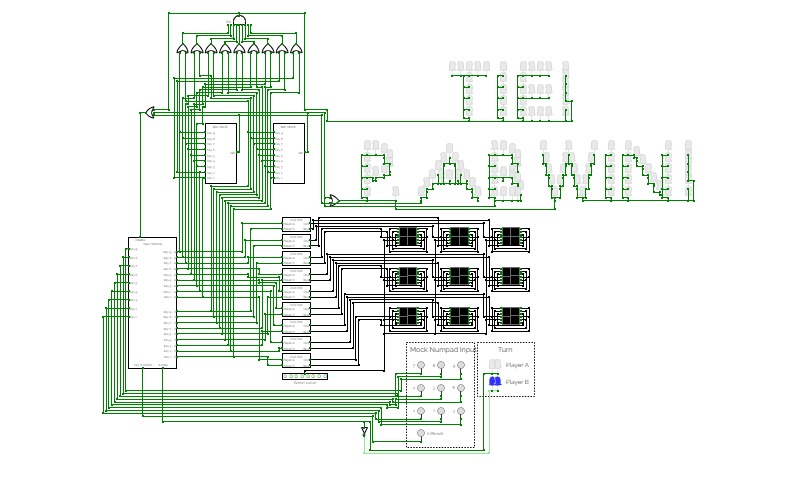

Tic tac toe Simulator

Tic tac toe Simulator

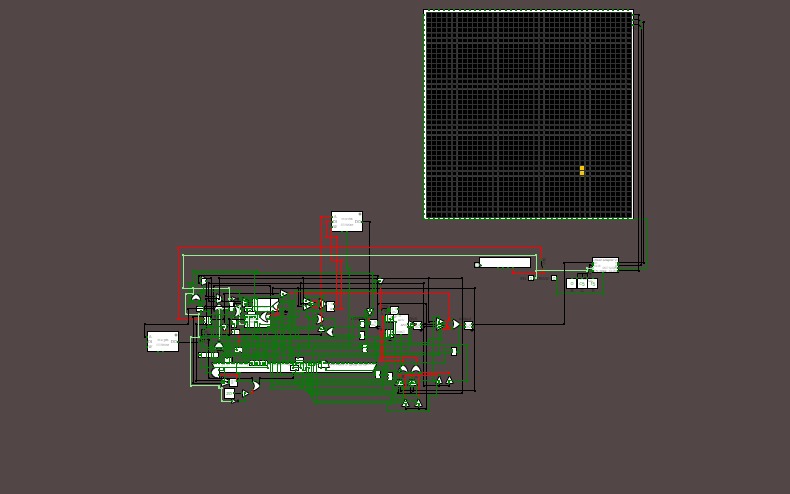

Basic GPU

Basic GPU

256-Series

256-Series

Asynchronous 16 - Segment Array

Asynchronous 16 - Segment Array

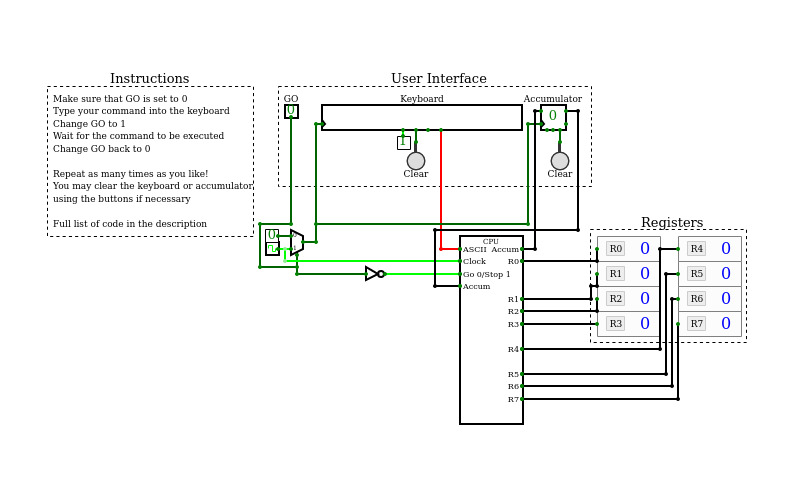

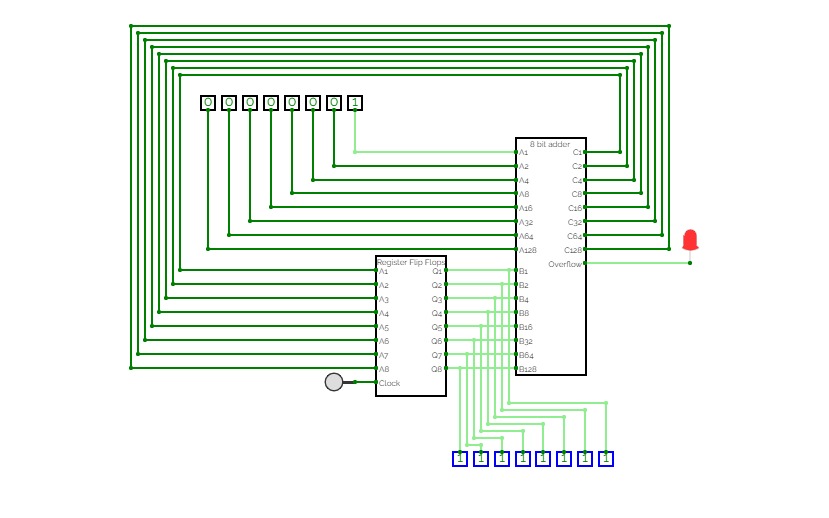

Accumulator Project

Accumulator Project

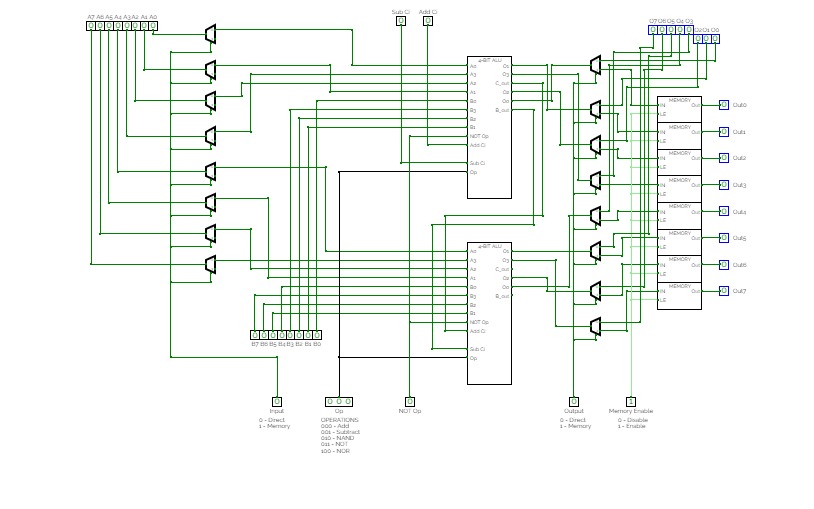

8 Bit ALU / Memory Main

8 Bit ALU / Memory Main

final circuit

final circuit

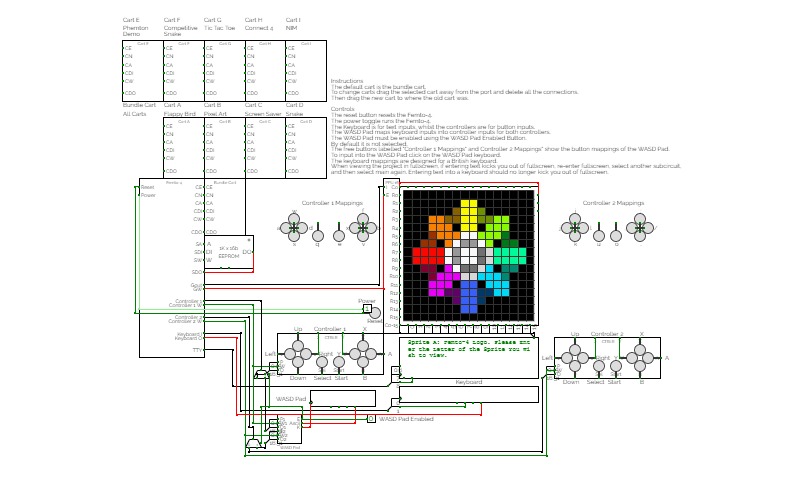

Femto-4v2.5 (Computer)

Femto-4v2.5 (Computer)

Femto-4v2.5 (Computer)

Femto-4v2.5 (Computer)

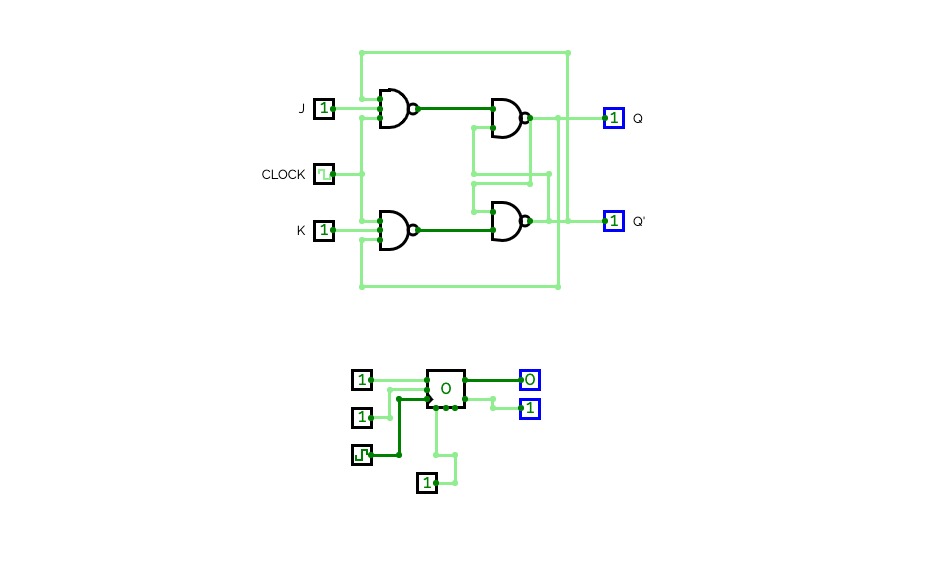

JK Flip flop

JK Flip flop

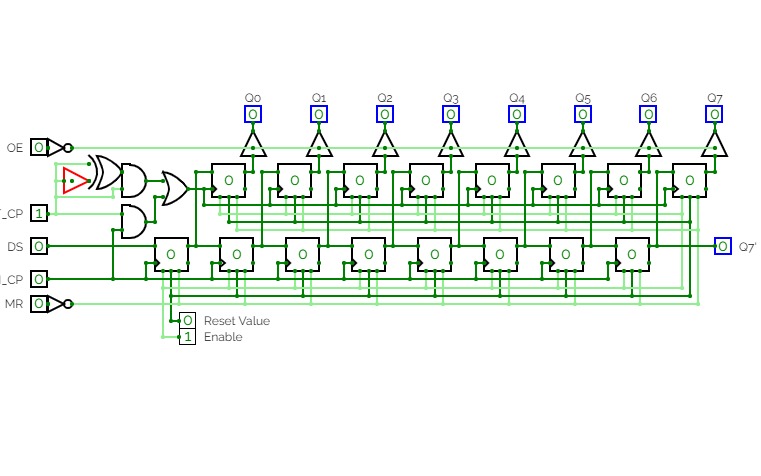

74HC595

74HC595

3 - BIT multiplication algorithum

3 - BIT multiplication algorithum

Femto-4v1.2 (Computer)

Femto-4v1.2 (Computer)

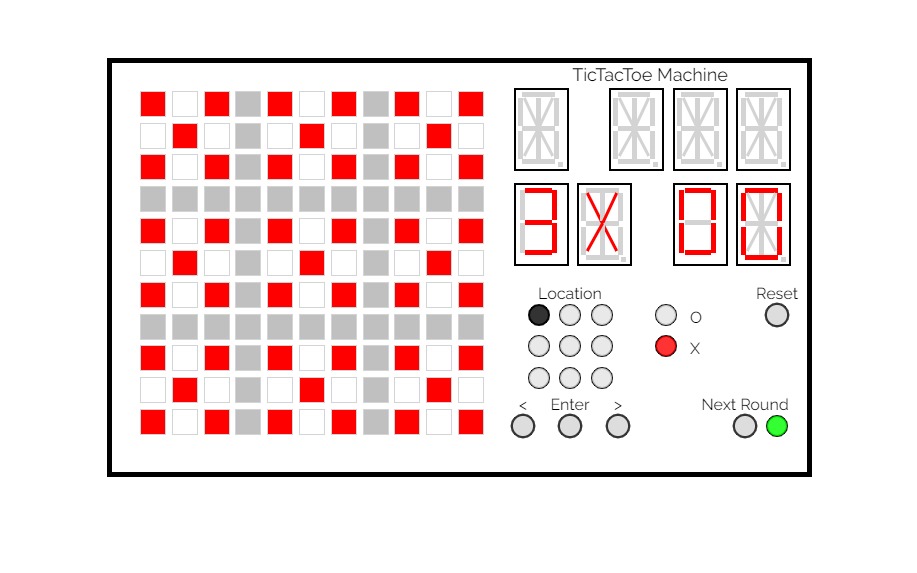

TicTacToe Machine

TicTacToe Machine

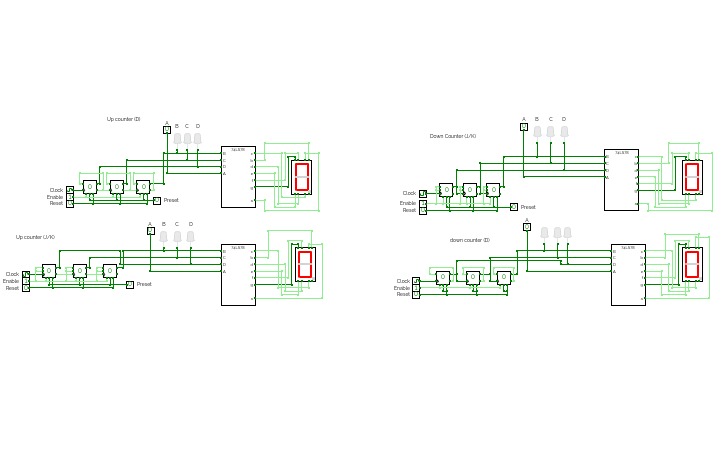

UpDownCounter

UpDownCounter

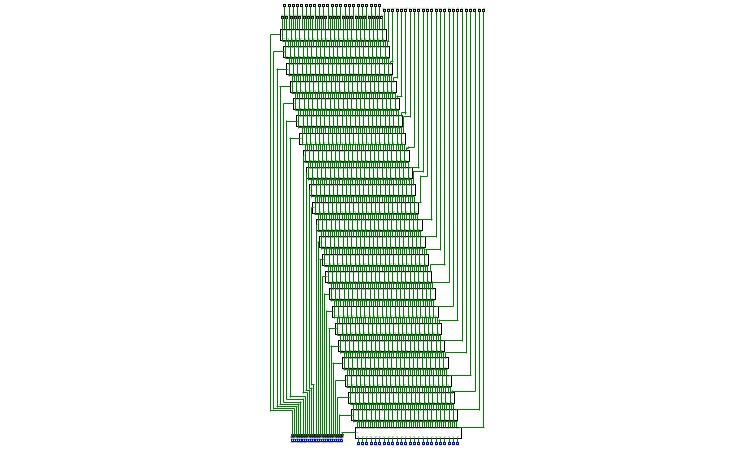

32-Bits RAM v0.1.50

32-Bits RAM v0.1.50

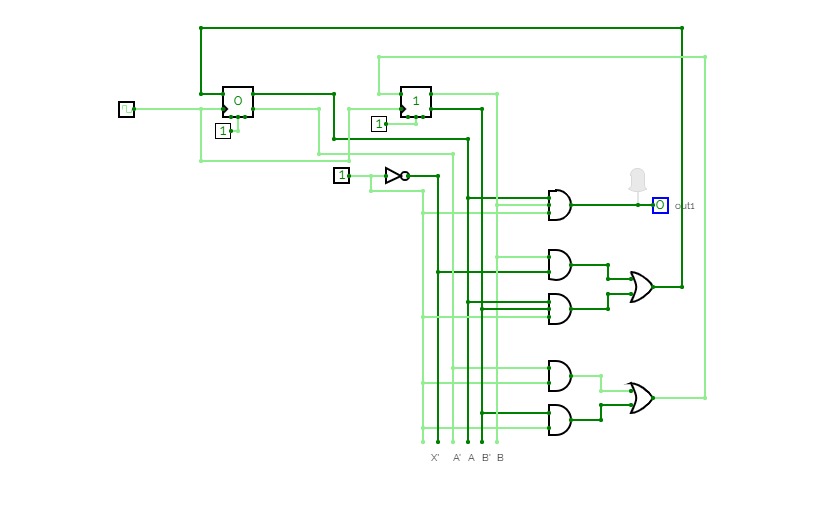

Find 1011 sequence

Find 1011 sequence

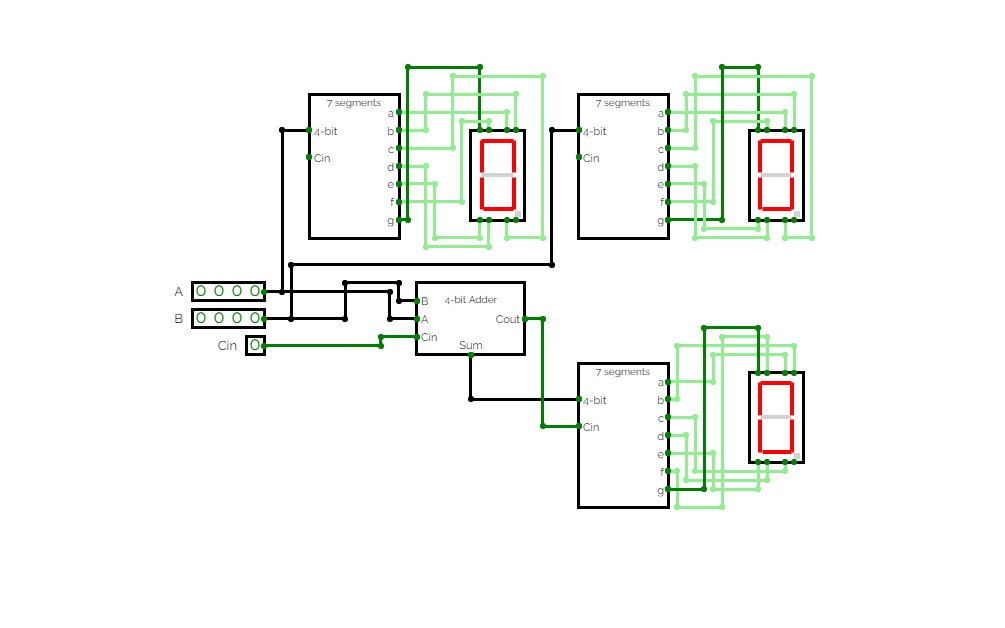

4-bit Adder num

4-bit Adder num

Afficher 8 bit

Afficher 8 bit

7-Segment Display Controller

7-Segment Display Controller

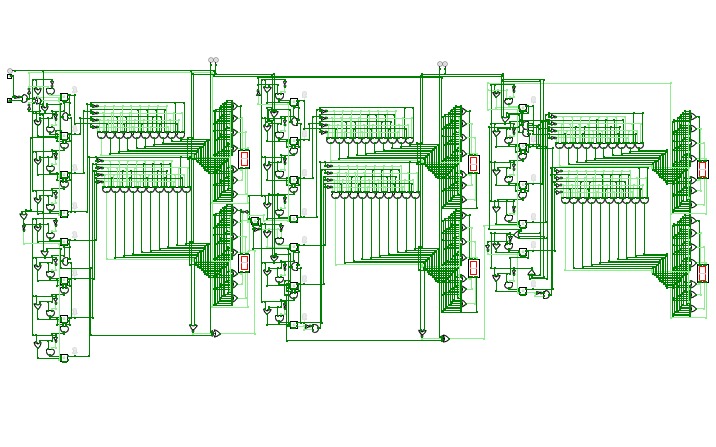

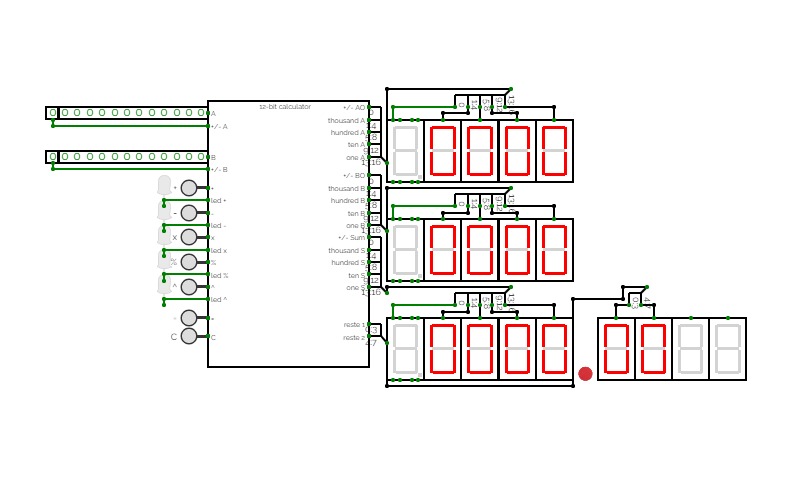

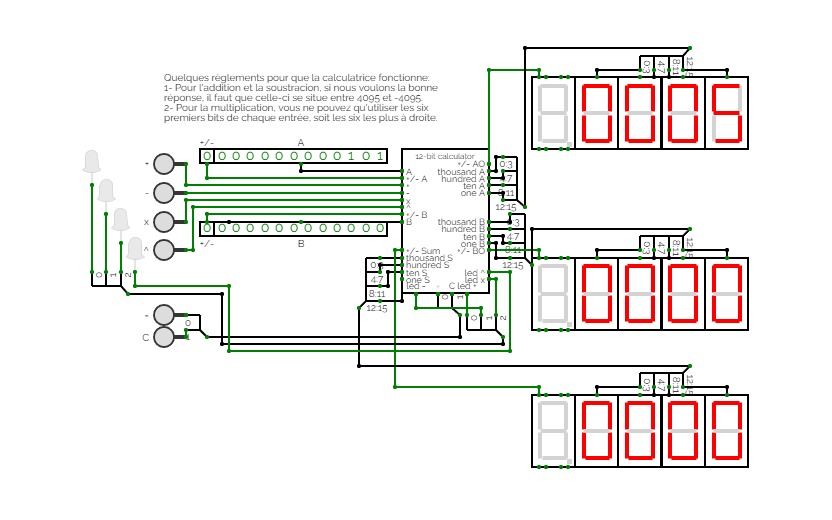

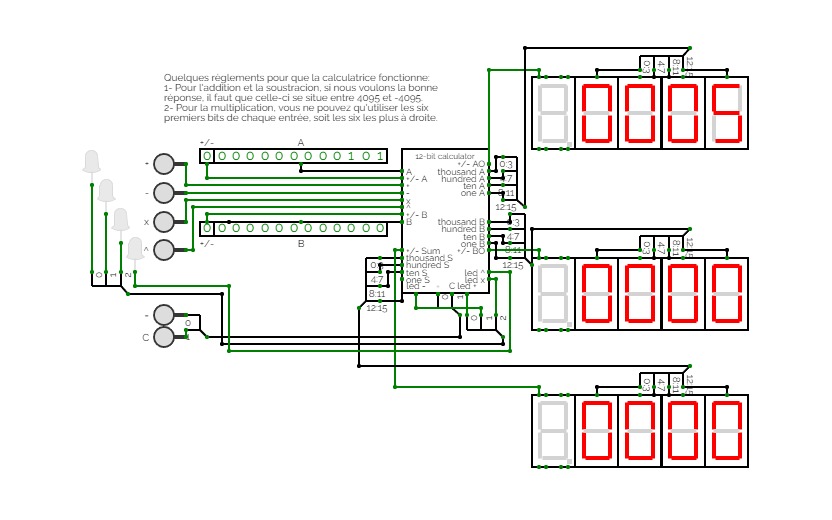

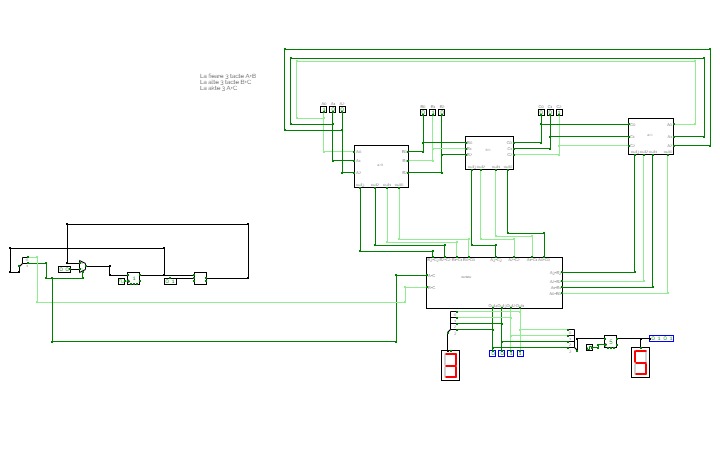

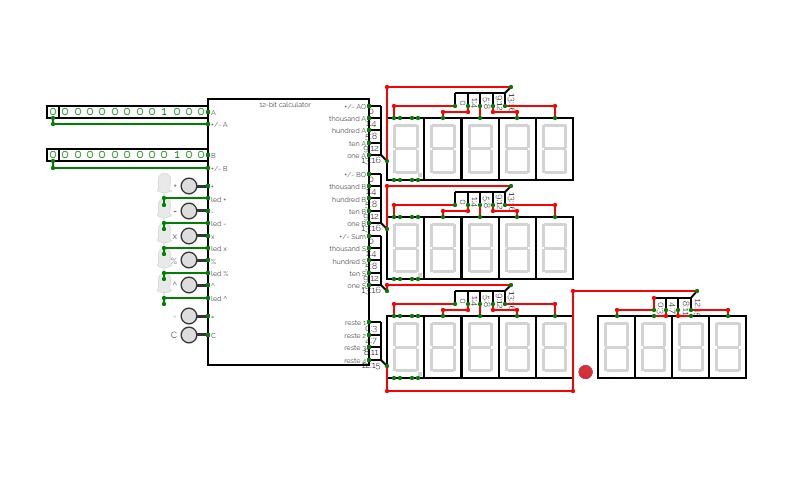

12-bit calculator

12-bit calculator

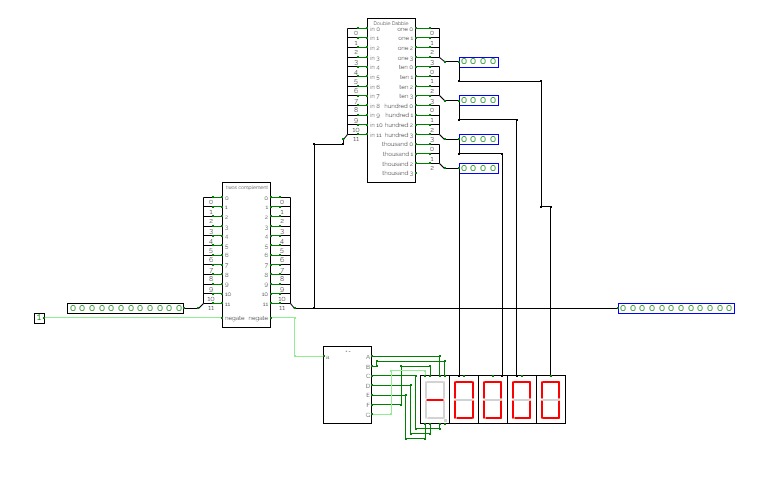

Twos complement

Twos complement

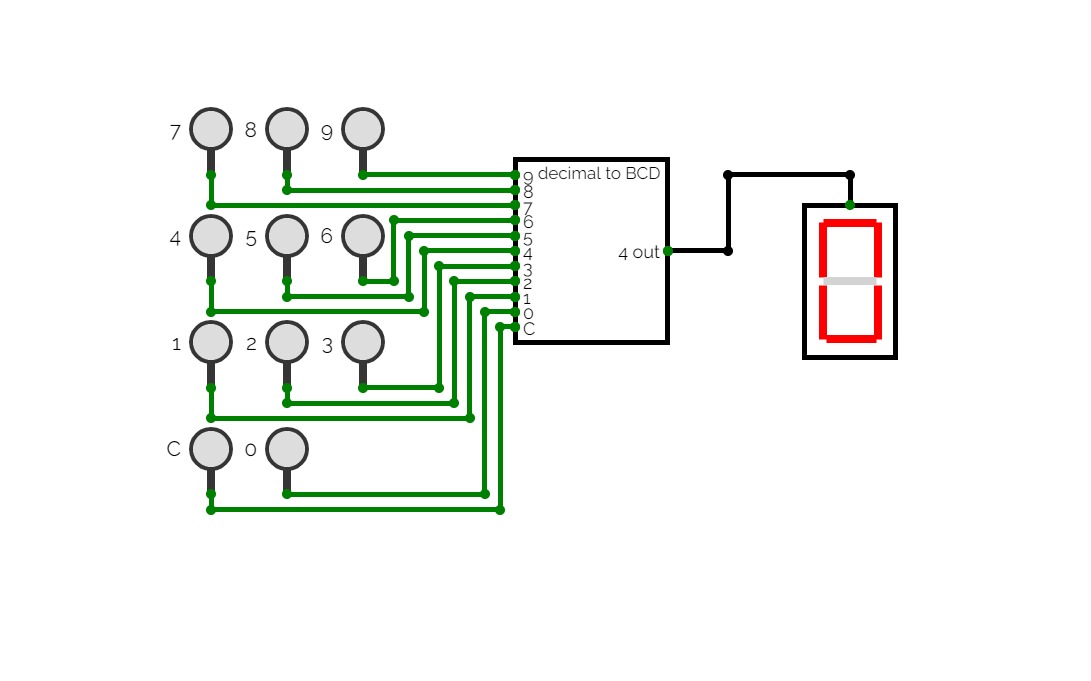

Decimal to BCD

Decimal to BCD

12-bit calculator

12-bit calculator

12-bit calculator sans div

12-bit calculator sans div

clock

clock

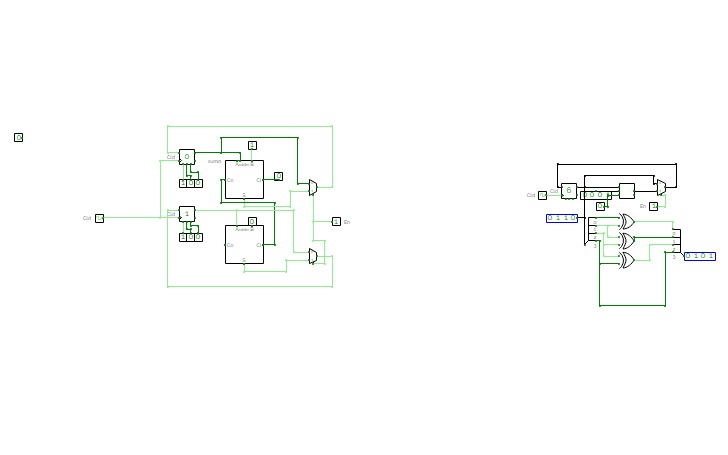

3.1.2 Flip Flop

3.1.2 Flip Flop

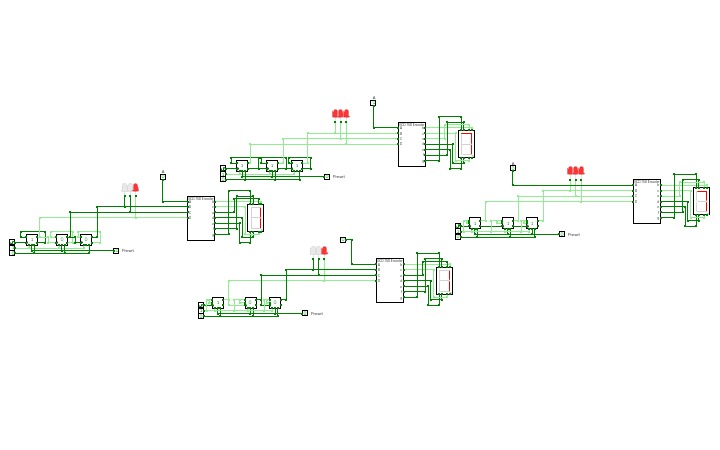

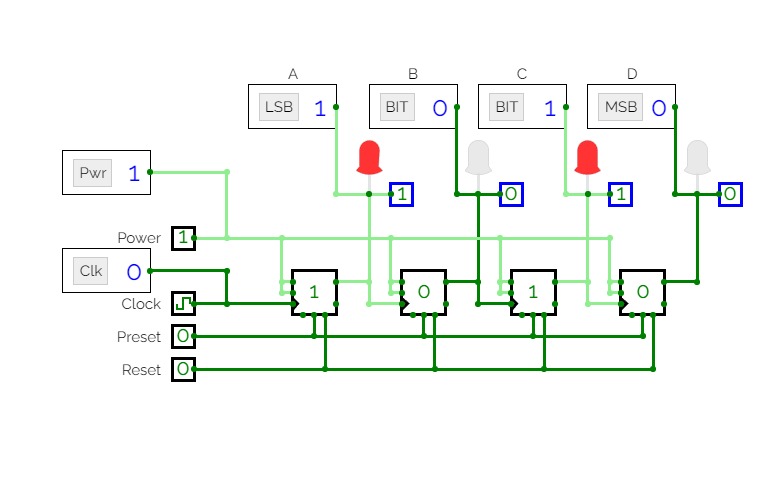

3.2.1 Asynch Counter

3.2.1 Asynch Counter

Tema25.04

Tema25.04

Tema marti 26.04

Tema marti 26.04

simple plotter circuit

simple plotter circuit

Sums and clocks

Sums and clocks

mod 16 ripple down counter

mod 16 ripple down counter

Division 24 bits

Division 24 bits

LAB 05

LAB 05

3.2.1 Asynchronous Counters

3.2.1 Asynchronous Counters

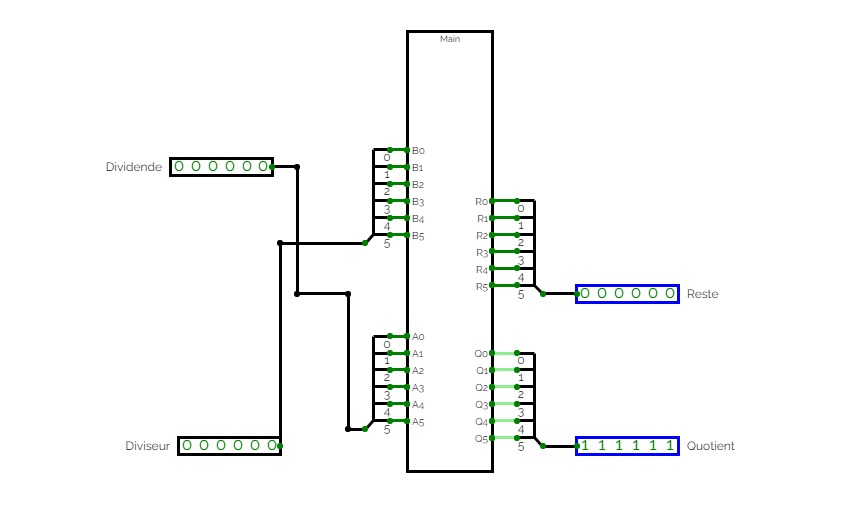

6-bits Divider

6-bits Divider

12bits calcu finale

12bits calcu finale

Adders

Adders

DEC hw7

DEC hw7

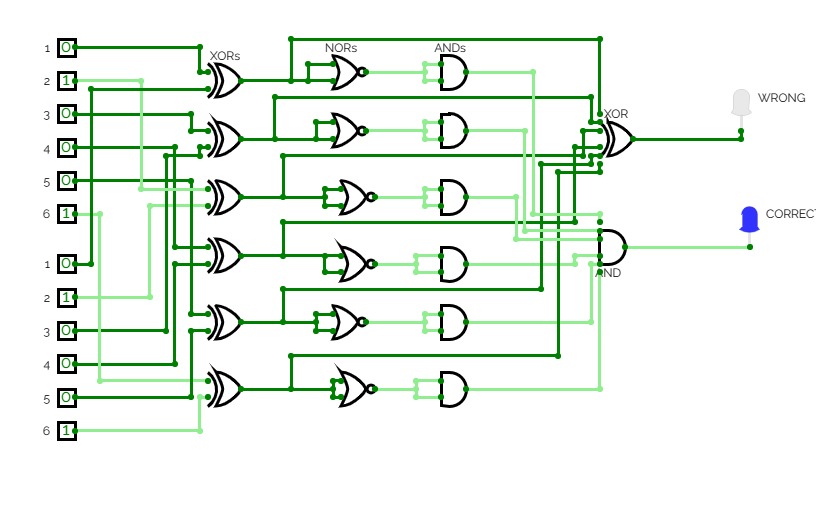

PASSWORD

PASSWORD

digital

digital

7 Segment Decoder

7 Segment Decoder

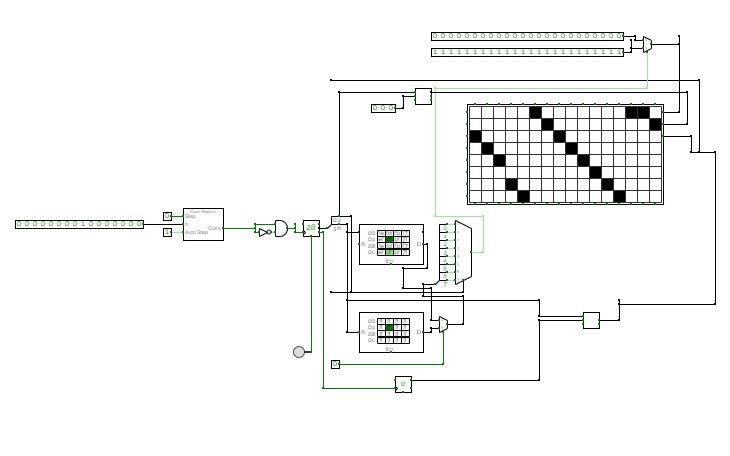

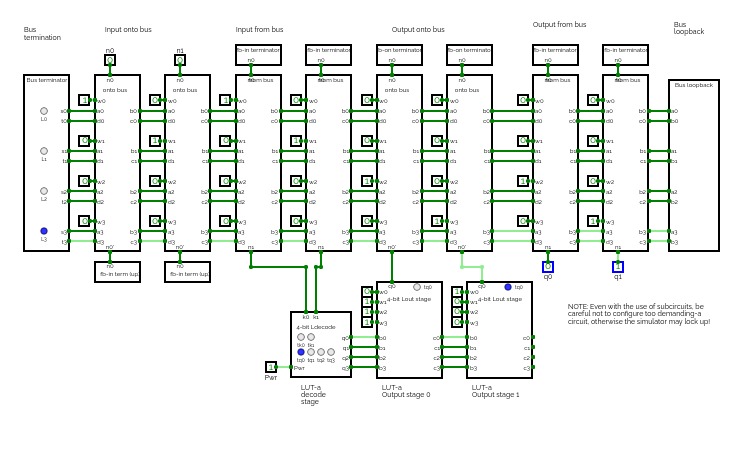

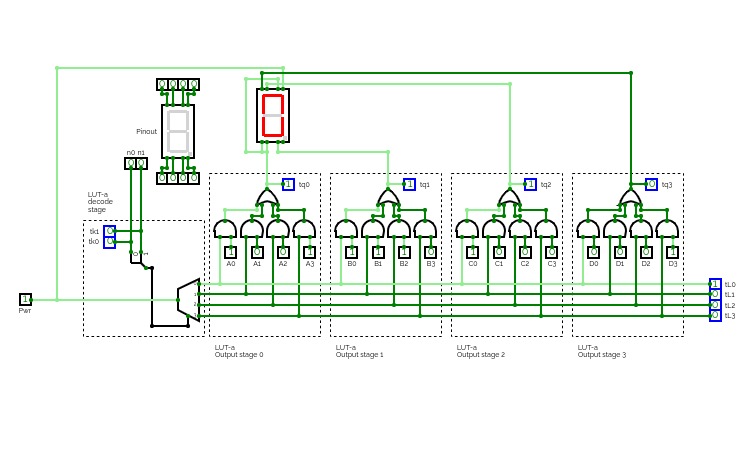

Modular FPGA with LUT and bus

Modular FPGA with LUT and bus

a look inside STRING2000C

a look inside STRING2000C

BCD LUT

BCD LUT

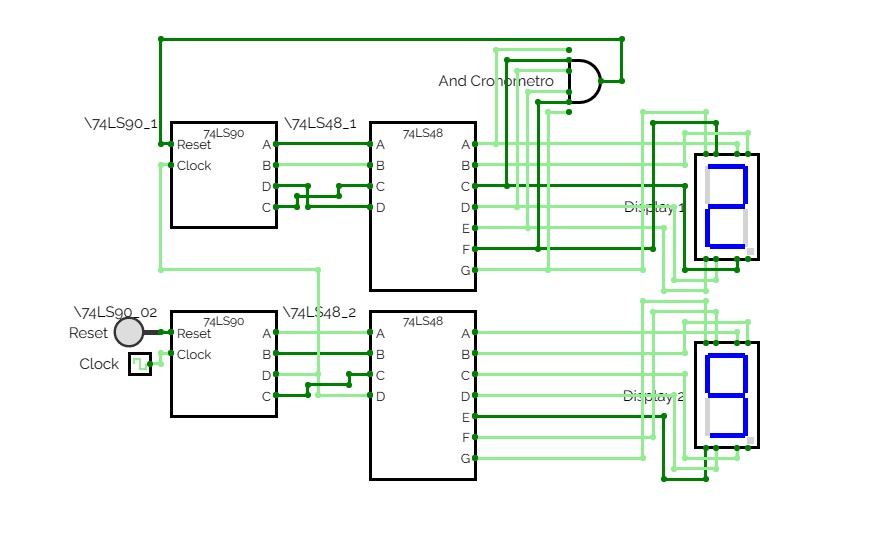

Cronometro

Cronometro

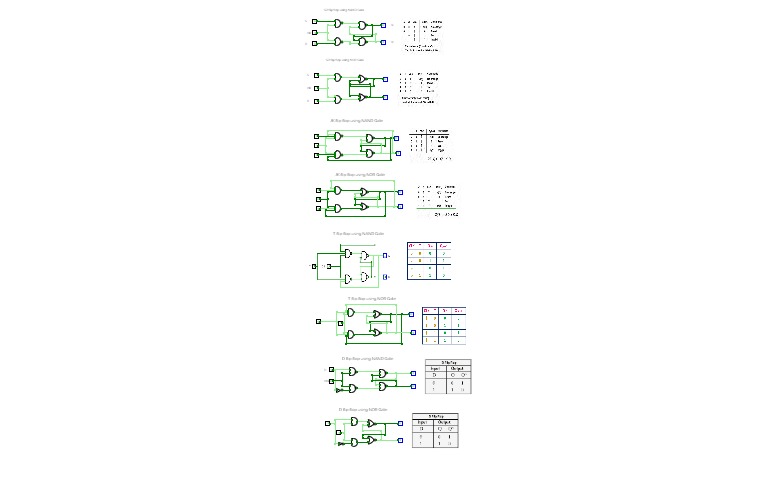

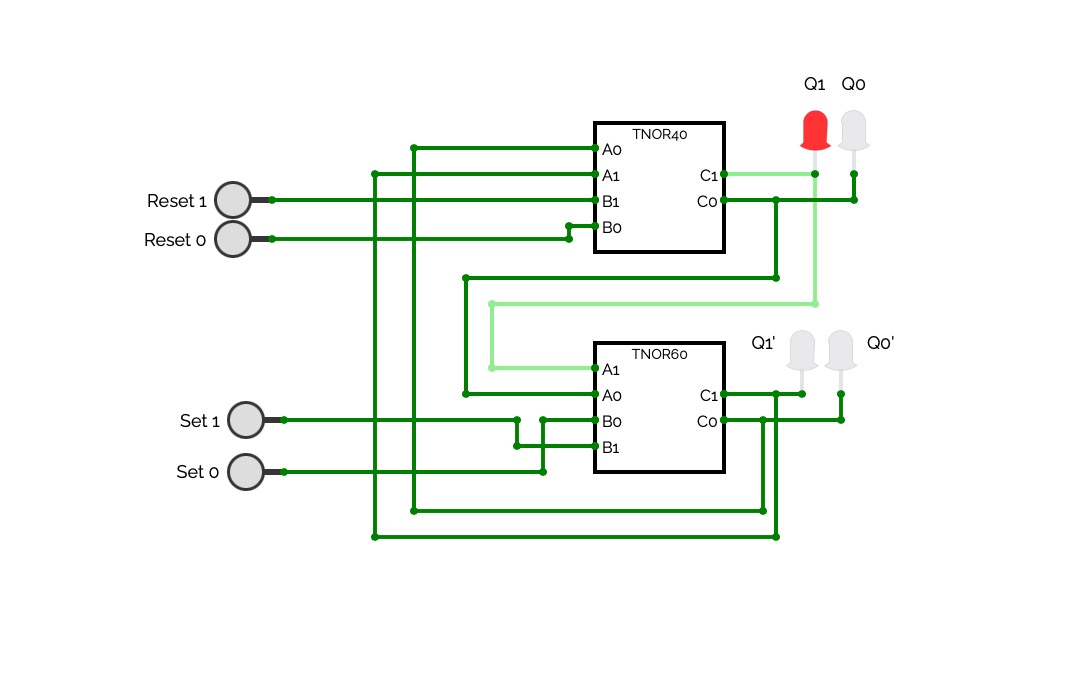

SR,JK,T,F FLIP FLOP Using NAND and NOR Gate

SR,JK,T,F FLIP FLOP Using NAND and NOR Gate

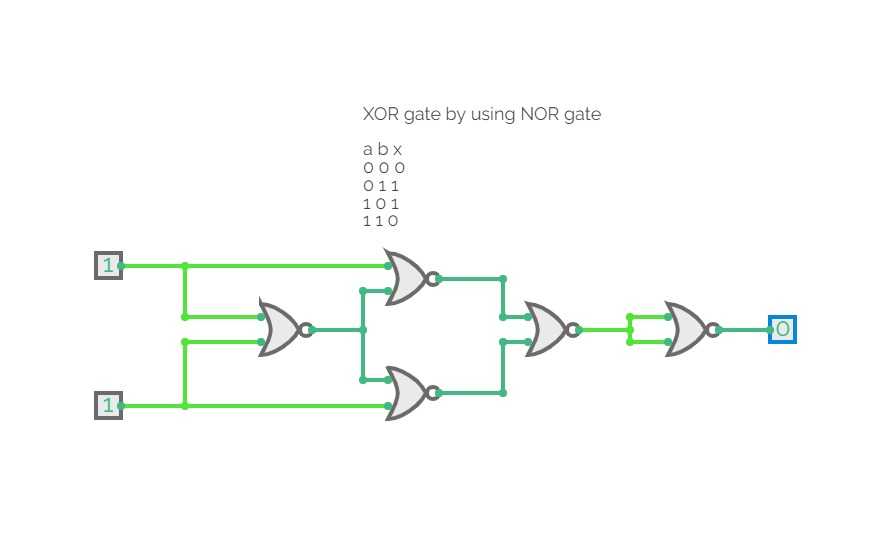

XOR gate by using NOR gate

XOR gate by using NOR gate

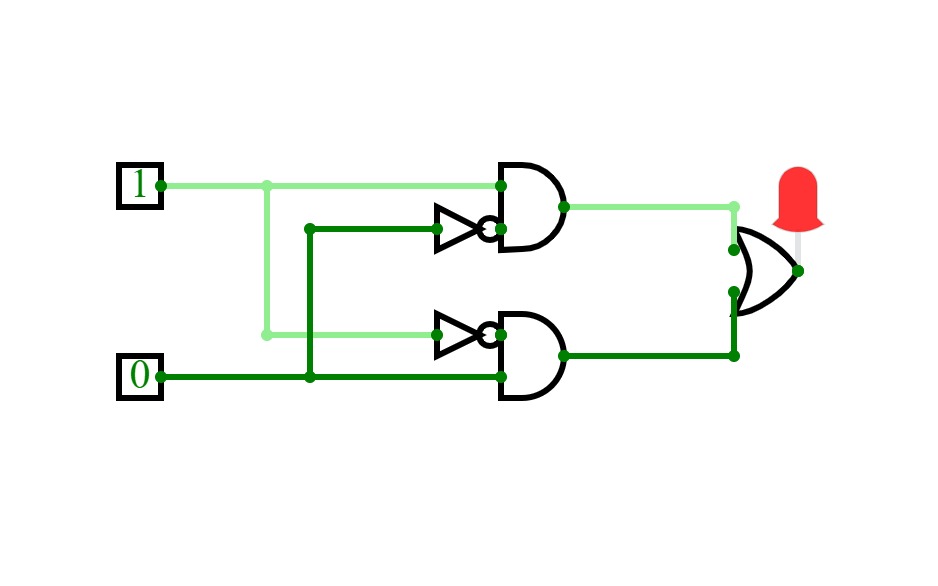

XOR Gate

XOR Gate

ED-2023_2-Lab1-Reto

ED-2023_2-Lab1-Reto

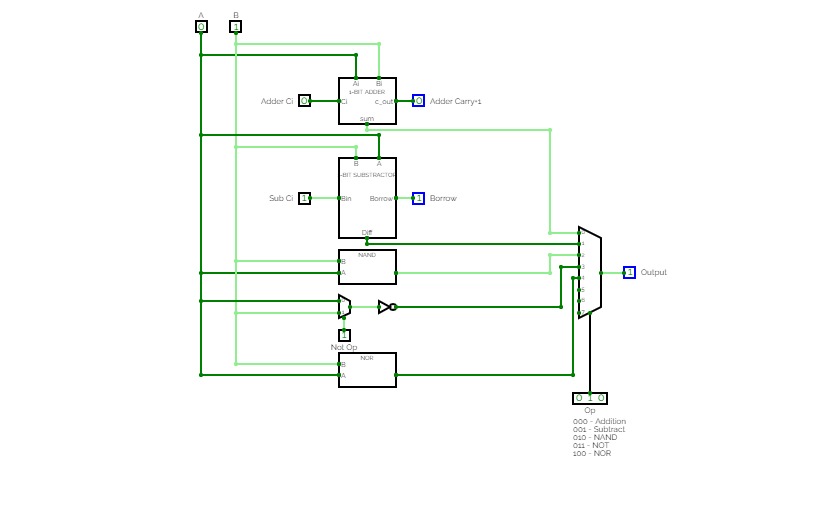

ALU

ALU

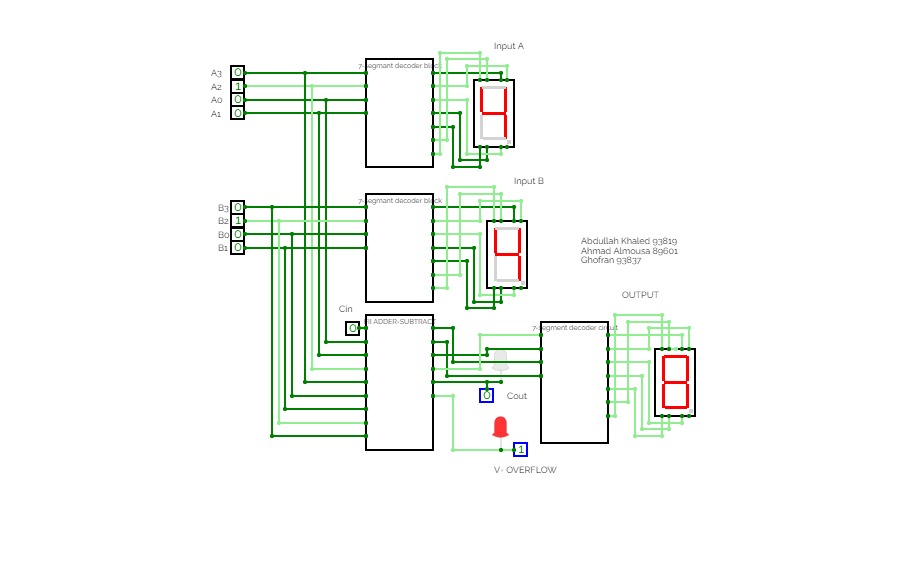

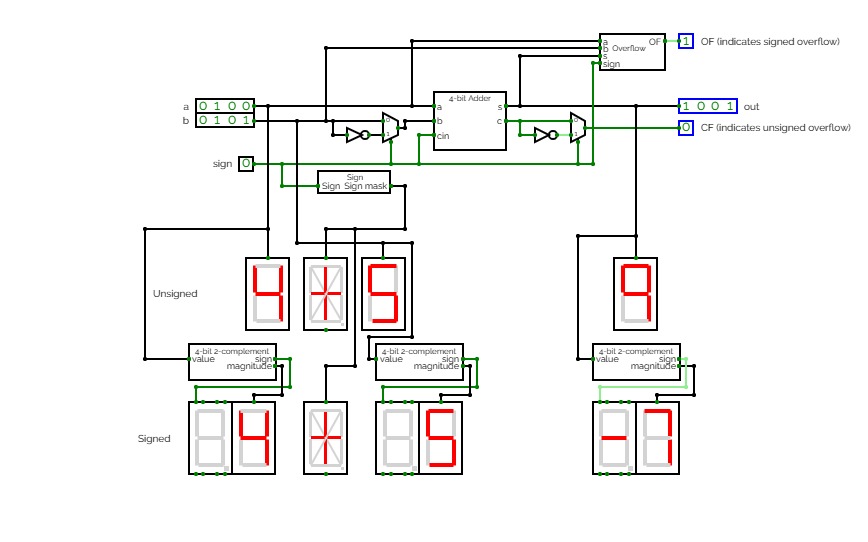

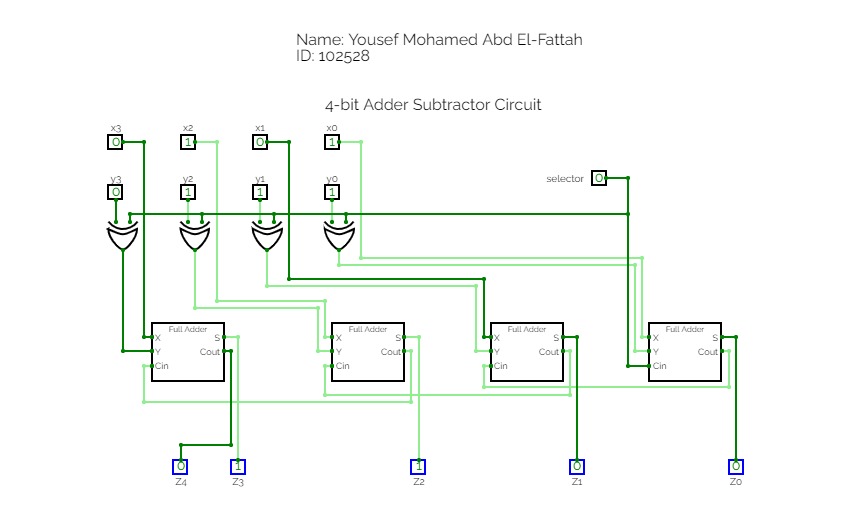

Adder subtractor Circuit detail explanation

Adder subtractor Circuit detail explanation

Lab 10

Lab 10

Subtracter

Subtracter

4 bit calculator

4 bit calculator