Modular FPGA with LUT and bus

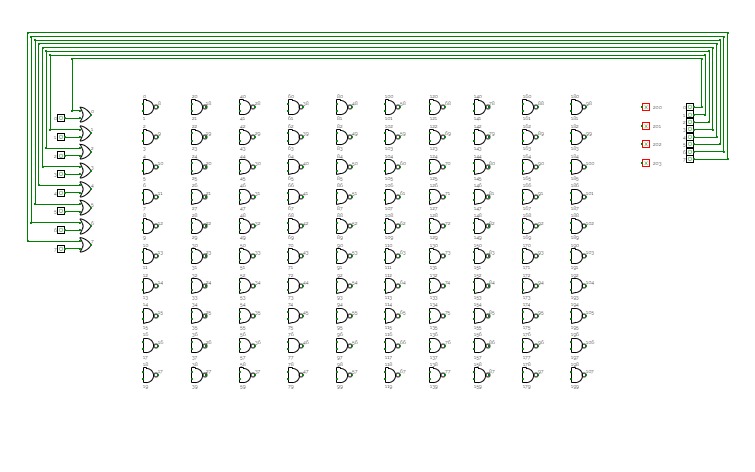

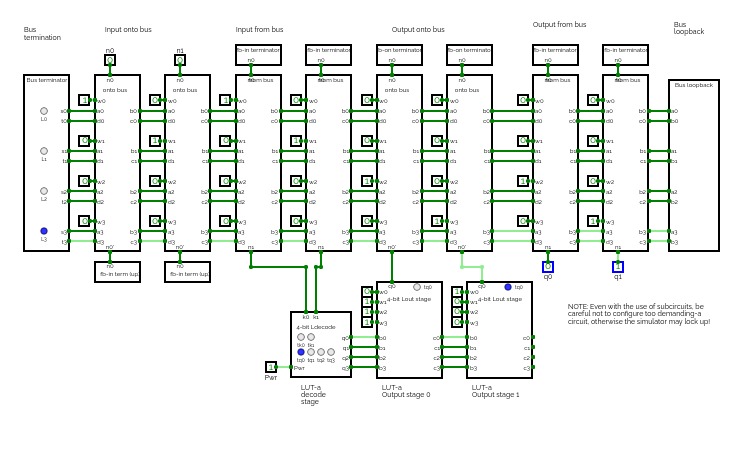

Modular FPGA with LUT and busA "trivial" FPGA, with two overall inputs, two overall outputs, and a 2/4 bit LUT with two output stages.

Forked from my non-modular version.

To fix previous issues with simulator capacity being exceeded, this modular version breaks the design up into subcircuits (as recommended). There are numerous repeating blocks, particularly within the bus. The bus modules are designed to easily be chained in both directions; both to increase the number of resources plugging into the bus, and the number of bus lines.

The number of bits was intended to increase... But even using modular construction, the simulator is still prone to overloading! I'm also seeing minor contention issues, presumably related to outputs being accidentally connected together. However, without more specific error messages, I am unable to determine where the error is. There's no error in my design; the trouble is adapting the design to the limitations of the simulator.