Keshav Kumar Jha

Member since: 3 years

Educational Institution: Not Entered

Country: India

even parity generator exp 13 a

even parity generator exp 13 a

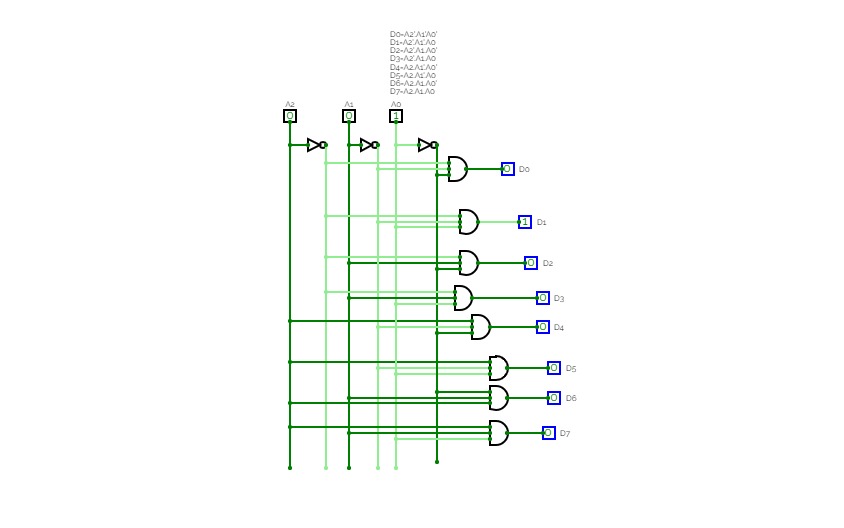

exp 19 Realization of the internal architecture of 3:8 Decoder using basic gates

exp 19 Realization of the internal architecture of 3:8 Decoder using basic gates

EXP 18 Realization of 4:2 Priority Encoder along with output indicator (Basic Gates).

EXP 18 Realization of 4:2 Priority Encoder along with output indicator (Basic Gates).

exp 11 full subtractor

exp 11 full subtractor

PARITY CHECKER exp 13 b

PARITY CHECKER exp 13 b

Full Subtractor

Full Subtractor

GRAY TO BINARY(EXP-5)

GRAY TO BINARY(EXP-5)

EXP 6(BCD to EXCESS 3)

EXP 6(BCD to EXCESS 3)

exp 2

exp 2

exp 3

exp 3

exp 16

exp 16

EXP 1 B

EXP 1 B

XOR using NOR

XOR using NOR

Experiment 9

Experiment 9

half subtractor exp 10

half subtractor exp 10

EXP 12FULL SUBTRACTOR USING TWO HALF SUBTRACTOR

EXP 12FULL SUBTRACTOR USING TWO HALF SUBTRACTOR

4:1 MUX exp 15 a

4:1 MUX exp 15 a

FULL ADDER(EXP-8B)

FULL ADDER(EXP-8B)

HALF ADDER(EXP-8A)

HALF ADDER(EXP-8A)

1:4DEMUX(EXP-15B)

1:4DEMUX(EXP-15B)

s flip flop nand gate(EXP 22)

s flip flop nand gate(EXP 22)

t flip flop nand gate(EXP 24)

t flip flop nand gate(EXP 24)

SISO

SISO

NOT USING NAND

NOT USING NAND

NOT USING NOR

NOT USING NOR

AND USING NAND

AND USING NAND

SIPO

SIPO

AND USING NOR

AND USING NOR

XOR USING NAND

XOR USING NAND

OR USING NAND

OR USING NAND

4:1 MUX EXP 15 A

4:1 MUX EXP 15 A

pipo

pipo

2-BIT COMPARATOR exp 14

2-BIT COMPARATOR exp 14

2-BIT COMPARATOR EXP 14

2-BIT COMPARATOR EXP 14

parity 12

parity 12

BINARY TO GRAY(EXP-4)

BINARY TO GRAY(EXP-4)

SR flip flop nand gate (EXP 21)

SR flip flop nand gate (EXP 21)

EXP 7(EXCESS-3 TO BCD)

EXP 7(EXCESS-3 TO BCD)

octal to binary (EXP 20)

octal to binary (EXP 20)

OR USING NOR

OR USING NOR

(Exp 16) Implementation of Full Adder using MUX IC 4539B (4:1 MUX)

(Exp 16) Implementation of Full Adder using MUX IC 4539B (4:1 MUX)

4 bit Synchronous DOWN Counter

4 bit Synchronous DOWN Counter

EXP 12 FULL SUBTRACTOR USING TWO HALF SUBTRACTOR

EXP 12 FULL SUBTRACTOR USING TWO HALF SUBTRACTOR

1-BIT COMPARATOR

1-BIT COMPARATOR

4-Bit Synchronous Up Counter

4-Bit Synchronous Up Counter

jk flip flop nand gate(EXP 23)

jk flip flop nand gate(EXP 23)

(Exp 17)Implementation of Full Subtractor using MUX IC 4539B (4:1 MUX).

(Exp 17)Implementation of Full Subtractor using MUX IC 4539B (4:1 MUX).