Shashank Chowdhury

Member since: 3 years

Educational Institution: Kalasalingam university

Country: India

PISO SHIFT REGISTER

PISO SHIFT REGISTER

MUX 1:4

MUX 1:4

demux 1:4

demux 1:4

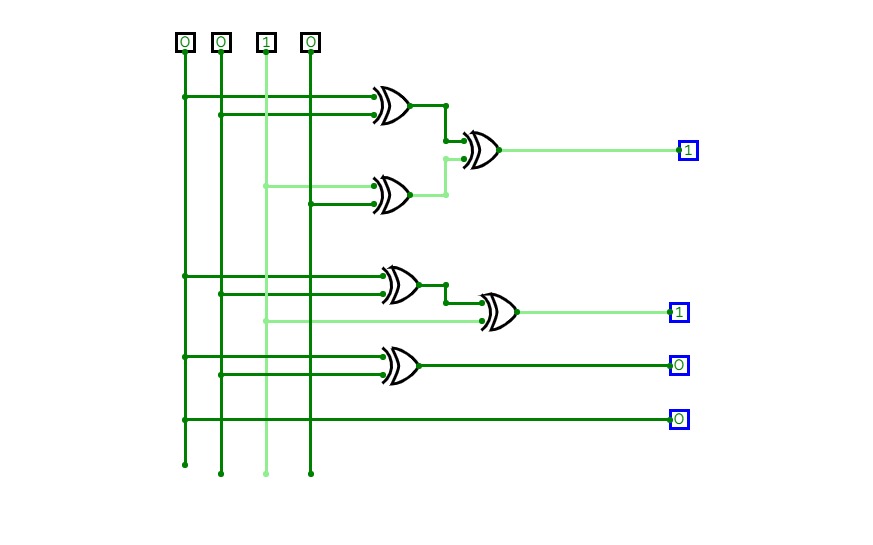

Encoder

Encoder

decoder

decoder

parity generator

parity generator

parity check

parity check

Flip Flops

Flip Flops

2 bit magnitude comparator

2 bit magnitude comparator

Binary to Grey And Grey to Binary

Binary to Grey And Grey to Binary

Parallel in Parallel Out Shift Register

Parallel in Parallel Out Shift Register

Counter

Counter

4-bit ripple counter

4-bit ripple counter

Full adder using NAND Gate

Full adder using NAND Gate

Binary to excess 3

Binary to excess 3

half Subtractor

half Subtractor

JK flip flop using NAND and NOR

JK flip flop using NAND and NOR

Logic Gates

Logic Gates

1 bit magnitude comparator

1 bit magnitude comparator

half adder using nand gates

half adder using nand gates

Flip-Flops using NAND Gate

Flip-Flops using NAND Gate

8:1 Mux using Logic Gates

8:1 Mux using Logic Gates

Serial In Serial Out Shift Register - D flip flop

Serial In Serial Out Shift Register - D flip flop

Flip-Flops

Flip-Flops

SERIAL IN PARALLEL OUT SHIFT REGISTER

SERIAL IN PARALLEL OUT SHIFT REGISTER

Flip-Flops

Flip-Flops

Half adder and full adder

Half adder and full adder

EX.NO:1 Implementation of Logic Gates

EX.NO:1 Implementation of Logic Gates

binary to gray

binary to gray

1:8 mux

1:8 mux

Ring and Johnson Counter

Ring and Johnson Counter