Srijeet Roy

Member since: 3 years

Educational Institution: UEM, Kolkata

Country: India

BINARY TO GRAY(EXP-4)

BINARY TO GRAY(EXP-4)

GRAY TO BINARY(EXP-5)

GRAY TO BINARY(EXP-5)

EXP 6(BCD to EXCESS 3)

EXP 6(BCD to EXCESS 3)

Half subtractor(EXP-10)

Half subtractor(EXP-10)

FULL ADDER(EXP-8B)

FULL ADDER(EXP-8B)

HALF ADDER(EXP-8A)

HALF ADDER(EXP-8A)

1:4DEMUX(EXP-15B)

1:4DEMUX(EXP-15B)

SISO

SISO

AND USING NOR

AND USING NOR

OR USING NAND

OR USING NAND

OR USING NOR

OR USING NOR

NOT USING NOR

NOT USING NOR

AND USING NAND(EXP-1A)

AND USING NAND(EXP-1A)

NOT USING NAND

NOT USING NAND

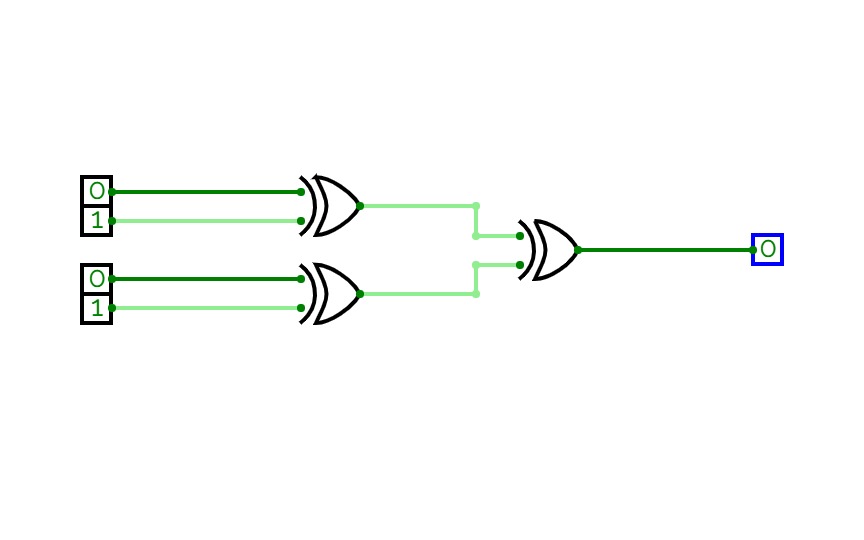

XOR USING NAND

XOR USING NAND

XOR using NOR

XOR using NOR

exp 2

exp 2

exp 3

exp 3

4-Bit Synchronous Up Counter

4-Bit Synchronous Up Counter

PARITY CHECKER exp 13 b

PARITY CHECKER exp 13 b

Experiment 9

Experiment 9

exp 11 full subtractor

exp 11 full subtractor

4:1 MUX exp 15 a

4:1 MUX exp 15 a

jk flip flop nand gate(EXP 23)

jk flip flop nand gate(EXP 23)

D flip flop nand gate(EXP 22)

D flip flop nand gate(EXP 22)

octal to binary (EXP 20)

octal to binary (EXP 20)

SR flip flop nand gate (EXP 21)

SR flip flop nand gate (EXP 21)

t flip flop nand gate(EXP 24)

t flip flop nand gate(EXP 24)

EXP 12 FULL SUBTRACTOR USING TWO HALF SUBTRACTOR

EXP 12 FULL SUBTRACTOR USING TWO HALF SUBTRACTOR

Untitled

Untitled

4 bit Synchronous DOWN Counter

4 bit Synchronous DOWN Counter

PAIRITY CHECKING

PAIRITY CHECKING

FULL SUBTRACTOR USING 4:1 MUX_EXP 17

FULL SUBTRACTOR USING 4:1 MUX_EXP 17

EXP 7(EXCESS-3 TO BCD)

EXP 7(EXCESS-3 TO BCD)

2-BIT COMPARATOR exp 14

2-BIT COMPARATOR exp 14

Untitled

Untitled

XOR USING NAND

XOR USING NAND

SIPO

SIPO

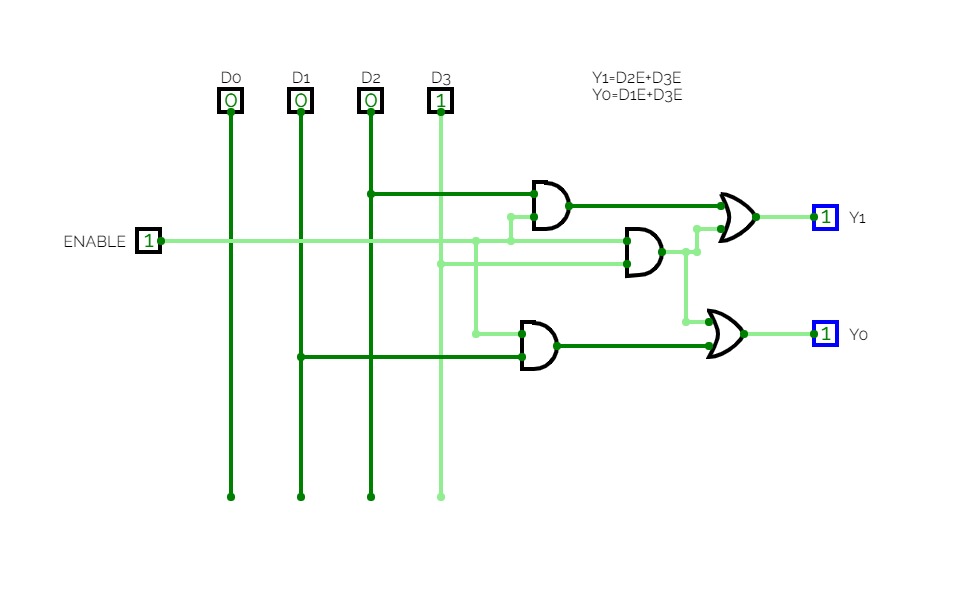

4:2 PRIORITY ENCODER(EXP-18)

4:2 PRIORITY ENCODER(EXP-18)

even parity generator exp 13 a

even parity generator exp 13 a

EXP 1 B

EXP 1 B

(Exp 17)Implementation of Full Subtractor using MUX IC 4539B (4:1 MUX).

(Exp 17)Implementation of Full Subtractor using MUX IC 4539B (4:1 MUX).

exp 19 Realization of the internal architecture of 3:8 Decoder using basic gates

exp 19 Realization of the internal architecture of 3:8 Decoder using basic gates

Full Subtractor using 4:1 MUX

Full Subtractor using 4:1 MUX

(Exp 16) Implementation of Full Adder using MUX IC 4539B (4:1 MUX)

(Exp 16) Implementation of Full Adder using MUX IC 4539B (4:1 MUX)