Arindam Ghosh

Member since: 3 years

Educational Institution: University of engineering and management

Country: India

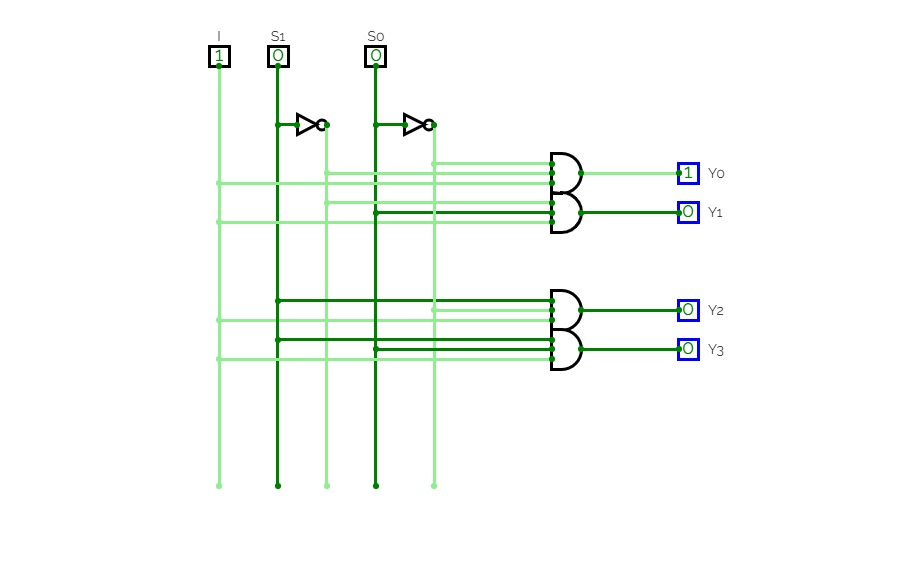

1:4 De-MUX

1:4 De-MUX

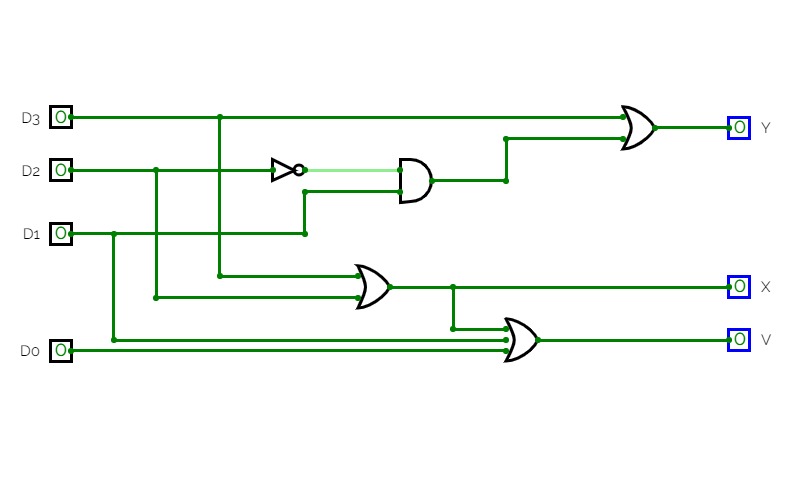

4:2 Priority Encoder

4:2 Priority Encoder

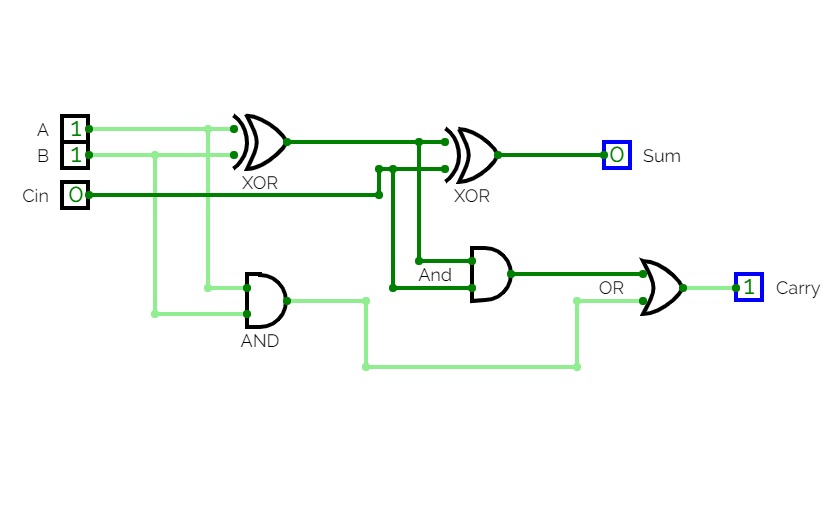

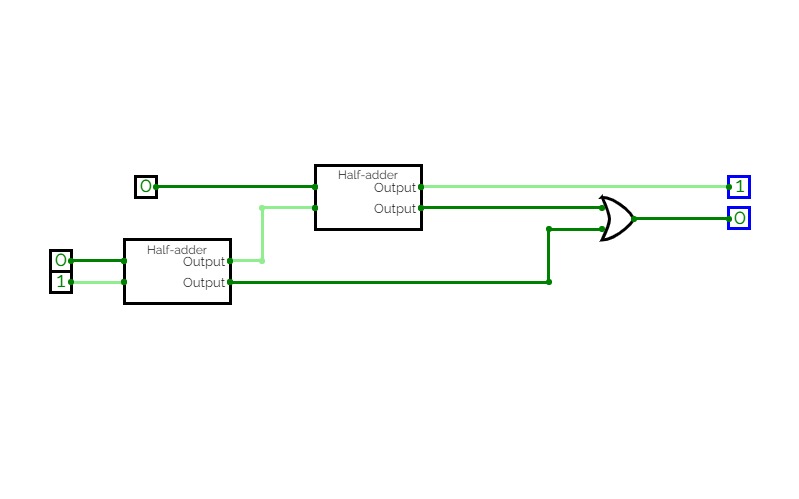

Full Adder Using Two Half Adder and an OR Gate

Full Adder Using Two Half Adder and an OR Gate

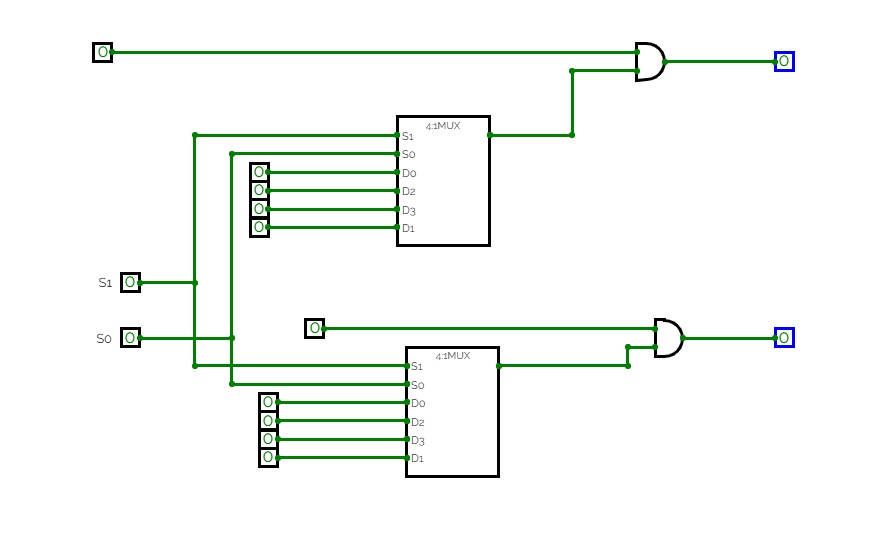

Implementation of Full Adder Using MUX IC 4539B.

Implementation of Full Adder Using MUX IC 4539B.

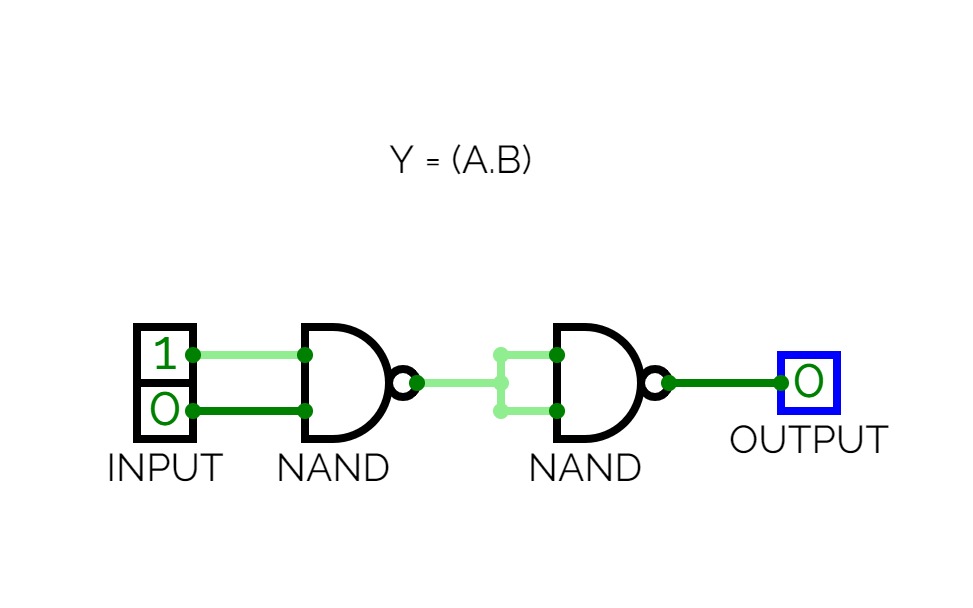

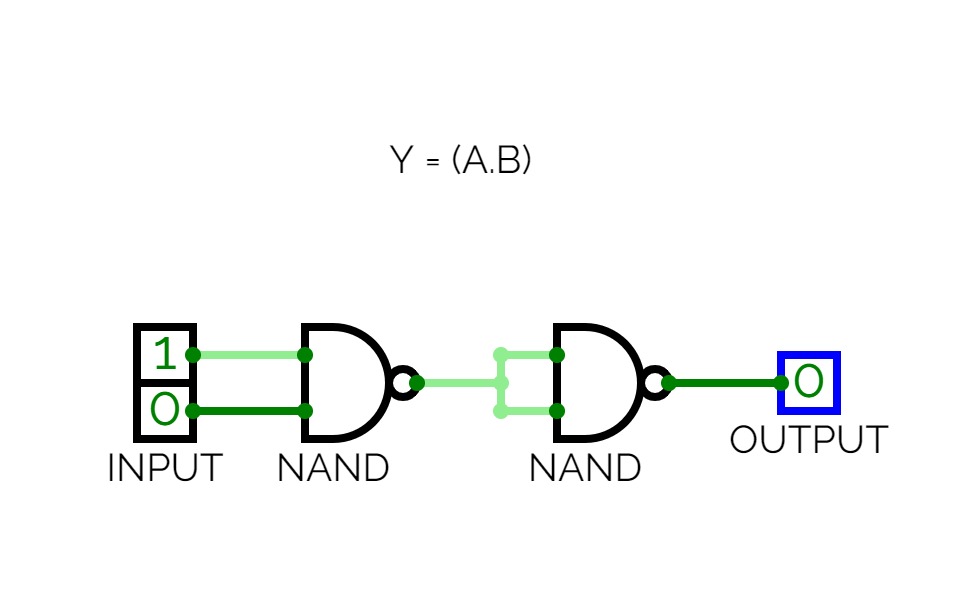

NAND gates as AND gate

NAND gates as AND gate

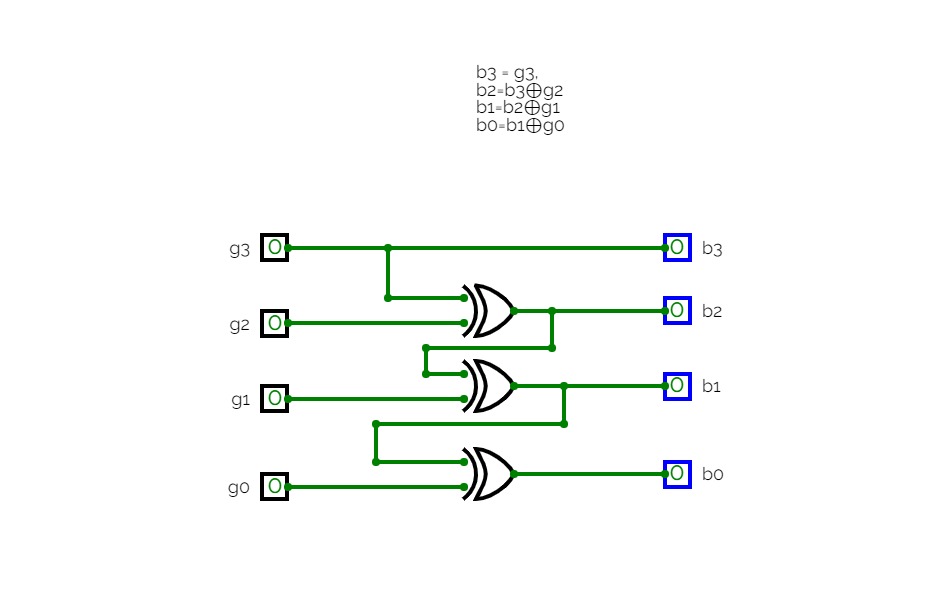

4 bit Gray code to 4 bit Binary

4 bit Gray code to 4 bit Binary

BCD to decimal

BCD to decimal

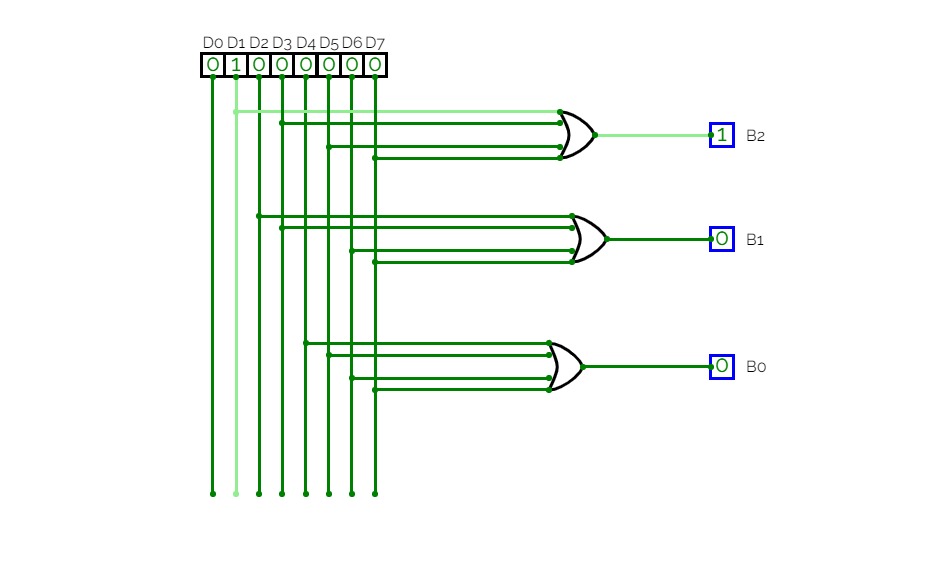

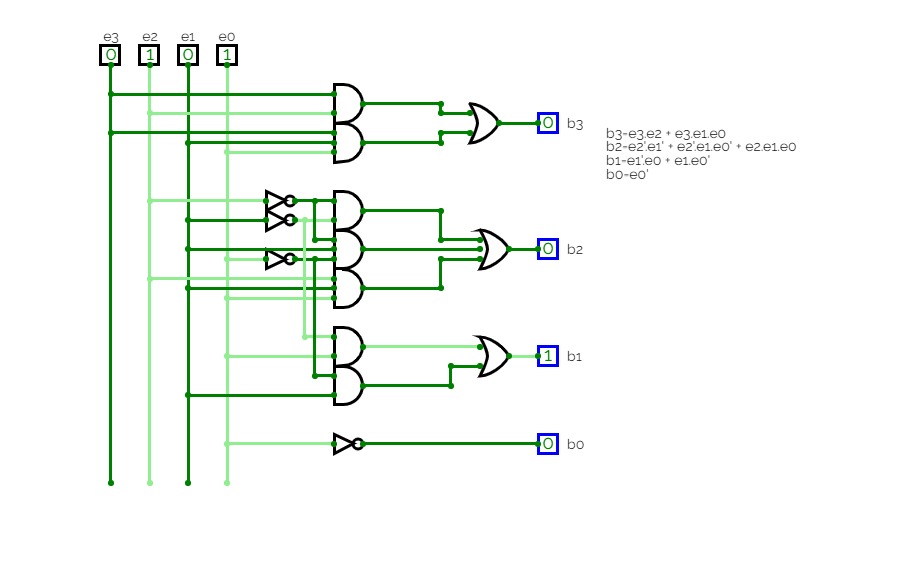

Octal to binary using basic Gate

Octal to binary using basic Gate

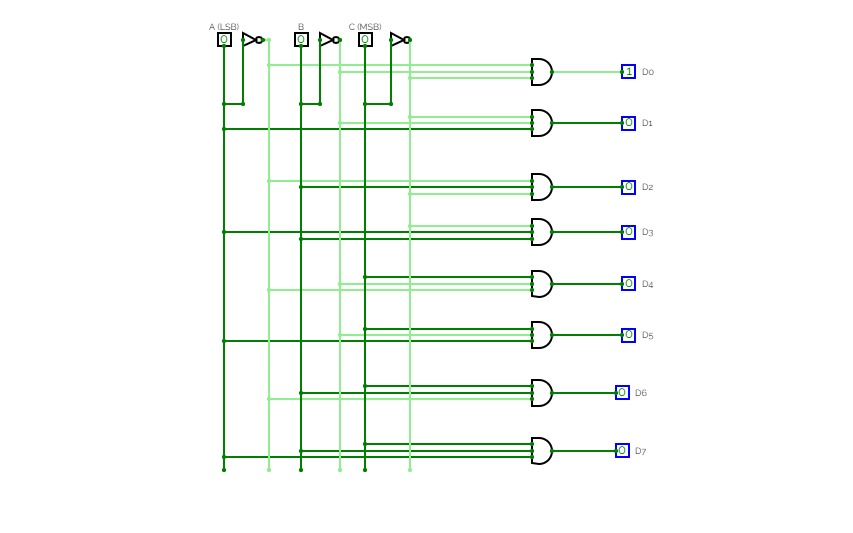

3-8 De-Coder

3-8 De-Coder

Trial befre 1st ex

Trial befre 1st ex

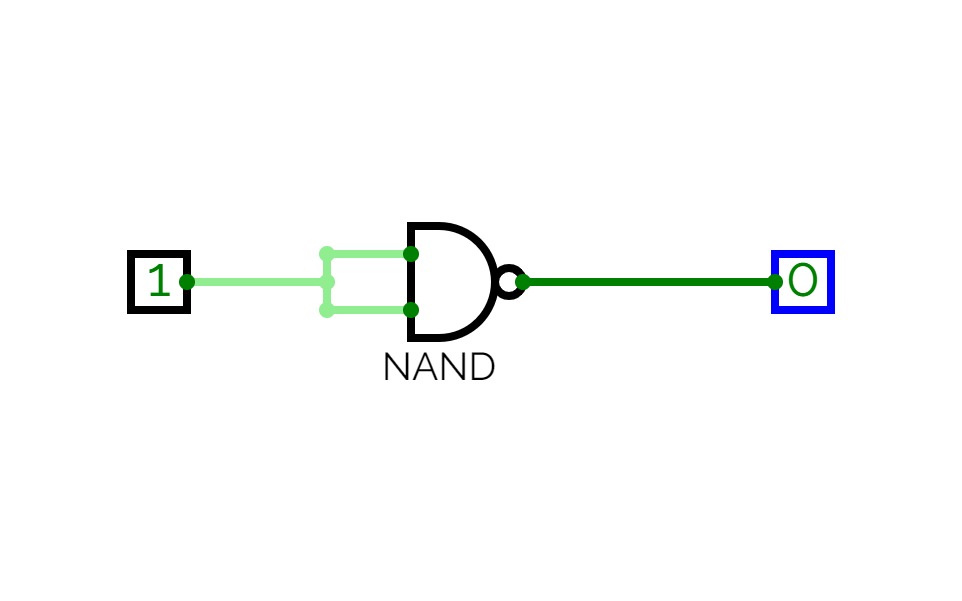

NAND gates as NOT gate

NAND gates as NOT gate

Untitled

Untitled

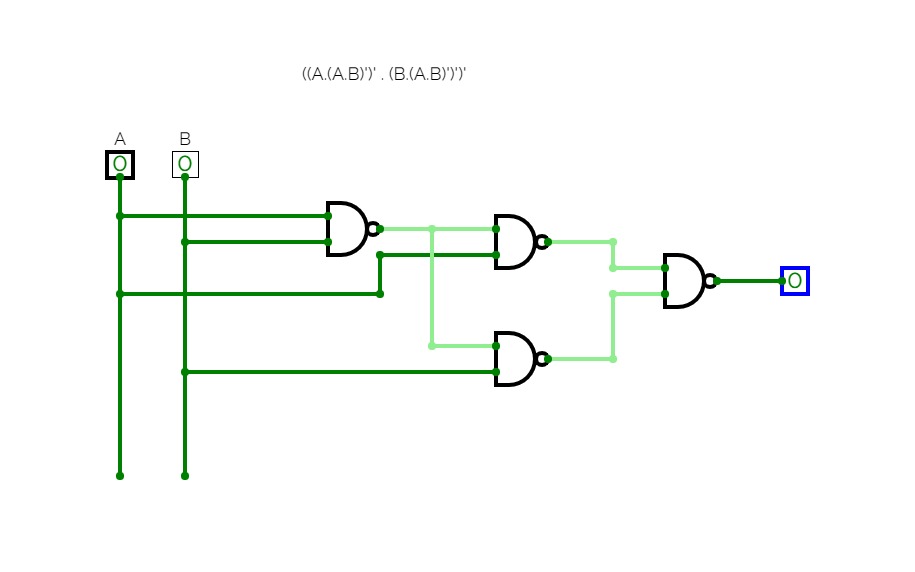

XOR with NAND

XOR with NAND

EXP-2

EXP-2

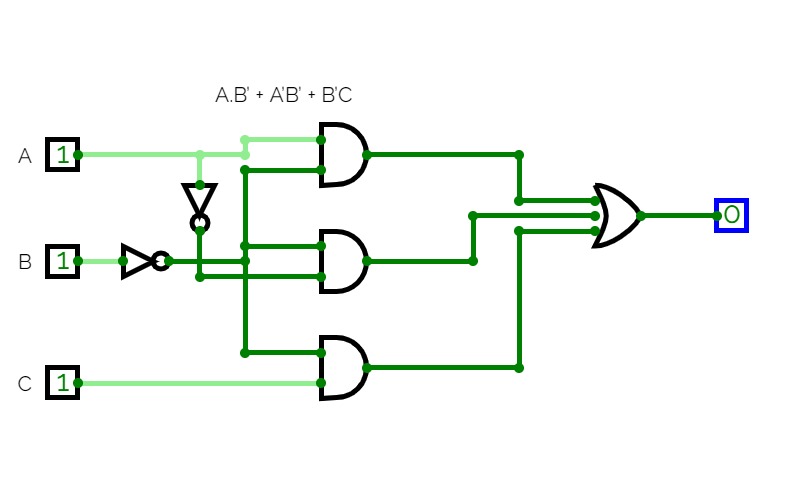

A.B’ + A’B’ + B’C

A.B’ + A’B’ + B’C

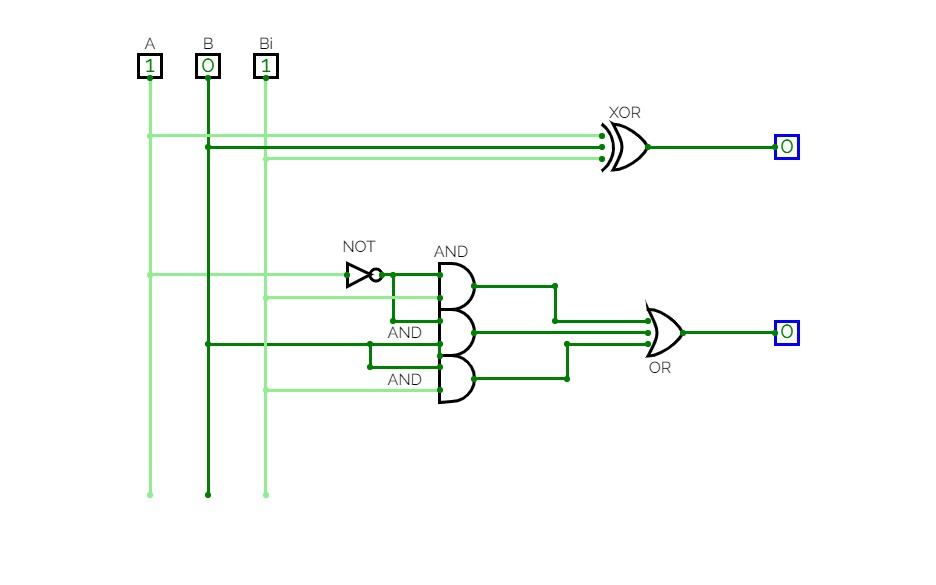

Half-Subtractor

Half-Subtractor

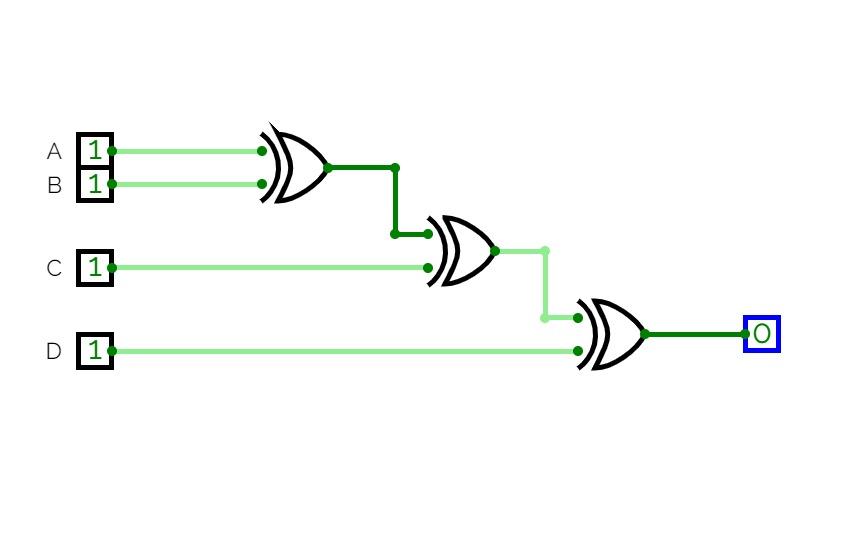

Even Parity

Even Parity

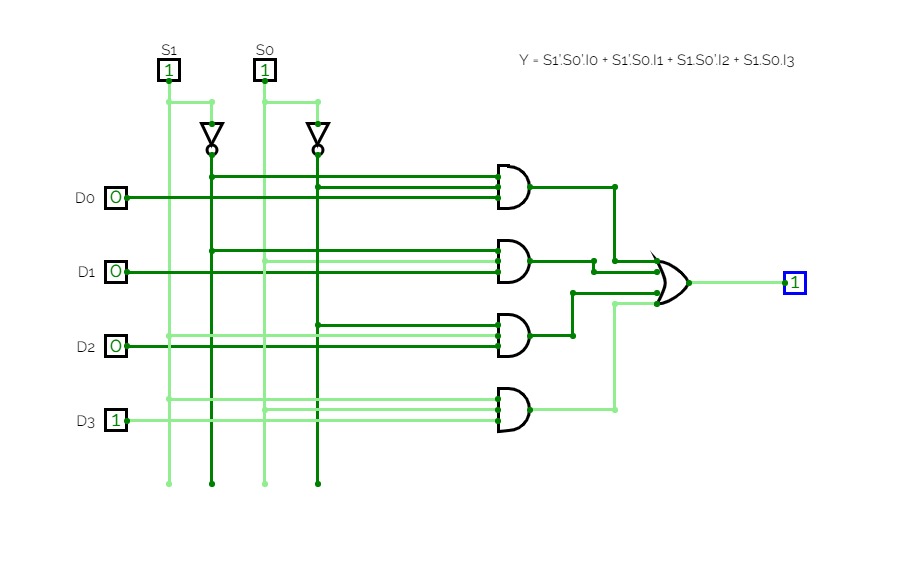

MUX 4:1

MUX 4:1

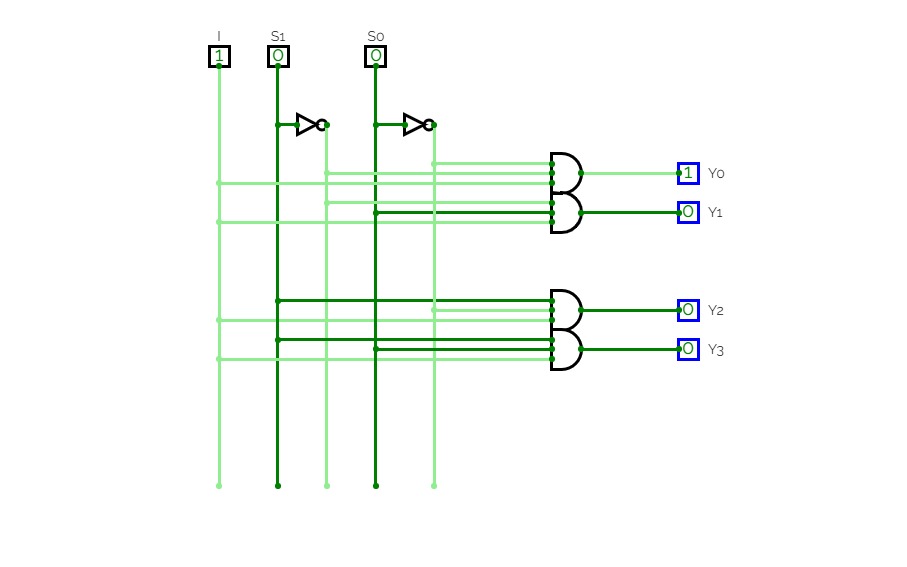

1:4 De-MUX

1:4 De-MUX

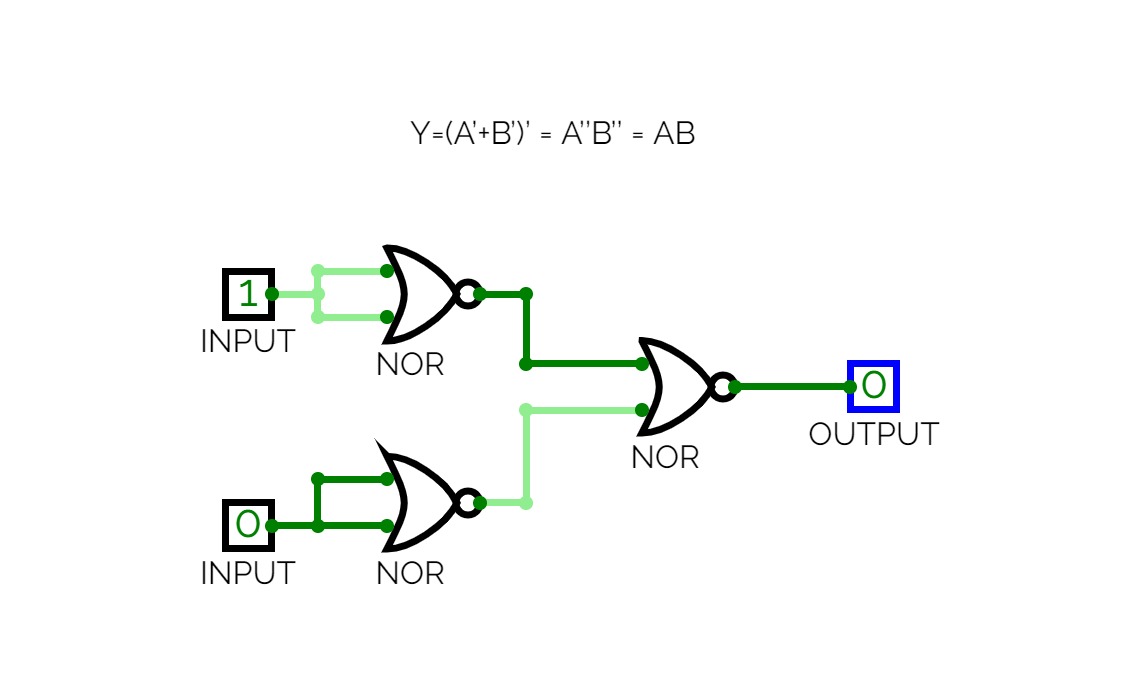

NOR gates as AND gate

NOR gates as AND gate

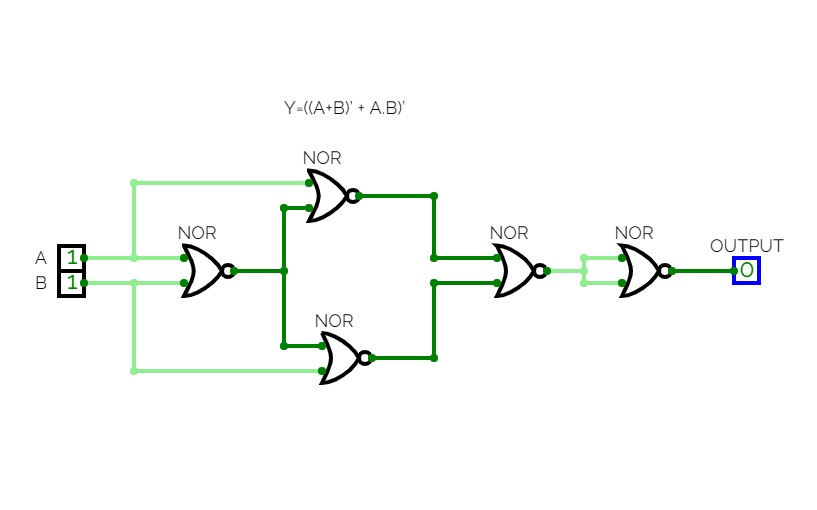

NOR gates as X-OR gate

NOR gates as X-OR gate

Full Subtractor

Full Subtractor

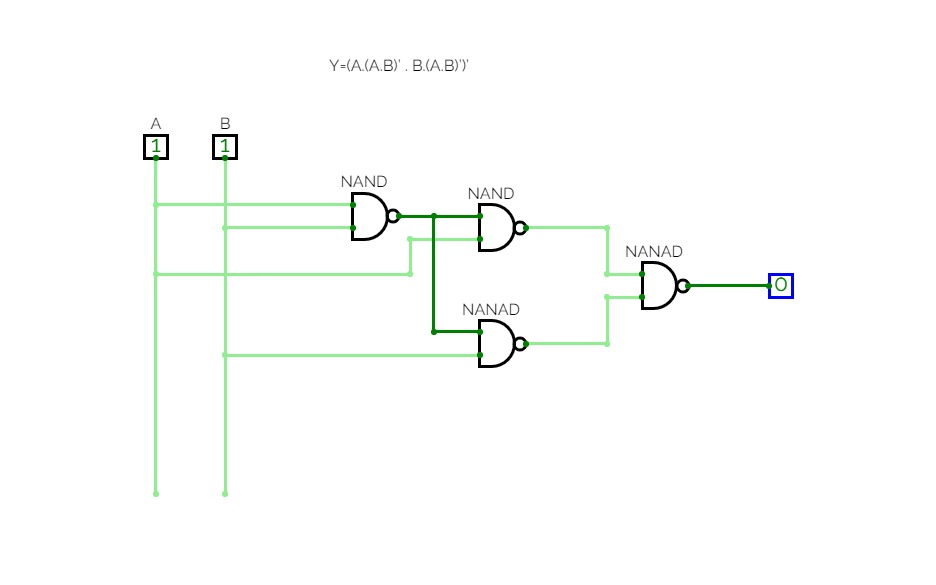

NAND gates as X-OR gate

NAND gates as X-OR gate

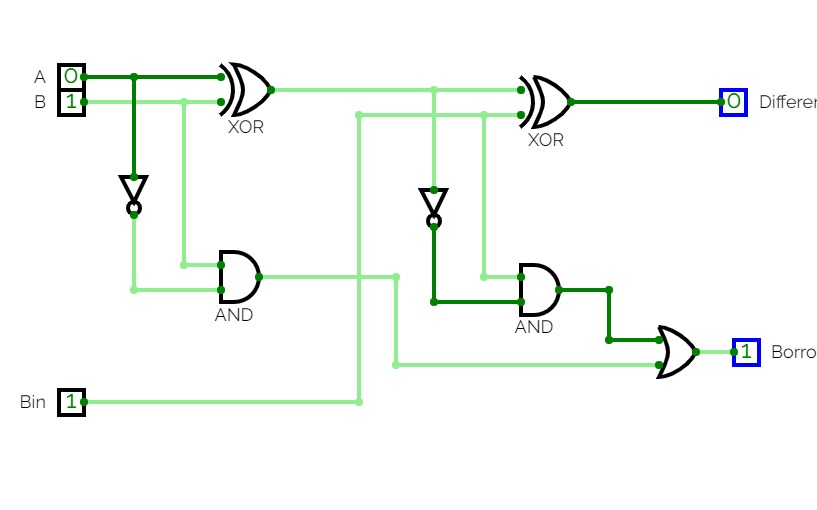

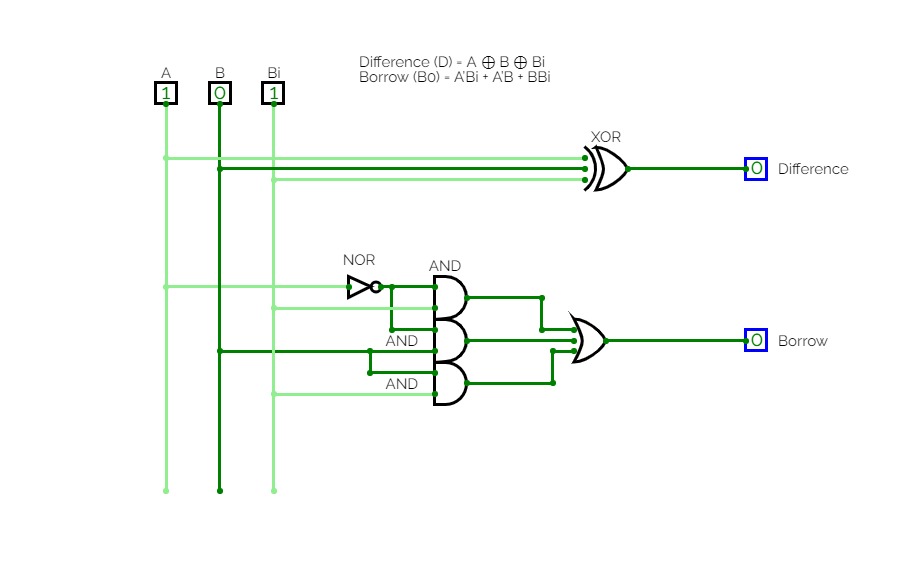

Full Subtractor

Full Subtractor

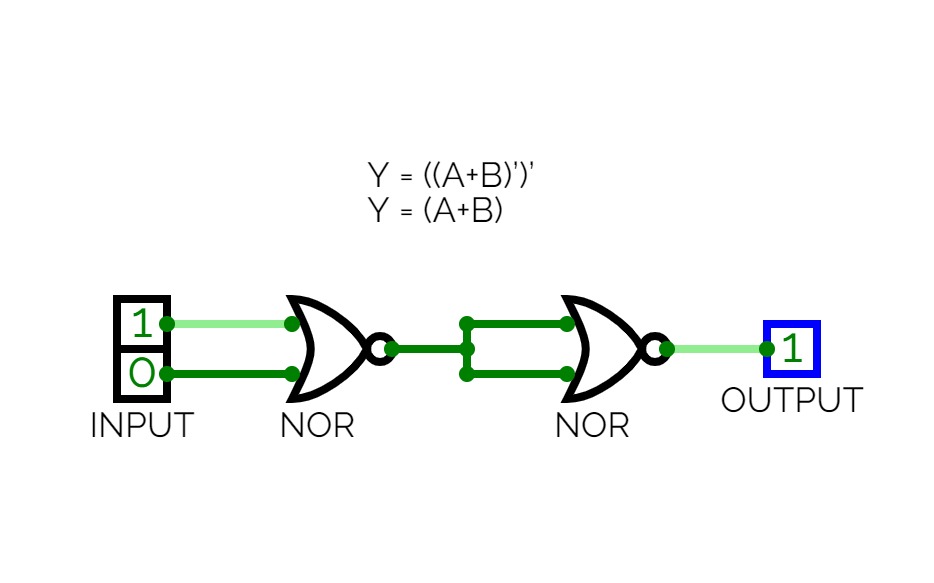

NOR gates as OR gate

NOR gates as OR gate

BCD to decimal

BCD to decimal

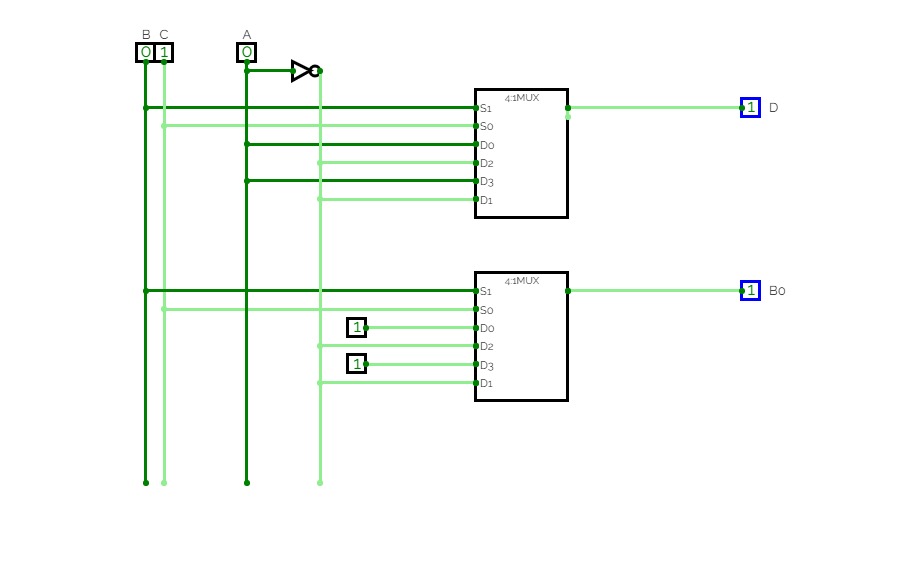

Implementation of Full Subtractor using MUX

Implementation of Full Subtractor using MUX

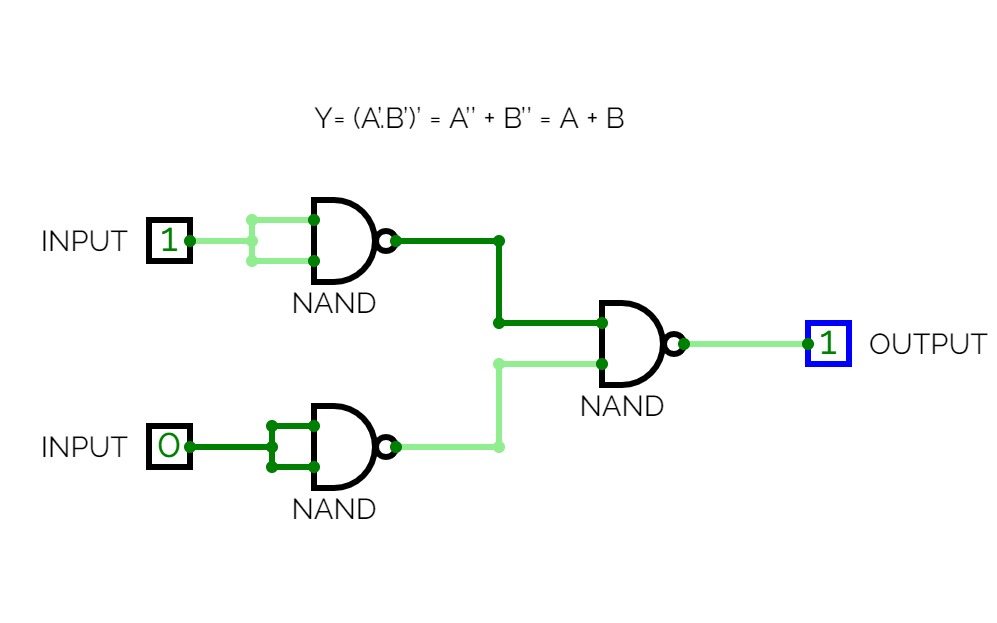

NAND gates as OR gate

NAND gates as OR gate

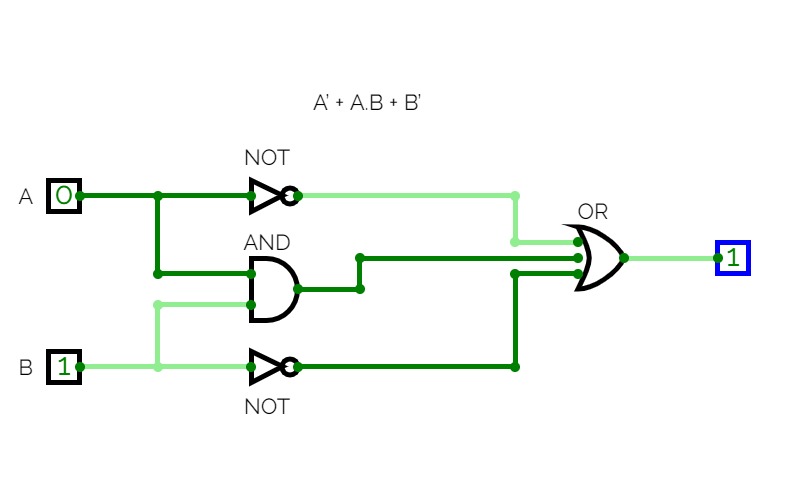

A’ + A.B + B’

A’ + A.B + B’

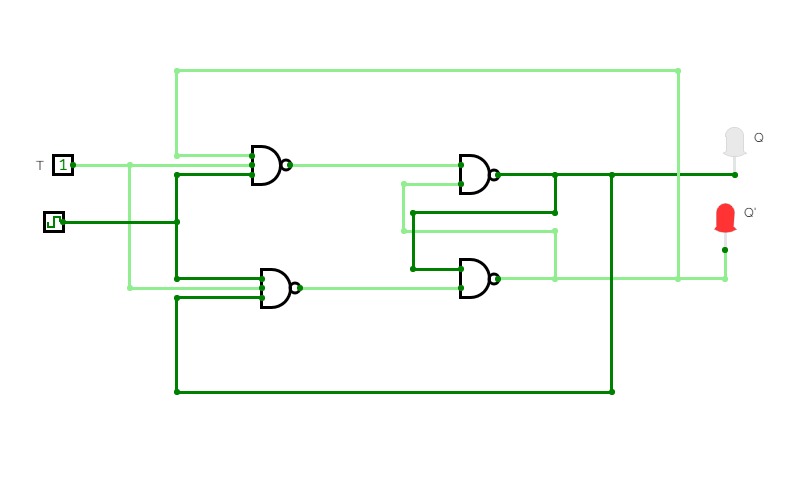

Flipflop

Flipflop

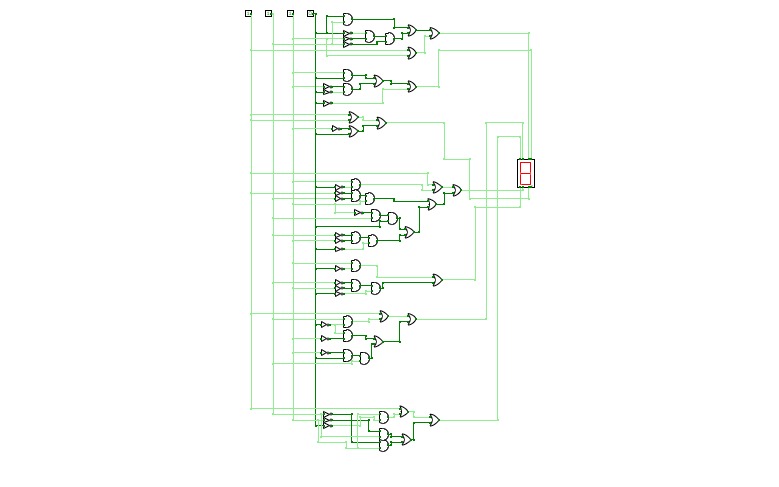

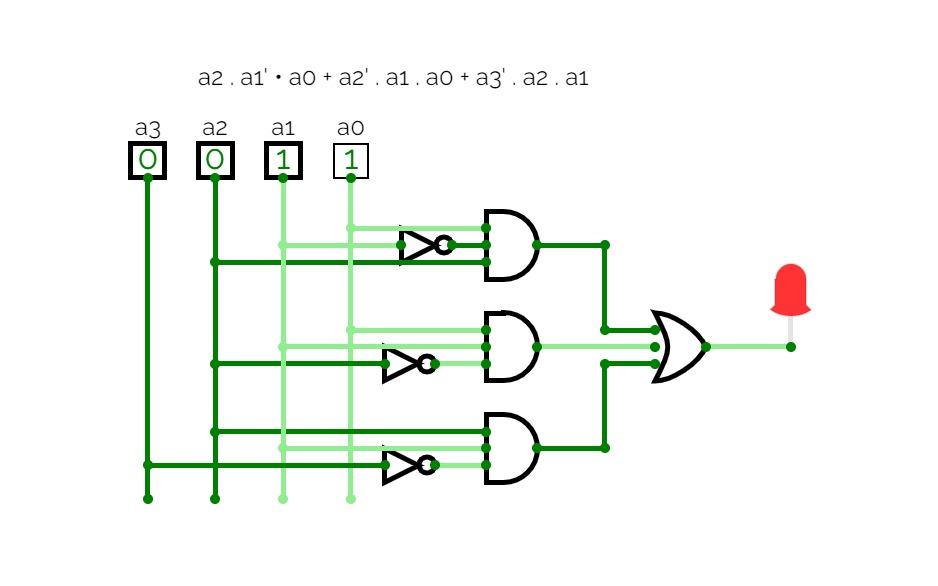

Prime and Non-Prime numbers (4-bit) Display

Prime and Non-Prime numbers (4-bit) Display

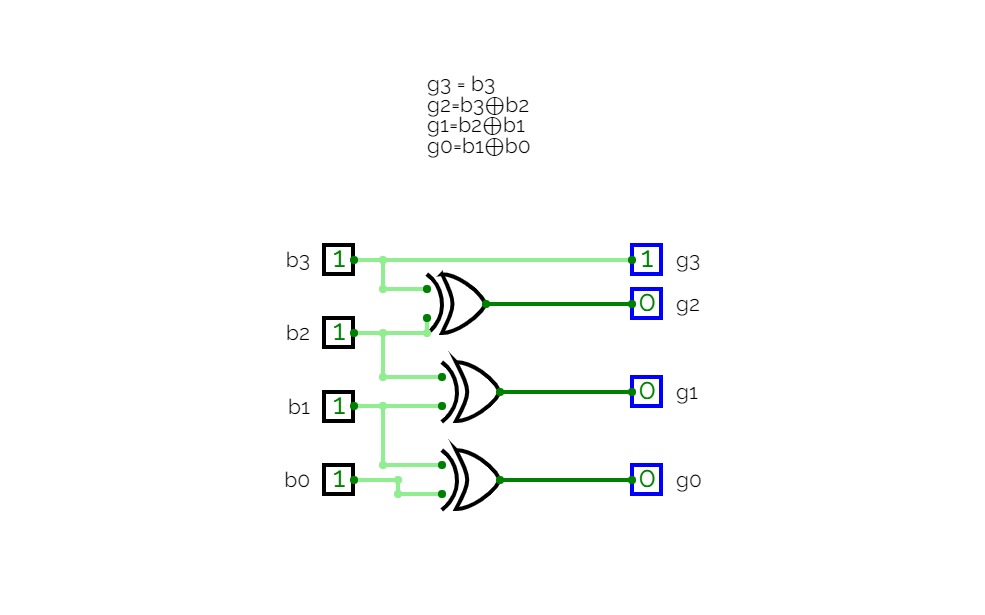

4 bit Binary code to 4 bit Gray code.

4 bit Binary code to 4 bit Gray code.

Excess -3 code to BCD.

Excess -3 code to BCD.

Adder

Adder

NAND gates as AND gate

NAND gates as AND gate

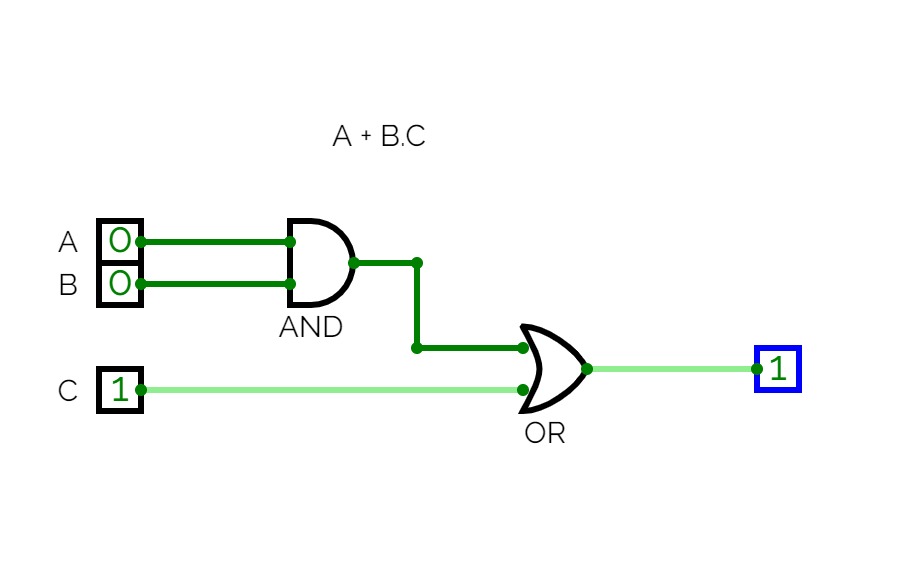

A + B.C

A + B.C

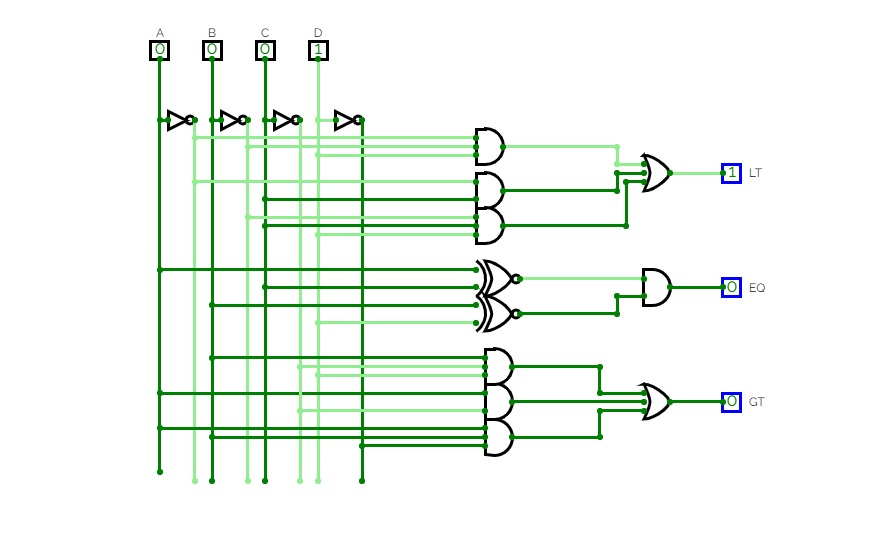

2 bit magnitude Comparator

2 bit magnitude Comparator

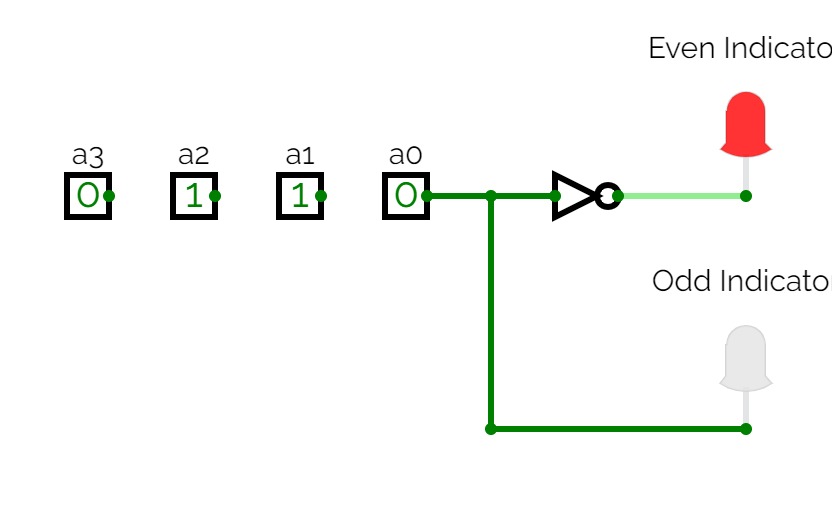

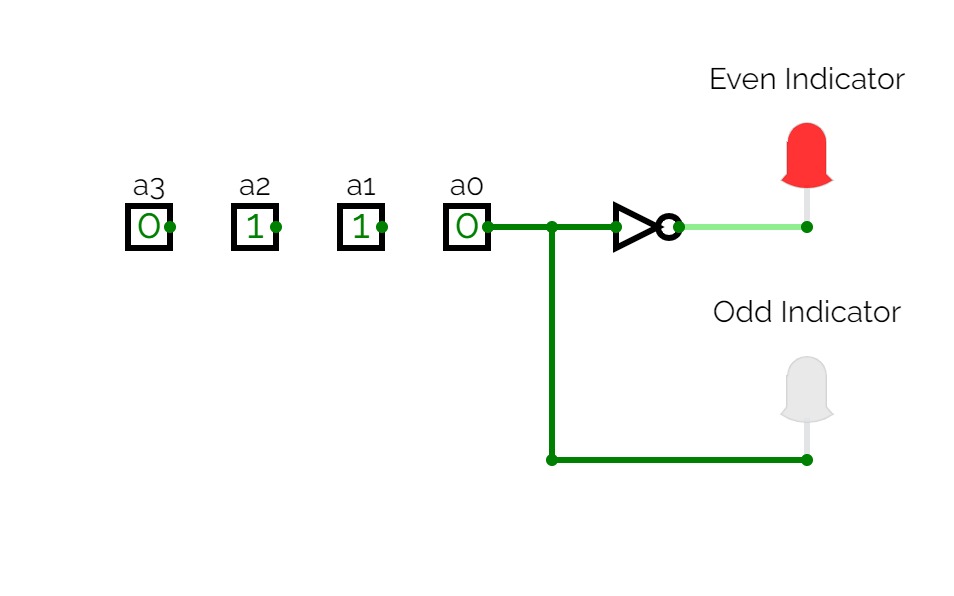

4-bit Odd and Even indicator

4-bit Odd and Even indicator

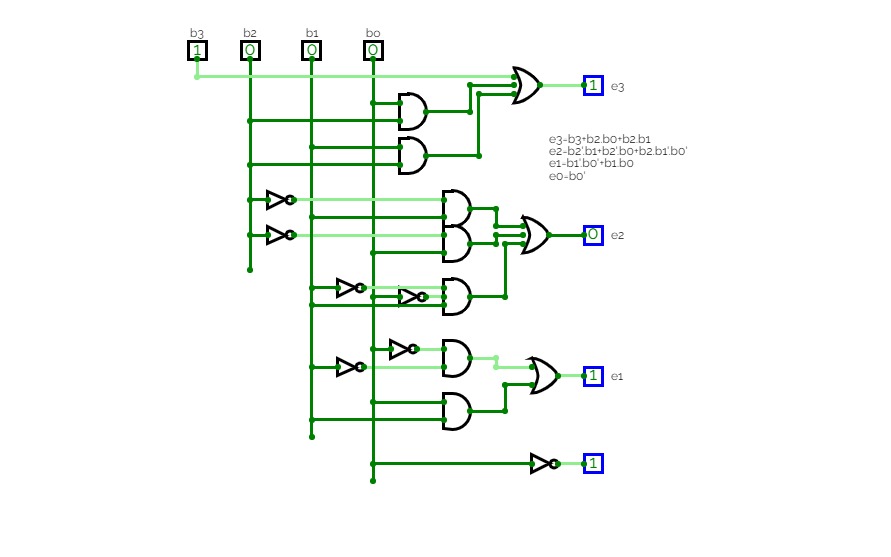

BCD to Excess -3 code

BCD to Excess -3 code

full subtractor using two half subtractor and an Or gate

full subtractor using two half subtractor and an Or gate