varun pandey

Member since: 3 years

Educational Institution: Not Entered

Country: Not Entered

16 : 1 Multiplexer

16 : 1 Multiplexer

16 : 1 Multiplexer

16 : 1 Multiplexer

8:1 MUX using 2:1 MUX

8:1 MUX using 2:1 MUX

8:1 mux using 2:1mux

8:1 mux using 2:1mux

4-bit right shift register

4-bit right shift register

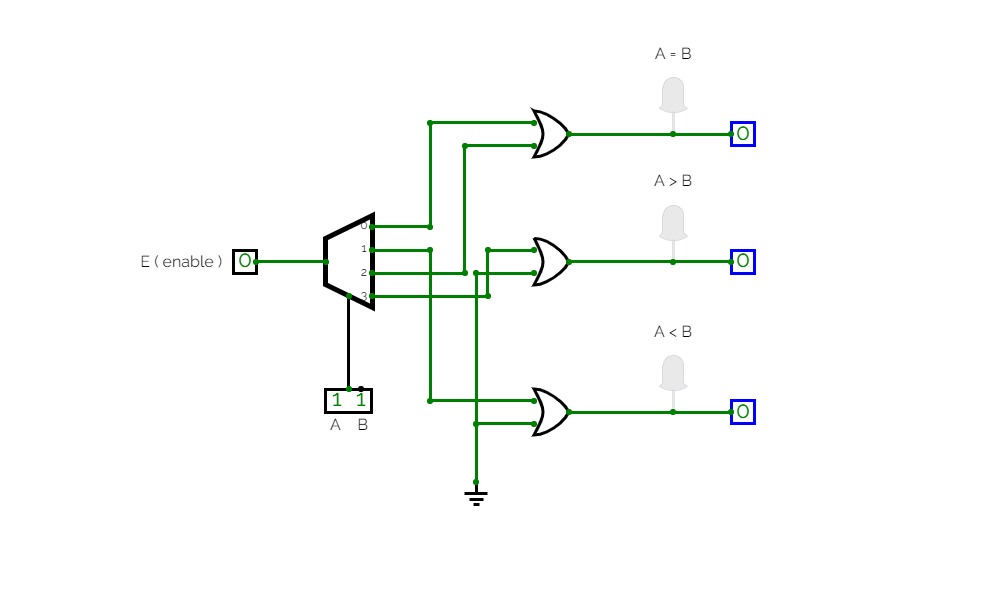

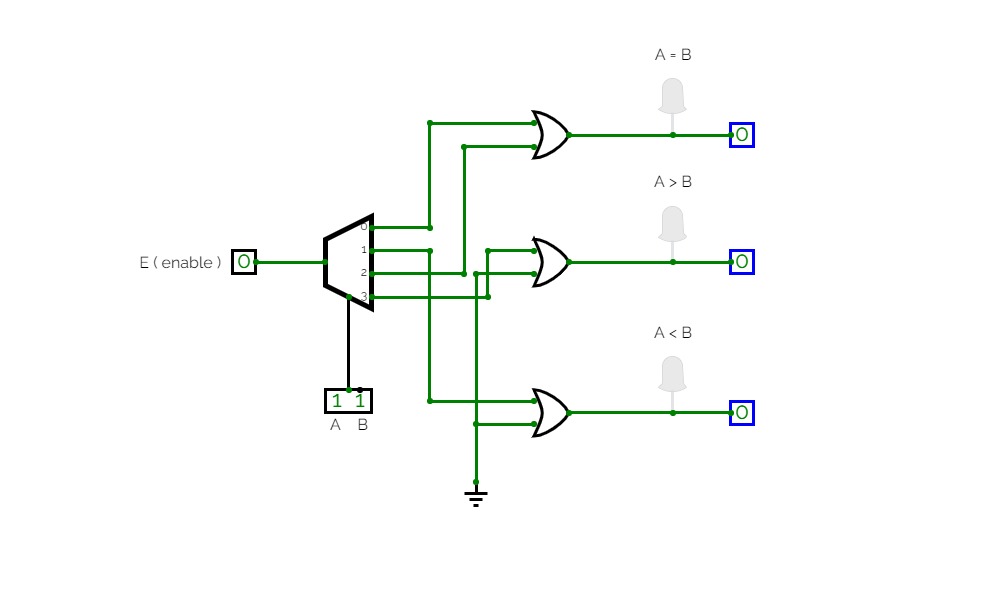

Design 1 bit comparator using 4:1 MUX

Design 1 bit comparator using 4:1 MUX

Design 1 bit comparator using 4:1 MUX

Design 1 bit comparator using 4:1 MUX

Design 1 bit comparator using 4:1 MUX

Design 1 bit comparator using 4:1 MUX

VARUN PANDEY 1 BIT COMPARATOR USING 4:1 Mux

VARUN PANDEY 1 BIT COMPARATOR USING 4:1 Mux

VARUN PANDEY 1 bit comparator using 4:1 mux

VARUN PANDEY 1 bit comparator using 4:1 mux

lol

lol

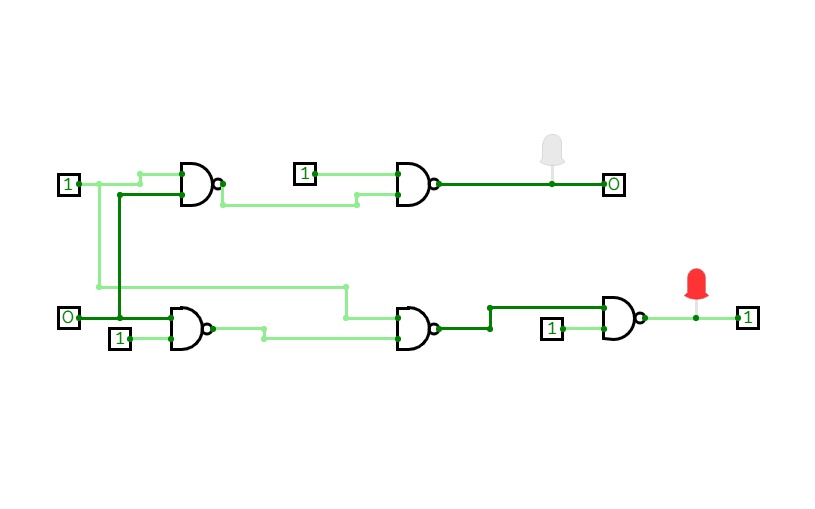

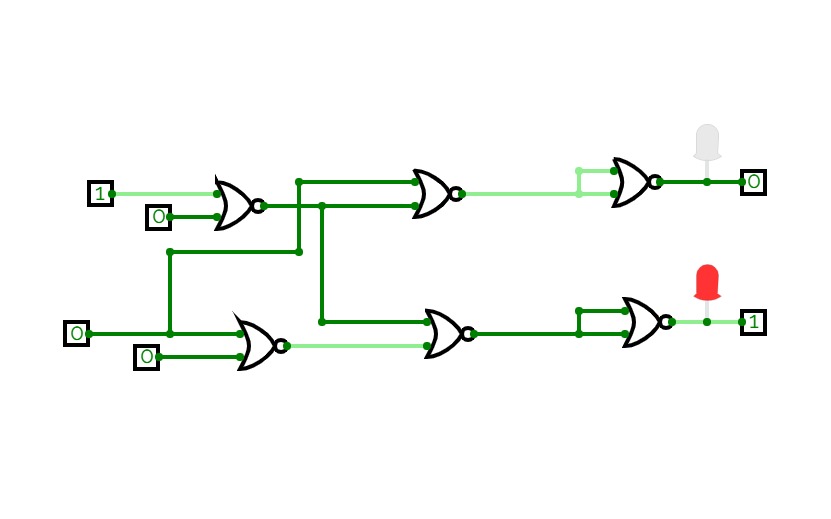

nand and nor

nand and nor

nand and nor

nand and nor

DEMUX

DEMUX

VARUN PANDEY HW 3 DEMUX

VARUN PANDEY HW 3 DEMUX

aryan khare task 4

aryan khare task 4

VARUN PANDEY 2:4 decoder using SOP equation

VARUN PANDEY 2:4 decoder using SOP equation

VARUN PANDEY 2:4 DECODER USING NOR LOGIC

VARUN PANDEY 2:4 DECODER USING NOR LOGIC

varun task3

varun task3

VARUN PANDEY 4:1 MUX USING 2:1 MUX

VARUN PANDEY 4:1 MUX USING 2:1 MUX

VARUN PANDEY 16:1 MUX using 2:1 MUX

VARUN PANDEY 16:1 MUX using 2:1 MUX

VARUN PANDEY IMPLEMENT USING NOR

VARUN PANDEY IMPLEMENT USING NOR

VARUN PANDEY Design the internal structure

VARUN PANDEY Design the internal structure

CAT: USING DECODER , DESIGN THE CLC

CAT: USING DECODER , DESIGN THE CLC

BCD to excess 3 code using 1:8 DEMUX

BCD to excess 3 code using 1:8 DEMUX

VARUN PANDEY IMPLEMENT THE EQUATION USING DECODER

VARUN PANDEY IMPLEMENT THE EQUATION USING DECODER

VARUN PANDEY IMPLEMENT FROM DECODER

VARUN PANDEY IMPLEMENT FROM DECODER

HOT QUESTION VARUN PANDEY

HOT QUESTION VARUN PANDEY

HW 3 CIRCUIT IMPLEMENTATION

HW 3 CIRCUIT IMPLEMENTATION

1 bit comparator using 4:1 mux

1 bit comparator using 4:1 mux

VARUN PANDEY 2 INPUT NAND/NOR

VARUN PANDEY 2 INPUT NAND/NOR

VARUN PANDEY DUAL MUX

VARUN PANDEY DUAL MUX

1 bit comparator using 1:4 demux

1 bit comparator using 1:4 demux

VARUN PANDEY 2:4 DECODER USING POS EQUATION

VARUN PANDEY 2:4 DECODER USING POS EQUATION

16:1 mux using 2:1 mux

16:1 mux using 2:1 mux

VARUN PANDEY BCD-excess 3 code

VARUN PANDEY BCD-excess 3 code

CAT: design the internal structure of Circuit given using NAND gates.

CAT: design the internal structure of Circuit given using NAND gates.

CAT. : IMPLELEMENT FROM DECODER

CAT. : IMPLELEMENT FROM DECODER

CAT: IMPLEMENT USING NOR LOGIC

CAT: IMPLEMENT USING NOR LOGIC

CAT: implement the equation using decoder

CAT: implement the equation using decoder

VARUN PANDEY 16:1 MUX USING 8:1 MUX, 8:1 MUX using 4:1 and 2:1

VARUN PANDEY 16:1 MUX USING 8:1 MUX, 8:1 MUX using 4:1 and 2:1

varun task3

varun task3

Design 1 bit comparator using 4:1 MUX

Design 1 bit comparator using 4:1 MUX

Design 1 bit comparator using 4:1 MUX

Design 1 bit comparator using 4:1 MUX

VARUN PANDEY 1 BIT COMPARATOR USING 1:4 DEMUX

VARUN PANDEY 1 BIT COMPARATOR USING 1:4 DEMUX

Design 1 bit comparator using 4:1 MUX

Design 1 bit comparator using 4:1 MUX

Design 1 bit comparator using 4:1 MUX

Design 1 bit comparator using 4:1 MUX

VARUN PANDEY 20MIC0139 DLCD LAB FAT IMPLEMENTED CIRCUIT

VARUN PANDEY 20MIC0139 DLCD LAB FAT IMPLEMENTED CIRCUIT

BCD to Excees-3 Converter circuit

BCD to Excees-3 Converter circuit

4 ->1 multiplexer using 2->1 Multiplexers

4 ->1 multiplexer using 2->1 Multiplexers

Design 1 bit comparator using 4:1 MUX

Design 1 bit comparator using 4:1 MUX

BCD to excess 3 code using 1:8 DEMUX

BCD to excess 3 code using 1:8 DEMUX

VARUN PANDEY TASK 1 POS 4:16 DECODER

VARUN PANDEY TASK 1 POS 4:16 DECODER

1 bit comparator using 1:4 demux

1 bit comparator using 1:4 demux

VARUN PANDEY DECODER USING REG NUMBER

VARUN PANDEY DECODER USING REG NUMBER

VARUN PANDEY CLC

VARUN PANDEY CLC

varun pandey right shift register using D FF

varun pandey right shift register using D FF

VARUN PANDEY 1 BIT COMPARATOR USING 1:4 DEMUX

VARUN PANDEY 1 BIT COMPARATOR USING 1:4 DEMUX