Subhadeep Sinha_20220PHY222

Member since: 3 years

Educational Institution: Banaras Hindu University

Country: Not Entered

parallel adder

parallel adder

jk circuit excitation

jk circuit excitation

3 to 8 line decoder

3 to 8 line decoder

D Flip Flop

D Flip Flop

Full adder using decoder and two OR gates

Full adder using decoder and two OR gates

Half-Subtractor

Half-Subtractor

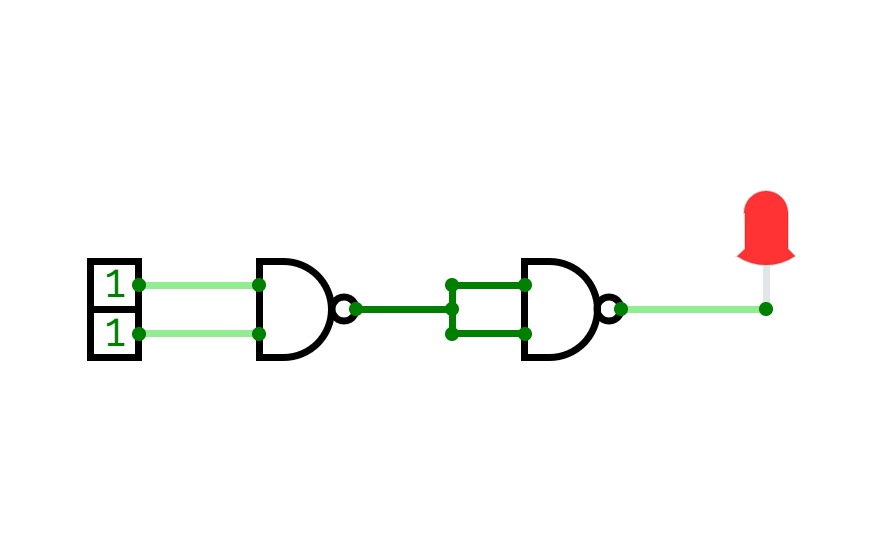

XOR using basic gates

XOR using basic gates

PLA with 3 inputs

PLA with 3 inputs

PAL

PAL

4 TO 1 MUX

4 TO 1 MUX

NOT Gate

NOT Gate

question 7

question 7

OR using NOR

OR using NOR

Full-adder

Full-adder

T flip flop using nand

T flip flop using nand

JK excitation circuit

JK excitation circuit

D excitation circuit

D excitation circuit

T excitation circuit

T excitation circuit

NOT using NAND

NOT using NAND

AND Gate

AND Gate

Question 4

Question 4

Full-subtractor

Full-subtractor

Full subtractor using decoder

Full subtractor using decoder

4 TO 1 MUX OF F

4 TO 1 MUX OF F

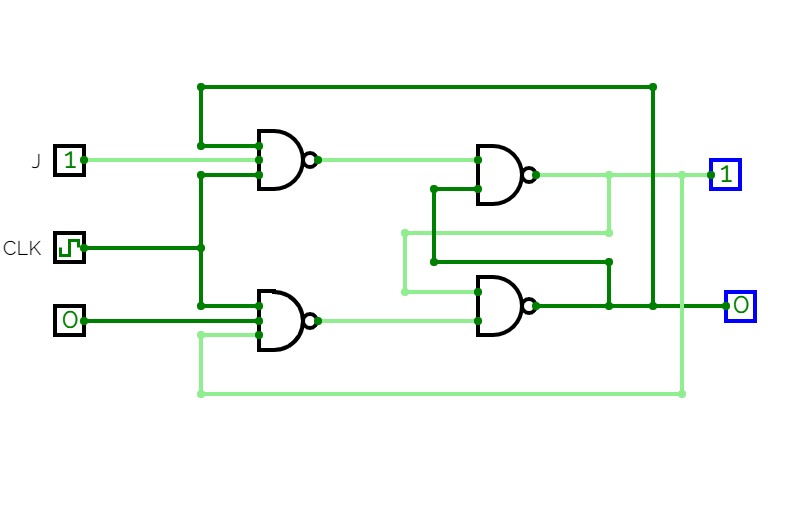

J K Flipflop

J K Flipflop

OR Gate

OR Gate

Half-adder

Half-adder

AND unsing NAND

AND unsing NAND

OR using NAND

OR using NAND

AND using NOR

AND using NOR

question 6

question 6

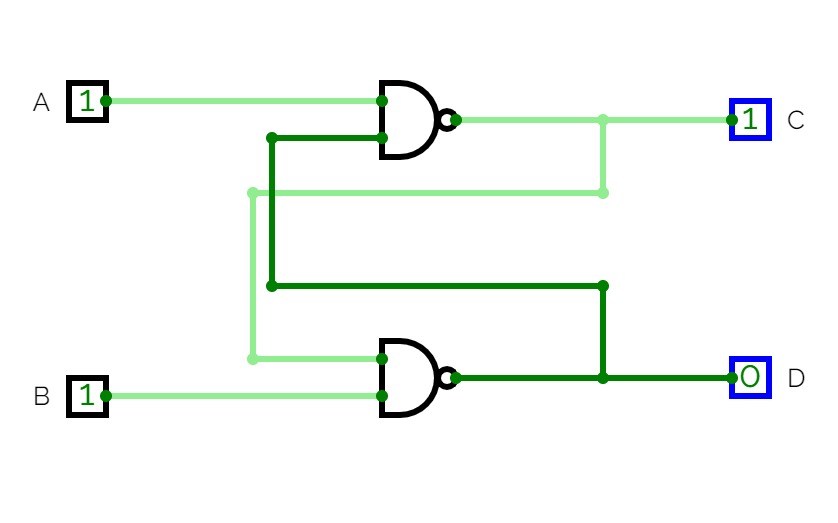

MAGNITUDE COMPARATOR

MAGNITUDE COMPARATOR

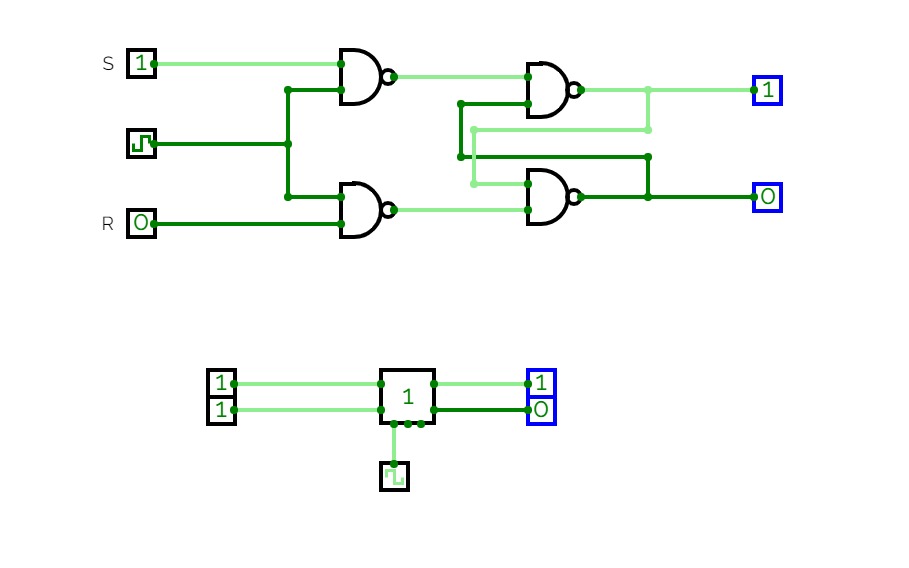

SR latch using nand gates

SR latch using nand gates

J K Flipflop using AND and NOR

J K Flipflop using AND and NOR

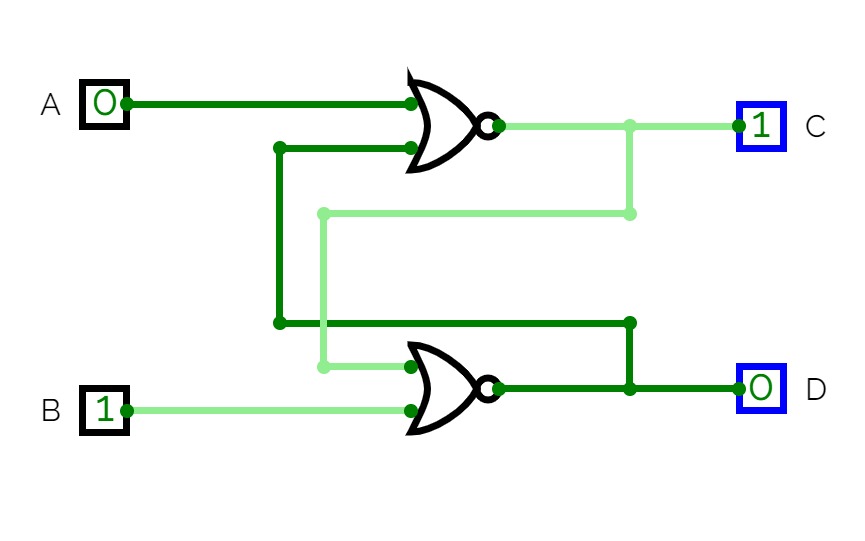

SR latch using NOR gates

SR latch using NOR gates

32 x 4 ROM

32 x 4 ROM

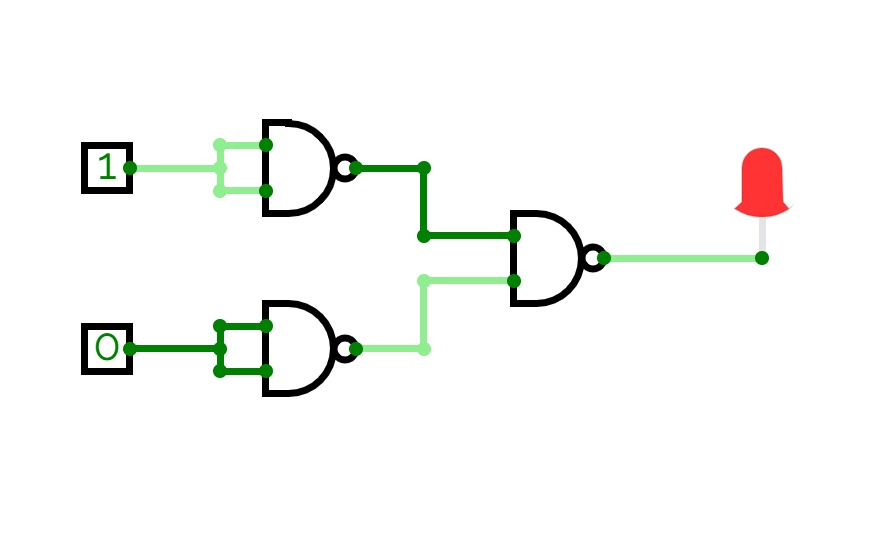

XNOR using basic gates

XNOR using basic gates

combinational circuit using ROM that accepts 2 bit number and generates output binary number equal to the square of the input number

combinational circuit using ROM that accepts 2 bit number and generates output binary number equal to the square of the input number

NOT using NOR

NOT using NOR

BCD to excess 3 code converter

BCD to excess 3 code converter

4 to 1 MUX

4 to 1 MUX

RS excitation circuit

RS excitation circuit

SR latch with control input using NAND gates

SR latch with control input using NAND gates

8 to 3 line encoder

8 to 3 line encoder

JK master slave flip flop

JK master slave flip flop