RAHUL S 20MIC0117

Member since: 3 years

Educational Institution: VIT Vellore

Country: India

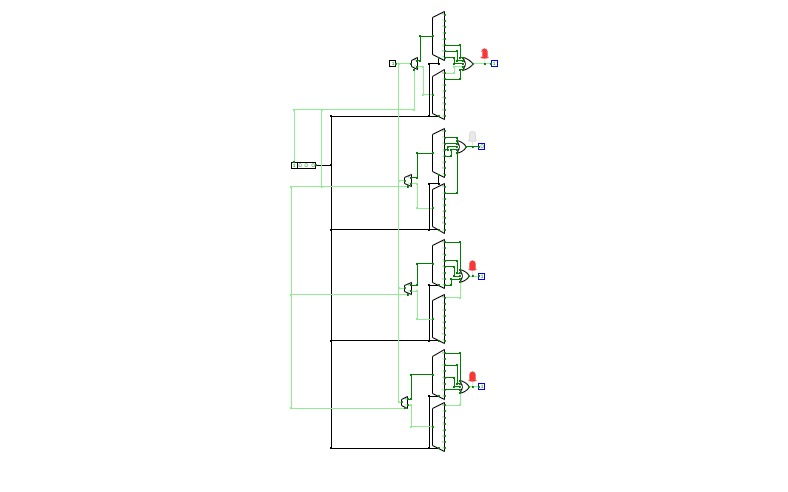

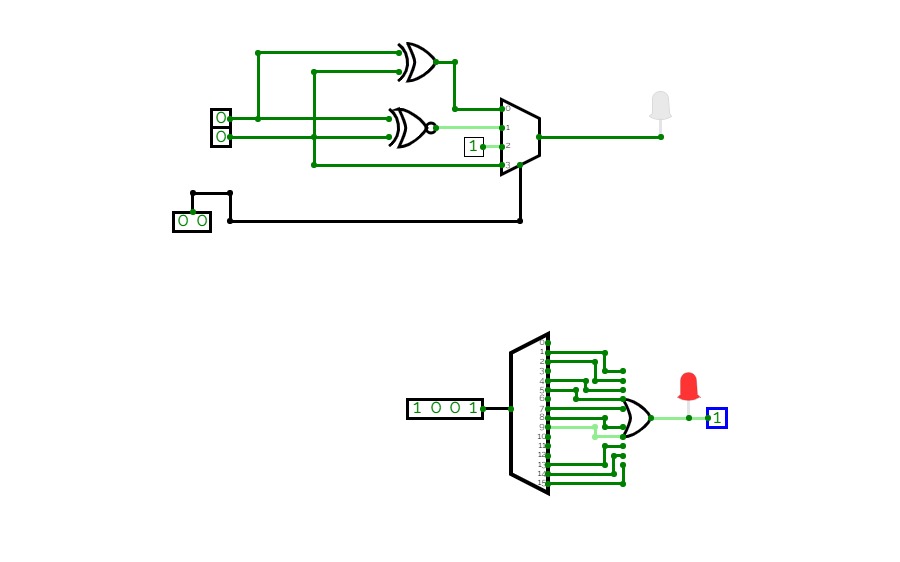

Decoder-VIVA2

Decoder-VIVA2

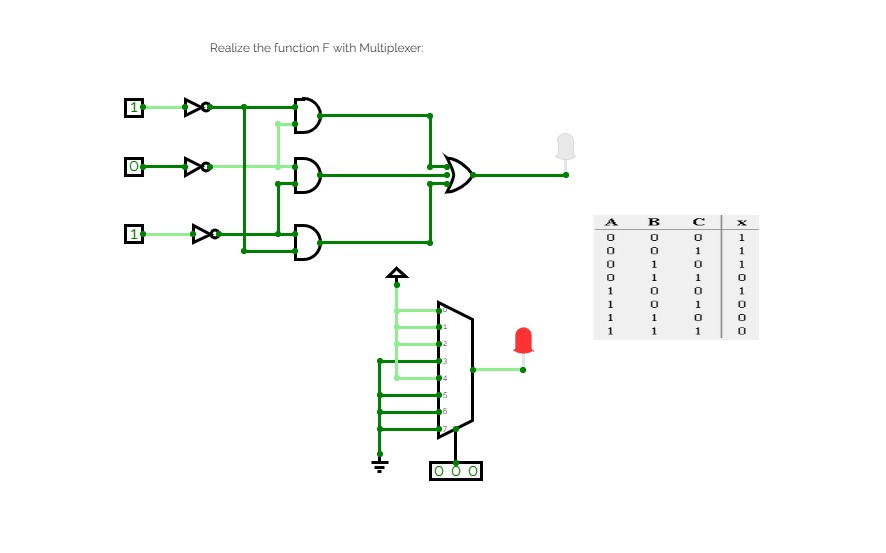

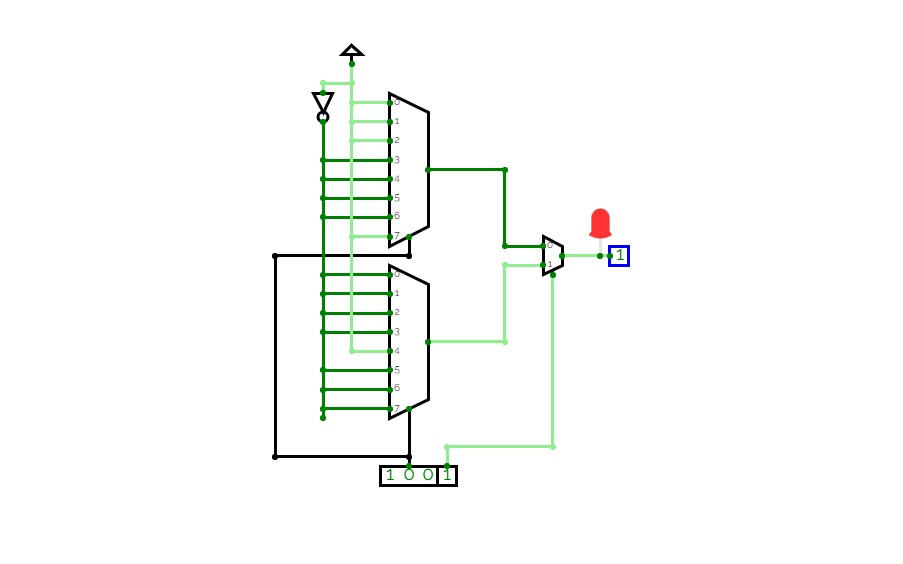

cat2-q3-b

cat2-q3-b

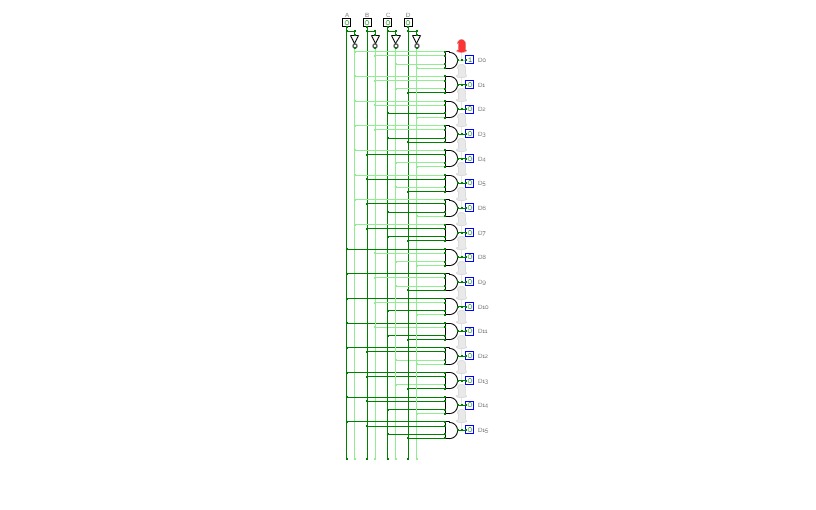

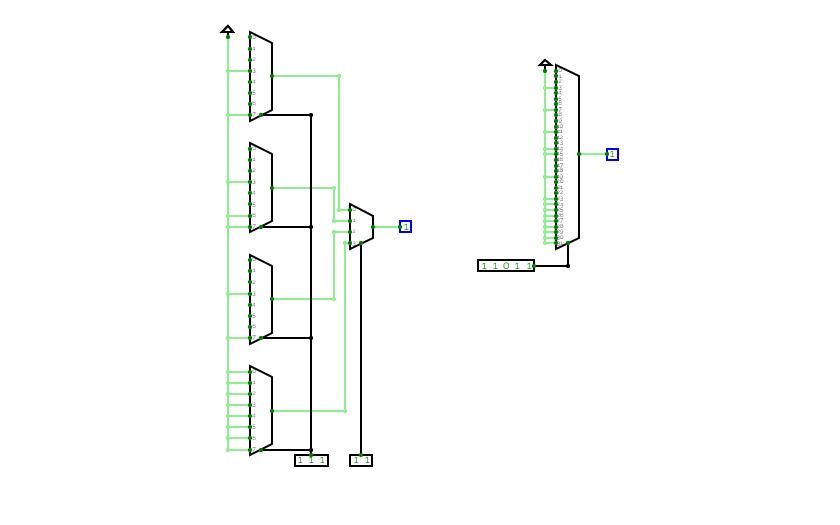

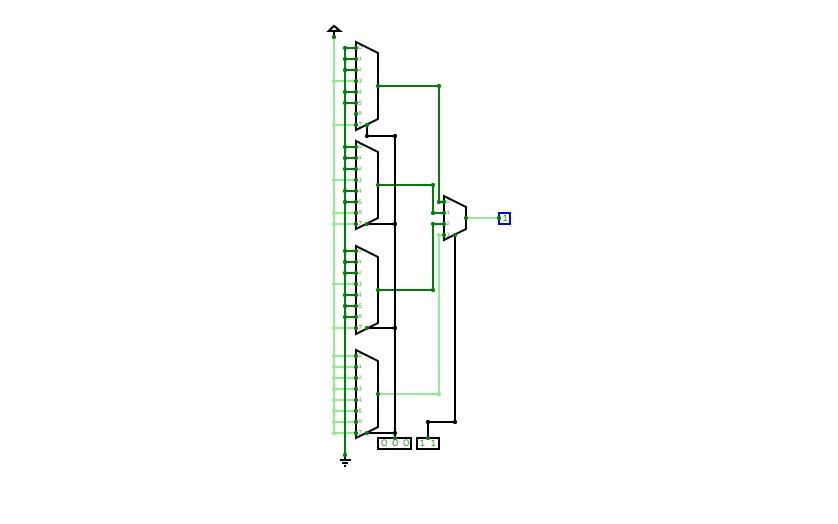

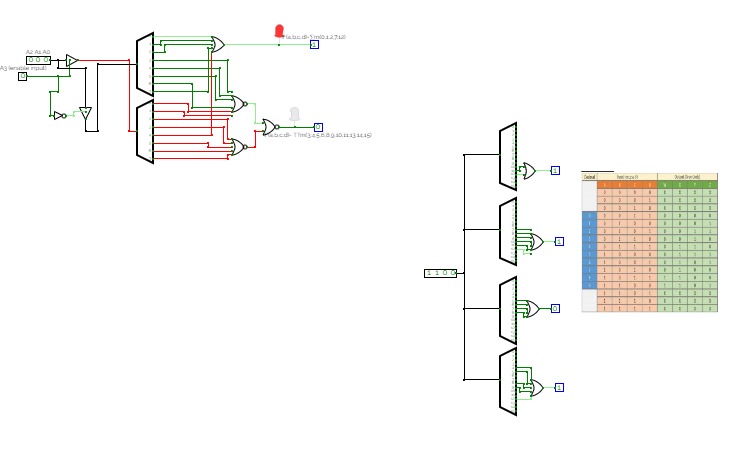

4:16 decoder using 3:8

4:16 decoder using 3:8

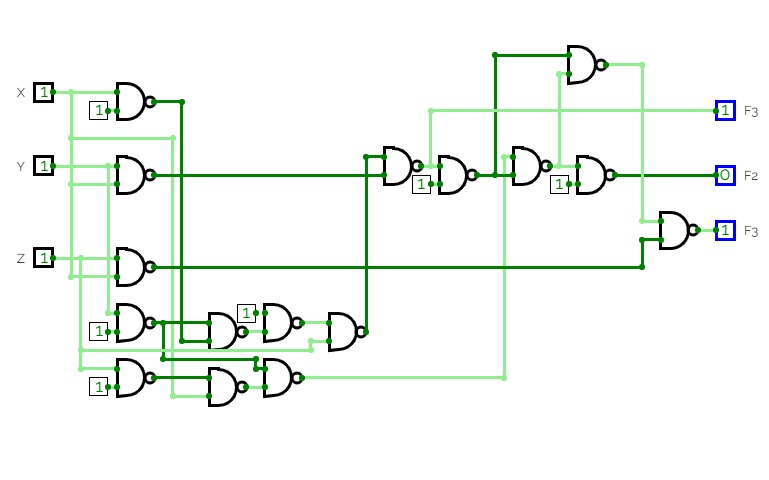

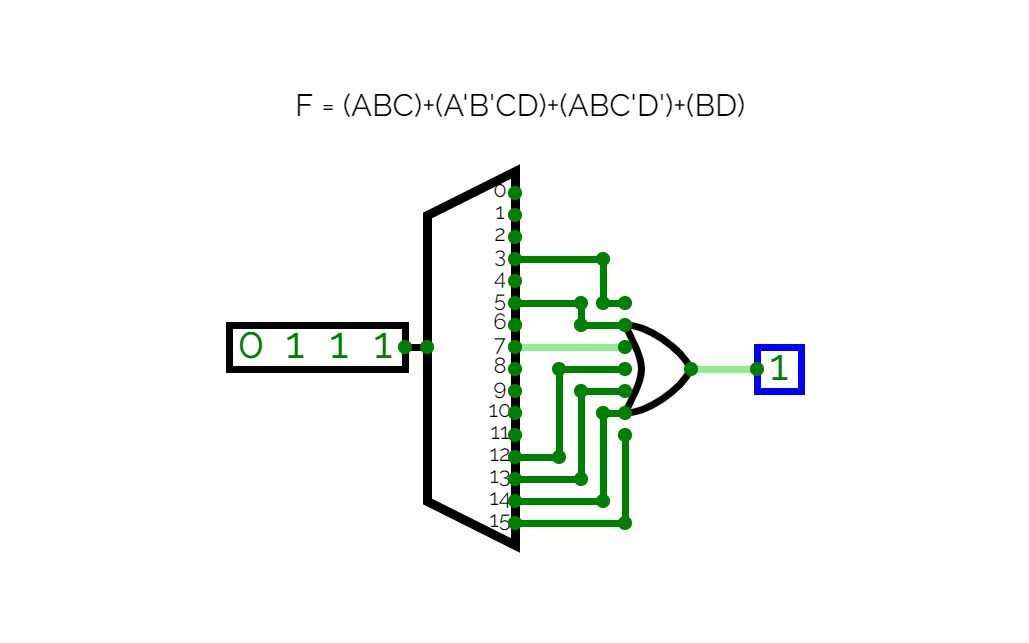

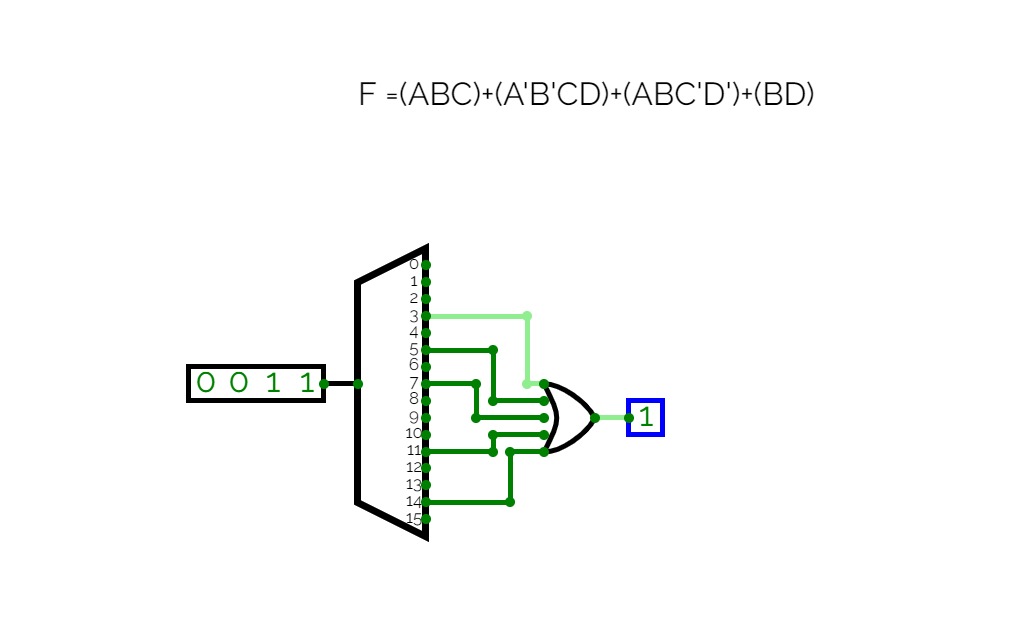

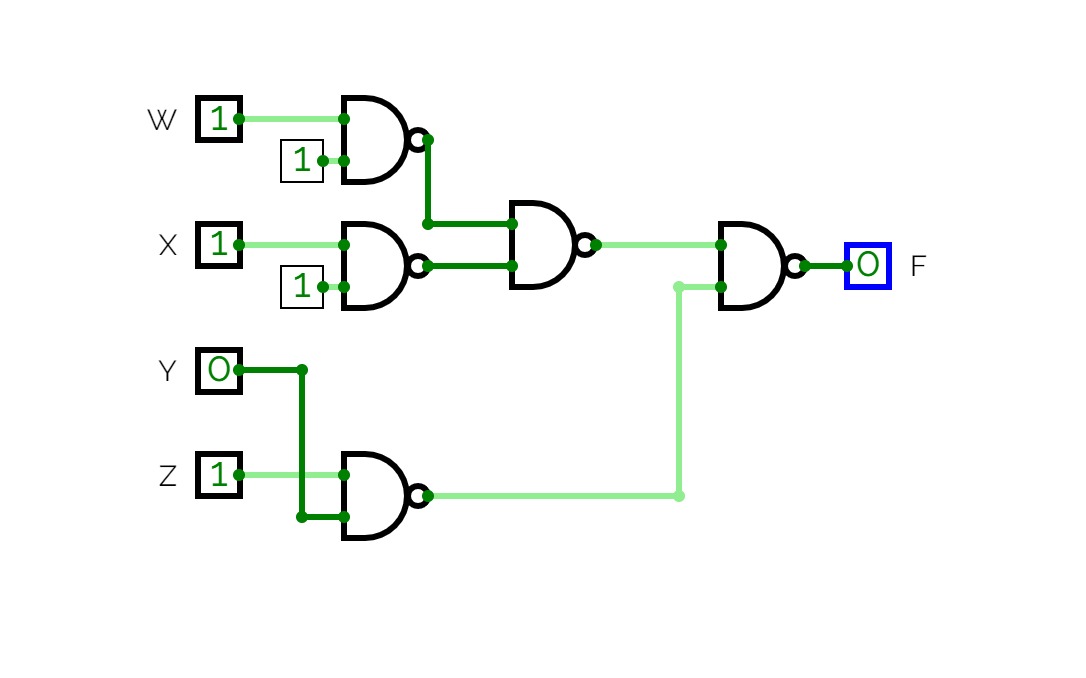

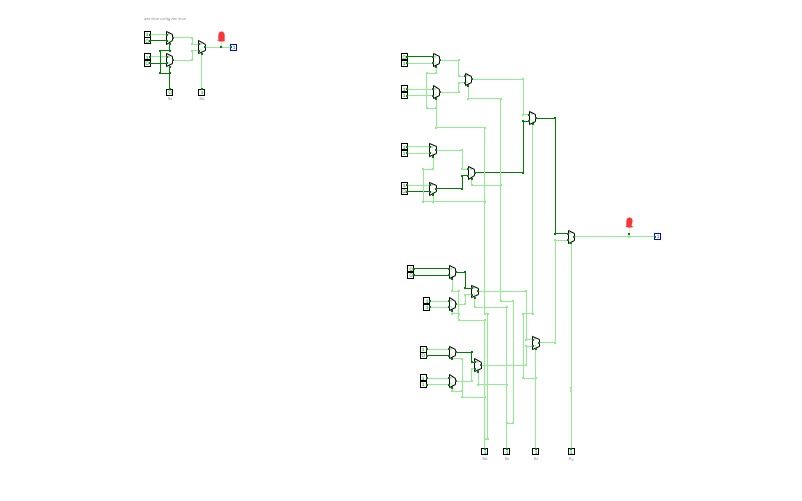

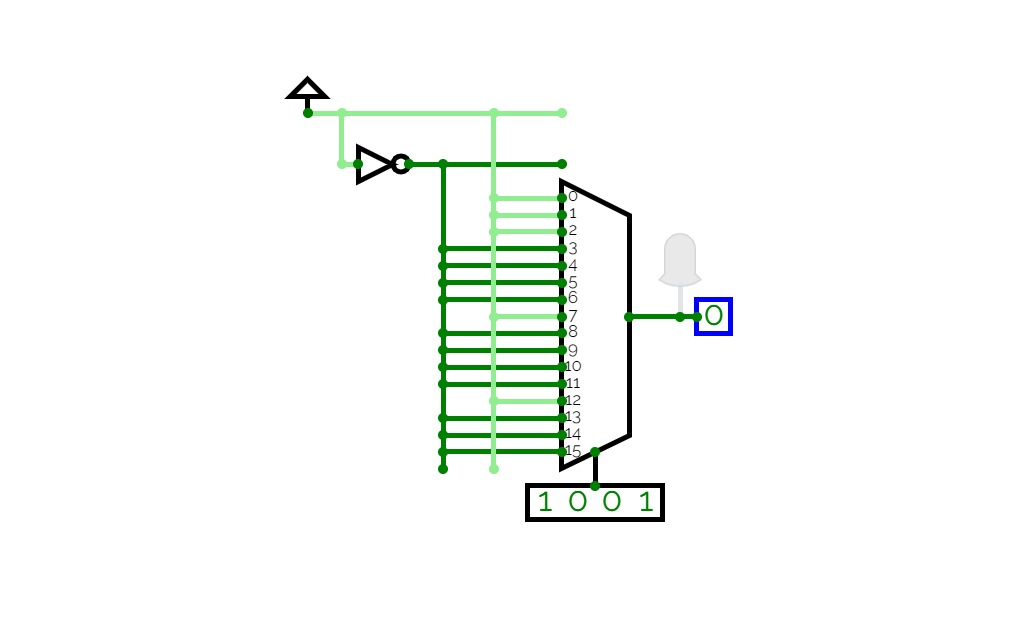

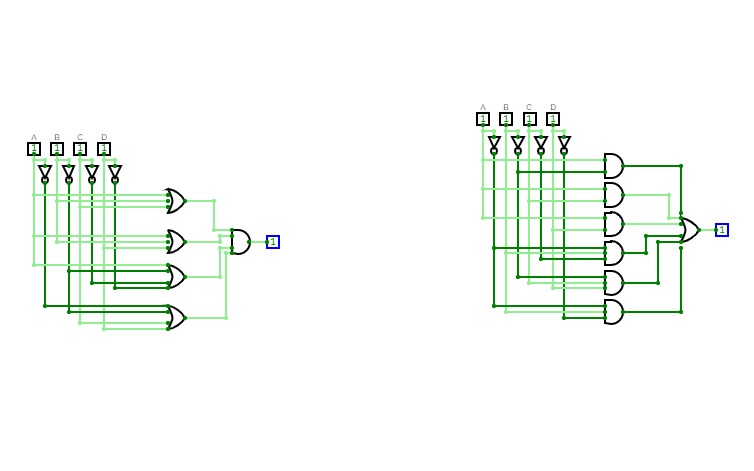

F = (ABC)+(A'B'CD)+(ABC'D')+(BD)

F = (ABC)+(A'B'CD)+(ABC'D')+(BD)

Untitled

Untitled

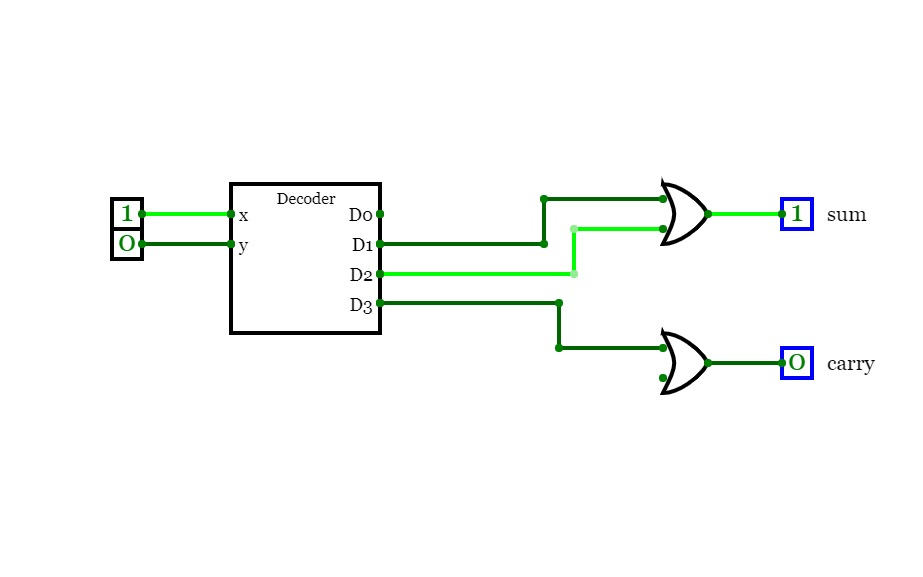

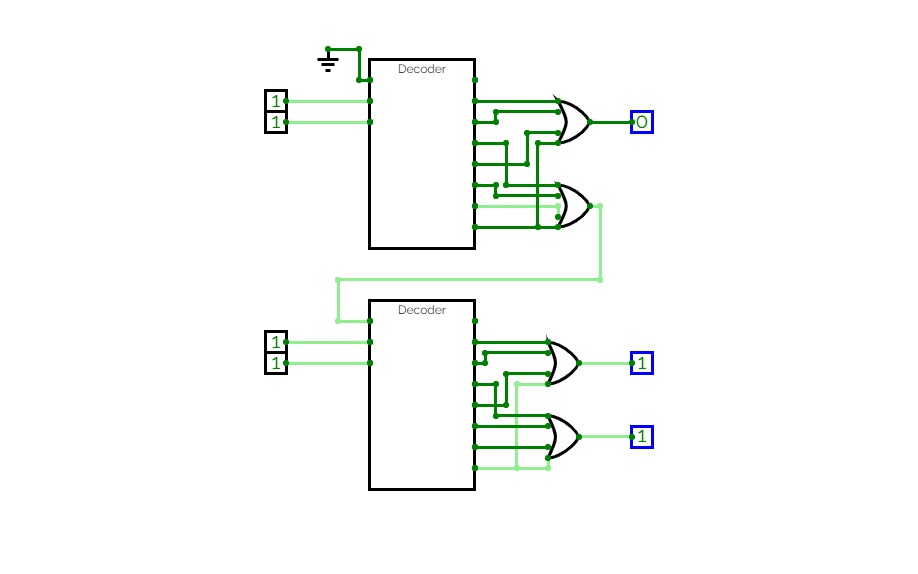

Half Adder using Decoder

Half Adder using Decoder

reg Decoder

reg Decoder

Adders using decoders

Adders using decoders

MUX VIVA1

MUX VIVA1

Viva--3--or-and

Viva--3--or-and

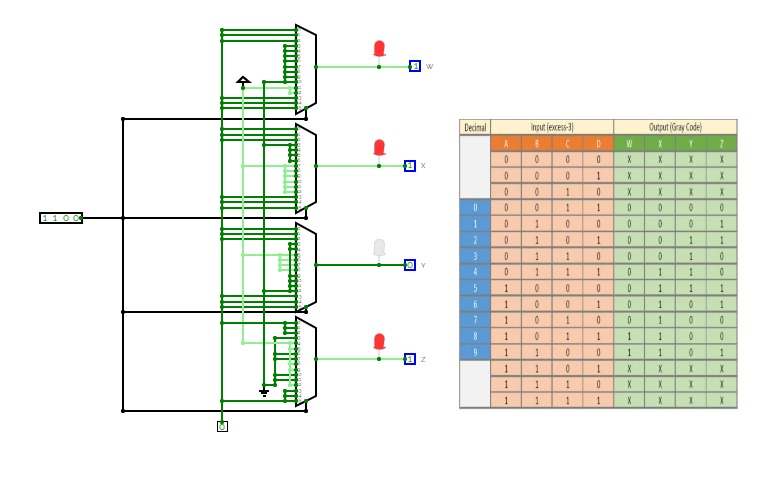

8:1MUX--XS-3--to--gray

8:1MUX--XS-3--to--gray

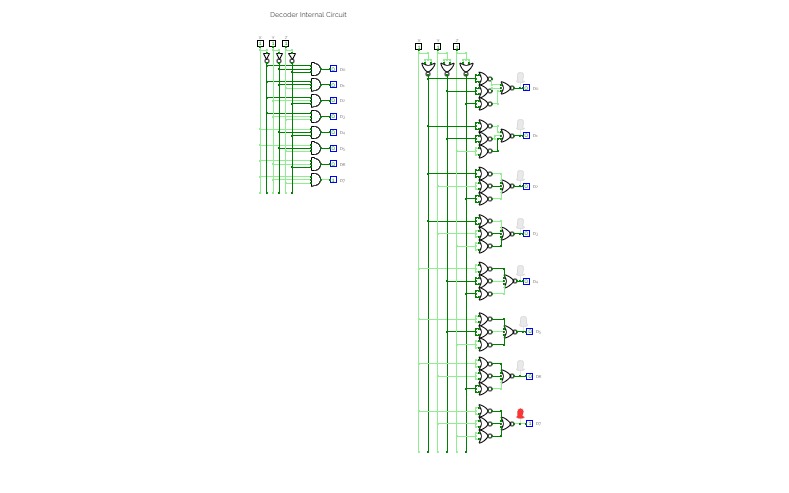

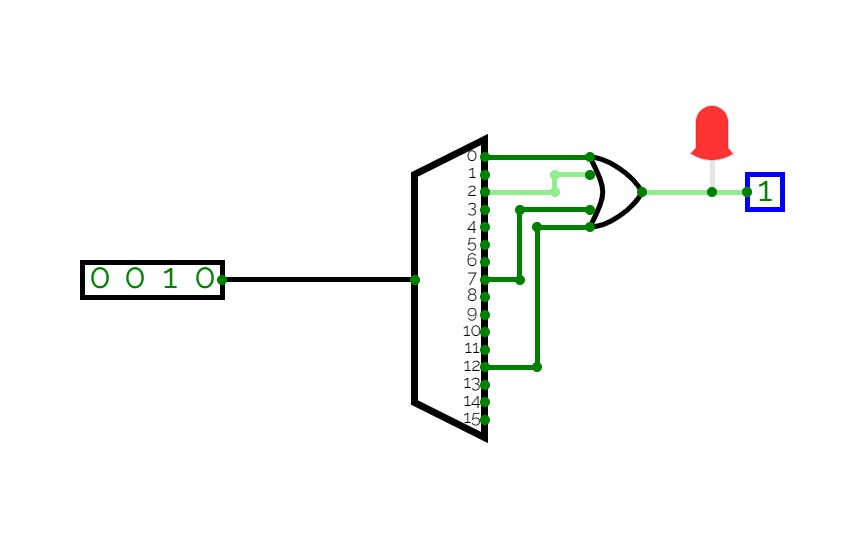

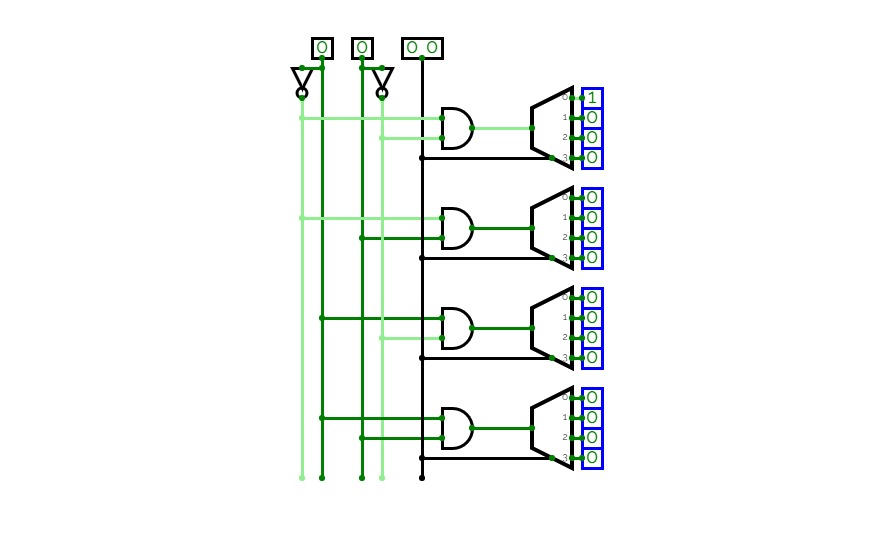

4:16 Decoder internal

4:16 Decoder internal

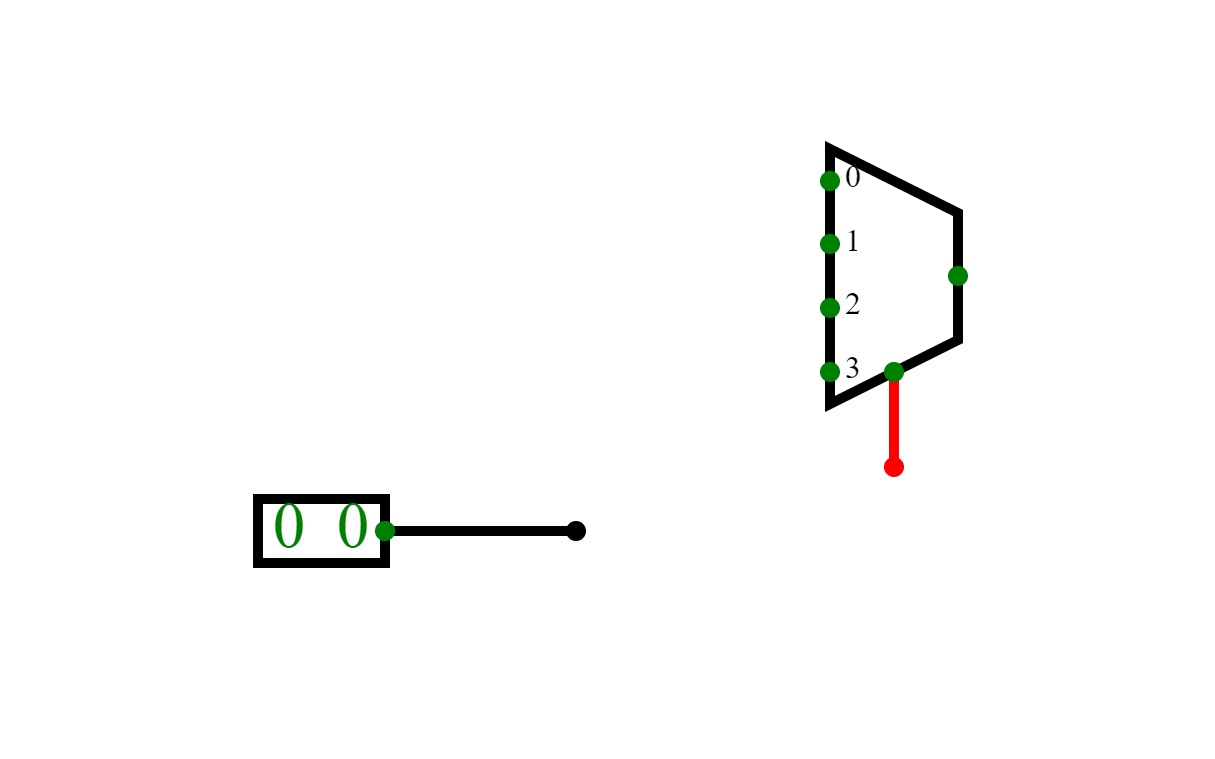

TASK-1

TASK-1

trrstrss

trrstrss

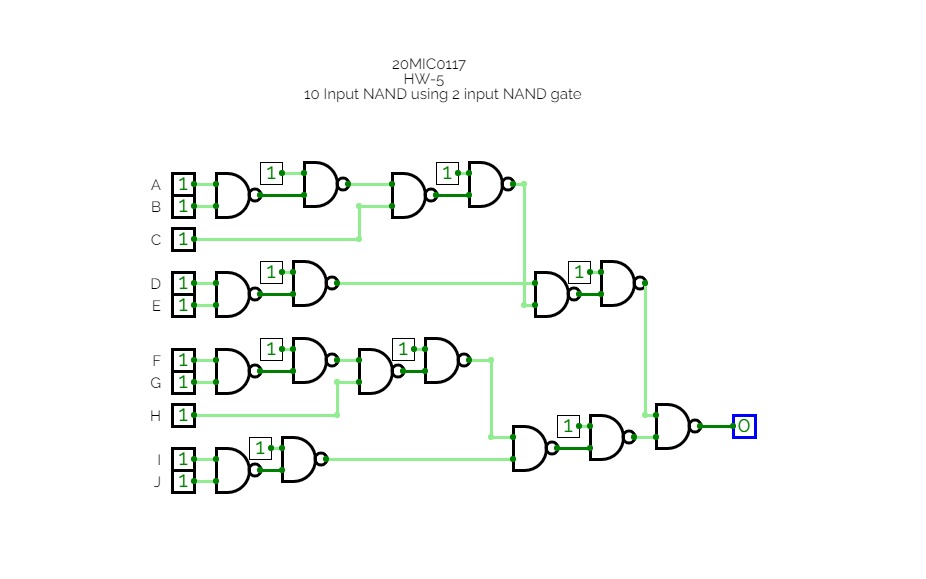

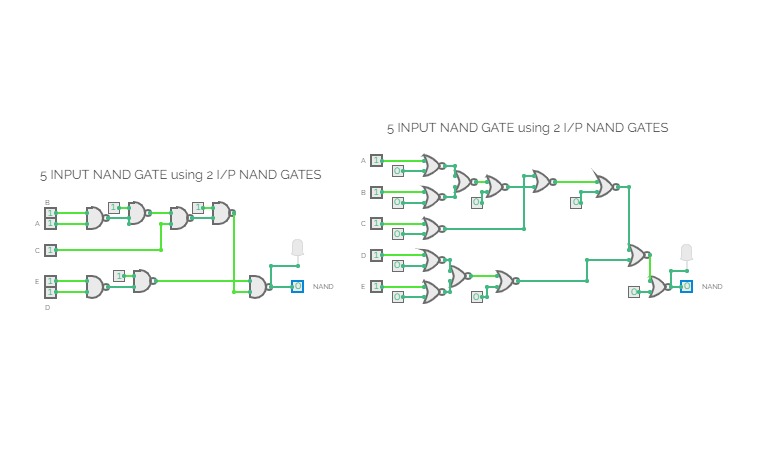

HW-5 == 10 input NAND gate using 2 input NAND

HW-5 == 10 input NAND gate using 2 input NAND

Untitled

Untitled

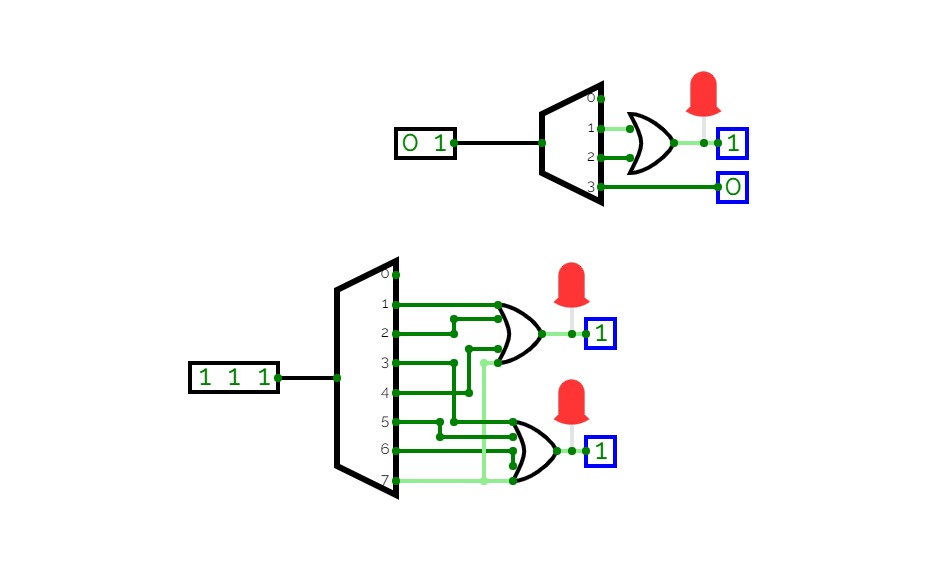

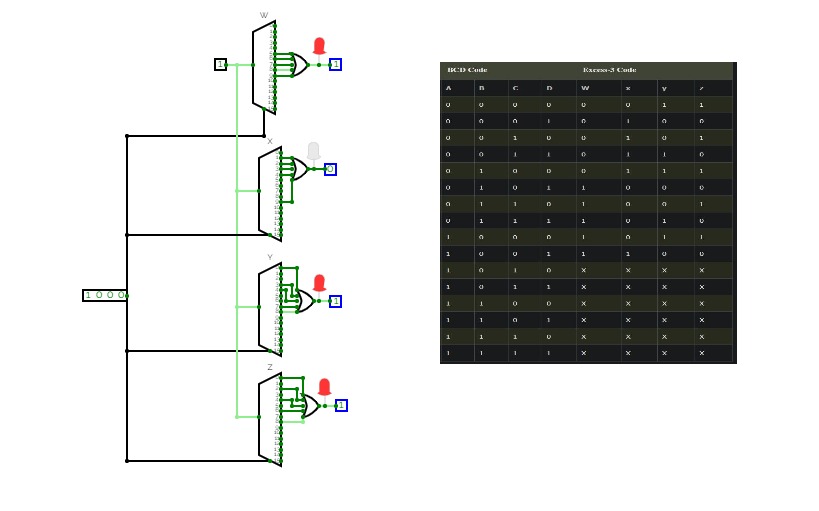

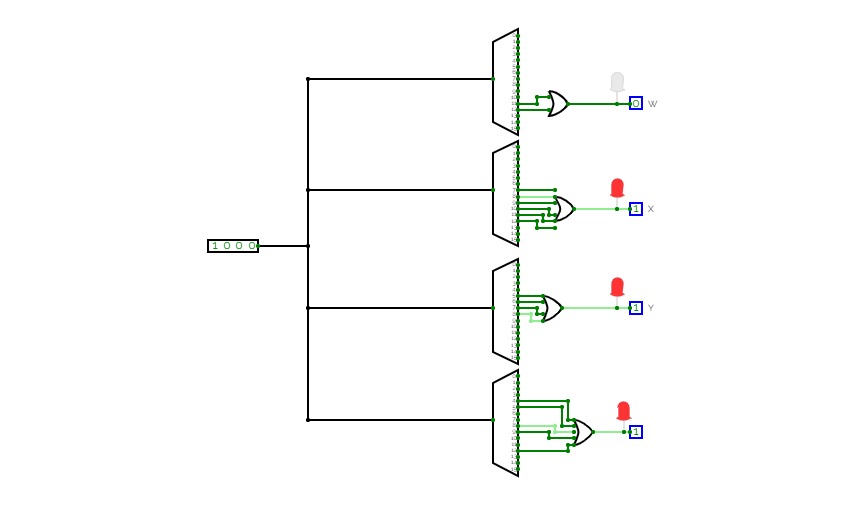

bcd to xs3 using 8:1 de-mux

bcd to xs3 using 8:1 de-mux

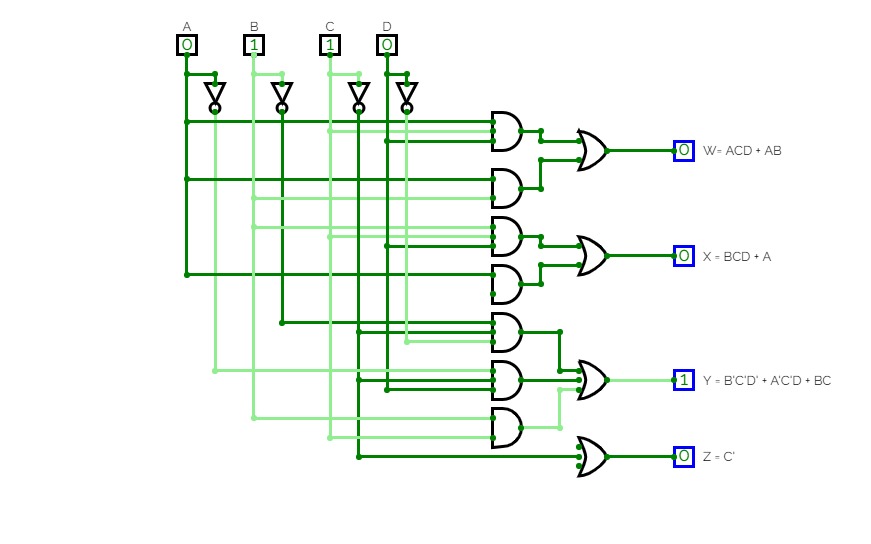

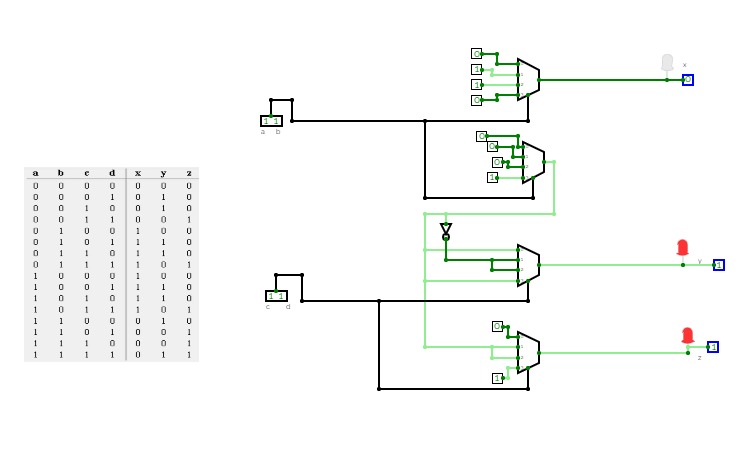

cat-1 q2

cat-1 q2

fat lab

fat lab

VIVA-3

VIVA-3

task-3 --q-1

task-3 --q-1

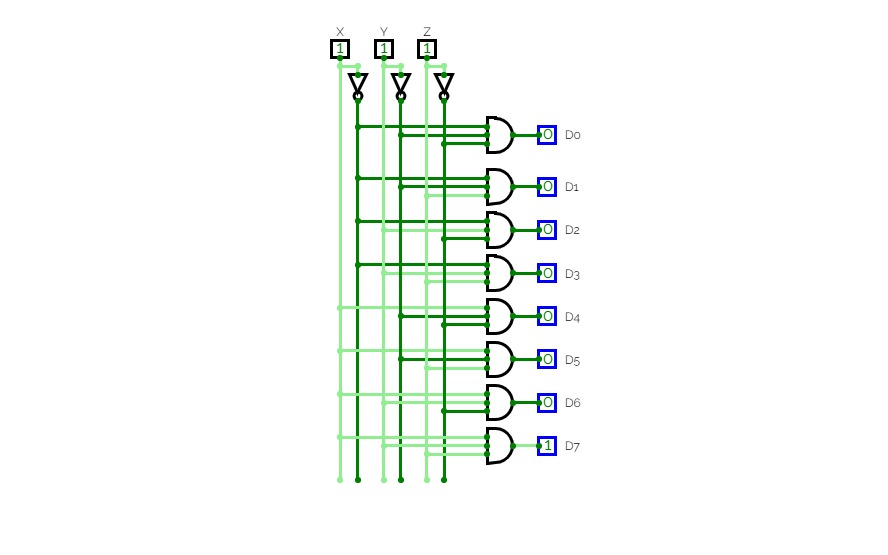

decoder

decoder

Untitled

Untitled

task-3--2

task-3--2

TASK5

TASK5

cat 2 q1 a

cat 2 q1 a

Task-3-1

Task-3-1

Task3

Task3

MUX VIVA1

MUX VIVA1

VIVA-4 -- AND & OR

VIVA-4 -- AND & OR

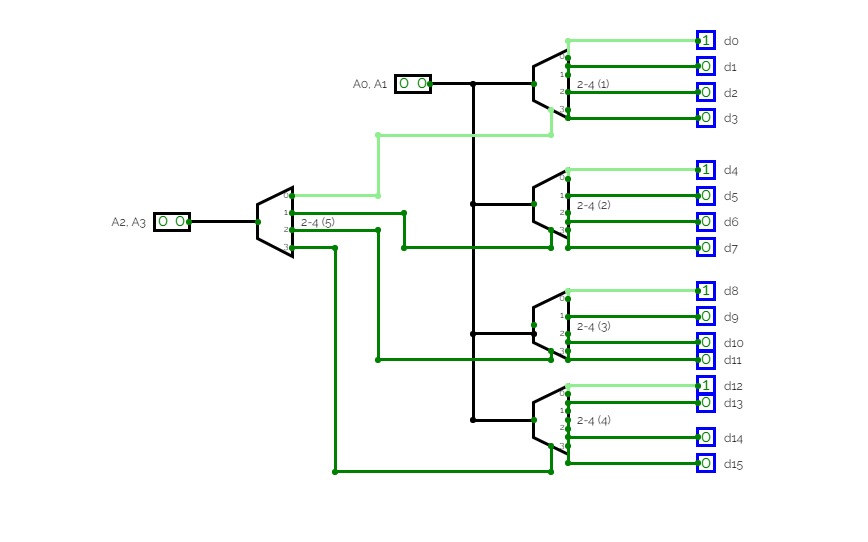

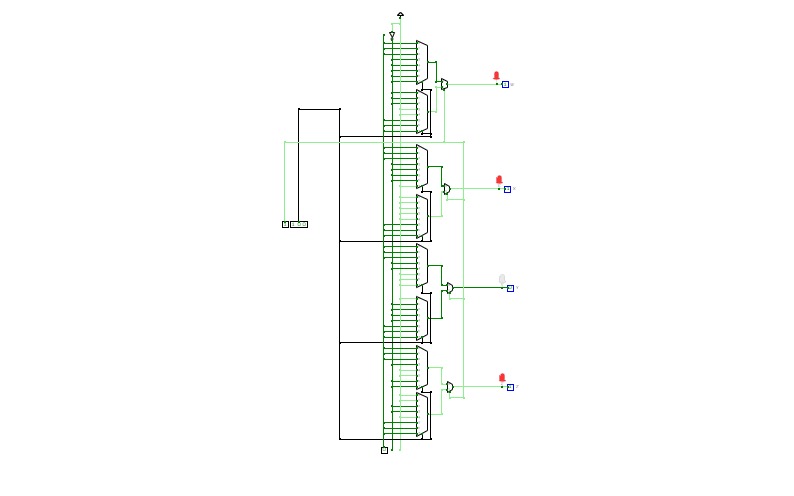

4:16 DECODER USING 2:4 DECODER

4:16 DECODER USING 2:4 DECODER

16:1

16:1

8:1

8:1

4:16 decoder using 3:8 Active high SOP and POS using 3:8 decoder:

4:16 decoder using 3:8 Active high SOP and POS using 3:8 decoder:

VIVA 5 HW NAND \ NOR GATES

VIVA 5 HW NAND \ NOR GATES

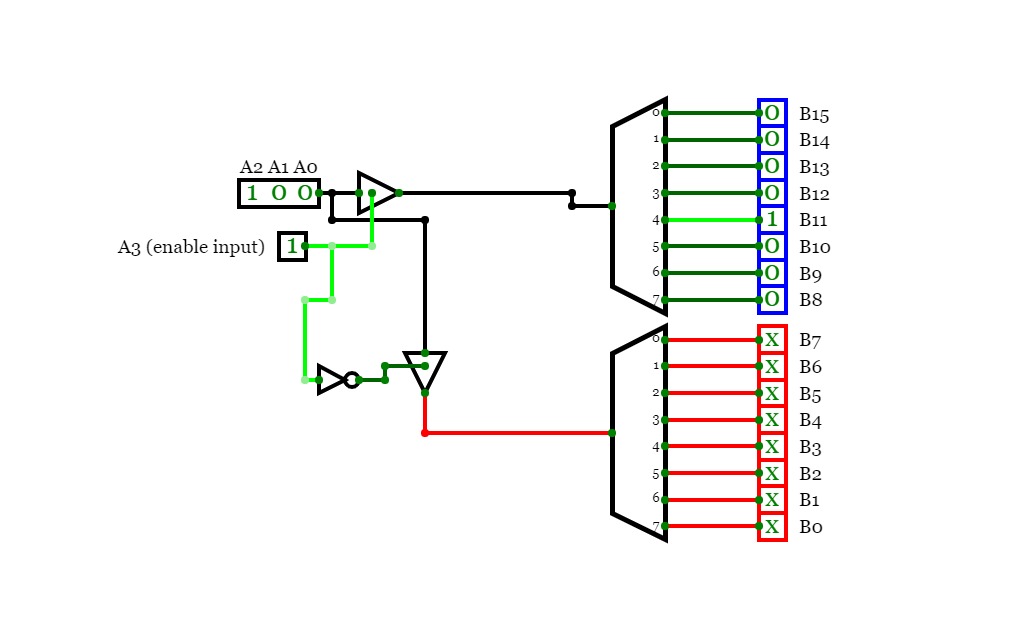

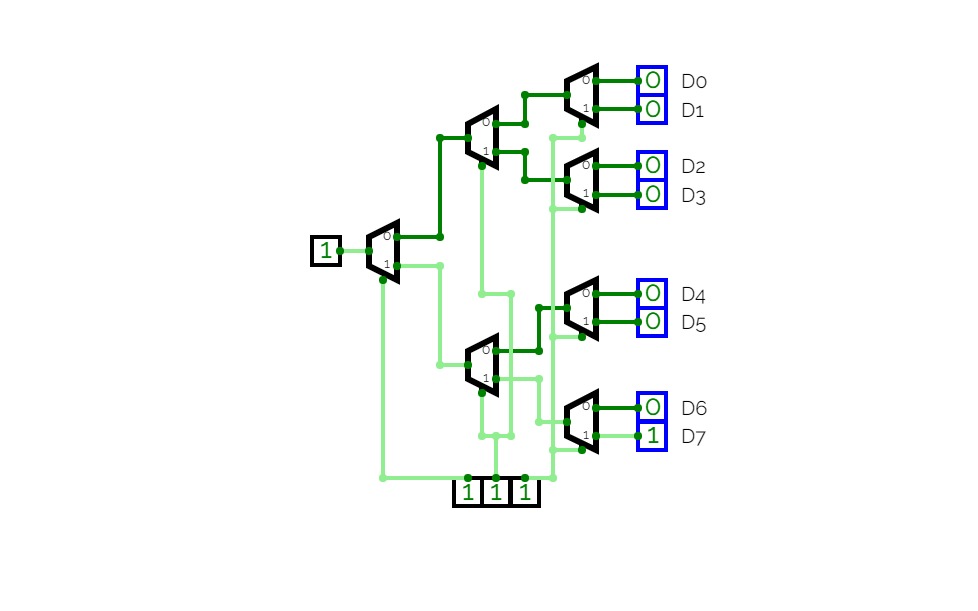

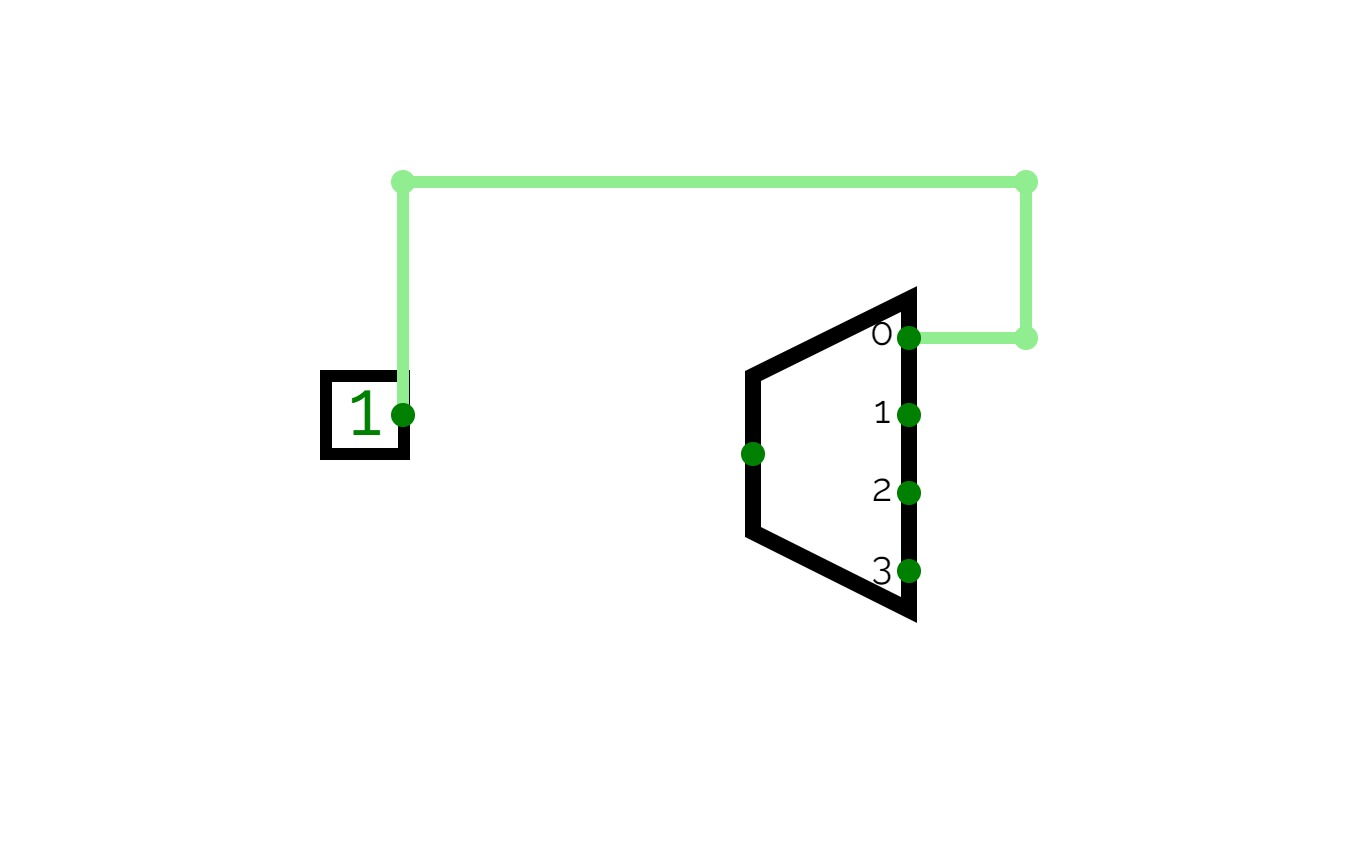

1:8 Demux using 1:2 Demux

1:8 Demux using 1:2 Demux

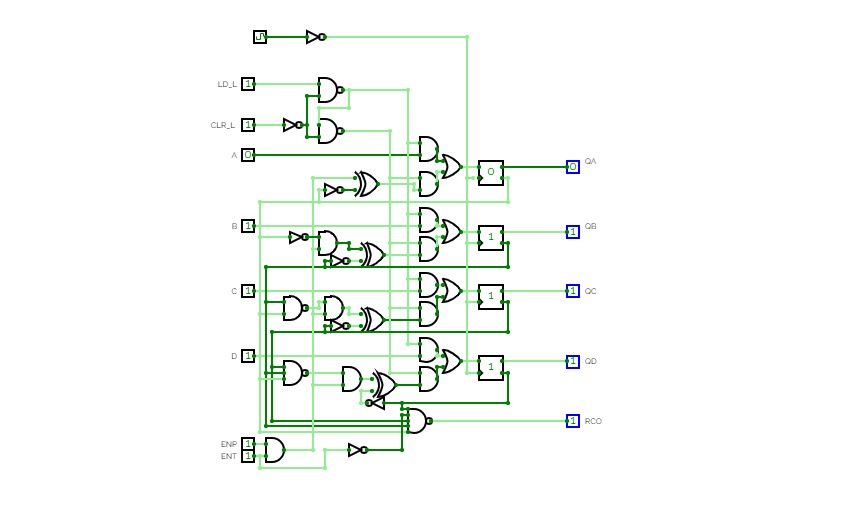

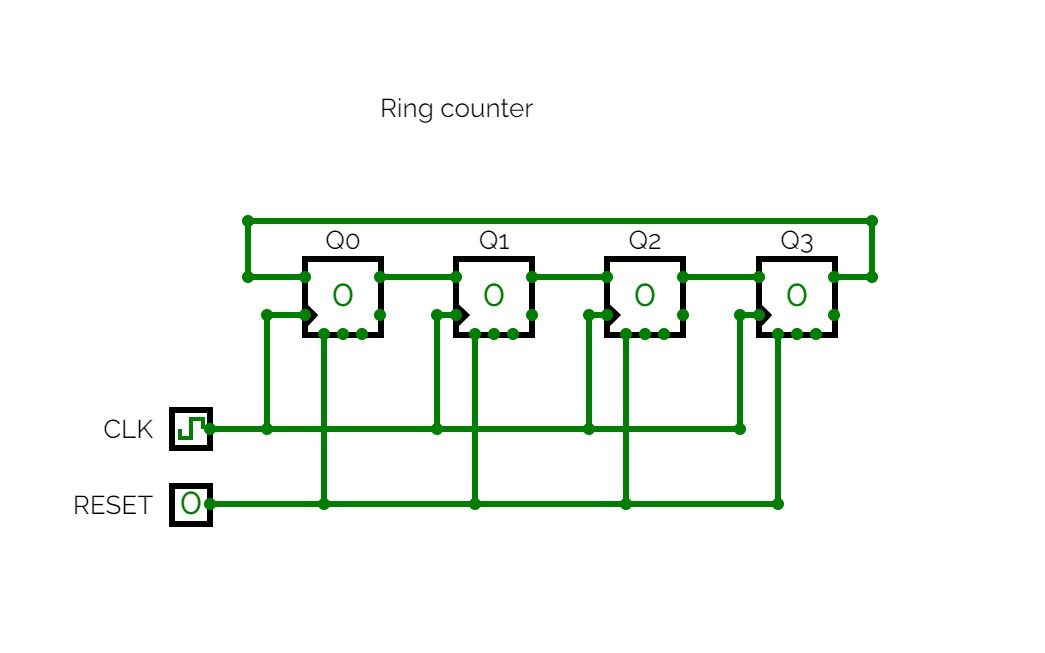

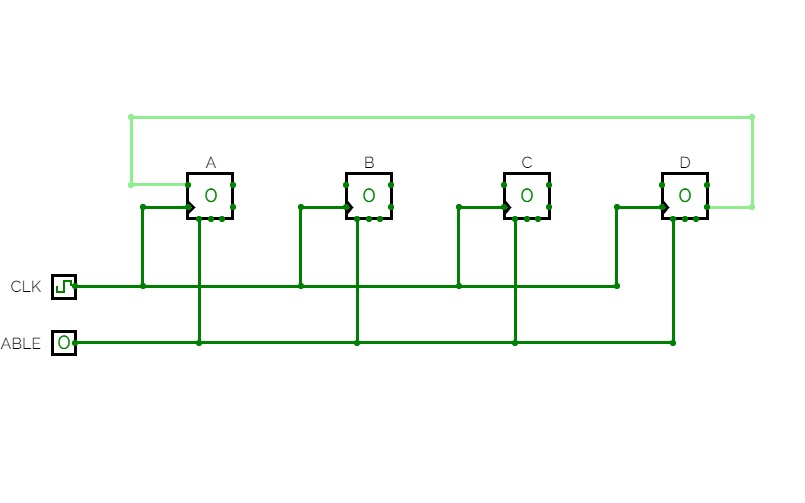

Ring counter

Ring counter

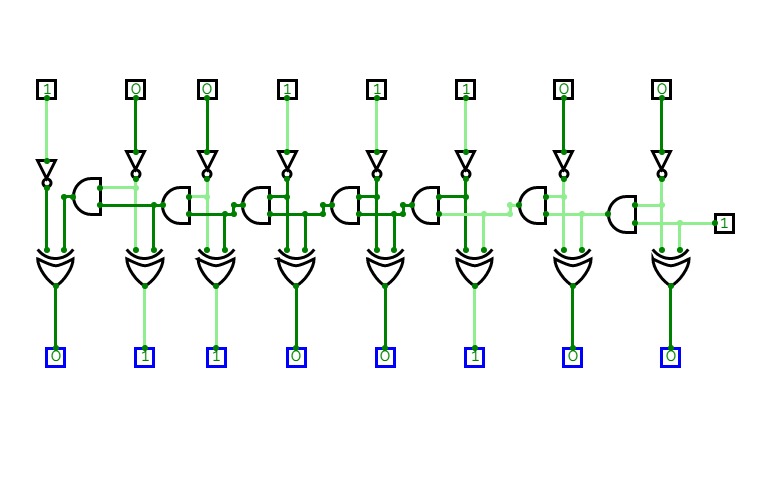

2's Complement

2's Complement

Task2

Task2

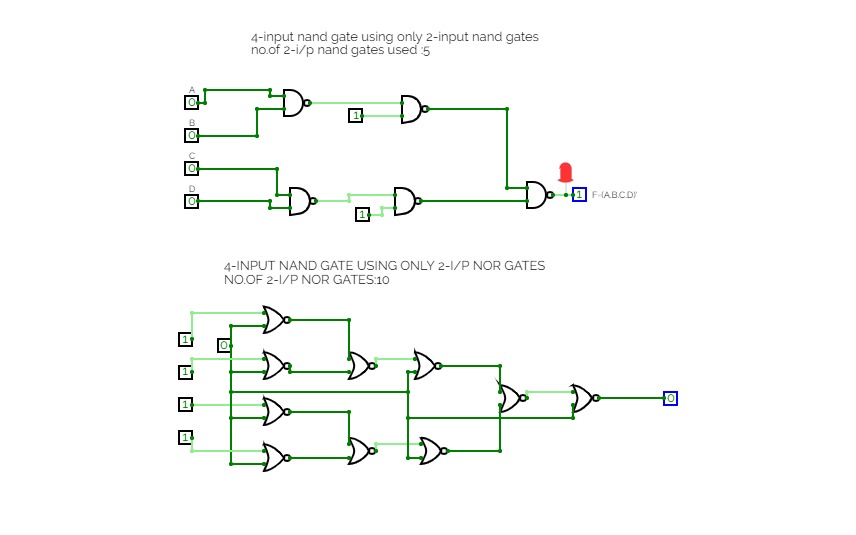

4 input nand gate

4 input nand gate

Decoder-VIVA2

Decoder-VIVA2

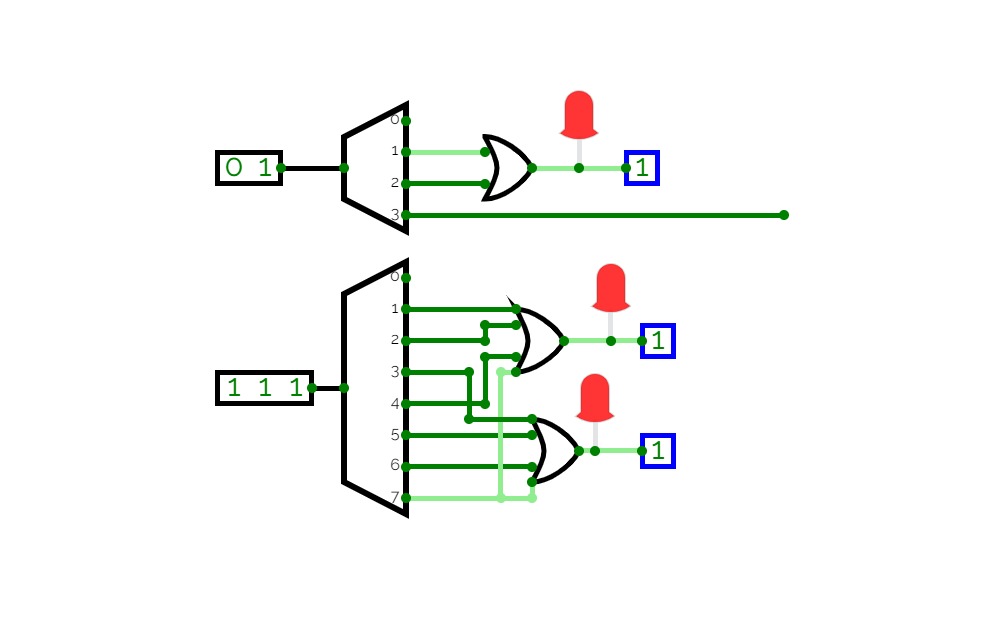

3:8 Decoder

3:8 Decoder

XS-3 to Gray using decoder

XS-3 to Gray using decoder

Ring and Johnson Counter

Ring and Johnson Counter

4:16 decoder using 2:4 decoders

4:16 decoder using 2:4 decoders