Pranita

Member since: 3 years

Educational Institution: Not Entered

Country: Not Entered

VIVA 5

VIVA 5

VIVA 2

VIVA 2

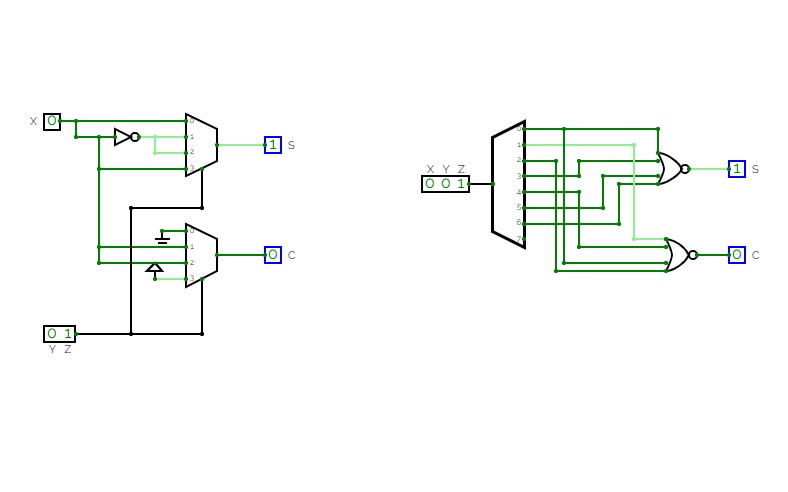

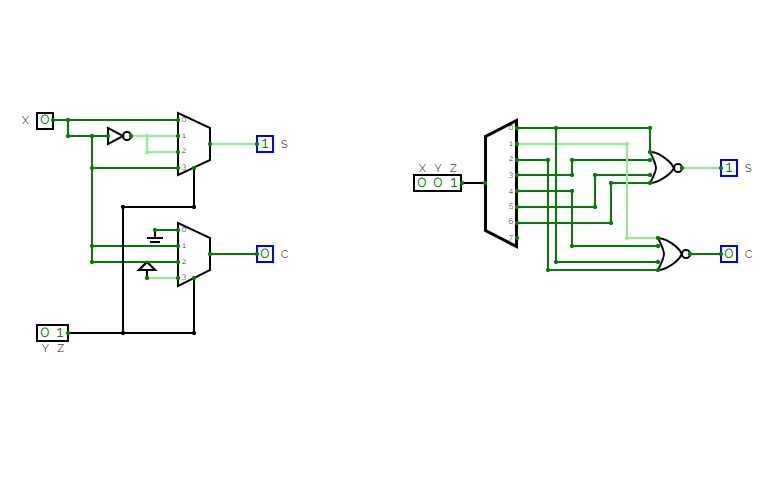

VIVA 1

VIVA 1

VIVA 3

VIVA 3

VIVA 4

VIVA 4

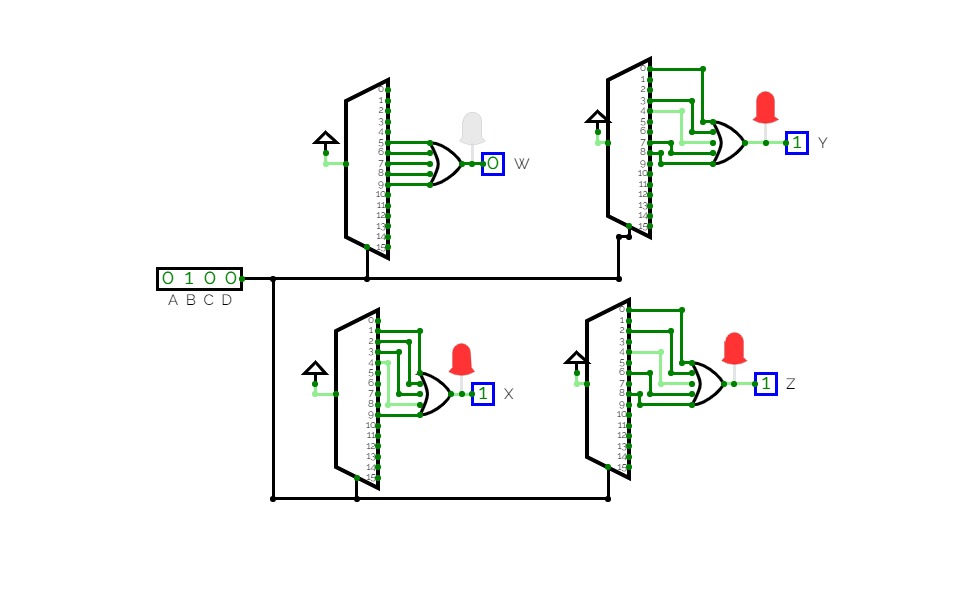

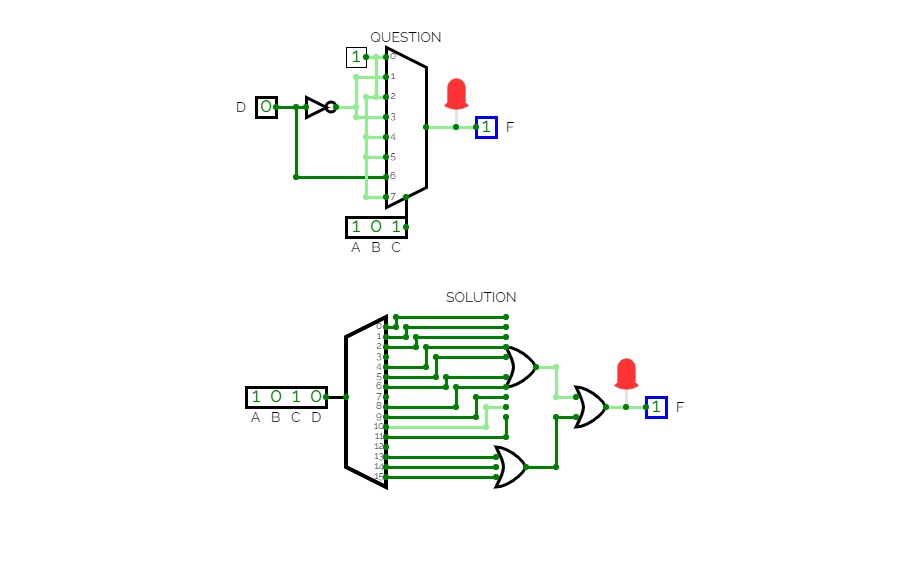

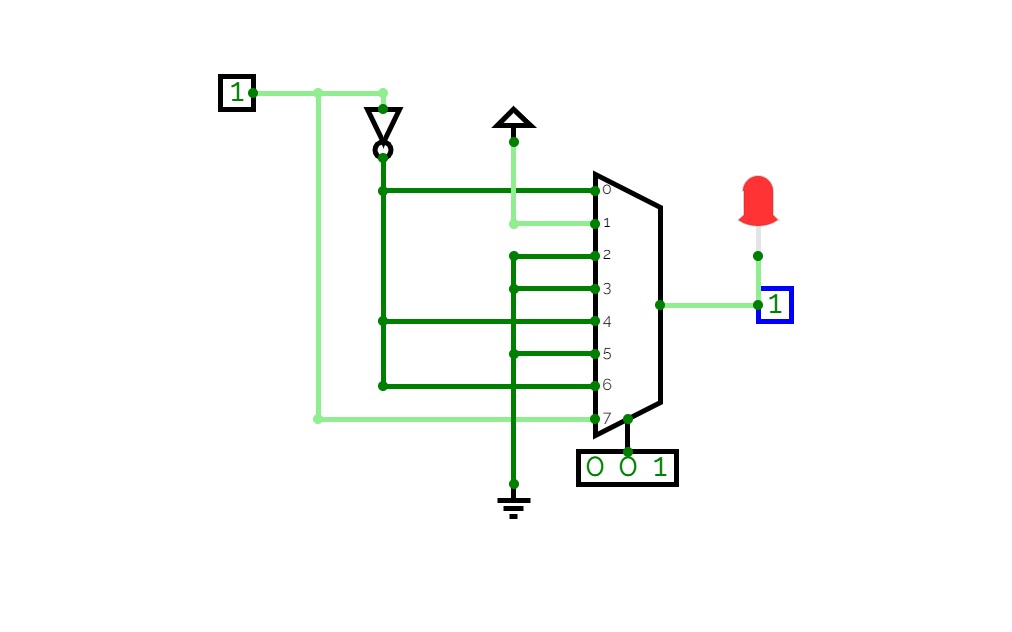

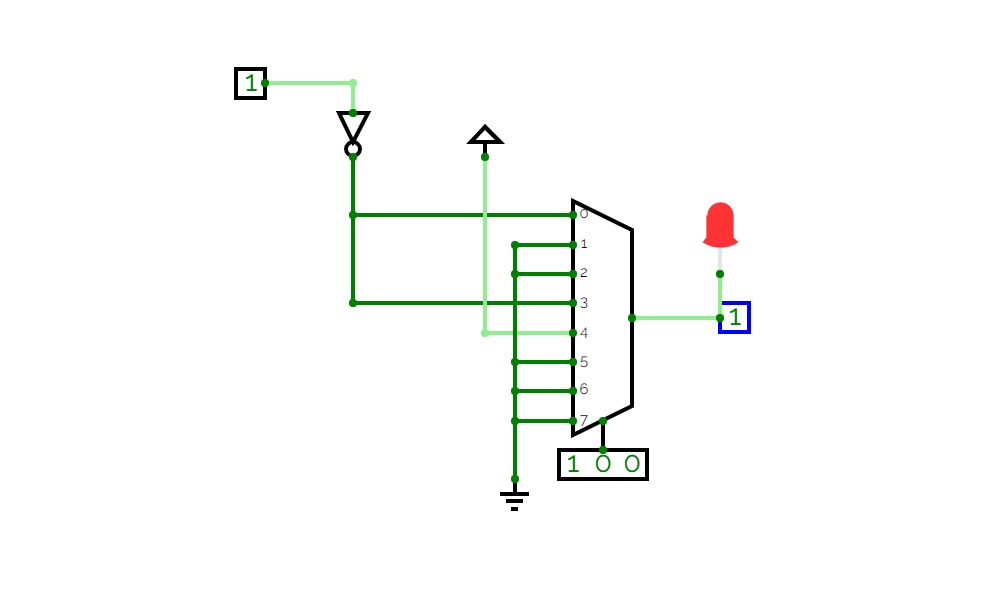

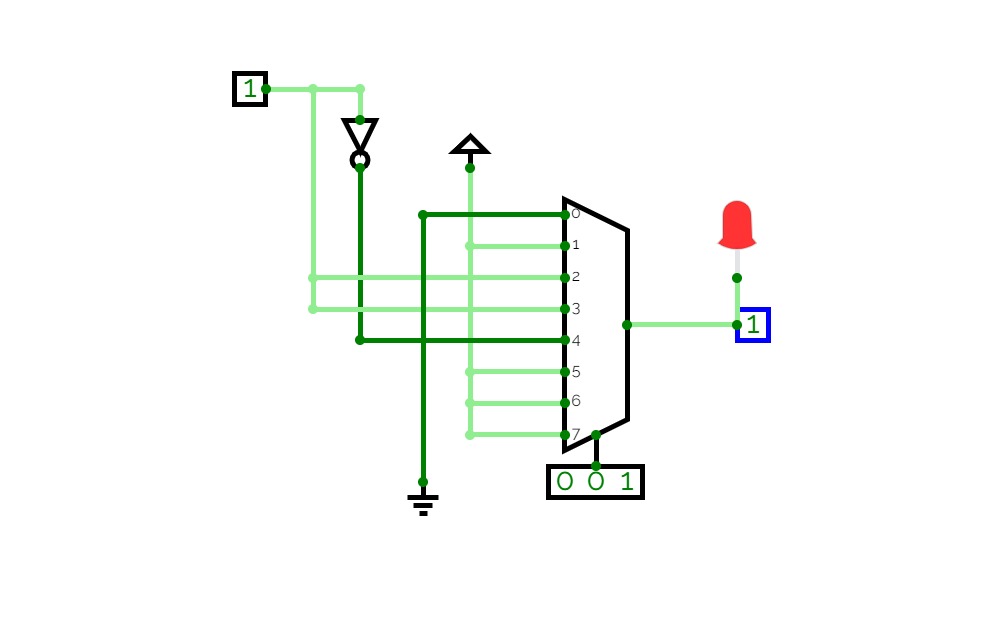

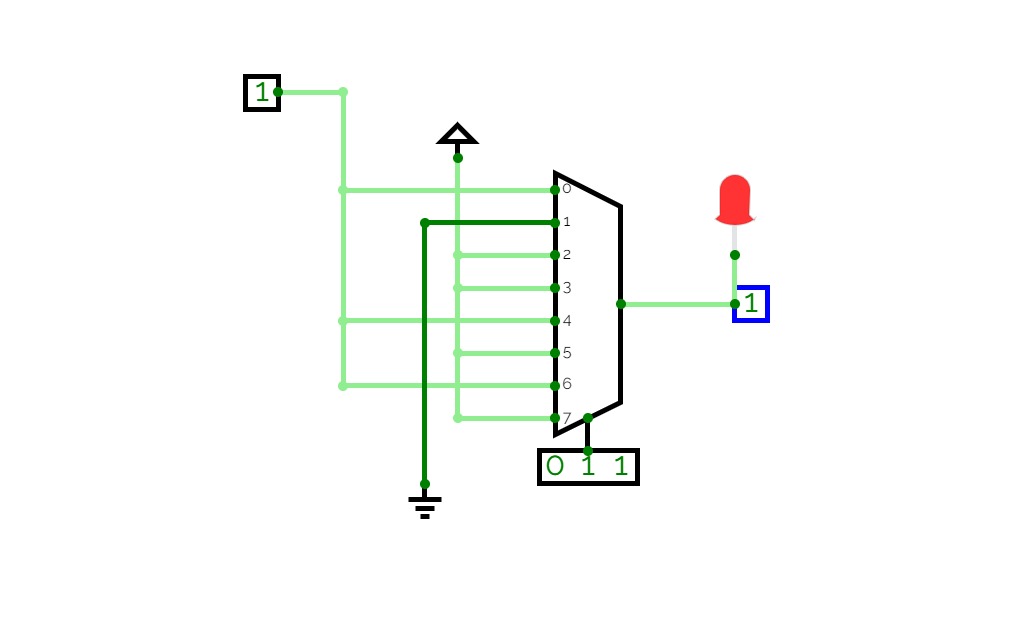

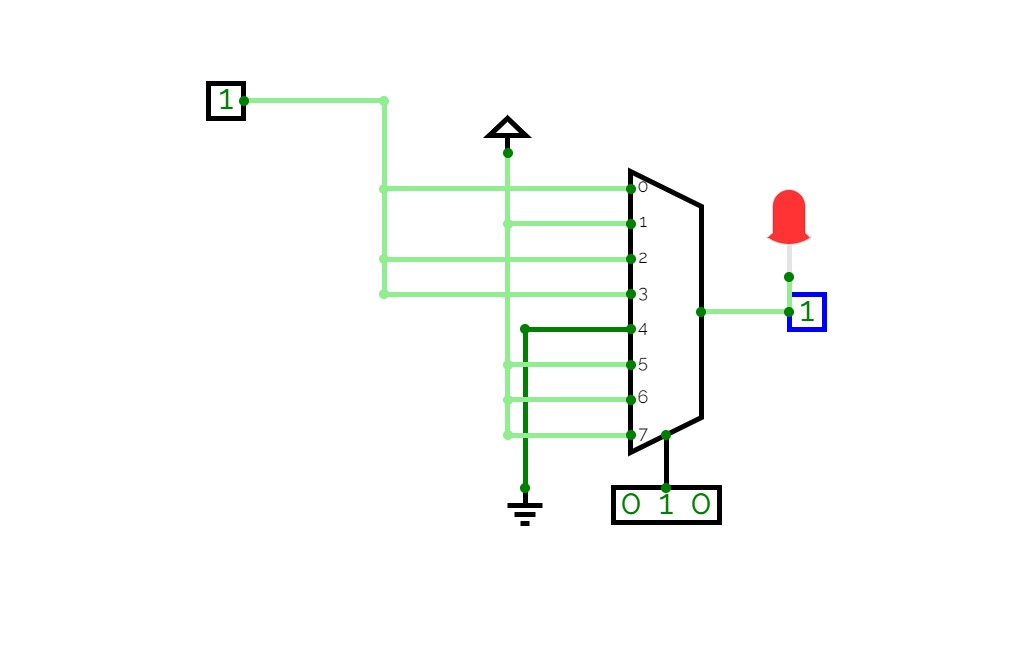

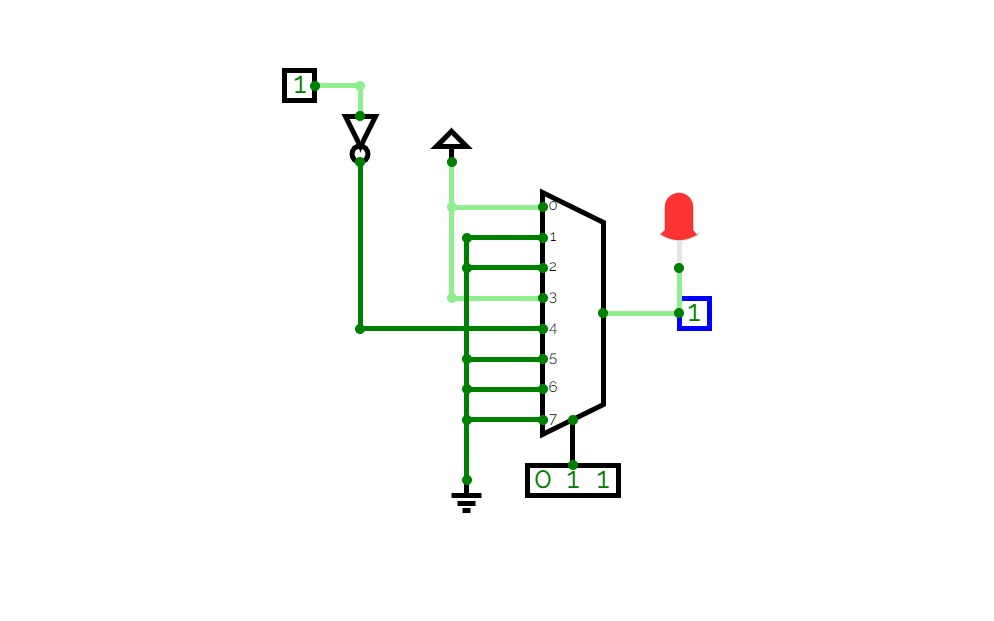

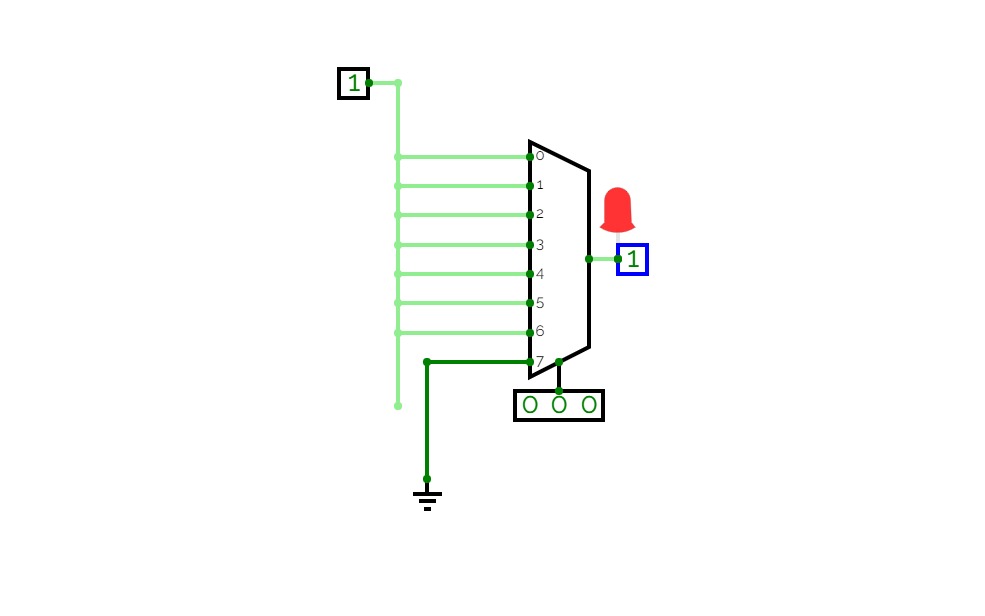

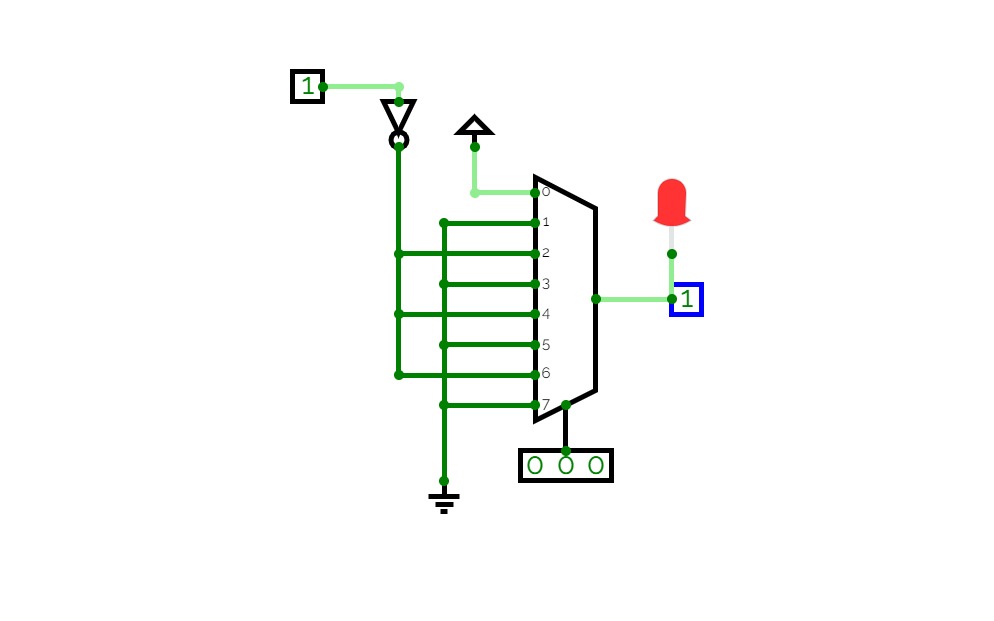

BCD to excess 3 code using 1:8 DEMUX

BCD to excess 3 code using 1:8 DEMUX

BCD to excess 3 code using 1:8 DEMUX

BCD to excess 3 code using 1:8 DEMUX

cat ans

cat ans

CAT ANS 2

CAT ANS 2

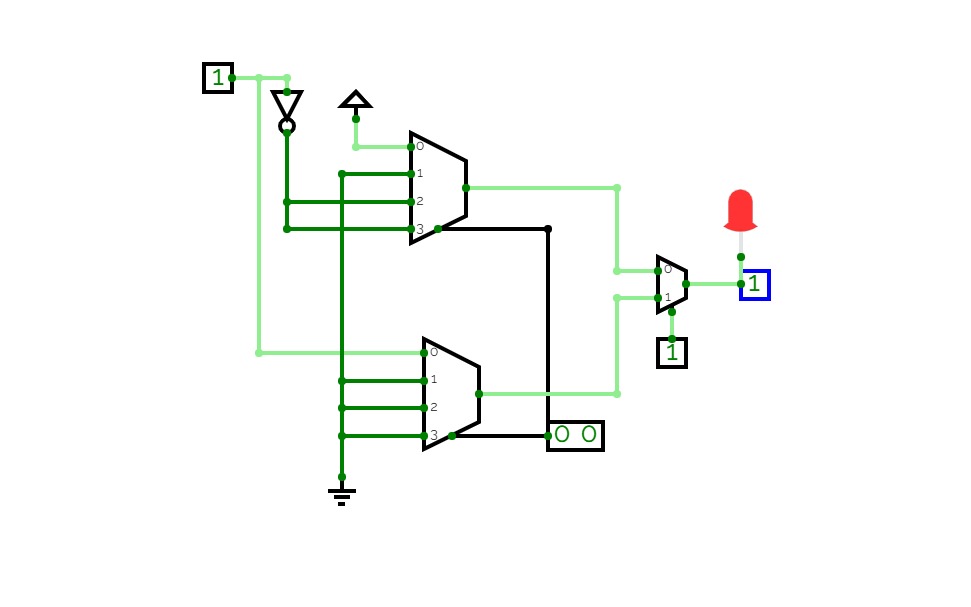

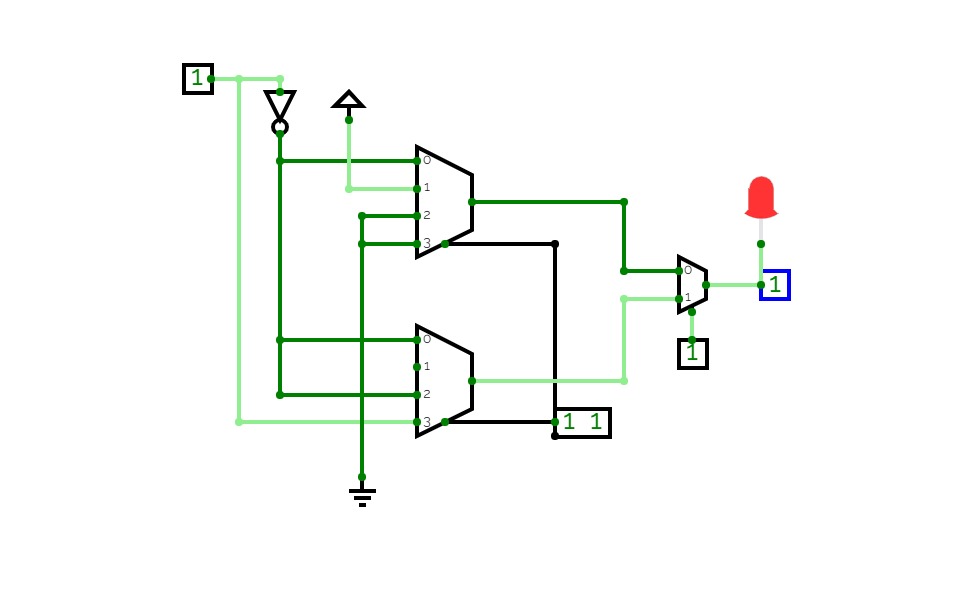

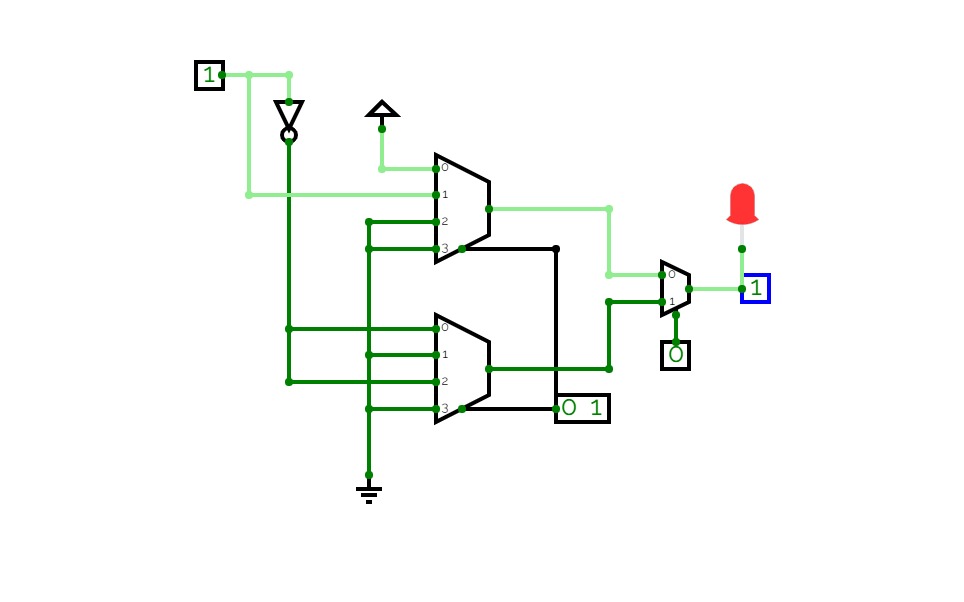

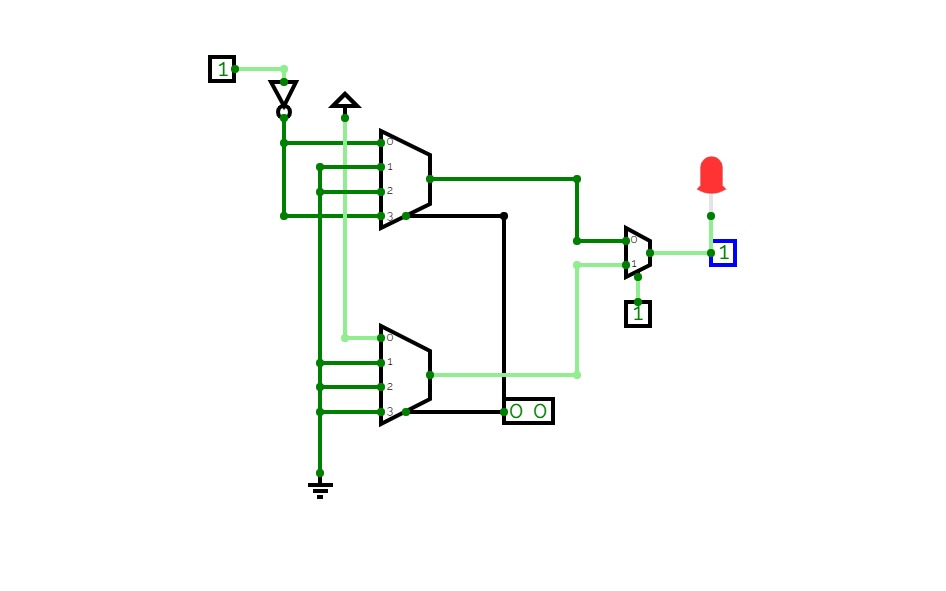

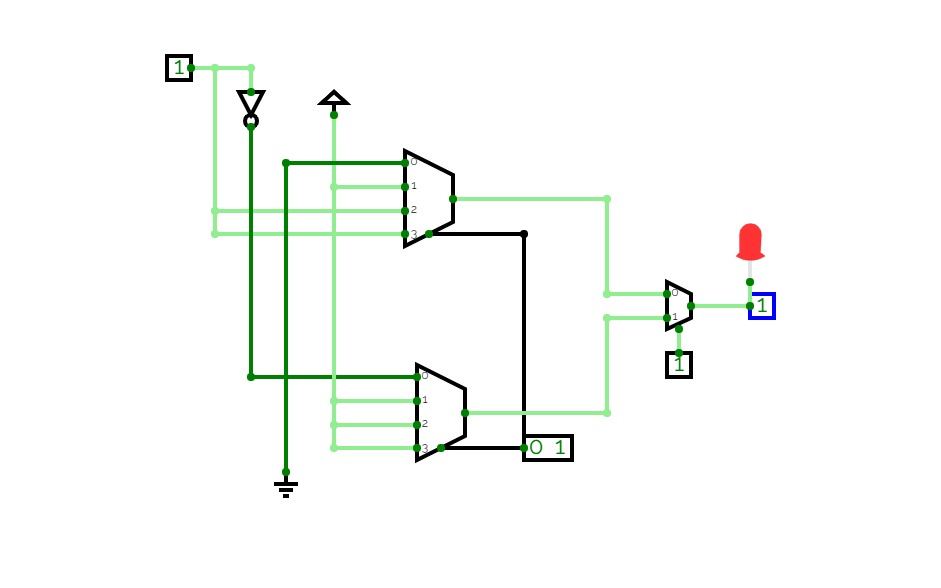

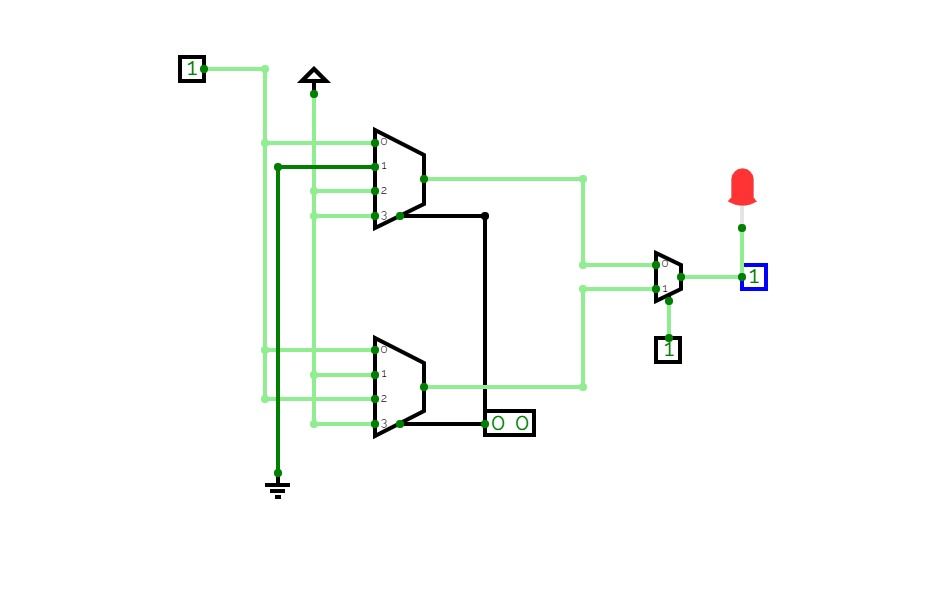

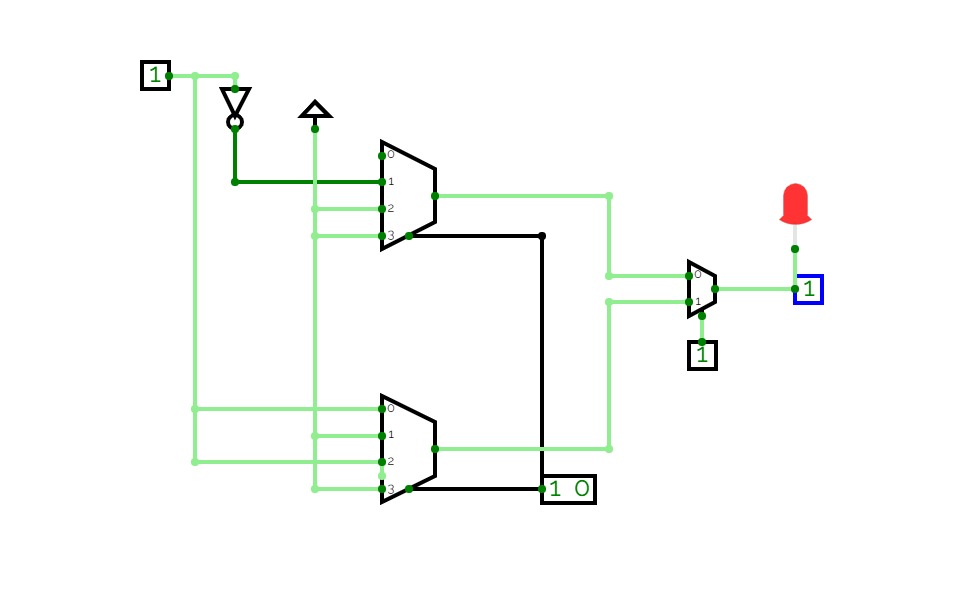

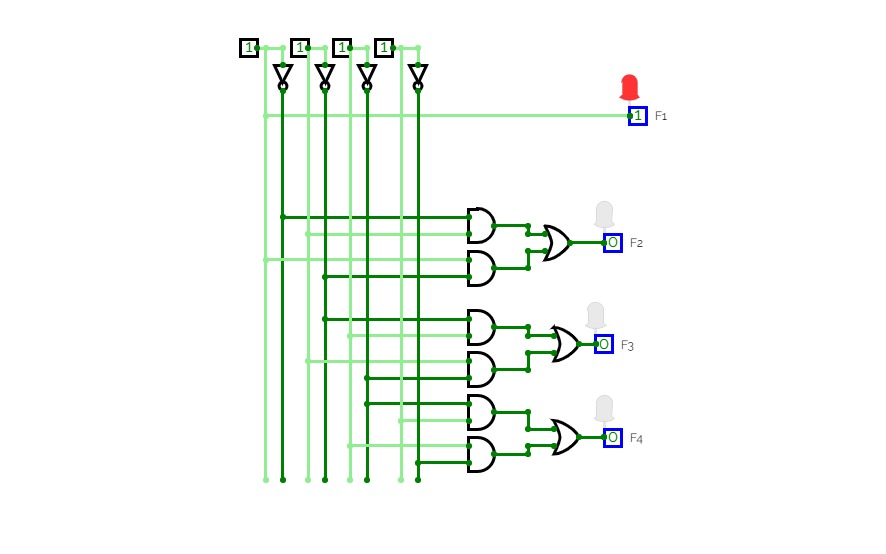

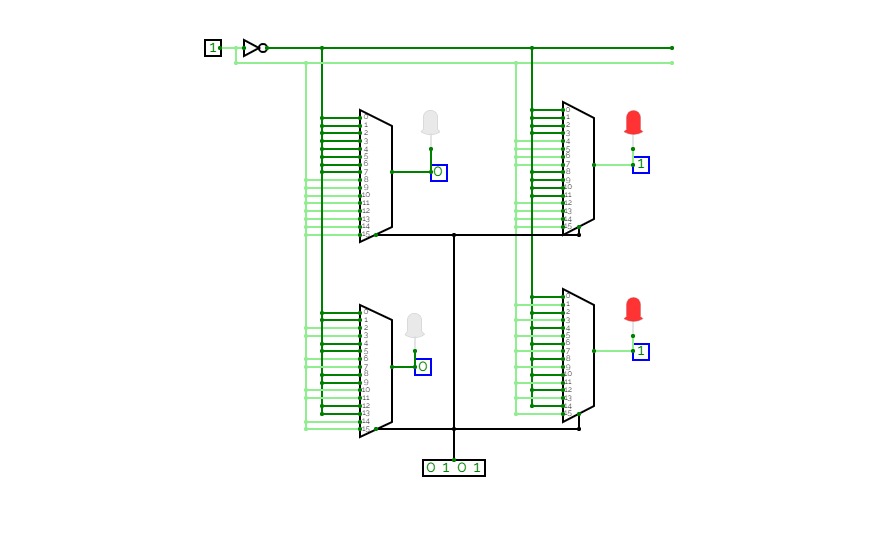

CAT.: DUAL MUX

CAT.: DUAL MUX

CAT ANS 3

CAT ANS 3

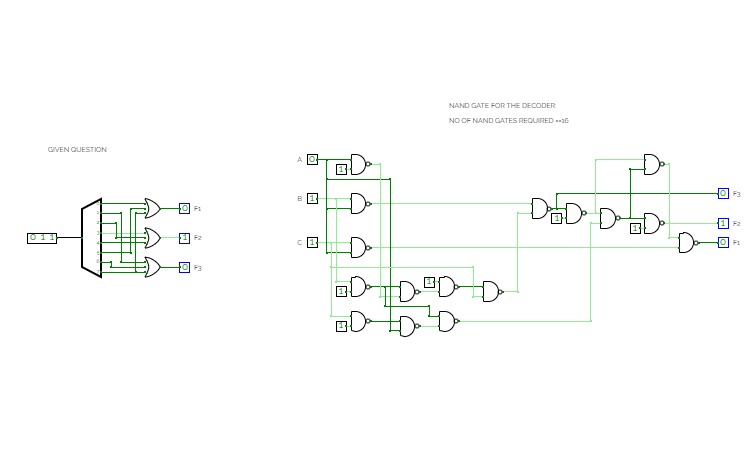

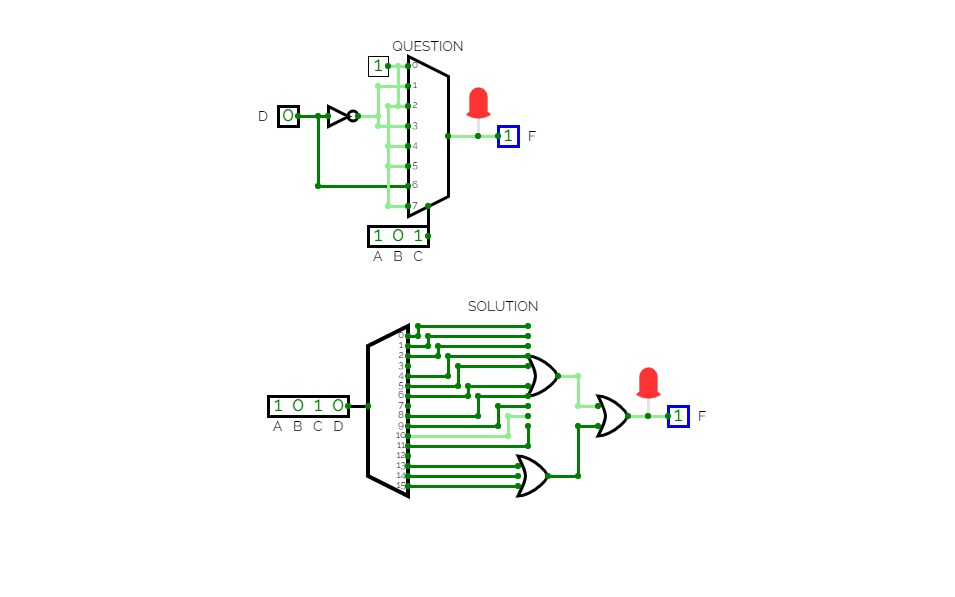

CAT. : IMPLELEMENT FROM DECODER

CAT. : IMPLELEMENT FROM DECODER

CAT: implement the equation using decoder

CAT: implement the equation using decoder

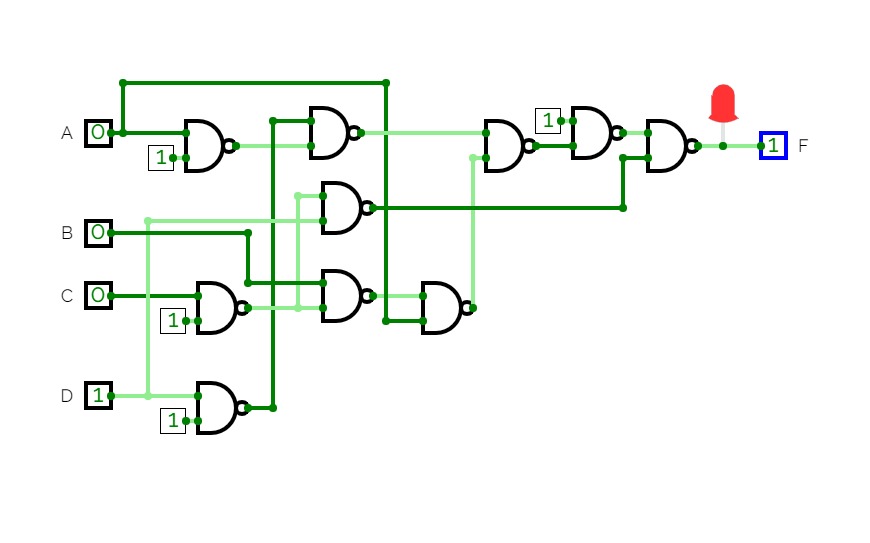

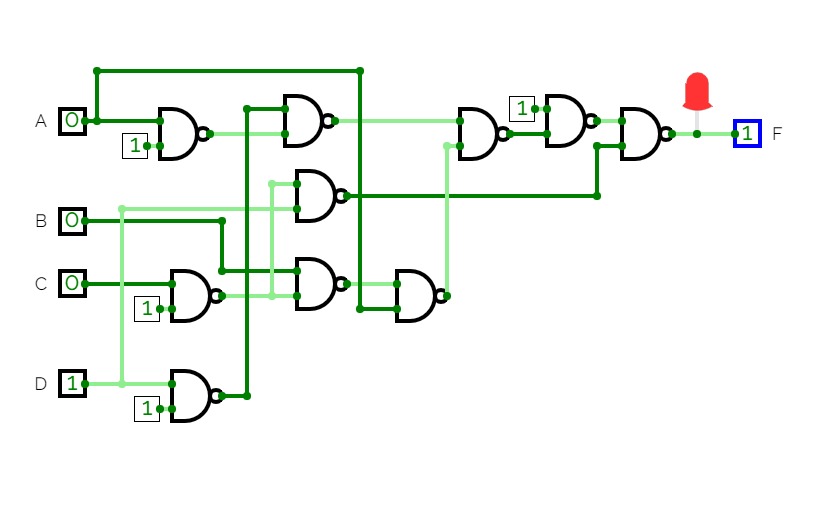

CAT ANS 4

CAT ANS 4

CAT: design the internal structure of Circuit given using NAND gates.

CAT: design the internal structure of Circuit given using NAND gates.

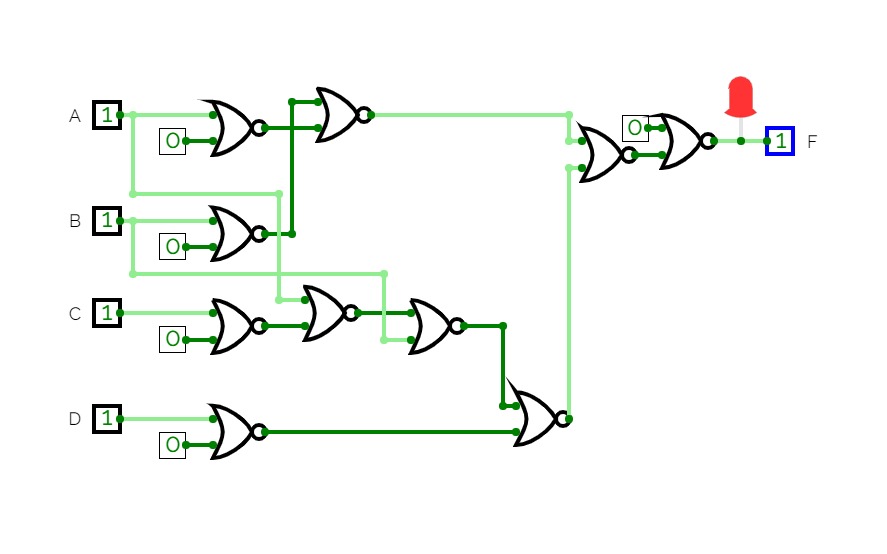

CAT ANS 5

CAT ANS 5

CAT AND 6

CAT AND 6

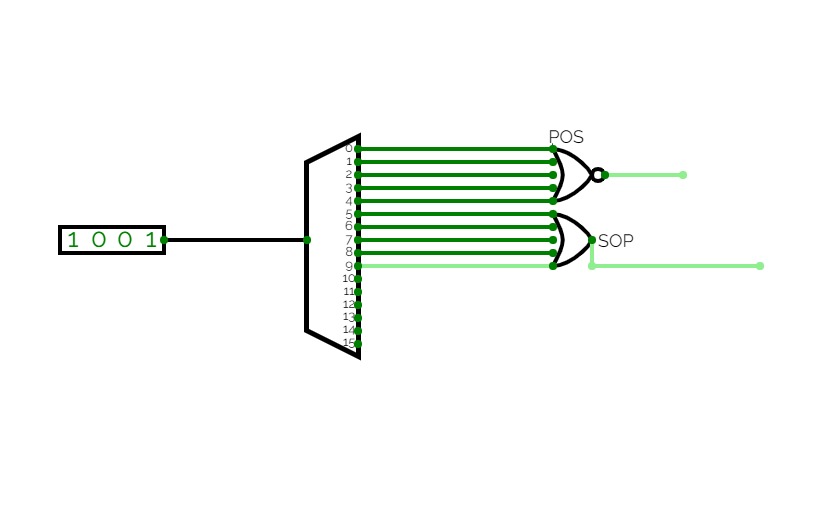

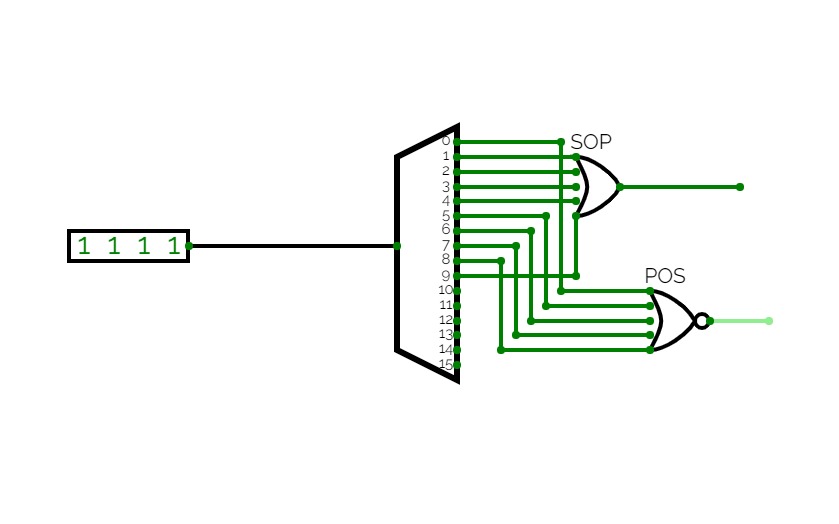

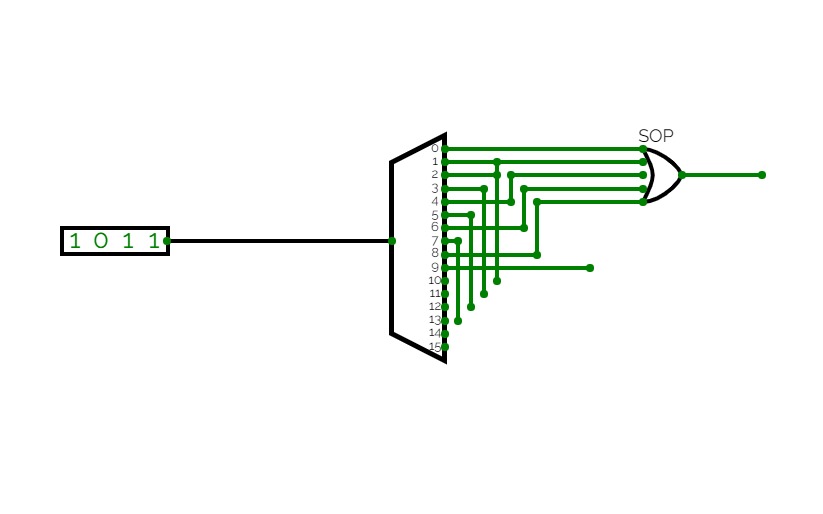

16X1 MUX REG NO. SOP F'

16X1 MUX REG NO. SOP F'

16X1 MUX SOP F'

16X1 MUX SOP F'

8X1 SOP BCD LINES

8X1 SOP BCD LINES

4X1 SOP BCD LINES

4X1 SOP BCD LINES

8X1 MUX SOP ABC LINE

8X1 MUX SOP ABC LINE

4X1 MUX ABC LINE

4X1 MUX ABC LINE

8X1 ABD LINE MUX

8X1 ABD LINE MUX

8X1 MUX ACD LINES

8X1 MUX ACD LINES

4X1 ABD LINES MUX

4X1 ABD LINES MUX

4X1 MUX ACD LINES

4X1 MUX ACD LINES

8X1 MUX BCD LINES

8X1 MUX BCD LINES

BCD LINES MUX F'

BCD LINES MUX F'

ABC LINES MUX F'

ABC LINES MUX F'

ABC LINE 4X1 F'

ABC LINE 4X1 F'

ABD 8X1 LINE F'

ABD 8X1 LINE F'

ABD LINE 4 MUC F'

ABD LINE 4 MUC F'

ACD 8X1 MUX LINE F'

ACD 8X1 MUX LINE F'

ACD 4X1 LINE F'

ACD 4X1 LINE F'

8X1 BCD TO EXCESS 3 CODE CONVERTER

8X1 BCD TO EXCESS 3 CODE CONVERTER

8X1 BCD TO EX 3 ABC LINE

8X1 BCD TO EX 3 ABC LINE

8X1 BCD TO EX 3 ACD LINES

8X1 BCD TO EX 3 ACD LINES

8X1 BCD TO EX3 ABD LINE

8X1 BCD TO EX3 ABD LINE

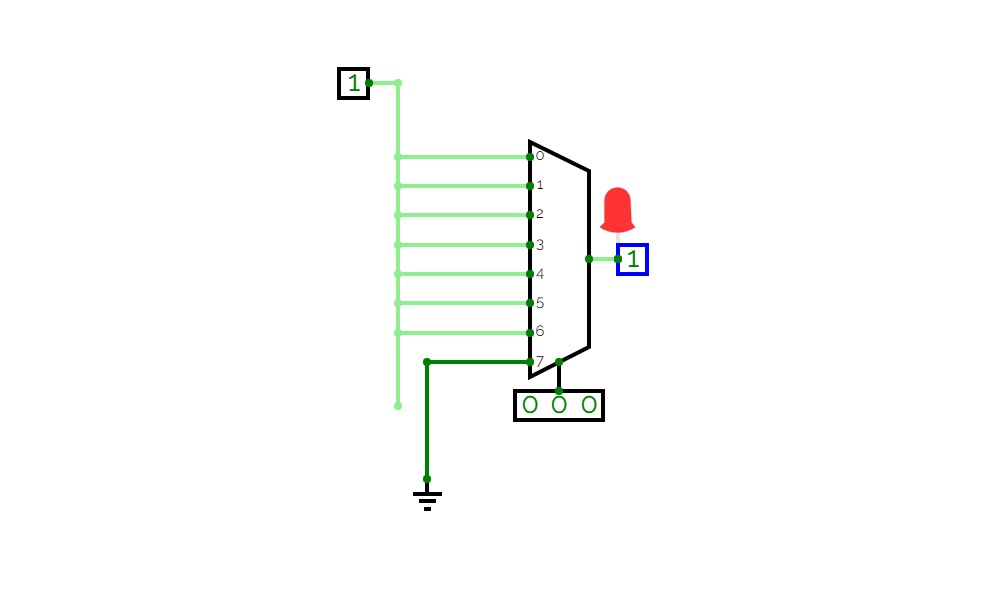

Registration no in seven segment display

Registration no in seven segment display

W ACTIVE HIGH

W ACTIVE HIGH

Y HIGH

Y HIGH

W ACTIVE LOW

W ACTIVE LOW

X HIGH

X HIGH

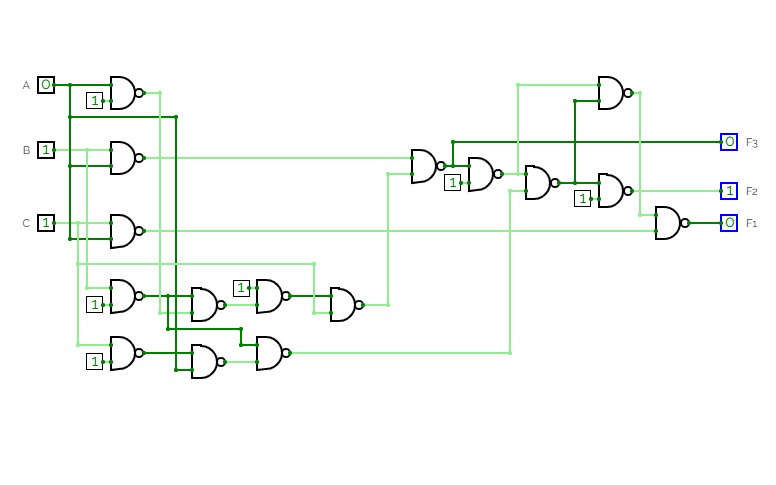

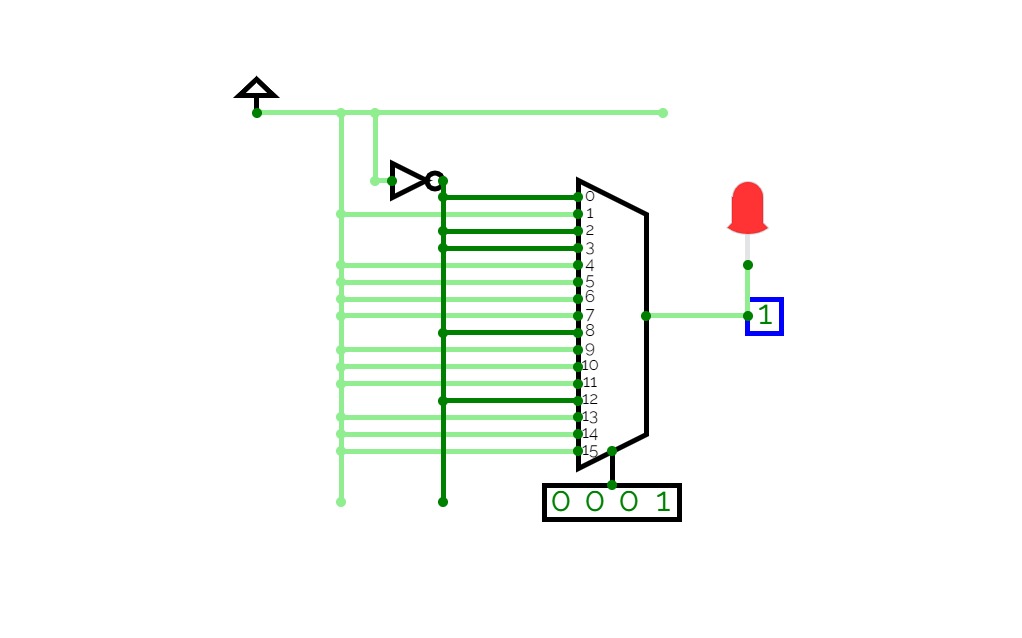

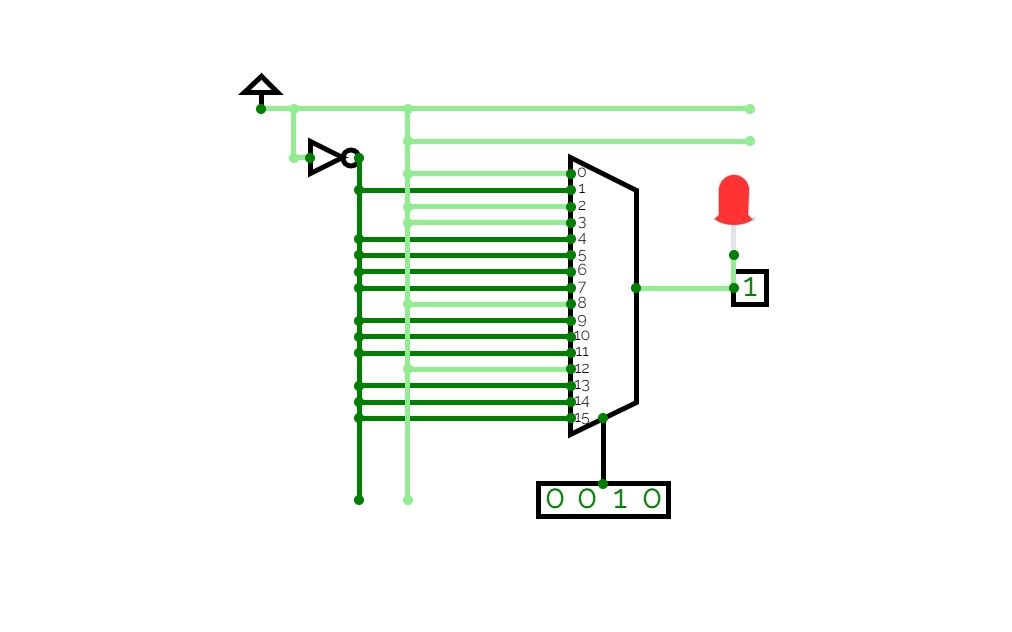

BCD TO EX 3 4: 16 DECODER

BCD TO EX 3 4: 16 DECODER

Untitled

Untitled

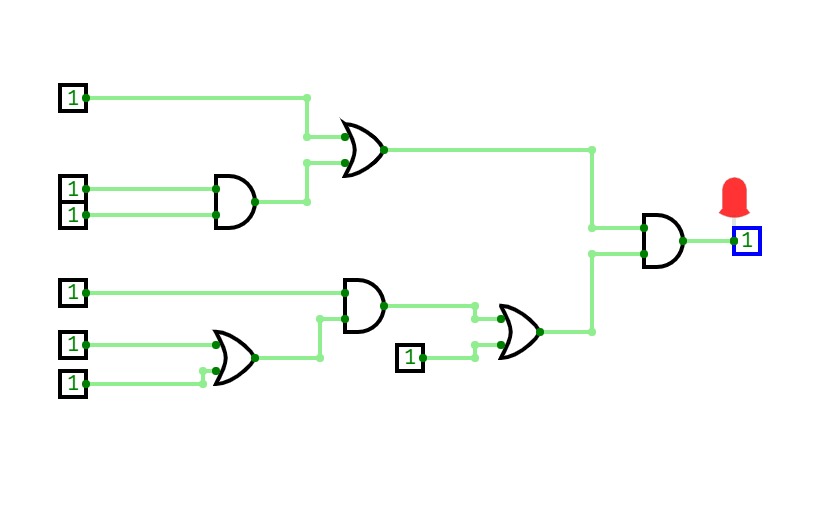

Class question 10 input or gate

Class question 10 input or gate

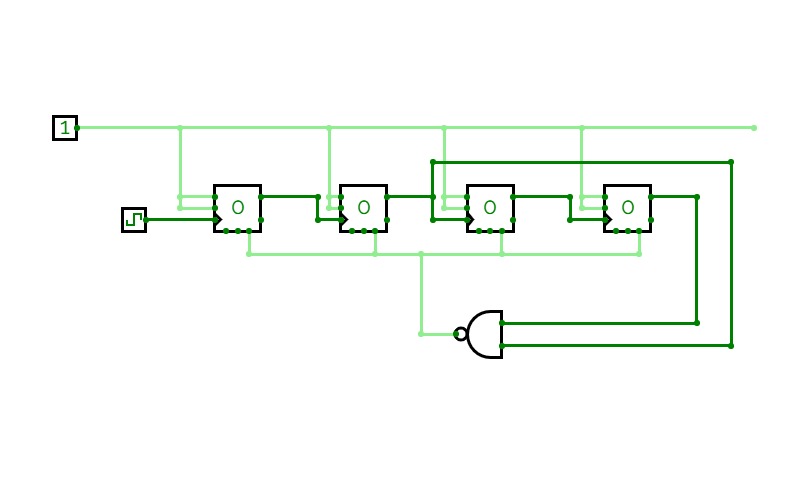

Decade counter

Decade counter

HW 1 -3 I/P AND GATE USINF 4X1 MUX

HW 1 -3 I/P AND GATE USINF 4X1 MUX

HW 2 3 I/P AND GATE USING 2X4 DECODER

HW 2 3 I/P AND GATE USING 2X4 DECODER

HW 3 CIRCUIT IMPLEMENTATION

HW 3 CIRCUIT IMPLEMENTATION

HW 4 REPRESENT IN MUX

HW 4 REPRESENT IN MUX

HW 4 FINAL CIRCUIT

HW 4 FINAL CIRCUIT

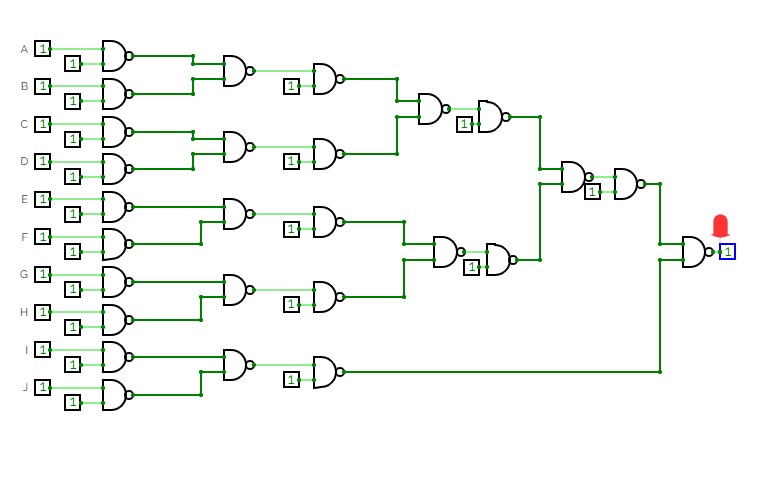

HW 5 10 INPUT 0R GATE USING NAND

HW 5 10 INPUT 0R GATE USING NAND

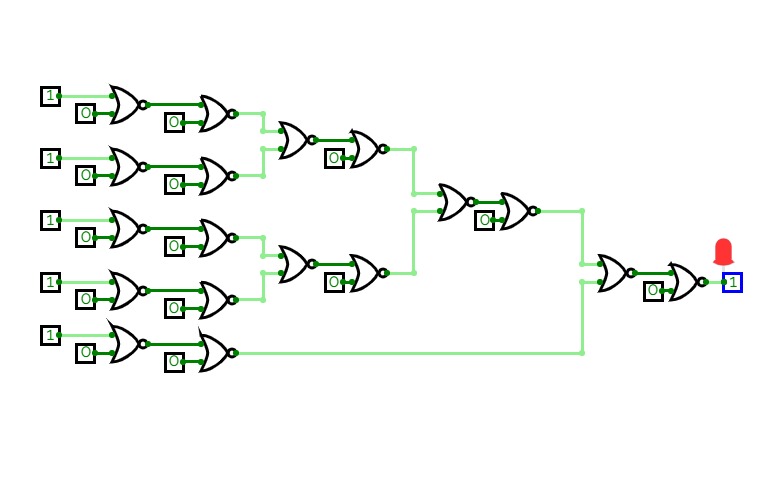

HW 5 10 INPUT OR GATE USING NOR

HW 5 10 INPUT OR GATE USING NOR

HW 5 10 INPUT OR GATE USING NOR

HW 5 10 INPUT OR GATE USING NOR

HW 4 FINAL CIRCUIT

HW 4 FINAL CIRCUIT

HW 4 FINAL CIRCUIT

HW 4 FINAL CIRCUIT

HW 6 4 bit input divisible by 5

HW 6 4 bit input divisible by 5

DLCD LAB FAT

DLCD LAB FAT

CAT: USING DECODER , DESIGN THE CLC

CAT: USING DECODER , DESIGN THE CLC

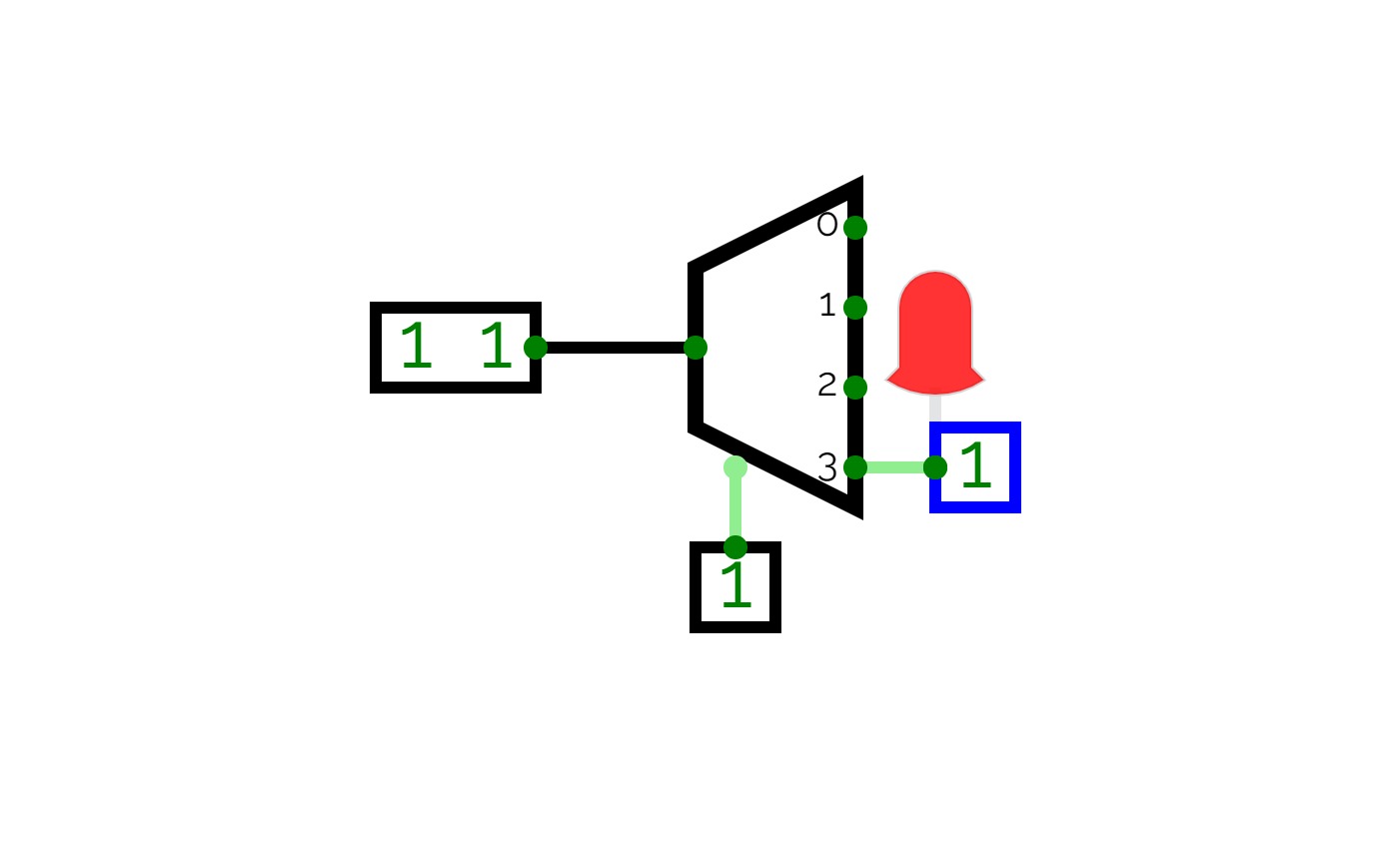

bcd to excesss 3 using 1:8 demux

bcd to excesss 3 using 1:8 demux

16X1 MUX SOP TASK 3

16X1 MUX SOP TASK 3

8X1 BCD TO EX 3 BCD LINES

8X1 BCD TO EX 3 BCD LINES

16X1 MUX BCD to Excess -3 code converter

16X1 MUX BCD to Excess -3 code converter

CAT: IMPLEMENT USING NOR LOGIC

CAT: IMPLEMENT USING NOR LOGIC

CAT: implement the equation using decoder

CAT: implement the equation using decoder