Manish Kumar Sharma

Member since: 3 years

Educational Institution: Not Entered

Country: Not Entered

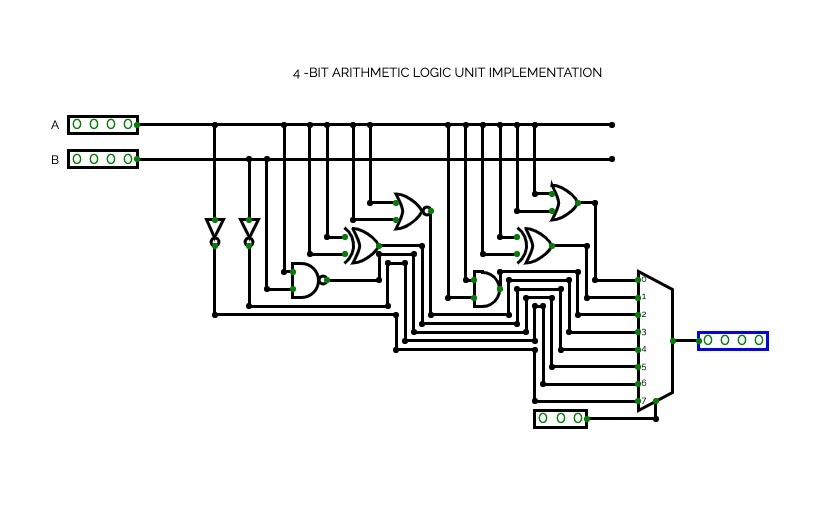

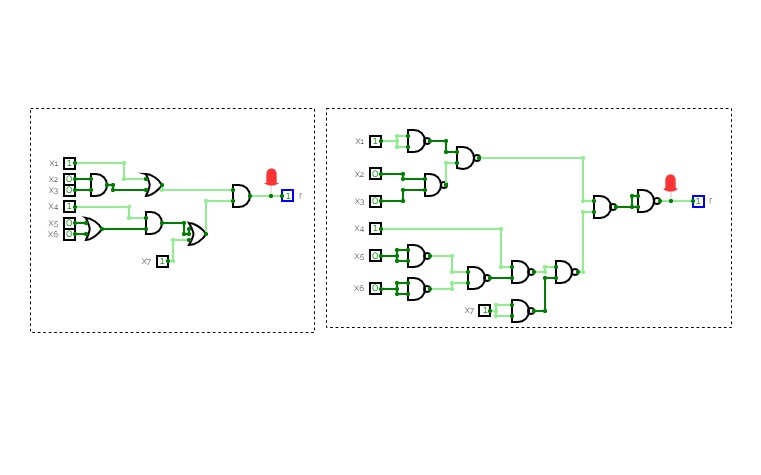

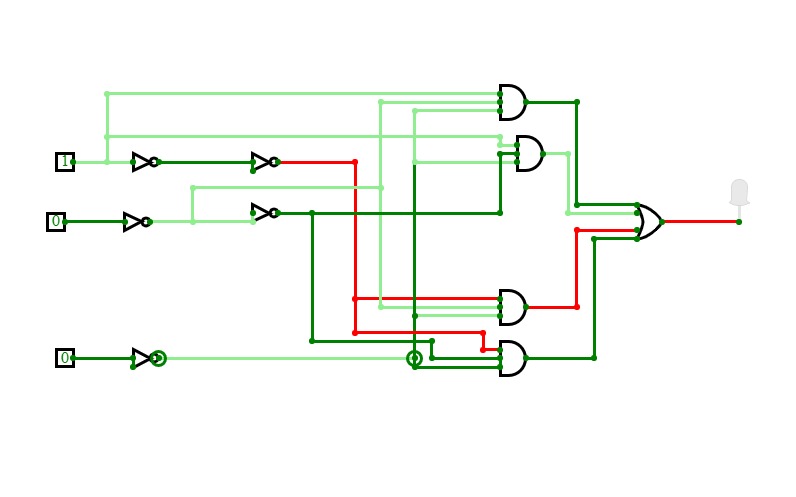

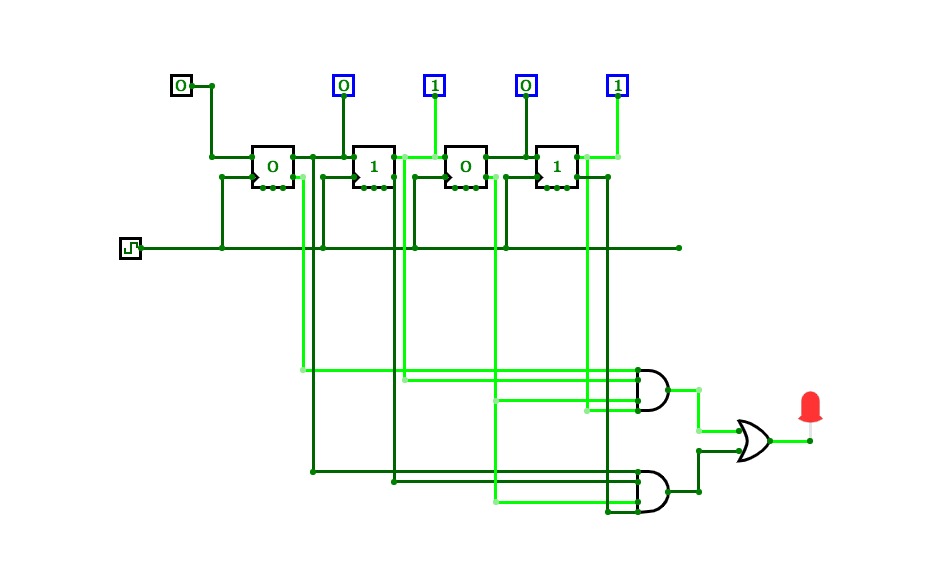

DA2

DA2

gopi hw4

gopi hw4

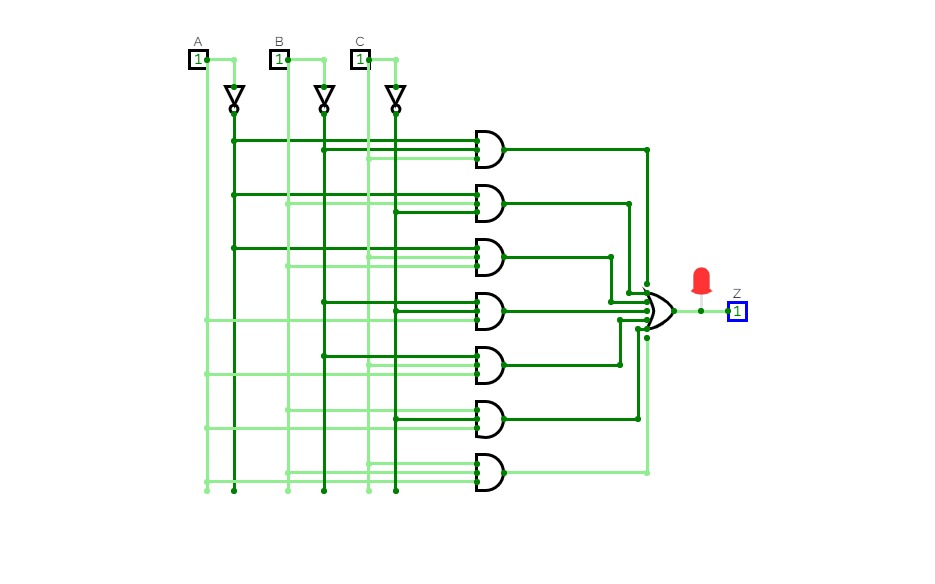

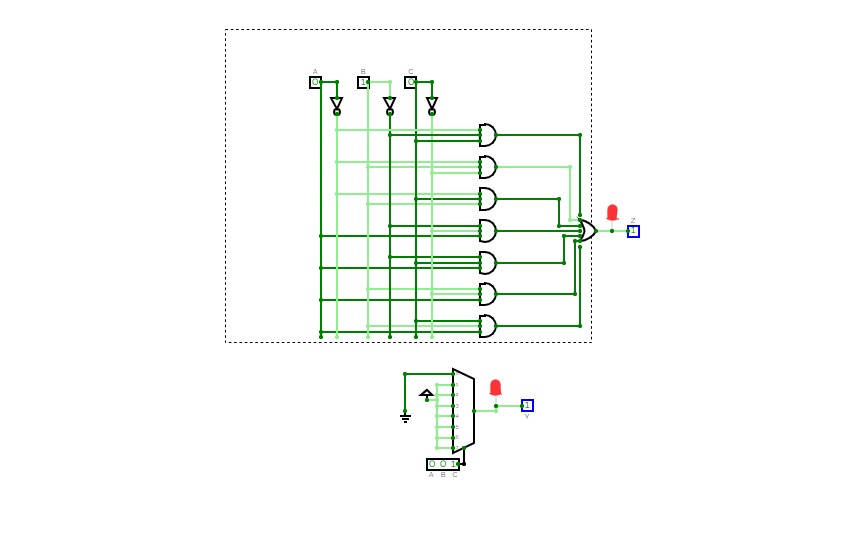

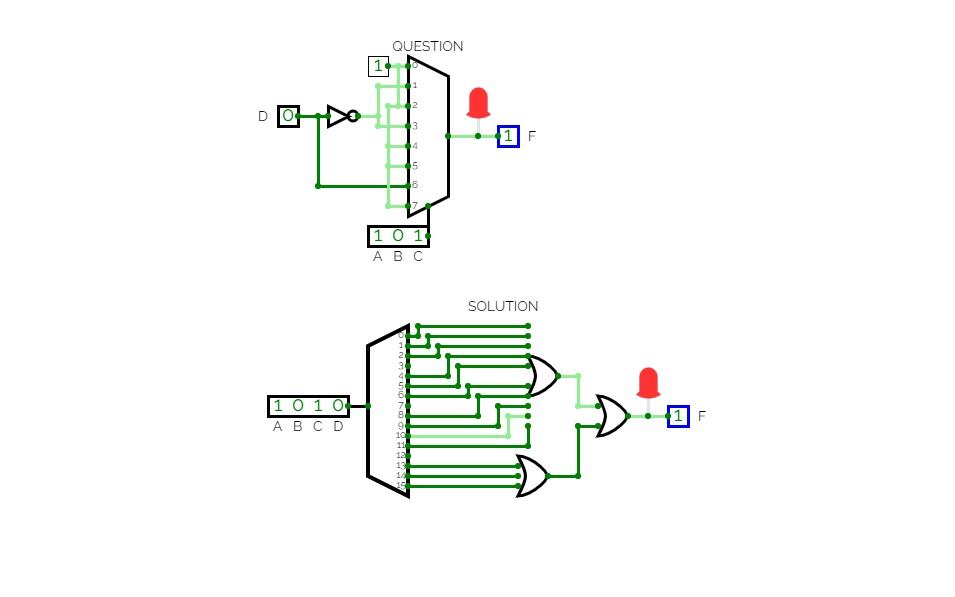

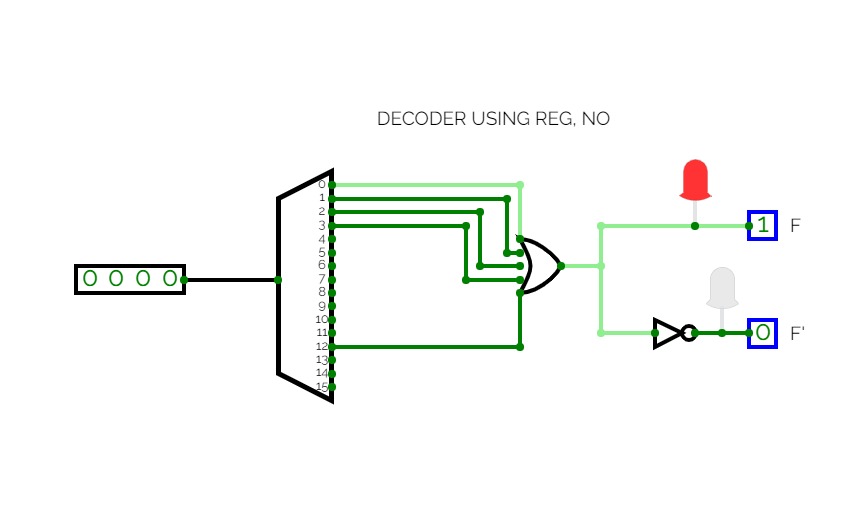

TASK2 USING DECODER

TASK2 USING DECODER

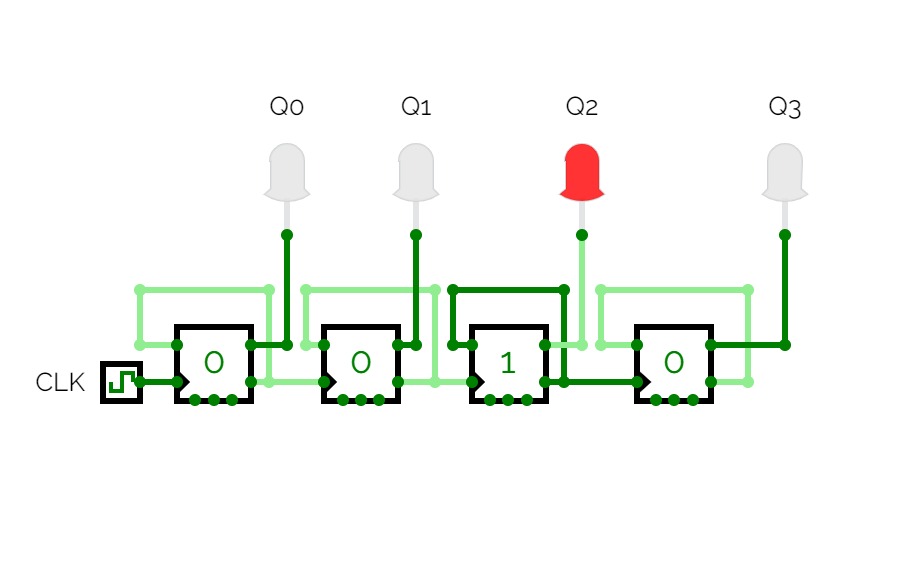

4-Bit Synchronous Up Counter

4-Bit Synchronous Up Counter

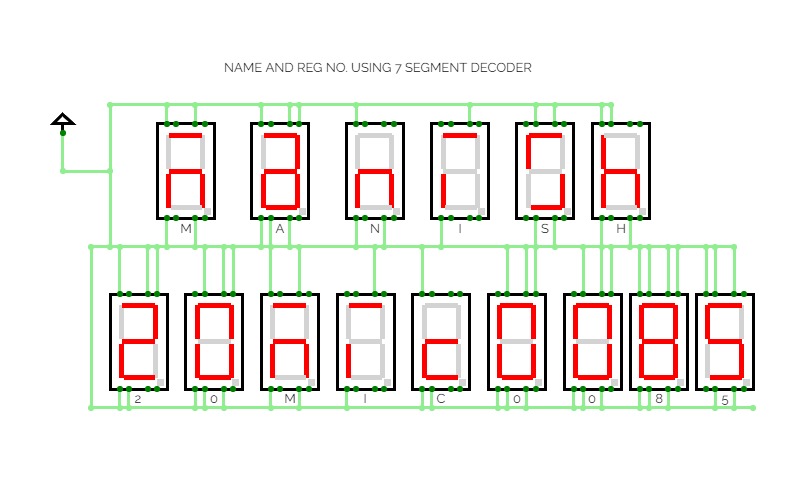

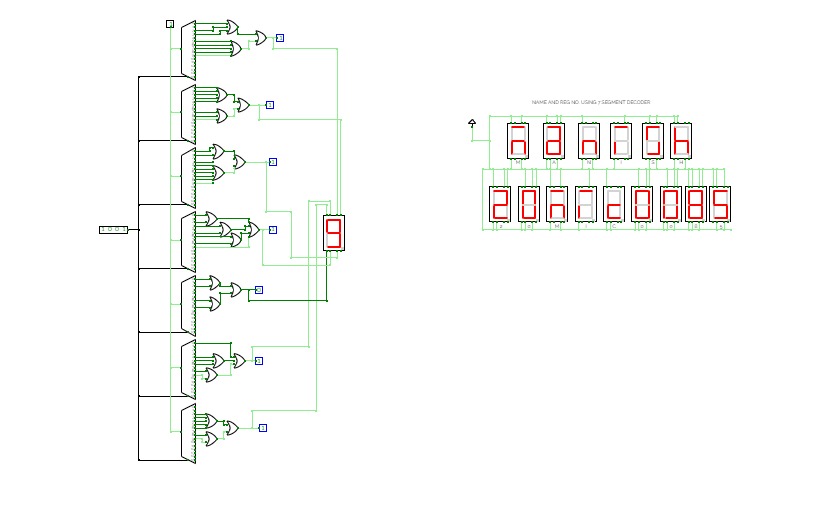

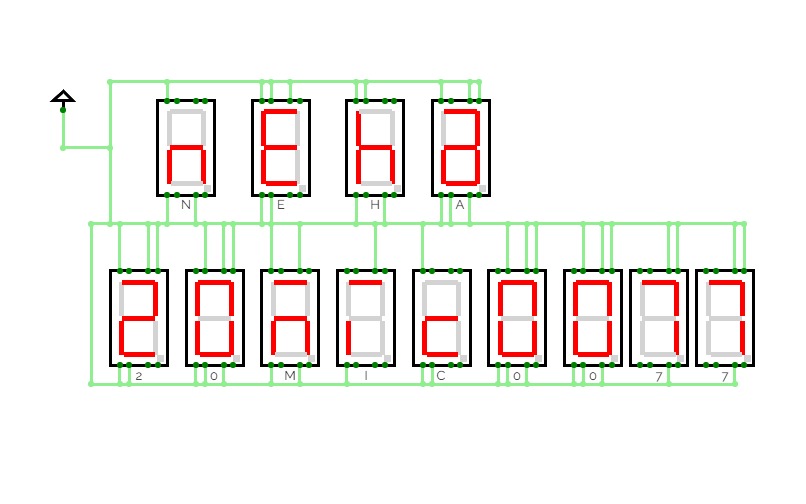

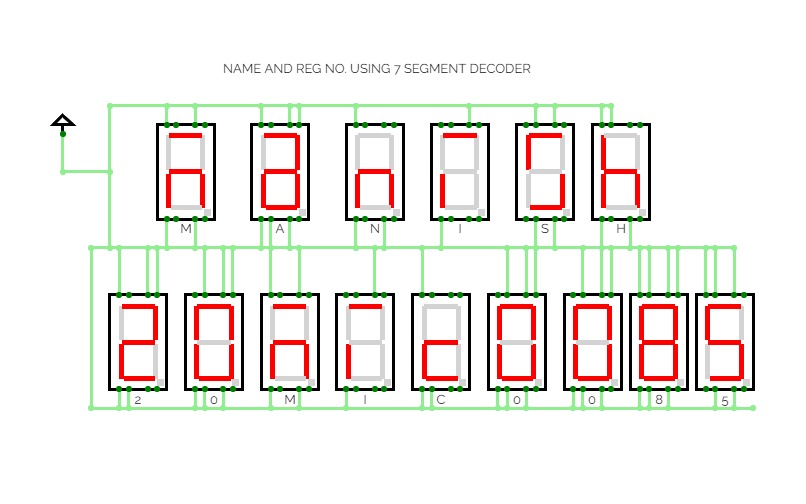

NAME AND REG NO. USING 7 SEGMENT DECODER

NAME AND REG NO. USING 7 SEGMENT DECODER

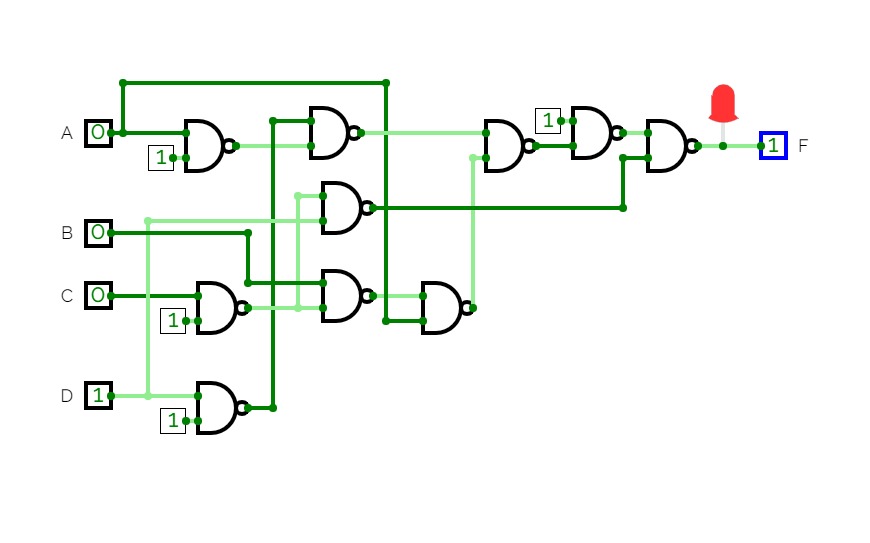

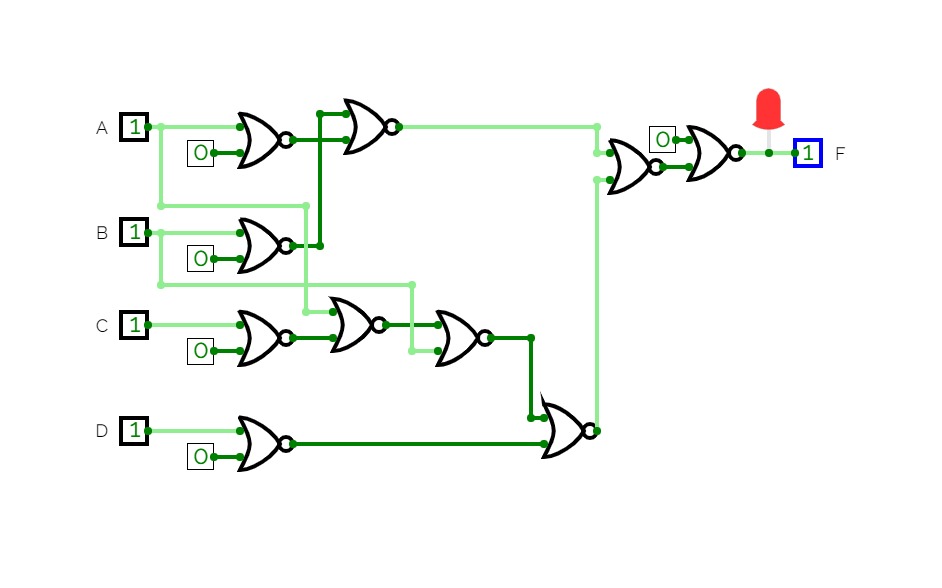

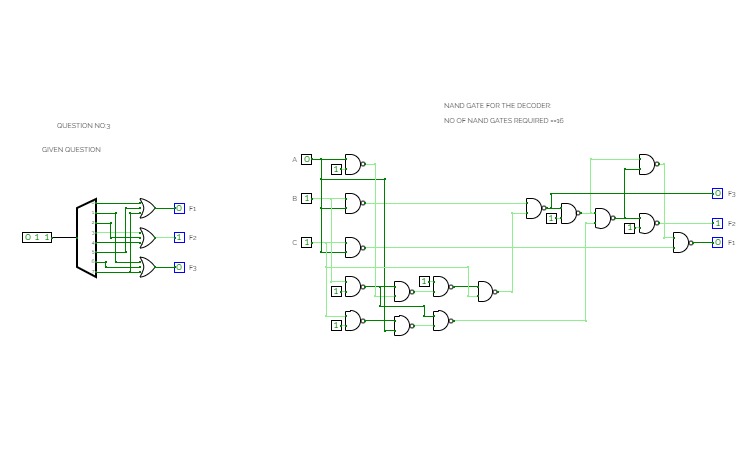

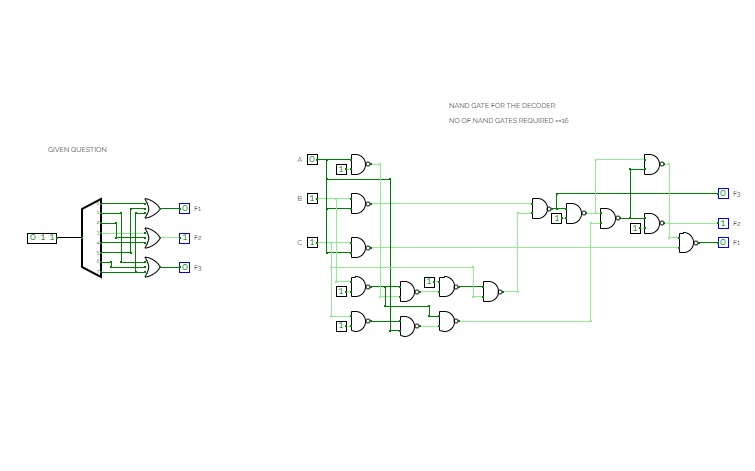

CAT: design the internal structure of Circuit given using NAND gates.

CAT: design the internal structure of Circuit given using NAND gates.

VIVA_4-1

VIVA_4-1

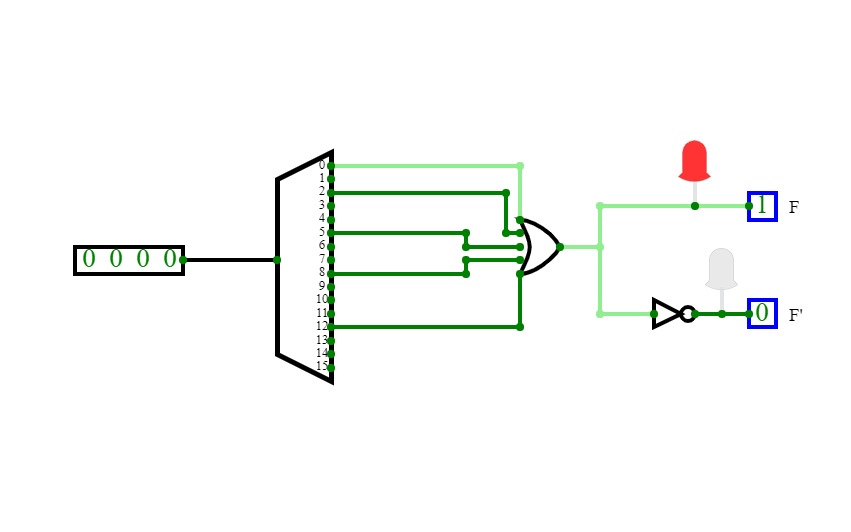

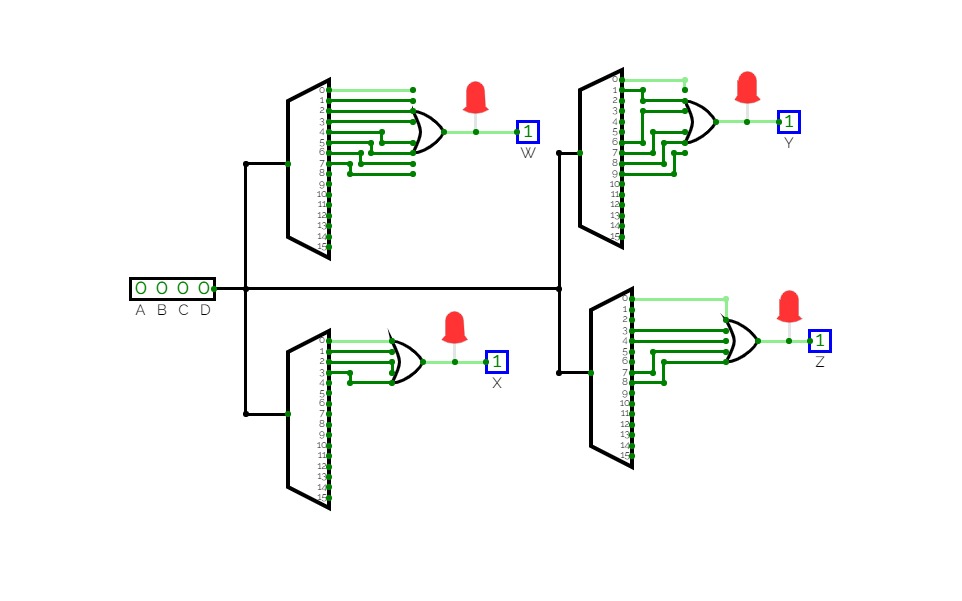

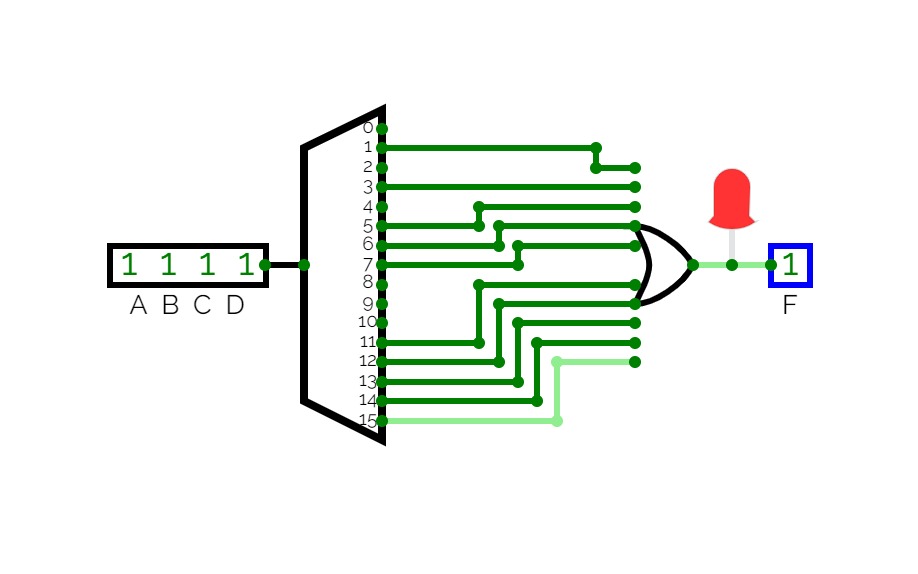

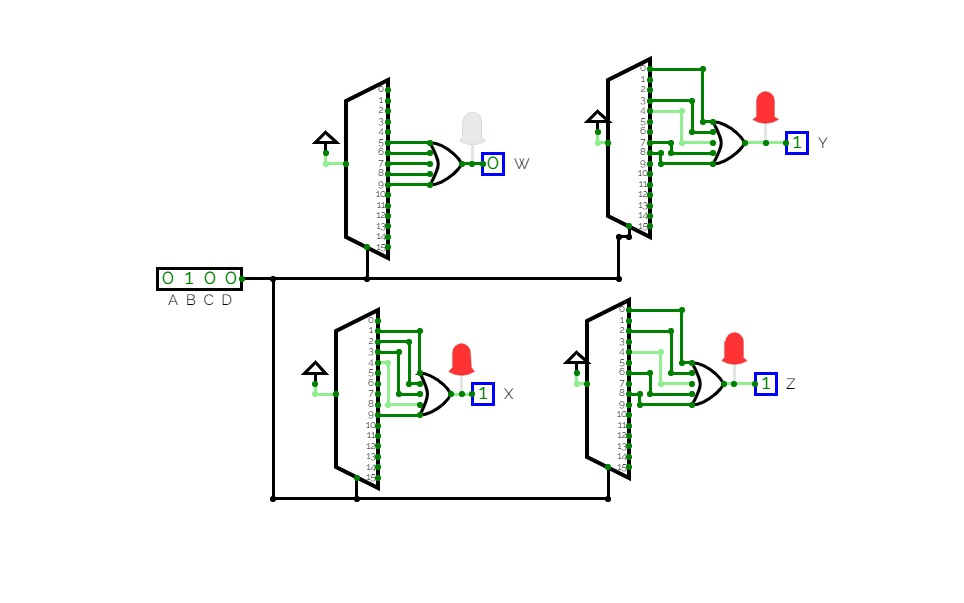

TASK 1 POS using 4:16 decoder

TASK 1 POS using 4:16 decoder

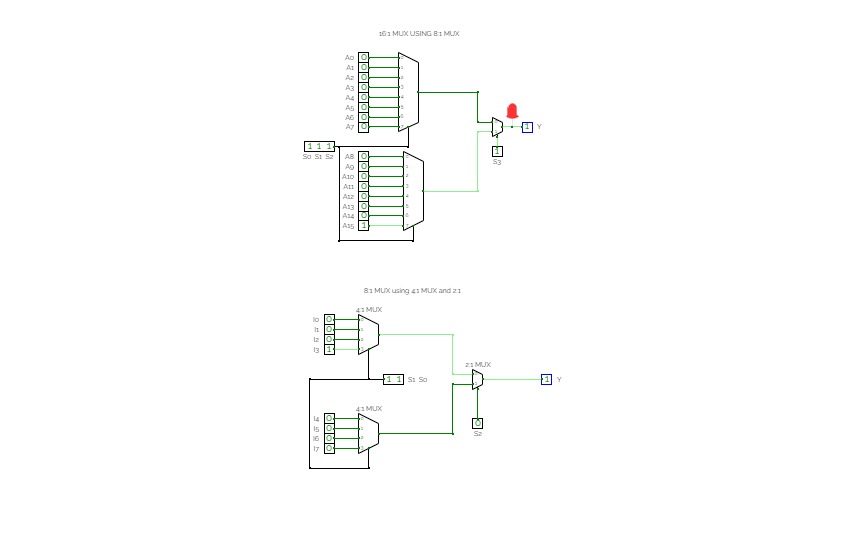

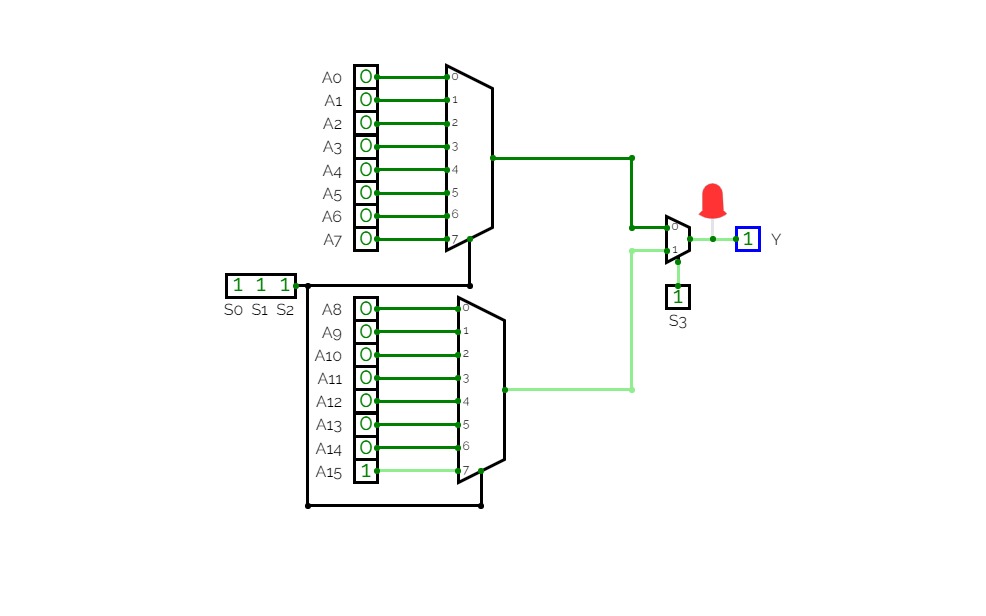

8:1 MUX FOR TASK-2

8:1 MUX FOR TASK-2

task1 using 4:16 decoder

task1 using 4:16 decoder

6) 1X16 DEMULTIPLEXER FOR C

6) 1X16 DEMULTIPLEXER FOR C

TTG

TTG

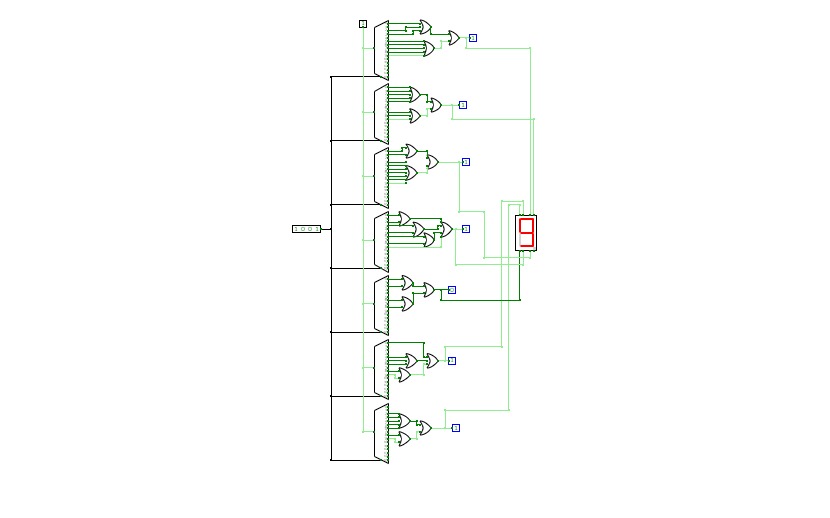

NAME REG.NO

NAME REG.NO

Aditya HW-4

Aditya HW-4

GOPI VIVA 3

GOPI VIVA 3

GOPI VIVA 1

GOPI VIVA 1

ADITYA VIVA 2

ADITYA VIVA 2

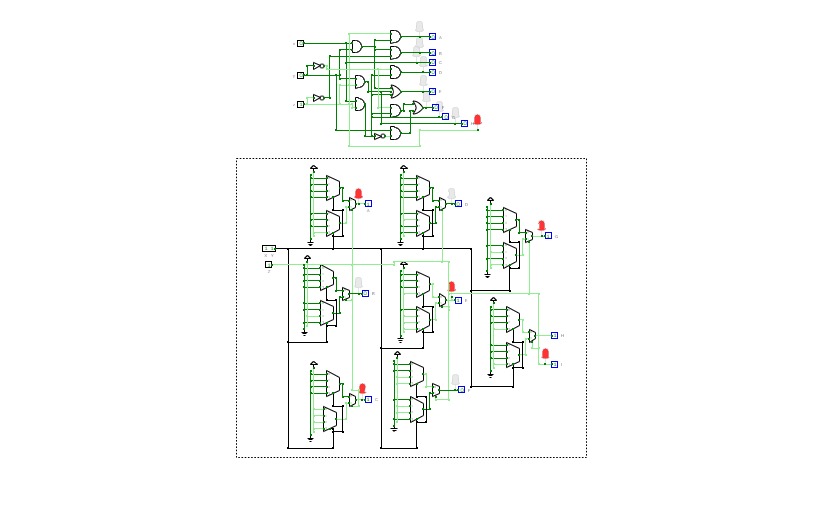

TASK 4 CIRCUITS

TASK 4 CIRCUITS

TASK 3 CIRCUITS

TASK 3 CIRCUITS

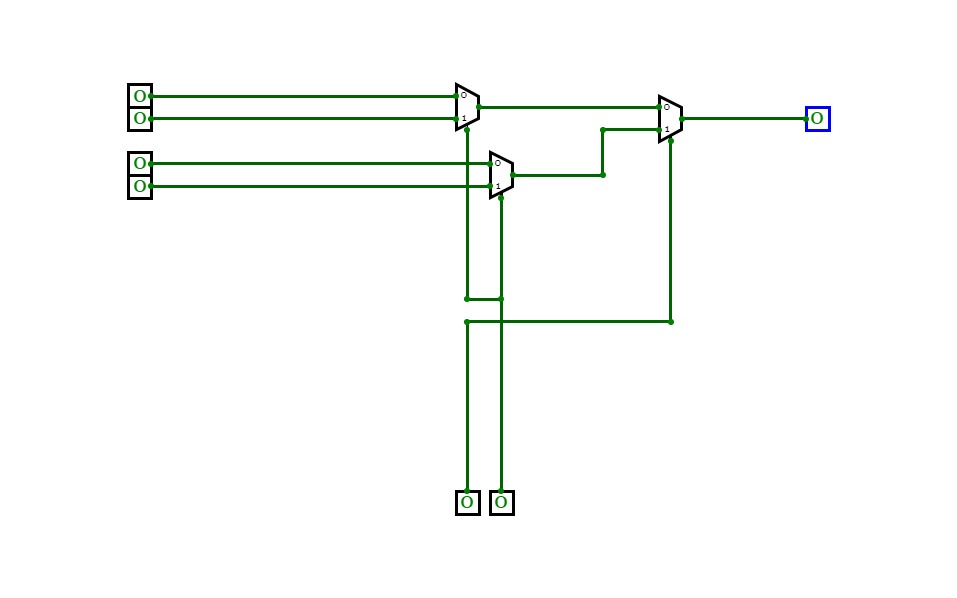

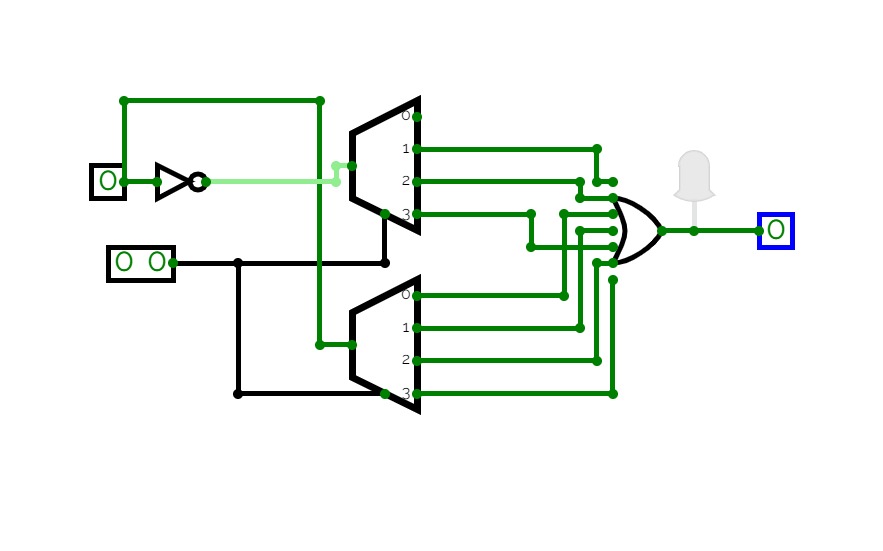

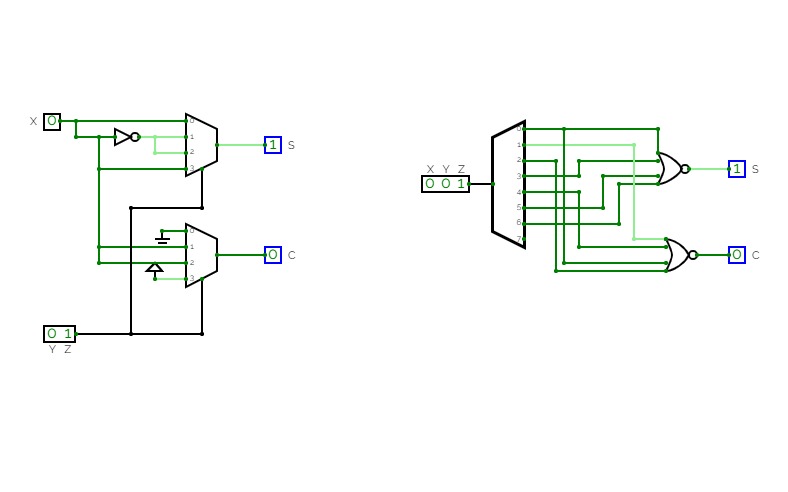

4 ->1 multiplexer using 2->1 Multiplexers

4 ->1 multiplexer using 2->1 Multiplexers

aryan khare task 4

aryan khare task 4

varun task3

varun task3

4 ->1 multiplexer using 2->1 Multiplexers

4 ->1 multiplexer using 2->1 Multiplexers

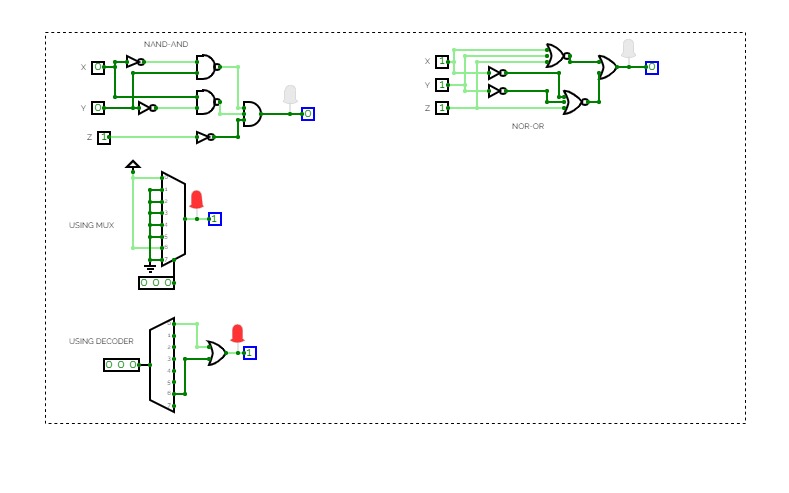

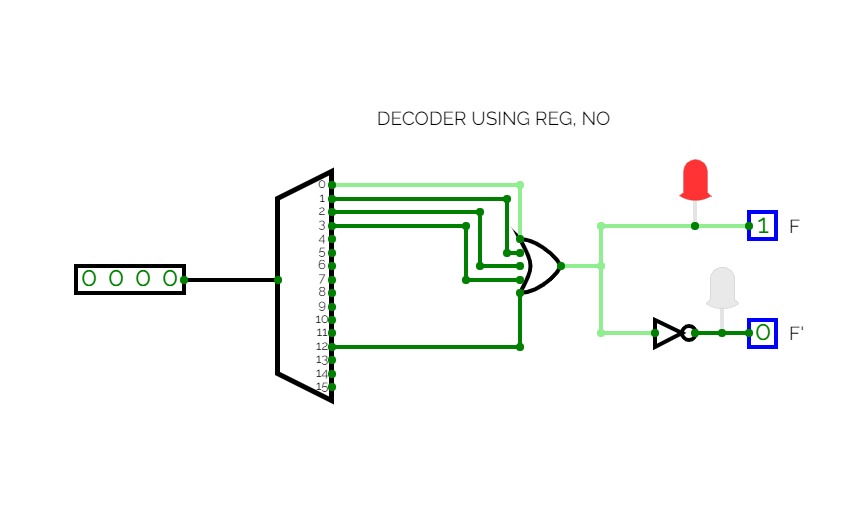

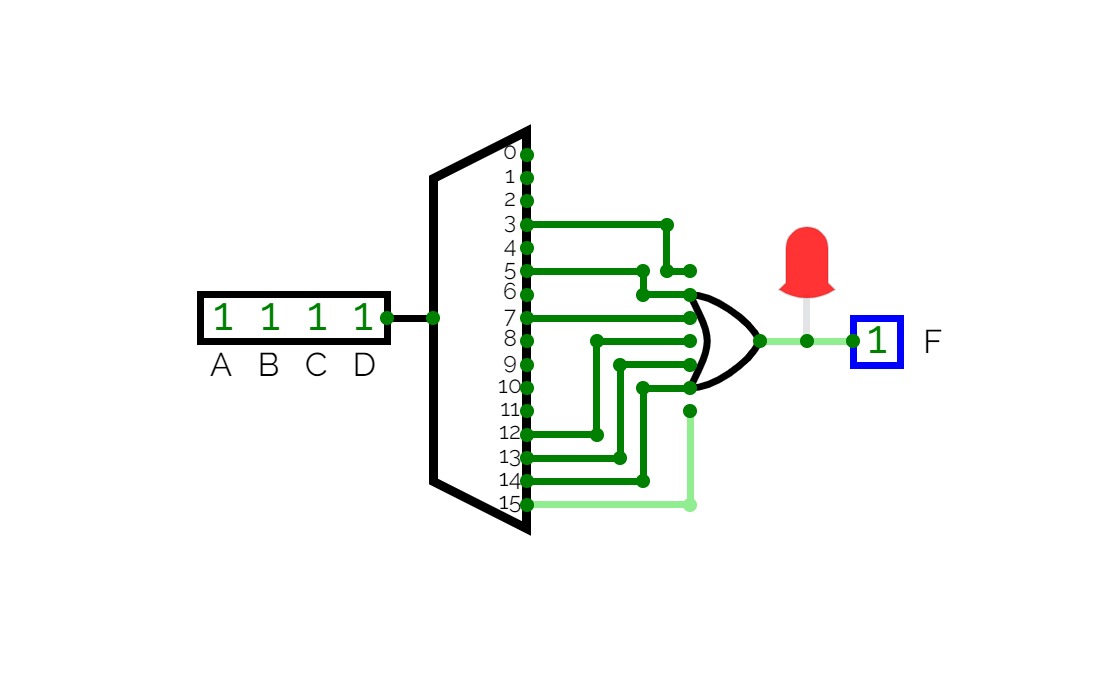

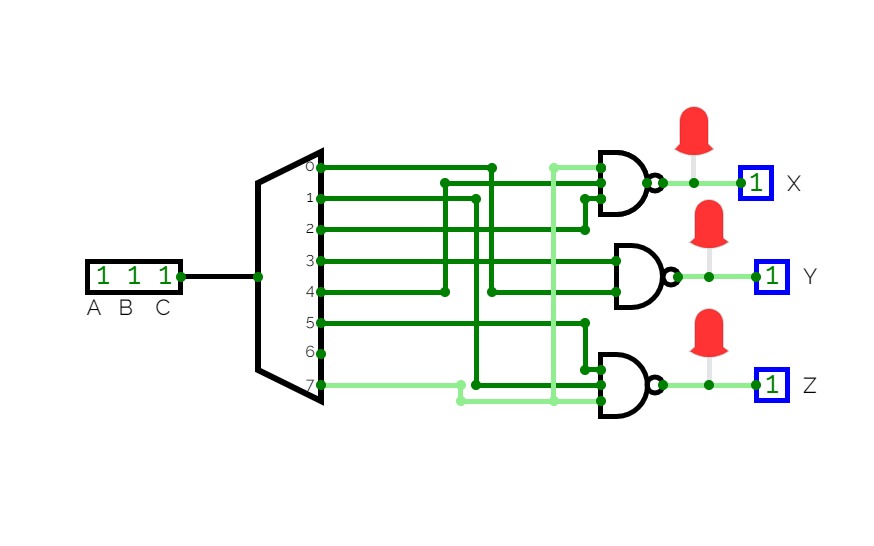

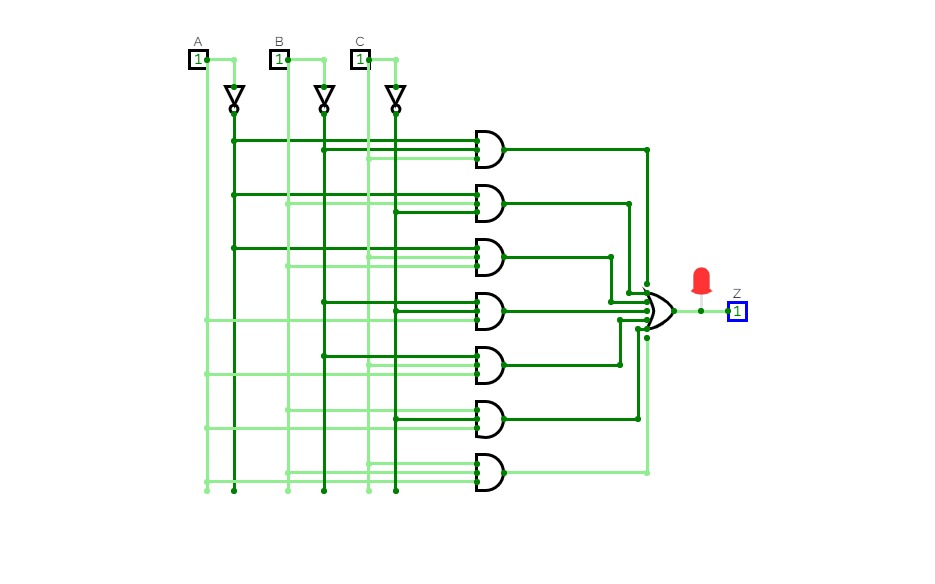

CAT: implement the equation using decoder

CAT: implement the equation using decoder

CAT: IMPLEMENT USING NOR LOGIC

CAT: IMPLEMENT USING NOR LOGIC

CAT 2

CAT 2

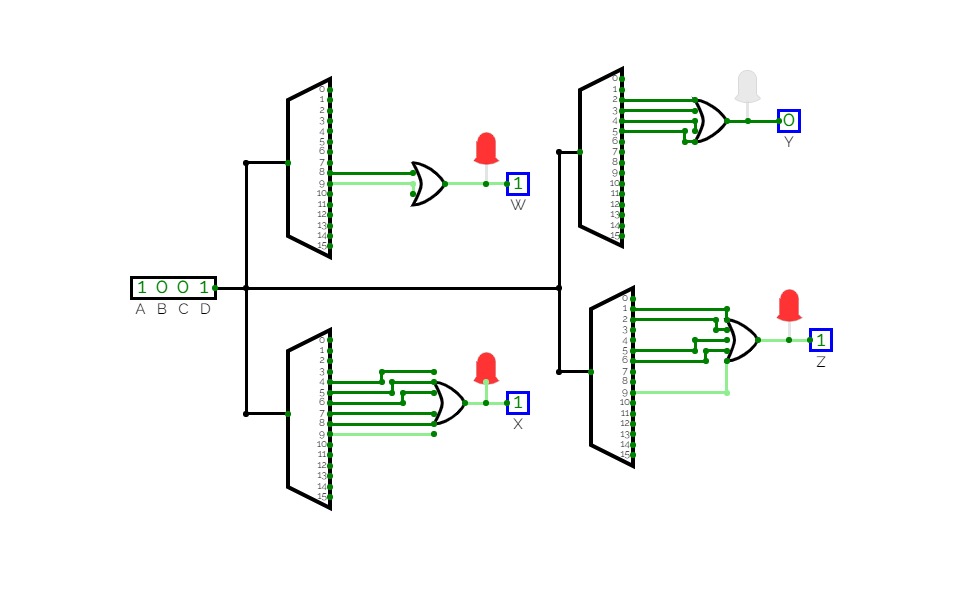

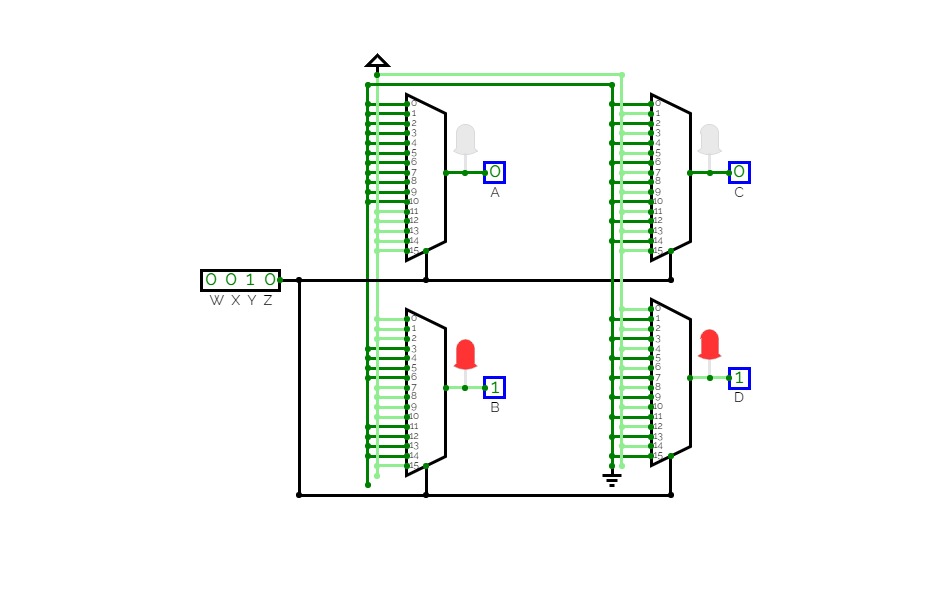

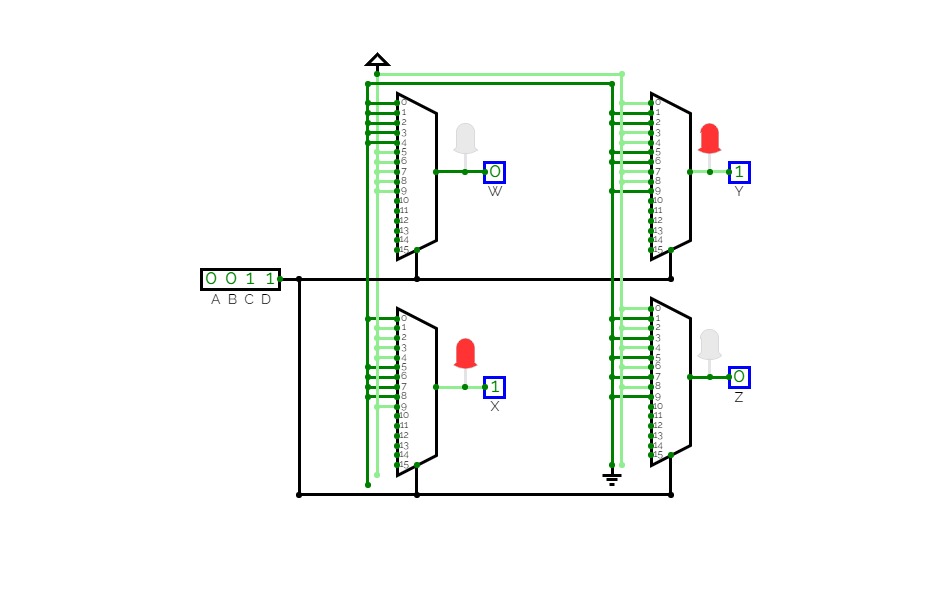

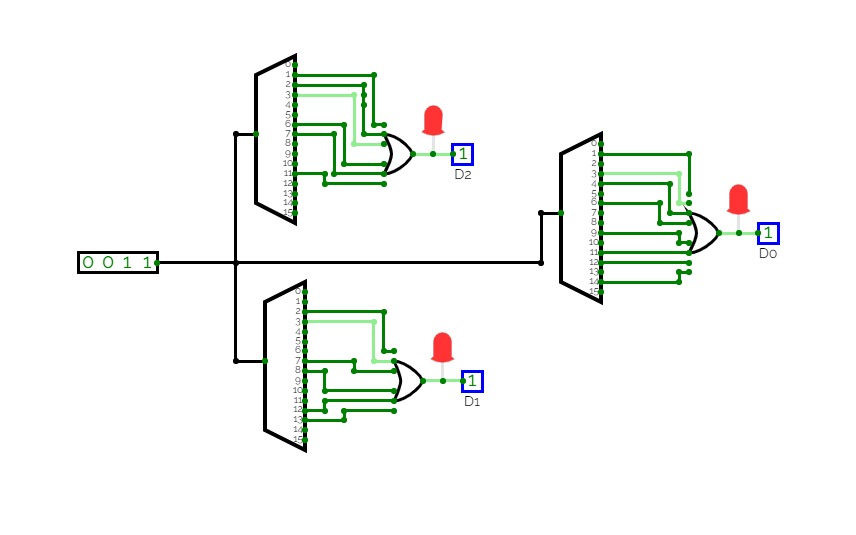

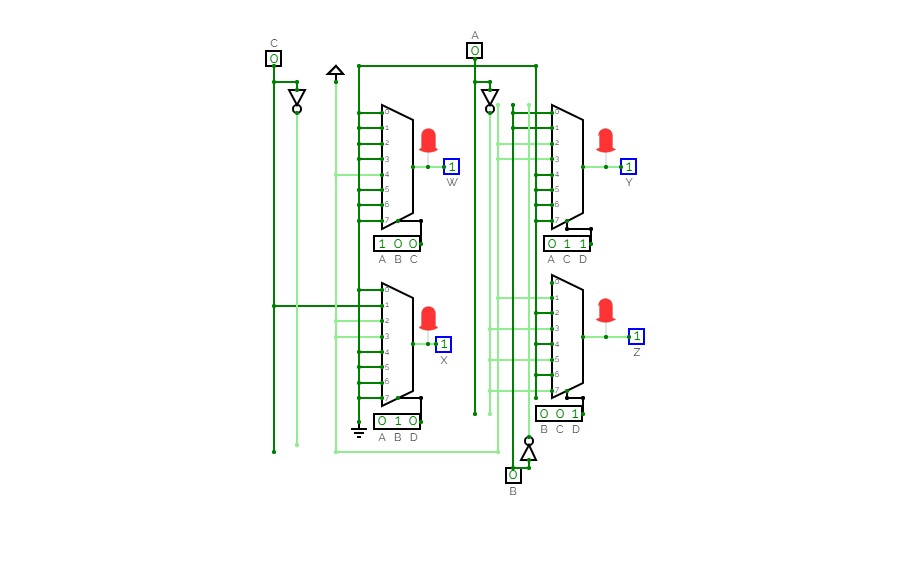

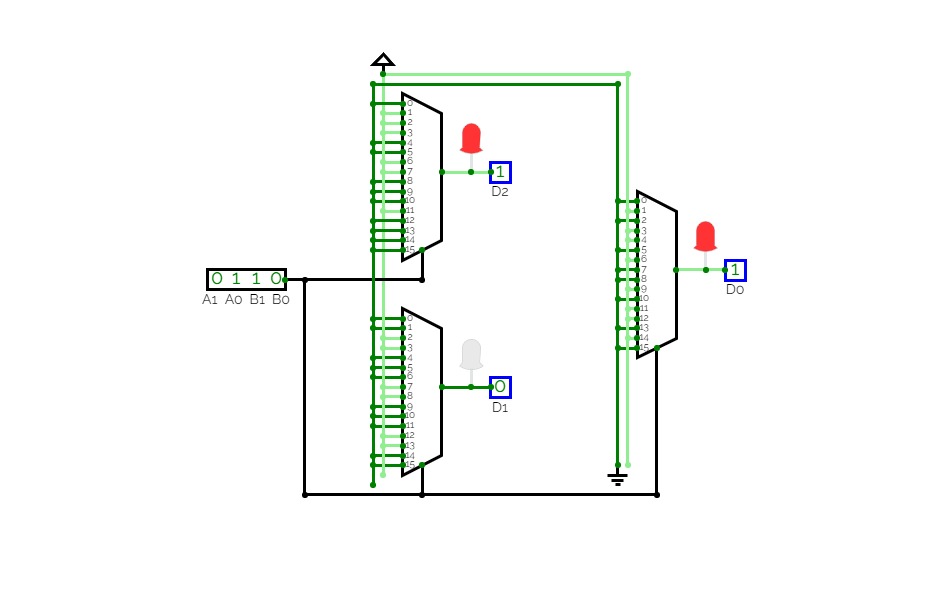

VARUN PANDEY DUAL MUX

VARUN PANDEY DUAL MUX

Ranadheer task3 links

Ranadheer task3 links

LABFAT 2OMIC0085

LABFAT 2OMIC0085

task3

task3

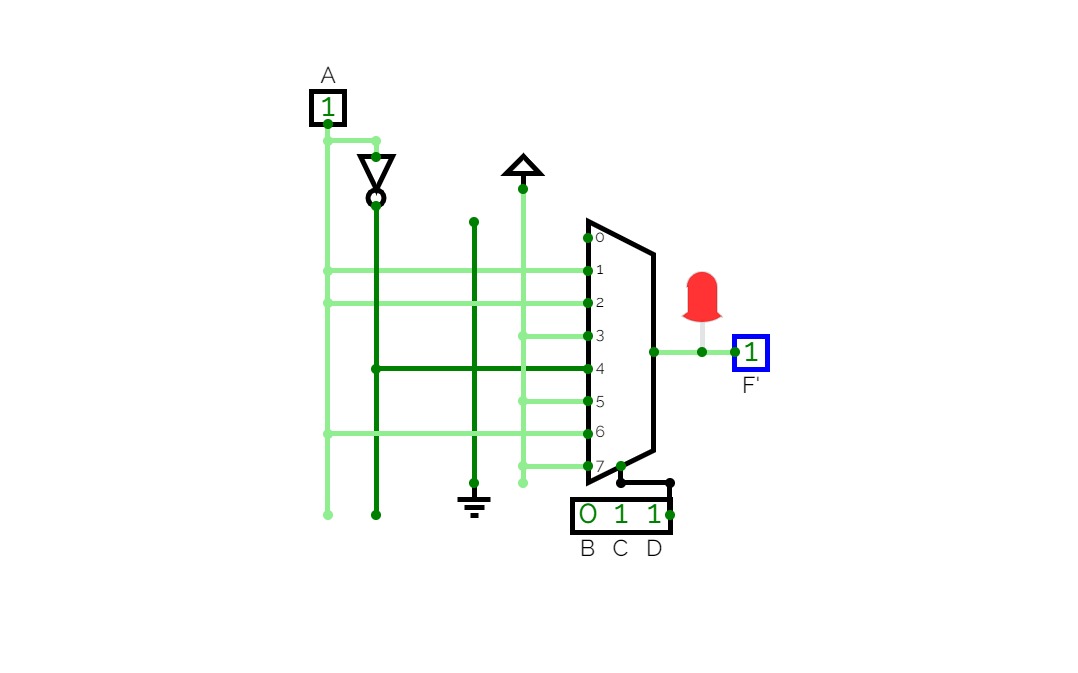

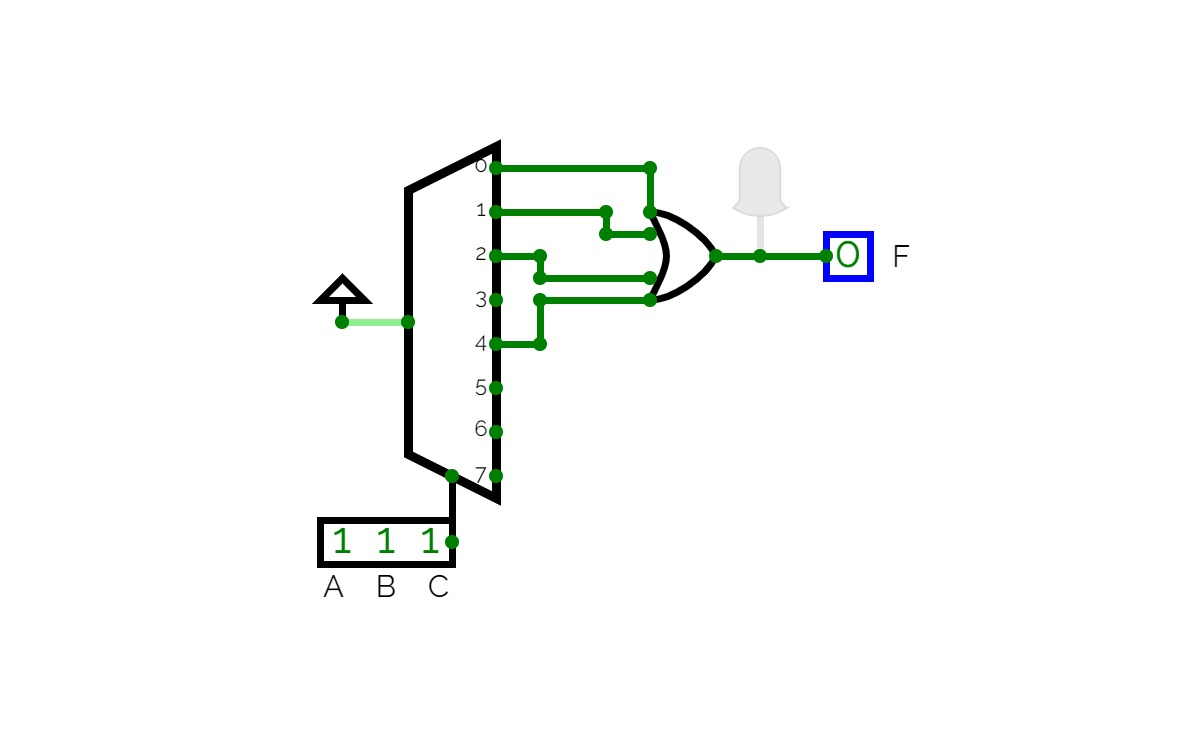

3 input OR gate using 4:1 MUX

3 input OR gate using 4:1 MUX

Untitled

Untitled

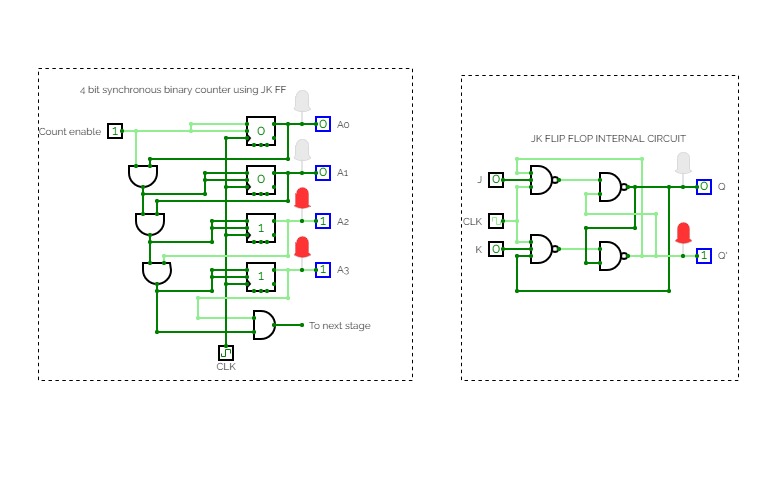

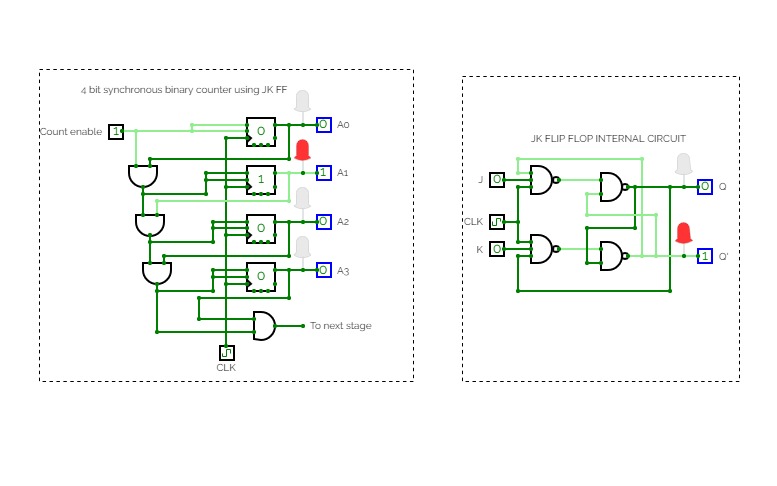

4-bit binary synchronous counter using JK flip flop

4-bit binary synchronous counter using JK flip flop

BCD to excess 3 code using 1:8 DEMUX

BCD to excess 3 code using 1:8 DEMUX

CAT. : IMPLELEMENT FROM DECODER

CAT. : IMPLELEMENT FROM DECODER

3 INPUT OR gate using 1:4 Demux

3 INPUT OR gate using 1:4 Demux

viva 3

viva 3

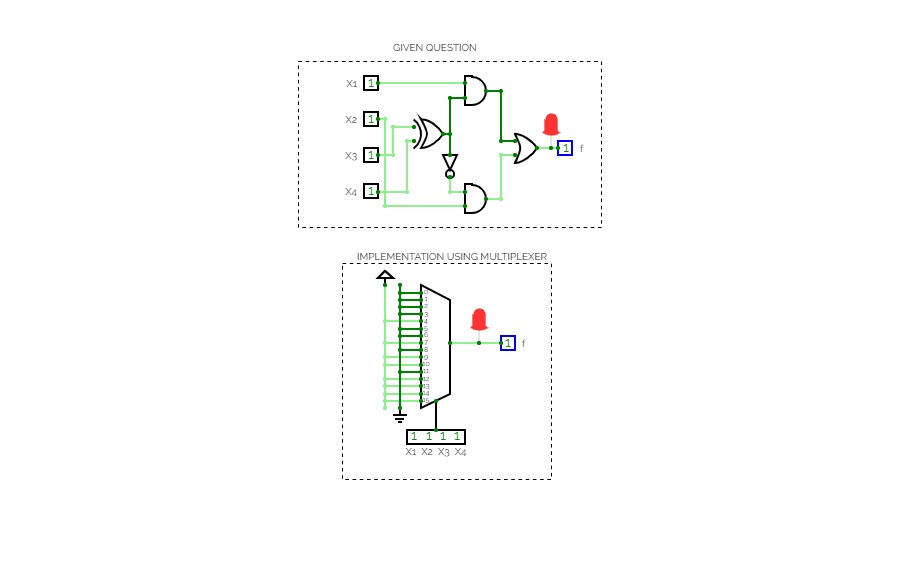

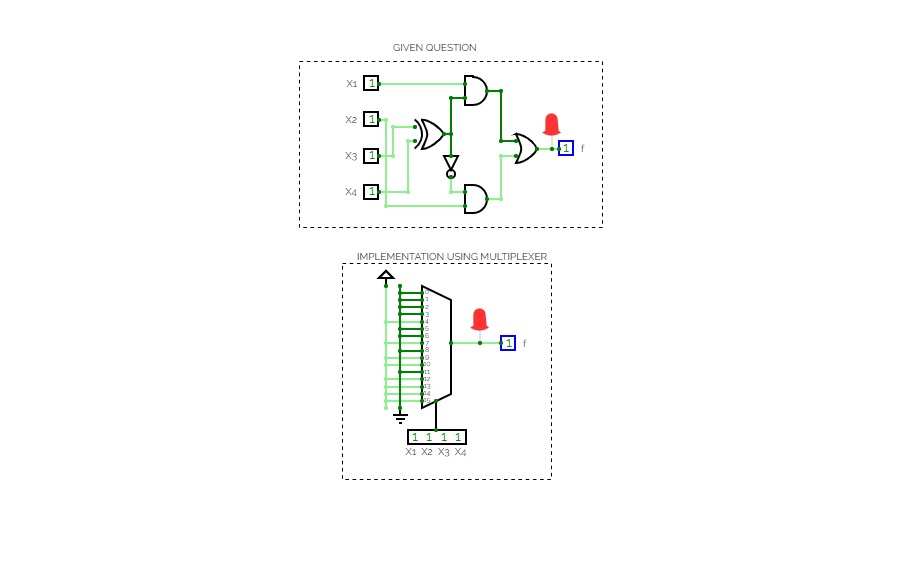

IMPLEMENTATION OF CIRCUIT USING MULTIPLEXER

IMPLEMENTATION OF CIRCUIT USING MULTIPLEXER

CAT.: DUAL MUX

CAT.: DUAL MUX

8:1 IMPLEMENTATION

8:1 IMPLEMENTATION

CIRCUIT DESIGN USING MUX

CIRCUIT DESIGN USING MUX

Untitled

Untitled

NAME

NAME

ADITYA VIVA 1

ADITYA VIVA 1

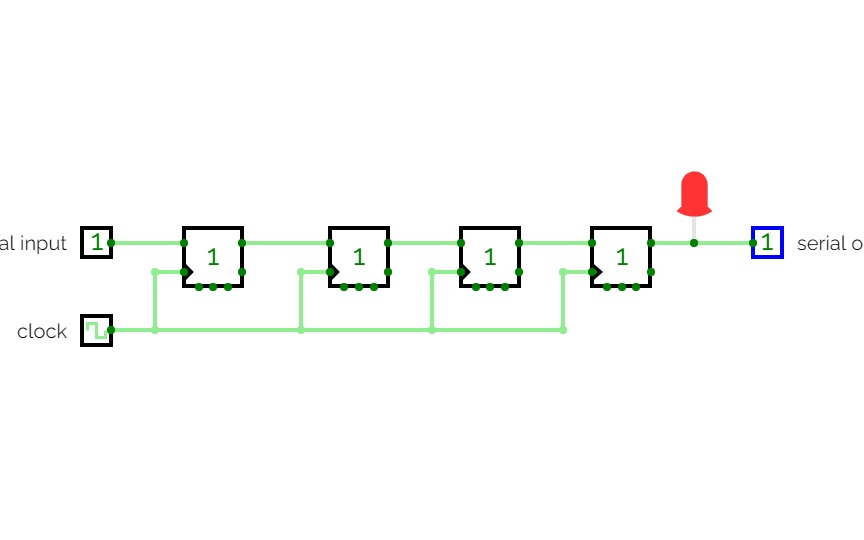

SISO Shift register using D FF

SISO Shift register using D FF

3 INPUT OR gate using 1:4 Demux

3 INPUT OR gate using 1:4 Demux

ADITYA VIVA 3

ADITYA VIVA 3

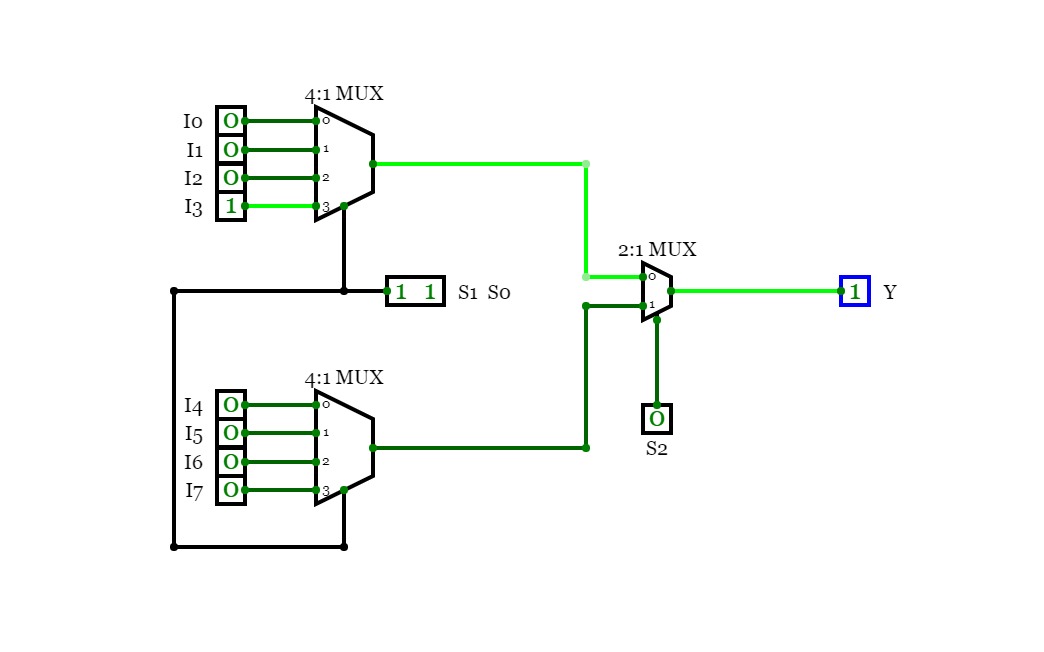

8:1 MUX using 4:1 MUX & 2:1 MUX

8:1 MUX using 4:1 MUX & 2:1 MUX

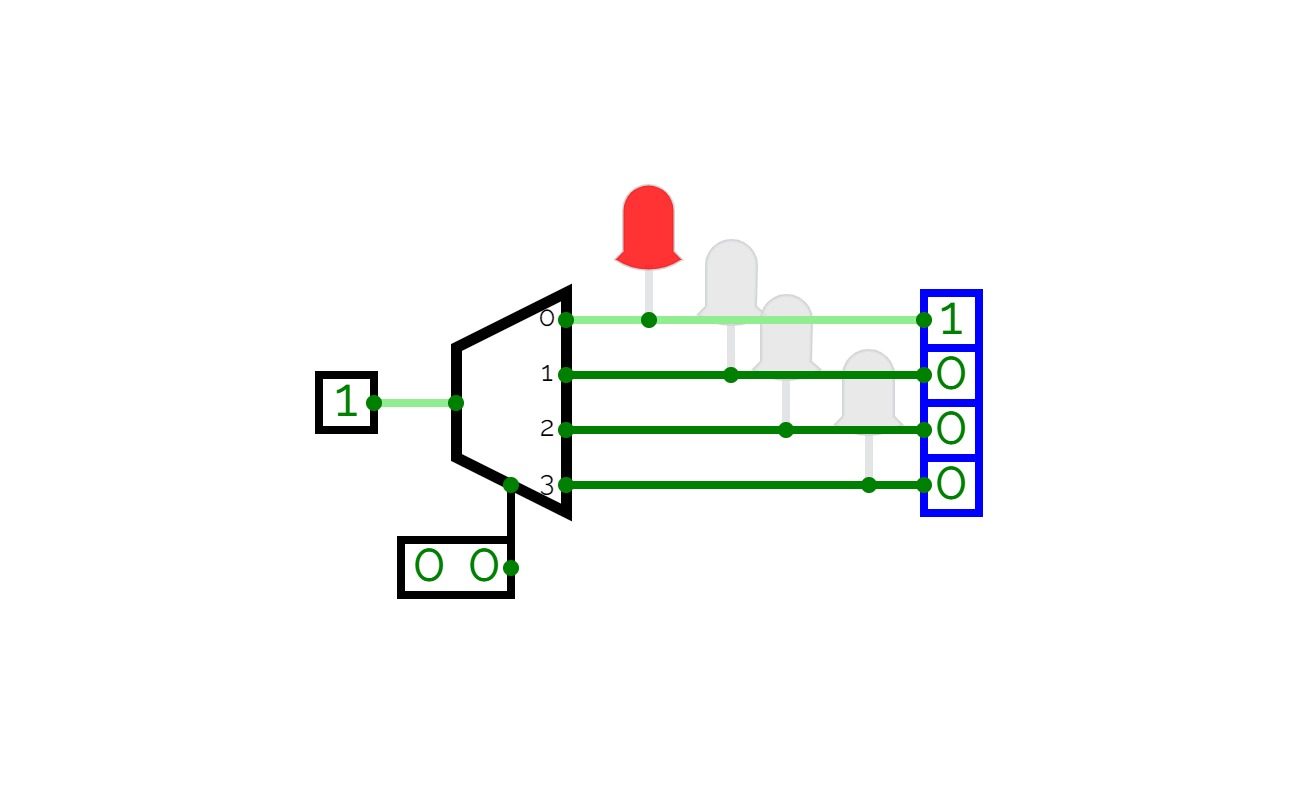

1:4 DEMUX

1:4 DEMUX

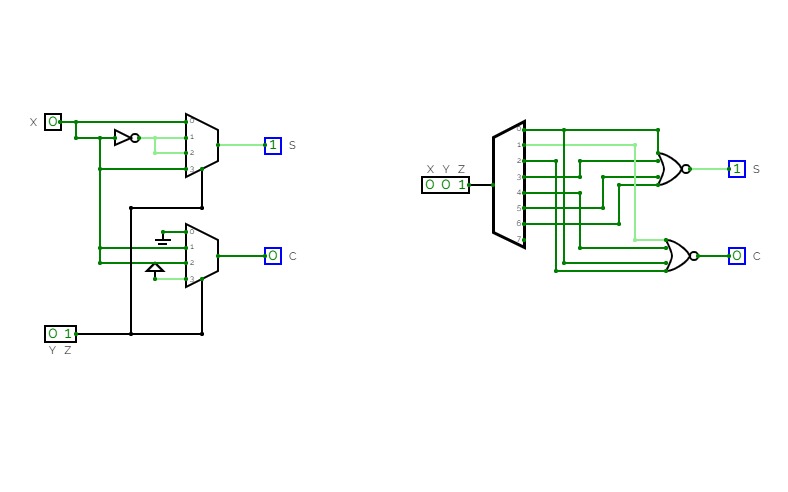

CAT: USING DECODER , DESIGN THE CLC

CAT: USING DECODER , DESIGN THE CLC

4 bit synchronous down counter using jk flip flop

4 bit synchronous down counter using jk flip flop

MID IMPLEMENTATION OF CIRCUIT USING MULTIPLEXER

MID IMPLEMENTATION OF CIRCUIT USING MULTIPLEXER

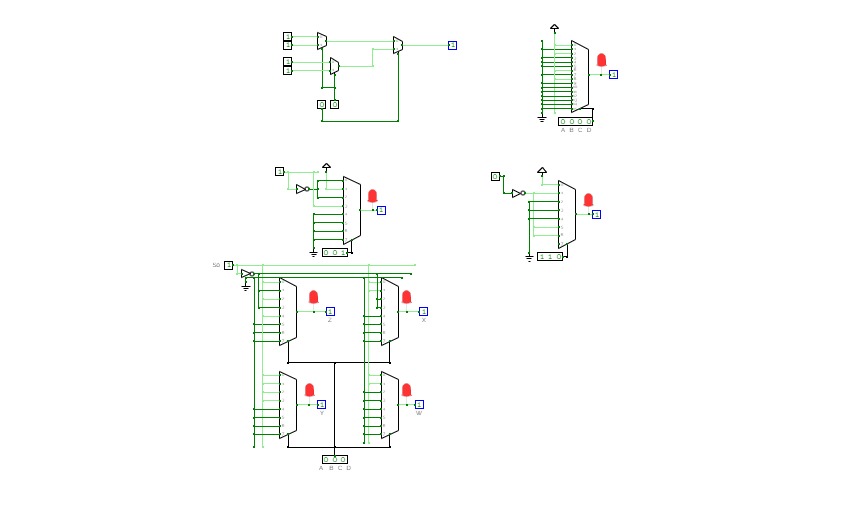

TASK 5 CIRCUITS

TASK 5 CIRCUITS

4-bit right shift register

4-bit right shift register

aryan khare task 4

aryan khare task 4

4 BIT Binary Ripple counter using D FF

4 BIT Binary Ripple counter using D FF

16:1 MUX USING 8:1 MUX

16:1 MUX USING 8:1 MUX

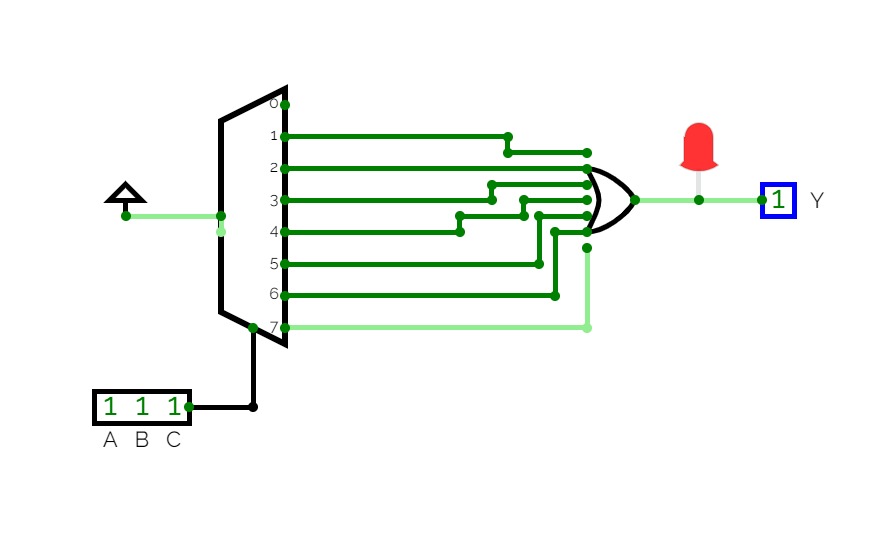

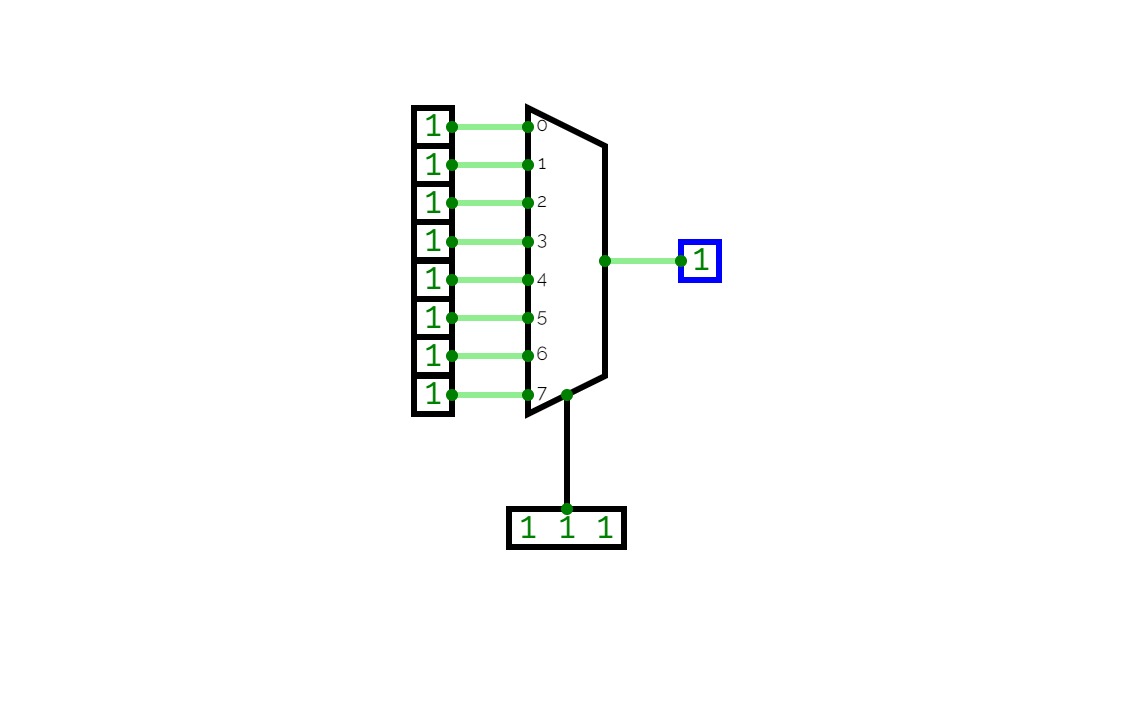

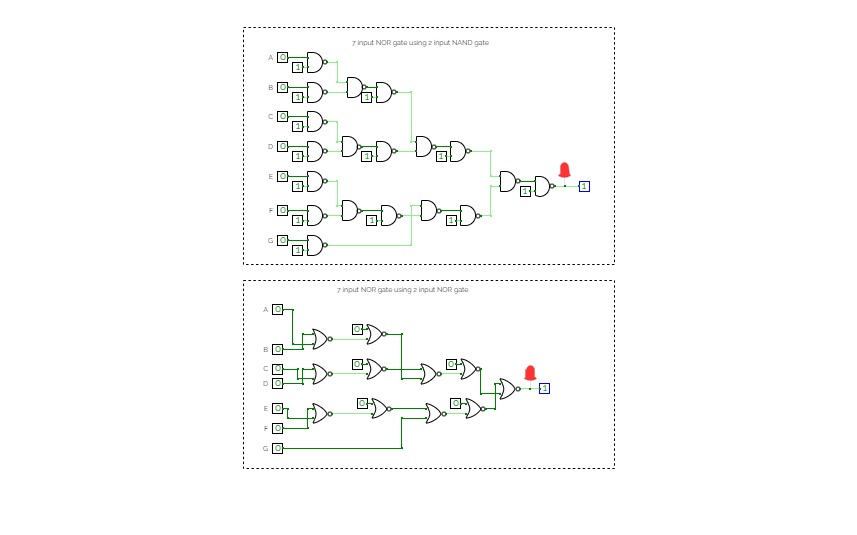

7 input NOR GATE

7 input NOR GATE

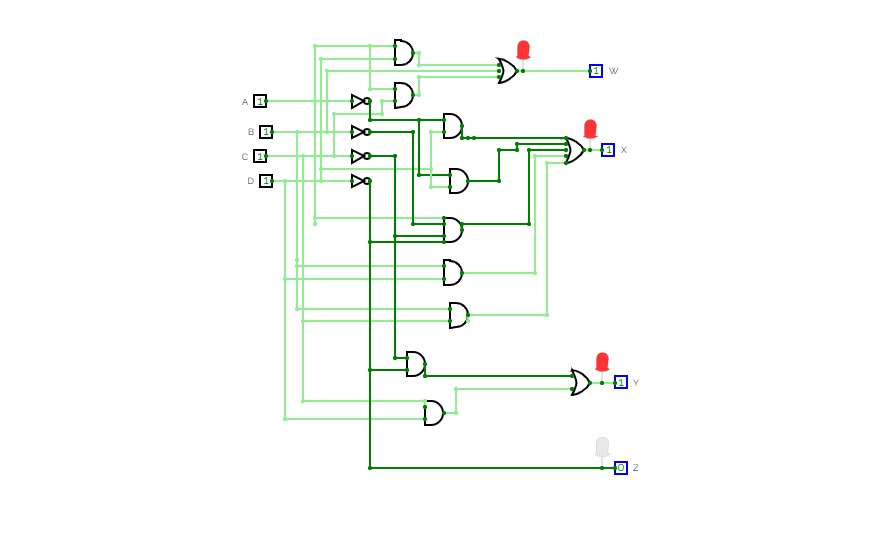

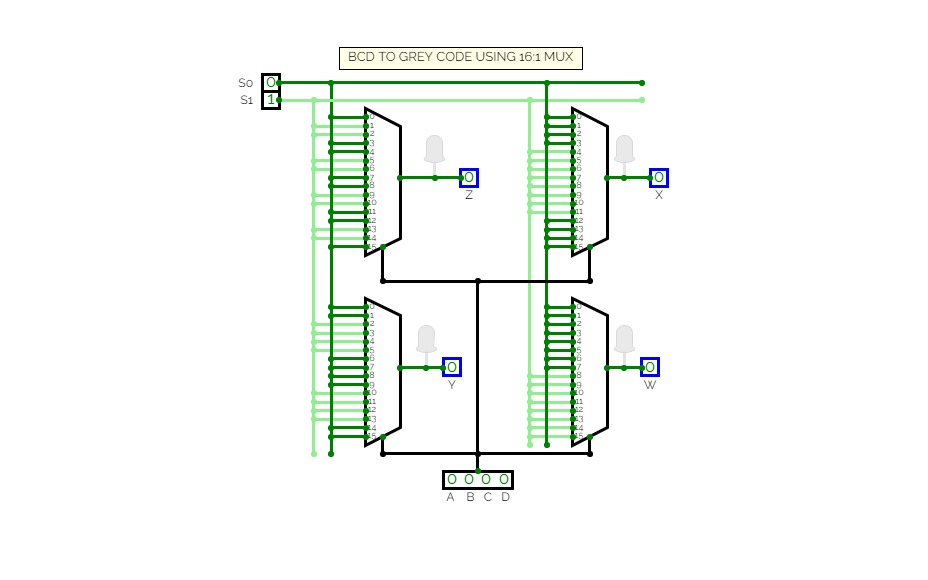

BCD TO GREY USING MUX

BCD TO GREY USING MUX

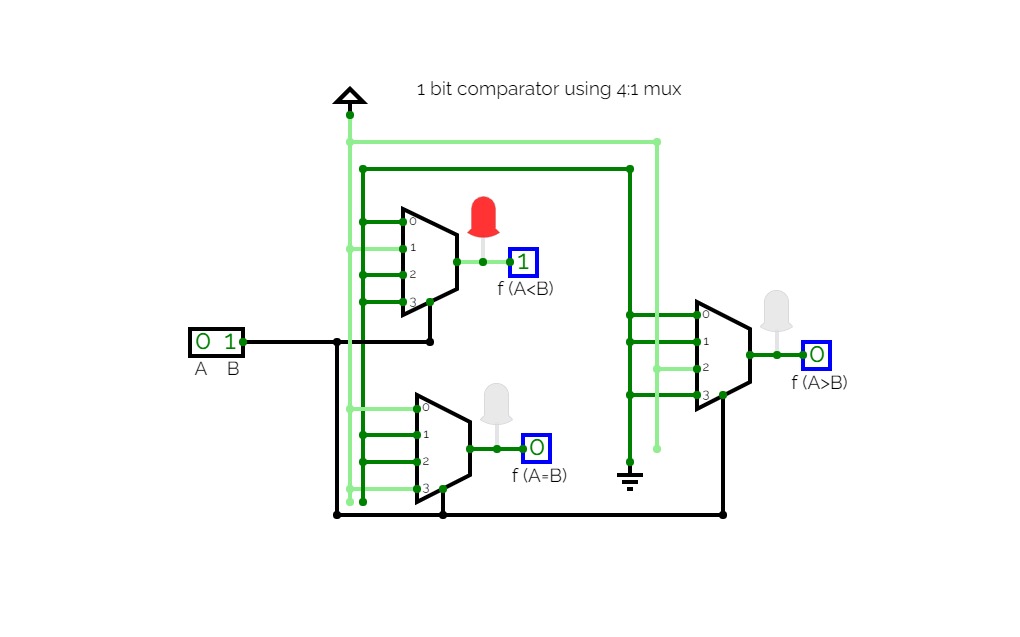

Design 1 bit comparator using 4:1 MUX

Design 1 bit comparator using 4:1 MUX

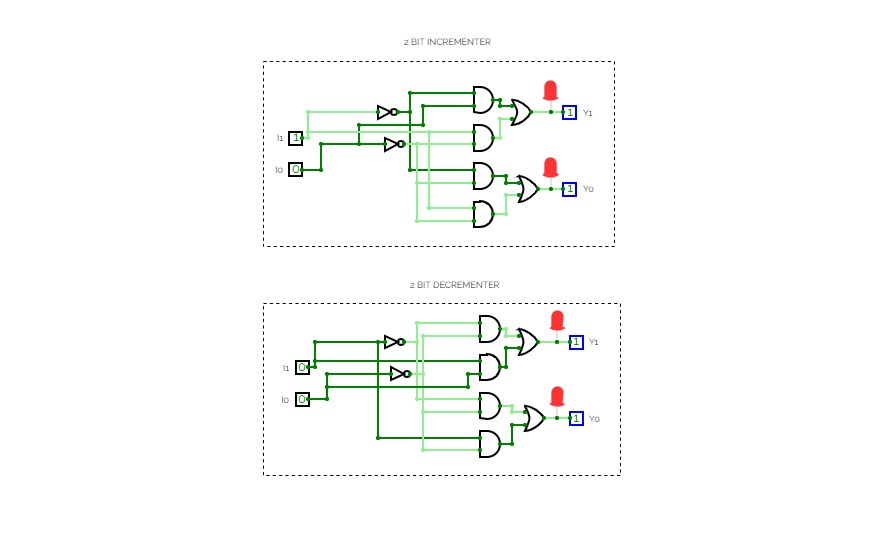

2 bit increment /decrement circuit

2 bit increment /decrement circuit

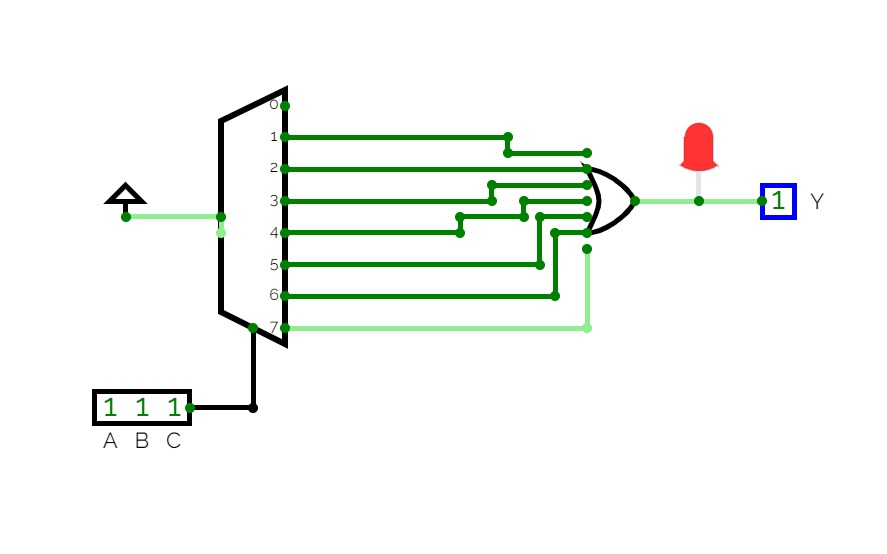

3 input OR gate using 4:1 MUX

3 input OR gate using 4:1 MUX

3 input OR gate using 4:1 MUX

3 input OR gate using 4:1 MUX