BT19ECE045_Jayant Rahate

Member since: 3 years

Educational Institution: Not Entered

Country: Not Entered

Implement the Boolean function using minimum number of NAND Gates

Implement the Boolean function using minimum number of NAND Gates

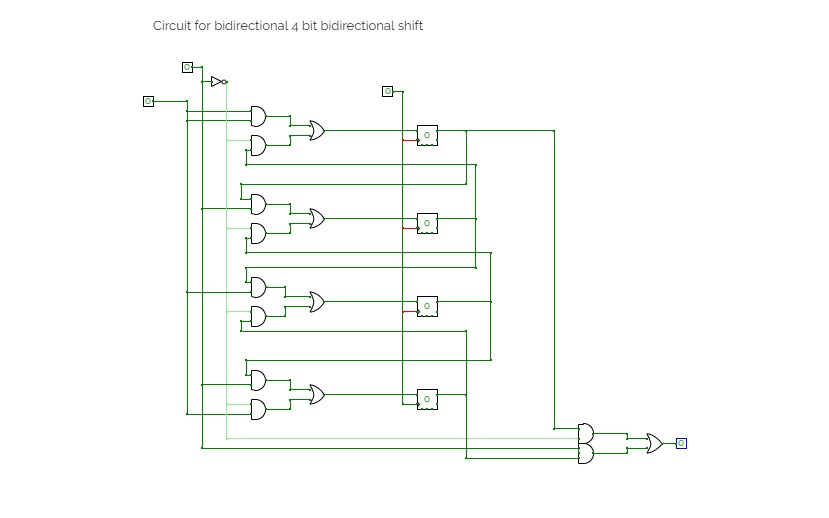

Experiment 12: Verification of truth table of four bit bidirectional shift register

Experiment 12: Verification of truth table of four bit bidirectional shift register

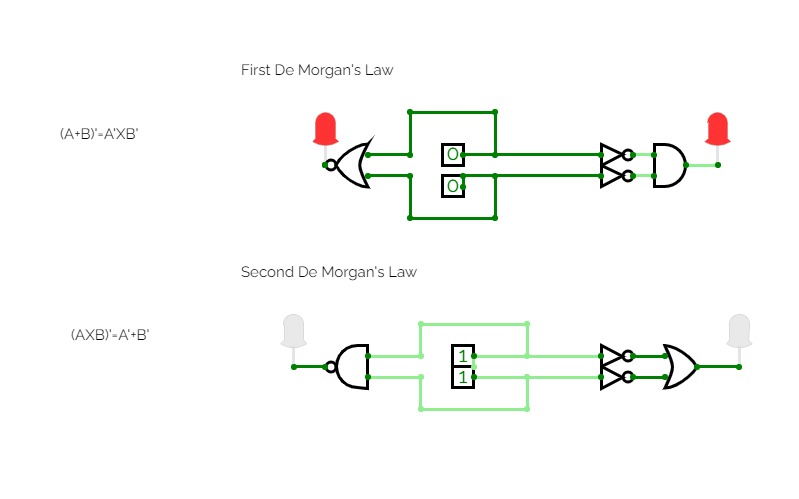

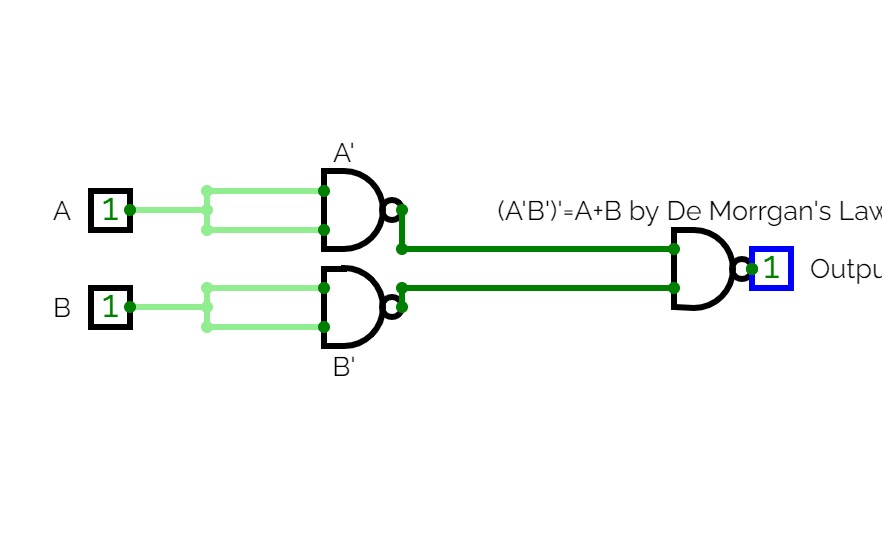

Experiment 2: Verification of De Morgan's Law

Experiment 2: Verification of De Morgan's Law

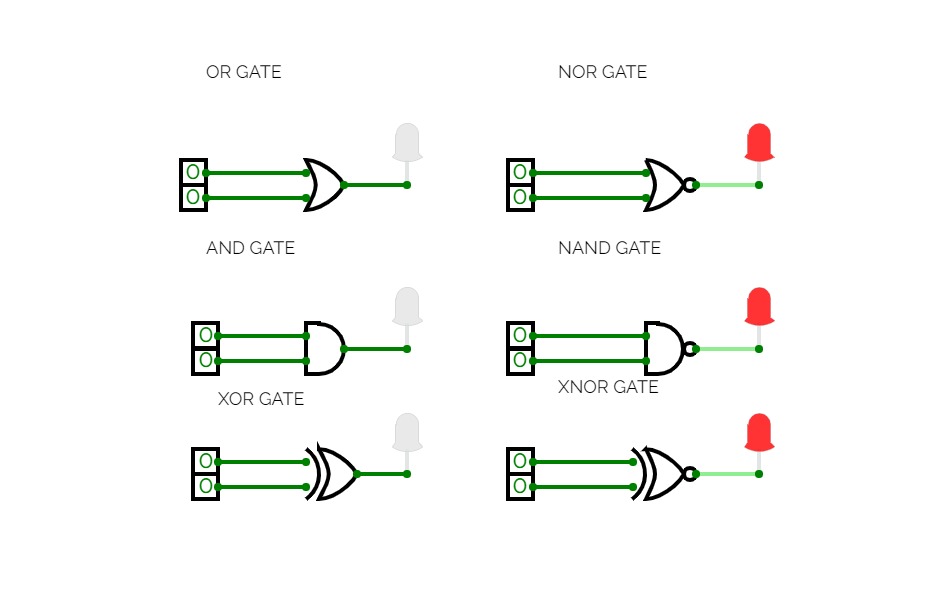

Experiment 1:Verifying truth table for gates

Experiment 1:Verifying truth table for gates

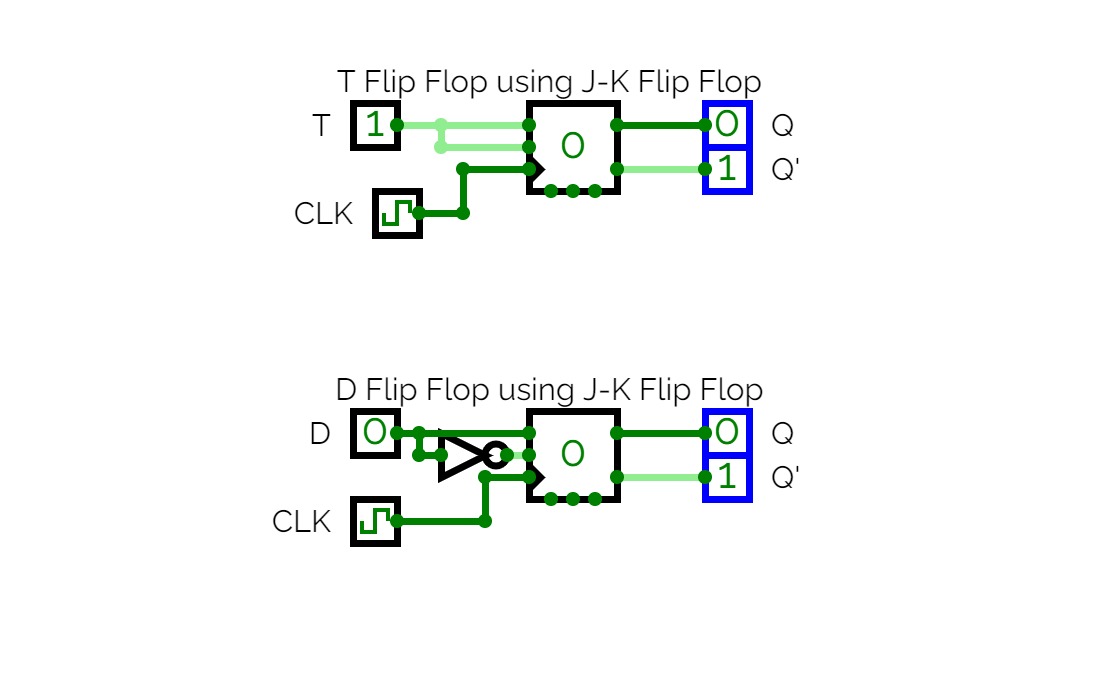

Experiment 11: Implementation of T Flip Flop and D Flip Flop using J-K Flip Flop

Experiment 11: Implementation of T Flip Flop and D Flip Flop using J-K Flip Flop

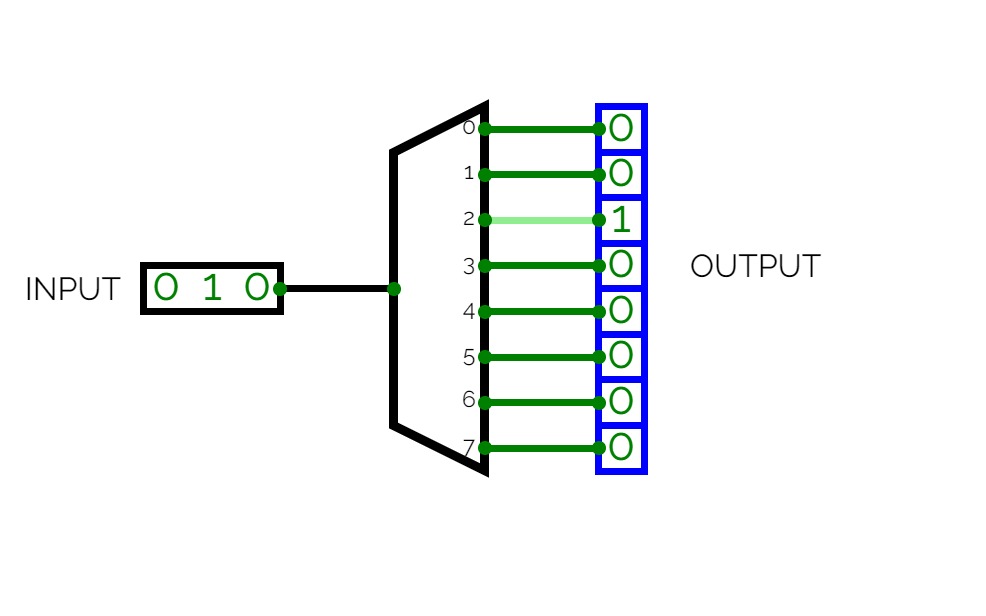

Experiment 7:To verify the truth tables of 3 bit Decoder

Experiment 7:To verify the truth tables of 3 bit Decoder

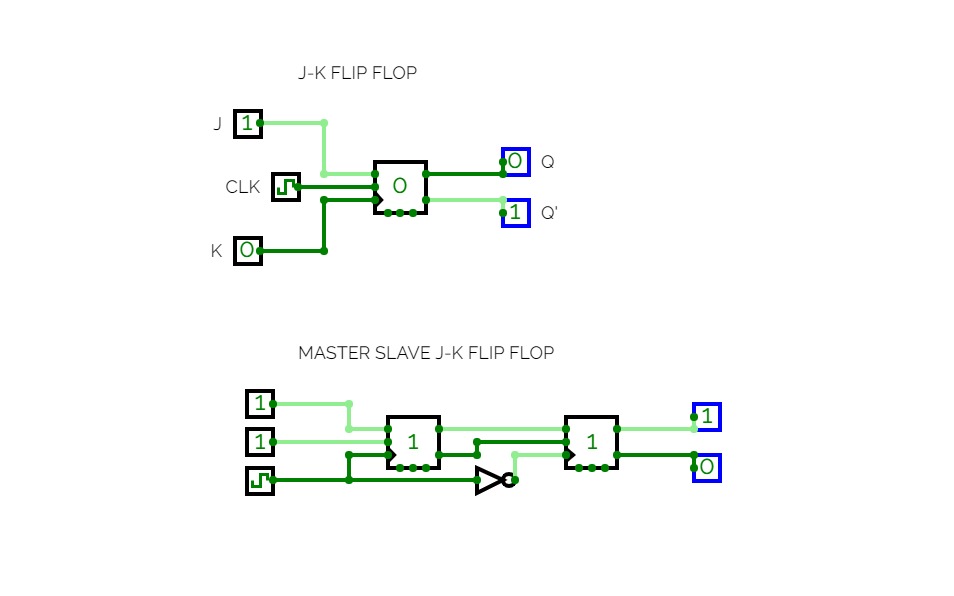

Experiment 10: J-K Flip Flop (VERIFICATION AND IMPLEMENTATION OF MASTER SLAVE USING J-K FLIP FLOP)

Experiment 10: J-K Flip Flop (VERIFICATION AND IMPLEMENTATION OF MASTER SLAVE USING J-K FLIP FLOP)

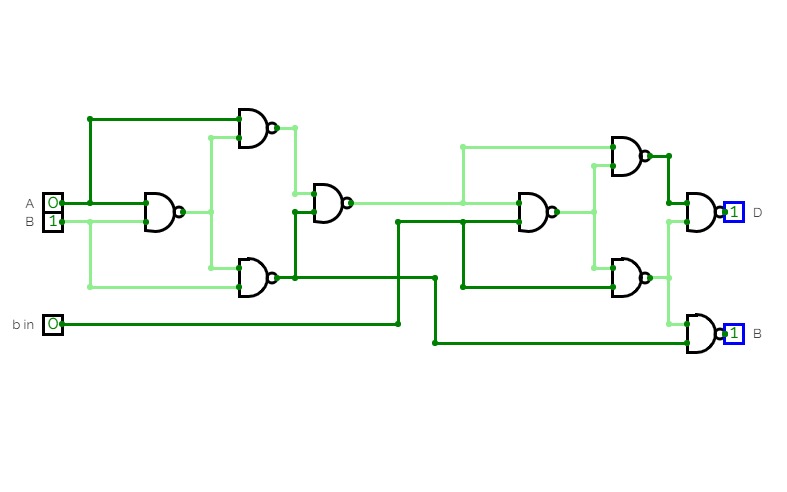

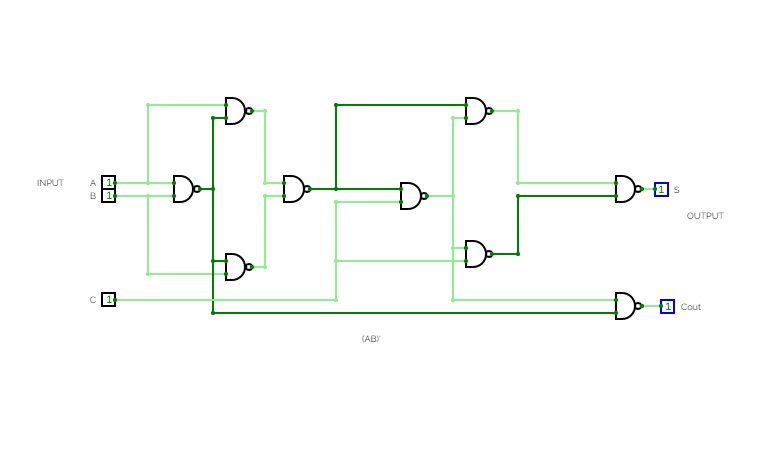

Experiment 8: To design and implement a logic circuit for full adder using NAND gates

Experiment 8: To design and implement a logic circuit for full adder using NAND gates

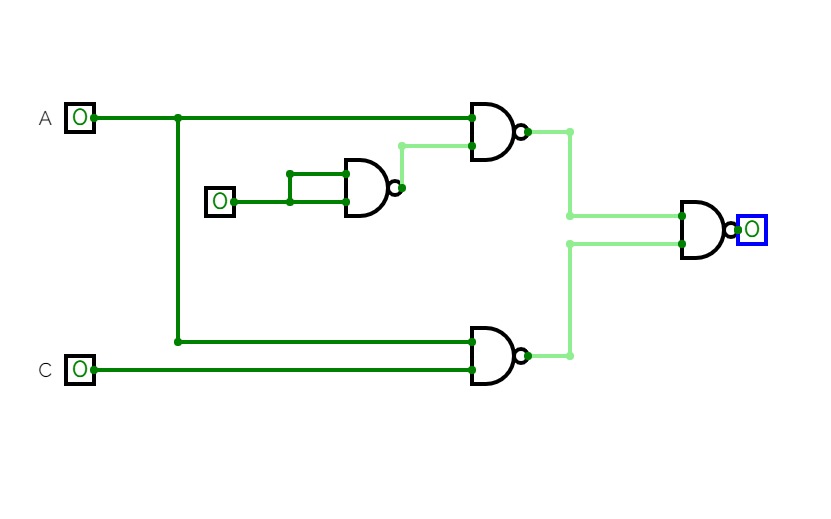

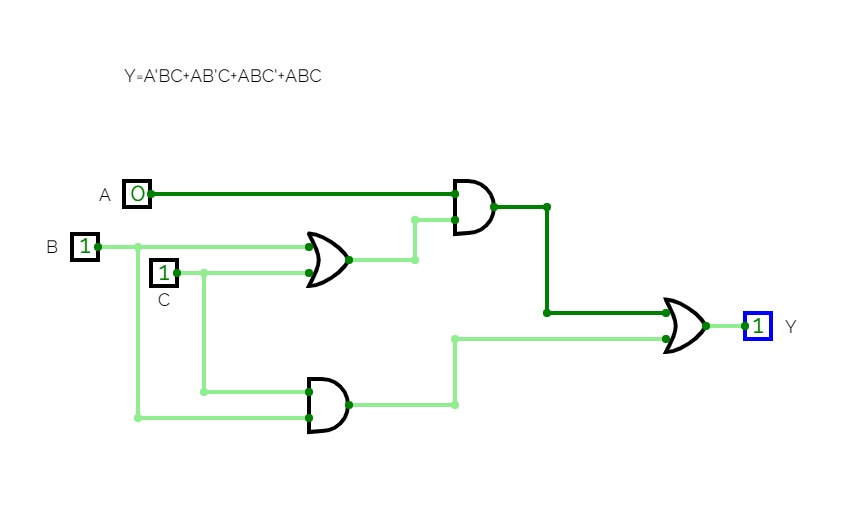

Experiment 5: To design and verify THREE input majority gates

Experiment 5: To design and verify THREE input majority gates

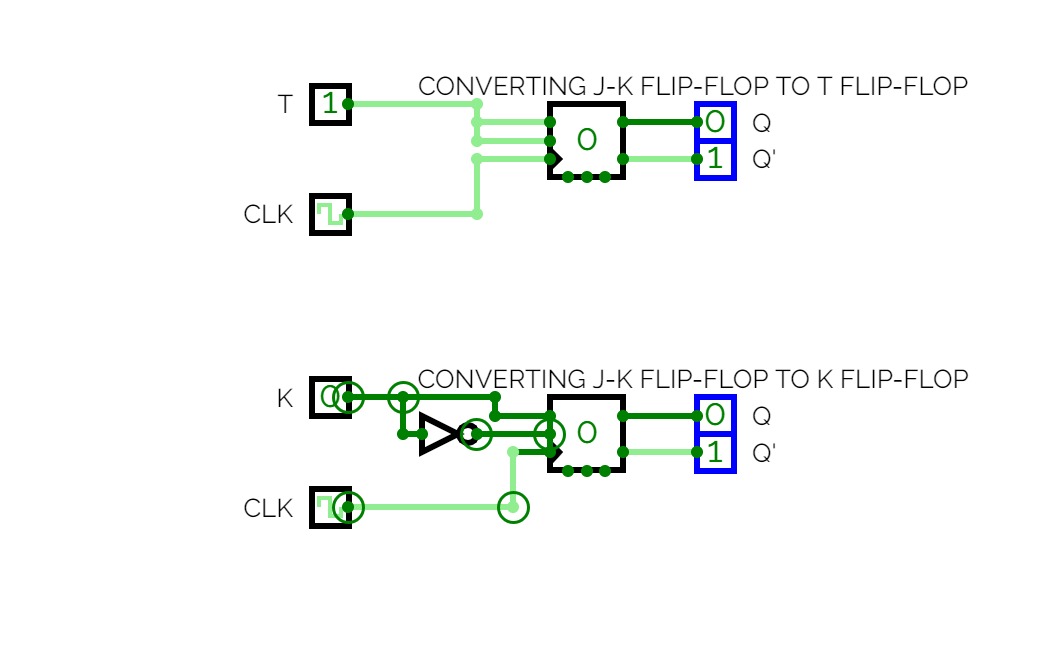

Experiment 11:To convert JK to T Flip flop, JK to D Flip flop

Experiment 11:To convert JK to T Flip flop, JK to D Flip flop

Implement the Boolean function using minimum number of NAND Gates

Implement the Boolean function using minimum number of NAND Gates

Experiment 3:To implement the following boolean functions using minimum number of NAND Gates

Experiment 3:To implement the following boolean functions using minimum number of NAND Gates

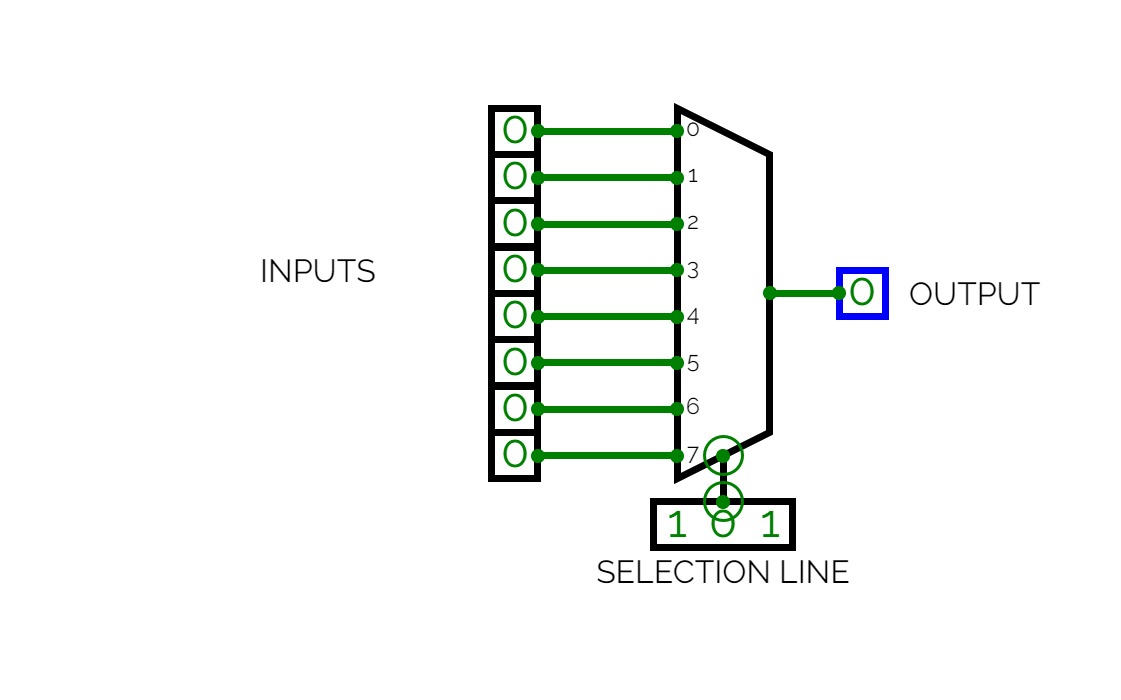

Experiment 6: To verify the truth tables of 8x1 multiplexer

Experiment 6: To verify the truth tables of 8x1 multiplexer

Experiment 9:To design and implement a logic circuit for full subtractor using NAND gates

Experiment 9:To design and implement a logic circuit for full subtractor using NAND gates