SOUMICK ROY

Member since: 4 years

Educational Institution: Not Entered

Country: Not Entered

Design PISO register.

Design PISO register.

4 BIT PARALLEL ADDER

4 BIT PARALLEL ADDER

D flip flop

D flip flop

D flip-flop to T flip-flop

D flip-flop to T flip-flop

SEVEN SEGMENT DECODER

SEVEN SEGMENT DECODER

A 3

A 3

A 3

A 3

and,or,not gate using nand gate

and,or,not gate using nand gate

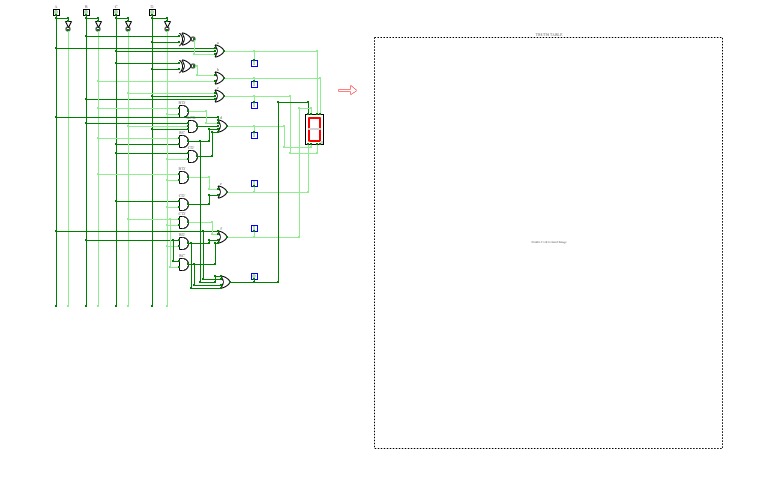

and,or,not gate using nor gate

and,or,not gate using nor gate

half adder using nand gate

half adder using nand gate

half adder using nor gate

half adder using nor gate

half subtractor using nand gate

half subtractor using nand gate

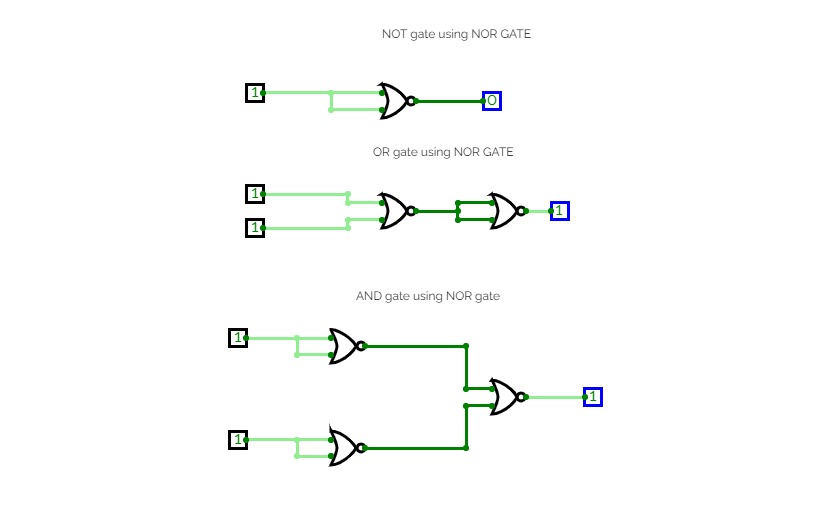

MUX is a universal gate

MUX is a universal gate

AB+BC+CD+DA

AB+BC+CD+DA

DESIGN A HALF ADDER SUBTRACTOR USING ENABLE LINE

DESIGN A HALF ADDER SUBTRACTOR USING ENABLE LINE

parity checker

parity checker

S R flip flop to D flip flop

S R flip flop to D flip flop

Design SISO register.

Design SISO register.

Design Universal Register using multiplexer and flip-flops.

Design Universal Register using multiplexer and flip-flops.

full subtractor using basic gates

full subtractor using basic gates

Untitled

Untitled

NAND GATE USING NOR GATE

NAND GATE USING NOR GATE

F(A,B,C)=SUM(1,3,5,6)

F(A,B,C)=SUM(1,3,5,6)

CONVERT D FLIP FLOP TO JK FLIP FLOP

CONVERT D FLIP FLOP TO JK FLIP FLOP

Design a 3-bit synchronous MOD-3 counter using JK - f/f.

Design a 3-bit synchronous MOD-3 counter using JK - f/f.

Design a 3-bit synchronous counter that count in straight binary (starting from 000) using D- f/f.

Design a 3-bit synchronous counter that count in straight binary (starting from 000) using D- f/f.

4 BIT PARALLEL ADDER

4 BIT PARALLEL ADDER