Dr Vijay Singh Bist

Member since: 3 years

Educational Institution: Department of Instrumentation Engineering, School of Engineering and Technology, HNB Garhwal University Srinagar (Garhwal)

Country: India

4 X 1 MUX using gates

4 X 1 MUX using gates

Half adder using MUXs

Half adder using MUXs

Branch name

Branch name

Asynchronous MOD-5 Counter

Asynchronous MOD-5 Counter

4-bit ripple counter

4-bit ripple counter

Higher MUX using lower MUXs

Higher MUX using lower MUXs

2-bit synchronous counter

2-bit synchronous counter

PARITY CHECKER

PARITY CHECKER

Full Adder From 2 half Adders

Full Adder From 2 half Adders

Full Adder From 2 half Adders

Full Adder From 2 half Adders

4 X 1 MUX using gates

4 X 1 MUX using gates

4-bit ripple counter

4-bit ripple counter

SR flip- flop using NAND

SR flip- flop using NAND

Design basic, universal, Ex-or, Ex-nor gate using Nand gate only.

Design basic, universal, Ex-or, Ex-nor gate using Nand gate only.

Design basic, universal, Ex-or, Ex-nor gate using Nand gate only.

Design basic, universal, Ex-or, Ex-nor gate using Nand gate only.

OR GATE

OR GATE

verify truth table of basic gates ,buffer and universal gate.

verify truth table of basic gates ,buffer and universal gate.

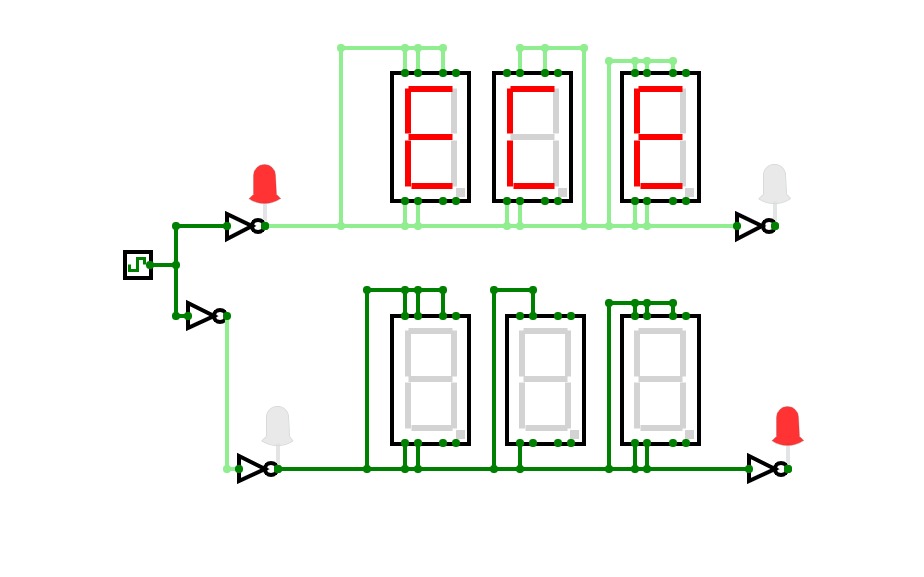

2-bit counter with display

2-bit counter with display

4 X 1 MUX using gates

4 X 1 MUX using gates

16 X 1 MUX using only 2 X 1 MUXs

16 X 1 MUX using only 2 X 1 MUXs

HA using HS and NOT

HA using HS and NOT

2 X 1 MUX

2 X 1 MUX

1 X 2 DMUX

1 X 2 DMUX

JK Flip Flops

JK Flip Flops

Two input AND gate using MUXs

Two input AND gate using MUXs

Hald adder using DMUXs

Hald adder using DMUXs

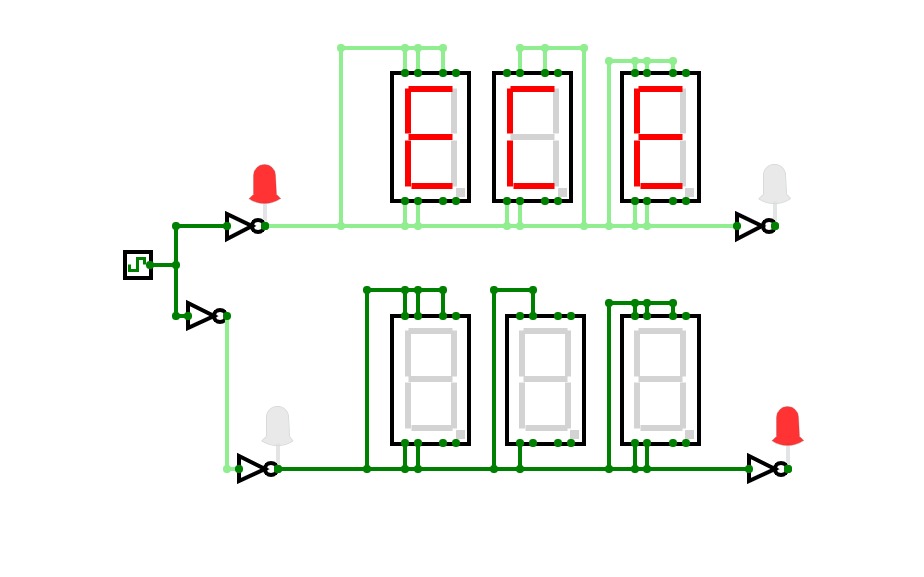

2-bit counter with display

2-bit counter with display

FLIP FLIPS CONVERSION

FLIP FLIPS CONVERSION

Design and verify 4-bit Asychronous up / down couter

Design and verify 4-bit Asychronous up / down couter

asynchronous decade counter

asynchronous decade counter

SR flip- flop using NAND

SR flip- flop using NAND

Untitled

Untitled

XOR USING FIVE NAND

XOR USING FIVE NAND

XOR USING NAND

XOR USING NAND

Untitled

Untitled

ASSICIATIVE LAW FOR AND LOGIC

ASSICIATIVE LAW FOR AND LOGIC

Absorption law for OR AND LOGIC

Absorption law for OR AND LOGIC

IDEMPOTENT LAW FOR OR LOGIC

IDEMPOTENT LAW FOR OR LOGIC

COMPLEMENTATION LAW FOR OR LOGIC

COMPLEMENTATION LAW FOR OR LOGIC

IDEMPOTENT LAW FOR AND LOGIC

IDEMPOTENT LAW FOR AND LOGIC

COMPLEMENT LAW FOR AND LOGIC

COMPLEMENT LAW FOR AND LOGIC

TWO LEVEL IMPLEMENTATION OF POS FORM

TWO LEVEL IMPLEMENTATION OF POS FORM

2-bit counter with display

2-bit counter with display

AND GATE

AND GATE

OR GATE

OR GATE

NAND

NAND

NOR

NOR

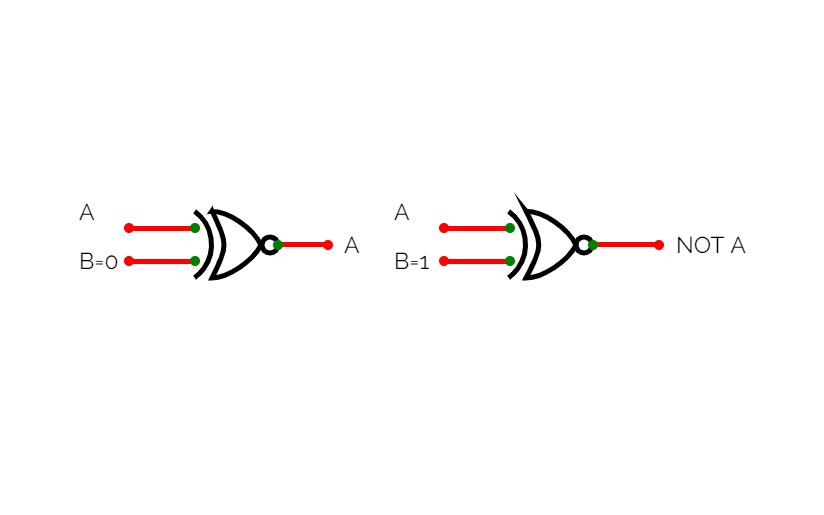

EX OR AS NOT AND BUFFER

EX OR AS NOT AND BUFFER

XOR AS NOT

XOR AS NOT

DEMORGAN FIRST LAW

DEMORGAN FIRST LAW

DEMORGAN SECOND LAW

DEMORGAN SECOND LAW

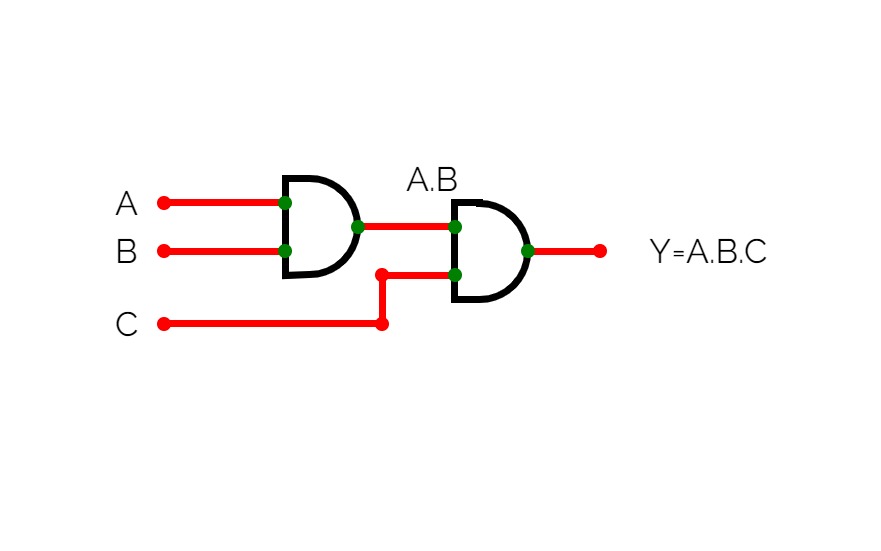

THREE INPUT AND USING TWO INPUT AND

THREE INPUT AND USING TWO INPUT AND

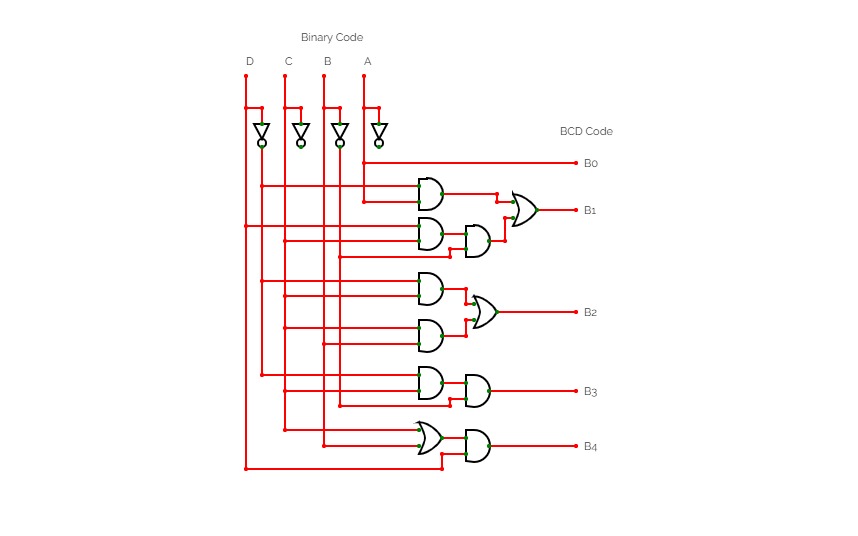

Binary to BCD

Binary to BCD

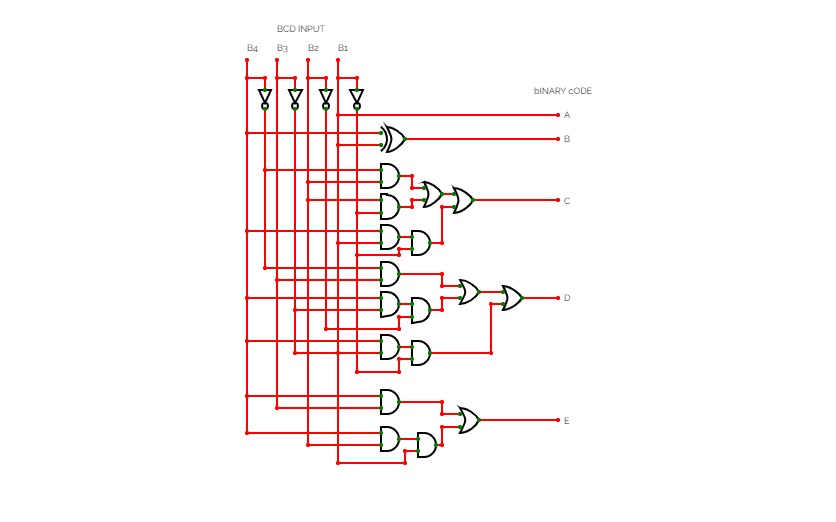

BCD TO BINARY

BCD TO BINARY

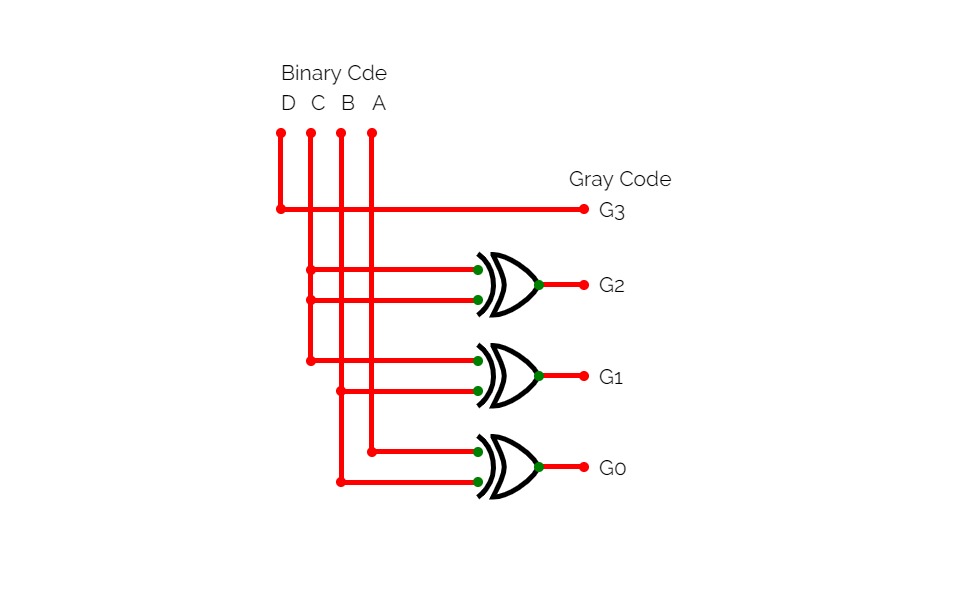

BINARY TO GRAY

BINARY TO GRAY

GRAY TO BINARY

GRAY TO BINARY

Untitled

Untitled

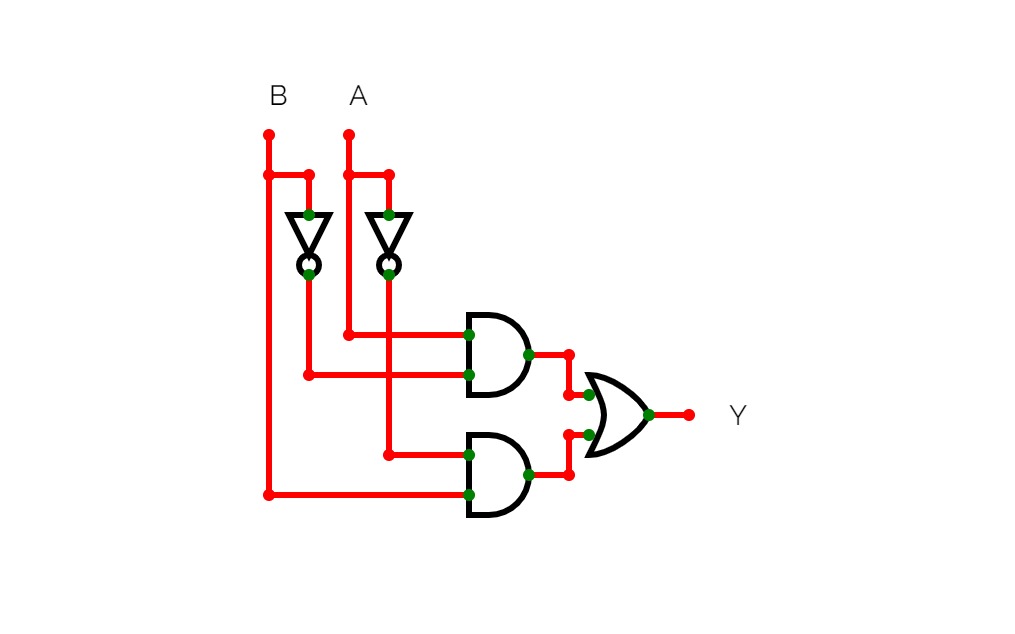

2 BIT COMPARATOR

2 BIT COMPARATOR

THREE BIT EVEN PARITY GENERATOR

THREE BIT EVEN PARITY GENERATOR

CC-1

CC-1

CC-2 NAND

CC-2 NAND

CC-3 NOR

CC-3 NOR

mux1

mux1

mux2

mux2

MUX3

MUX3

mux4

mux4

mux5

mux5

mux7

mux7

MUX6

MUX6

Untitled

Untitled

HS USING BASIC GATES

HS USING BASIC GATES

HS NOR NOR

HS NOR NOR

HS USING XOR, NANAD

HS USING XOR, NANAD

FS USIN BASIC GATES

FS USIN BASIC GATES

FS USING TWO HS

FS USING TWO HS

FS USING NANND

FS USING NANND

FS USING NAND-NAND GATES

FS USING NAND-NAND GATES

FS USING NOR NOR

FS USING NOR NOR

OCTAL TO BINAY

OCTAL TO BINAY

XOR USING BASIC GATES

XOR USING BASIC GATES

HA USING NOR NOR

HA USING NOR NOR

D F/F USING NAND

D F/F USING NAND

2-bit asynchronous counter

2-bit asynchronous counter

DISTRIBUTION LAW OR OVER AND

DISTRIBUTION LAW OR OVER AND

HS USING NAND

HS USING NAND

ABSORPTION LAW FOR OR AND LOGIC

ABSORPTION LAW FOR OR AND LOGIC

FOUR INPUT NAND USING TWO INPUT NAND

FOUR INPUT NAND USING TWO INPUT NAND

4 X 1 MUX using gates

4 X 1 MUX using gates

SR flip- flop using NAND

SR flip- flop using NAND

Design basic, universal, Ex-or, Ex-nor gate using Nand gate only.

Design basic, universal, Ex-or, Ex-nor gate using Nand gate only.

Full Adder

Full Adder

3-bit Asynchronous up/down counter using control switch

3-bit Asynchronous up/down counter using control switch

4-bit synchronous counter

4-bit synchronous counter

4 X 1 MUX using gates

4 X 1 MUX using gates

SR flip- flop using NAND

SR flip- flop using NAND

Design basic, universal, Ex-or, Ex-nor gate using Nand gate only.

Design basic, universal, Ex-or, Ex-nor gate using Nand gate only.

Design basic, universal, Ex-or, Ex-nor gate using Nand gate only.

Design basic, universal, Ex-or, Ex-nor gate using Nand gate only.

FULL ADDER USING XOR AND NAND GATES

FULL ADDER USING XOR AND NAND GATES

TWO LEVEL IMPLEMENTATION OF SOP

TWO LEVEL IMPLEMENTATION OF SOP

4 X 1 MUX using gates

4 X 1 MUX using gates

2-bit counter with display

2-bit counter with display

SR flip- flop using NAND

SR flip- flop using NAND

16 X 1 MUX using only 2 X 1 MUXs

16 X 1 MUX using only 2 X 1 MUXs

Branch name

Branch name

FLIP FLIPS CONVERSION

FLIP FLIPS CONVERSION

Design and verify 4-bit Asychronous up / down couter

Design and verify 4-bit Asychronous up / down couter

4-bit ripple counter

4-bit ripple counter

asynchronous decade counter

asynchronous decade counter

Asynchronous MOD-5 Counter

Asynchronous MOD-5 Counter

3-bit Asynchronous up/down counter using control switch

3-bit Asynchronous up/down counter using control switch

4-bit synchronous counter

4-bit synchronous counter

2-bit synchronous counter

2-bit synchronous counter