T Vyomakesh aka Twi Sam

Member since: 4 years

Educational Institution: Not Entered

Country: Not Entered

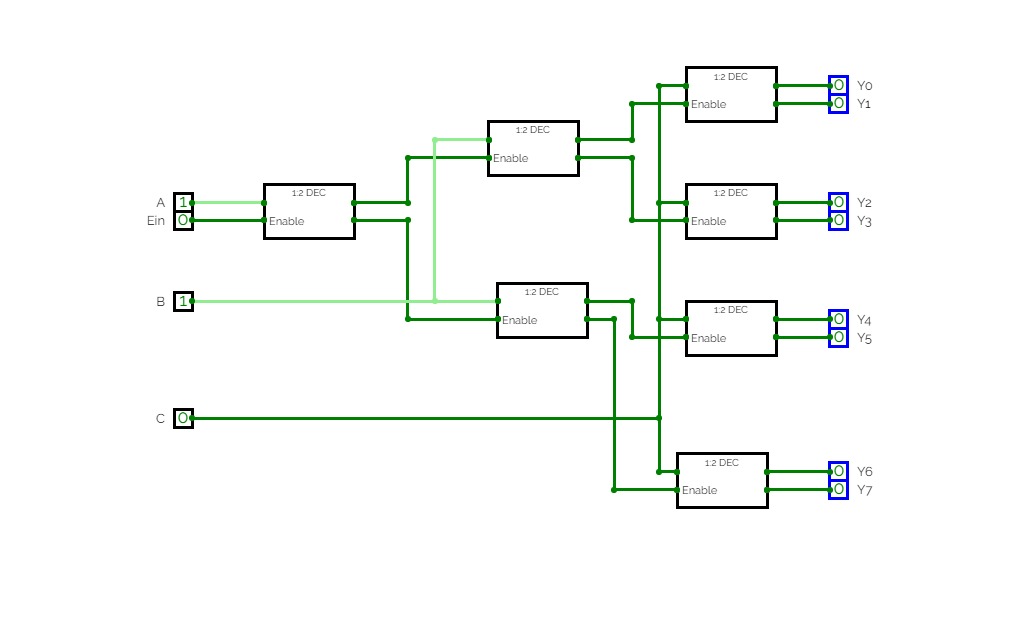

3:8 DEC using 1:2 DEC

3:8 DEC using 1:2 DEC

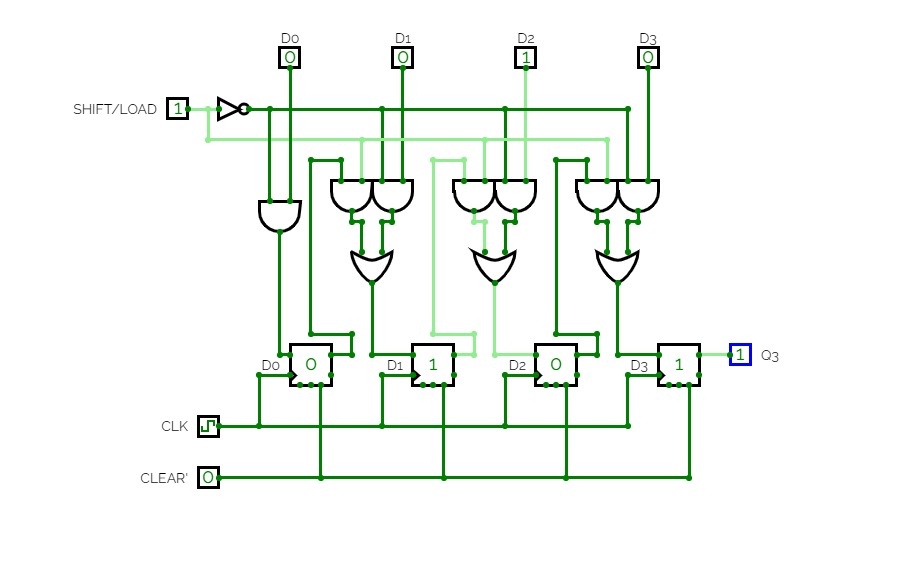

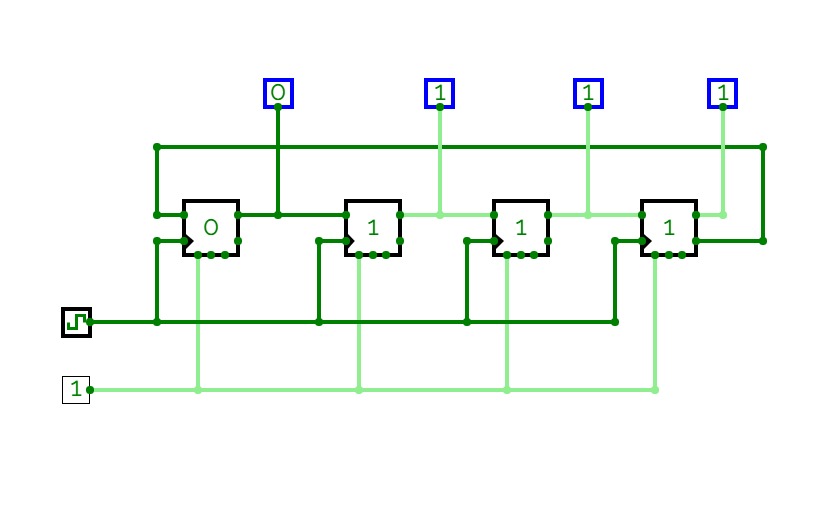

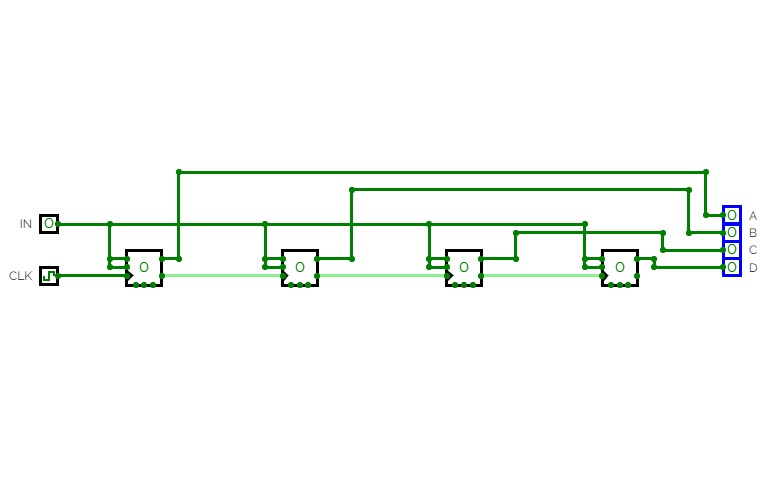

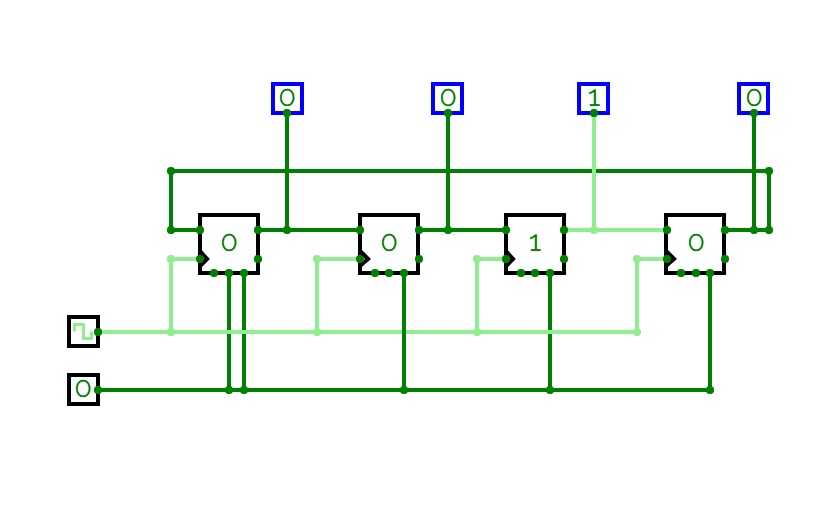

PISO

PISO

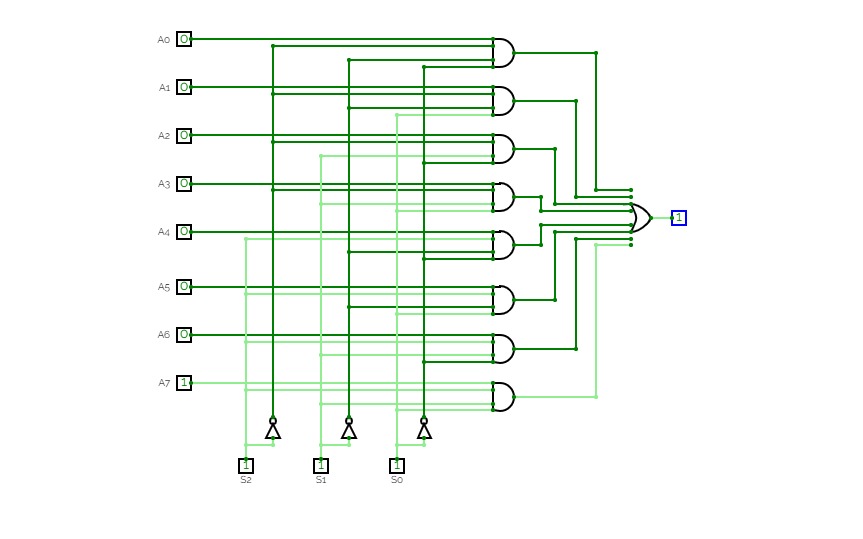

8 to 1 mux internal

8 to 1 mux internal

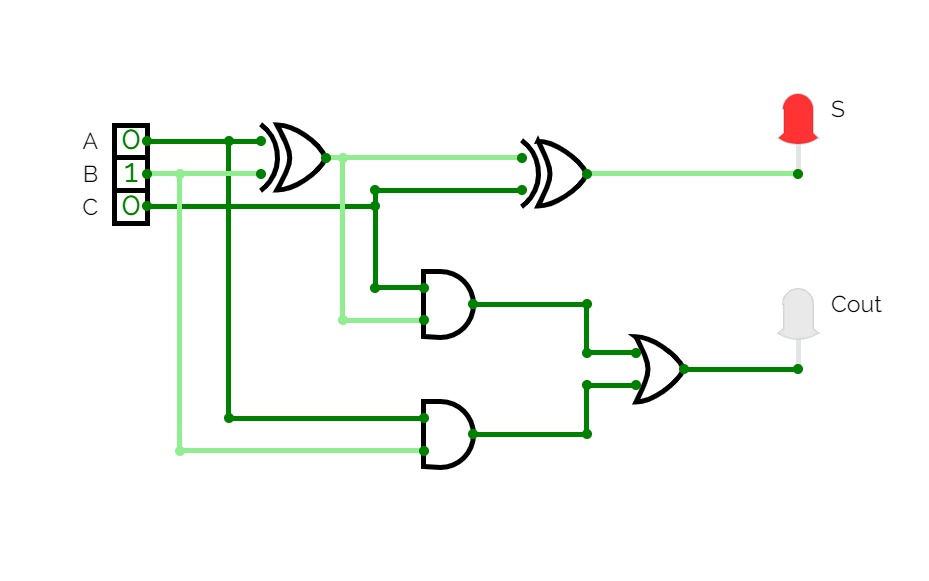

full adder

full adder

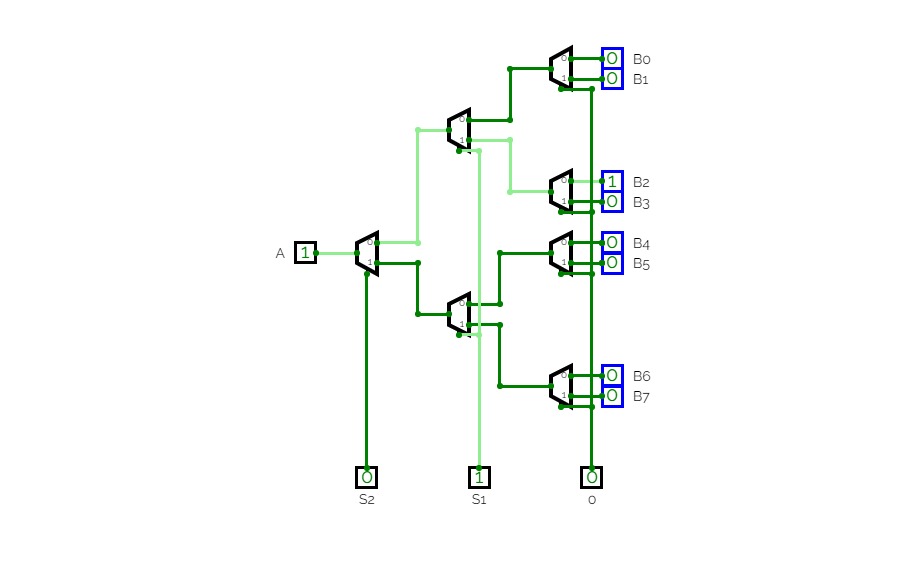

1:8 demux

1:8 demux

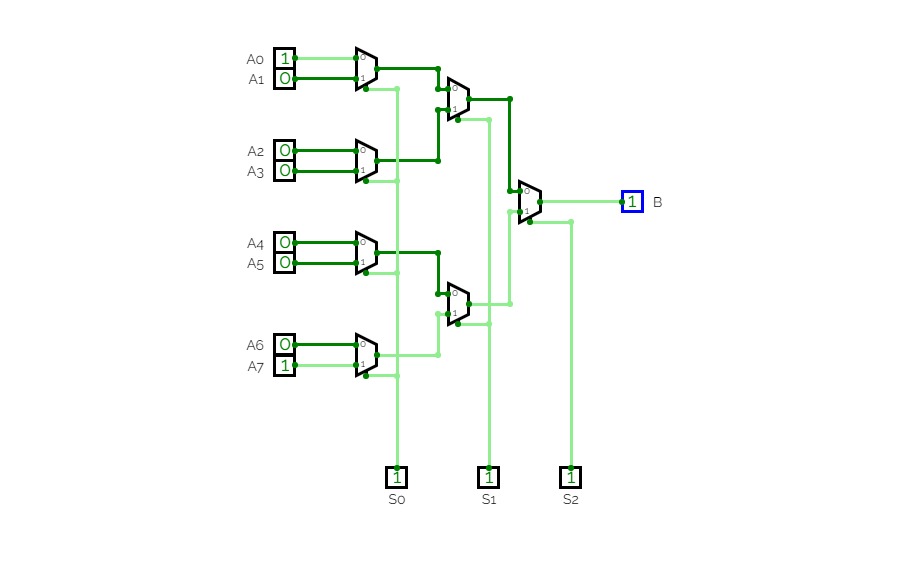

8:1 MUX

8:1 MUX

8:3 encoder

8:3 encoder

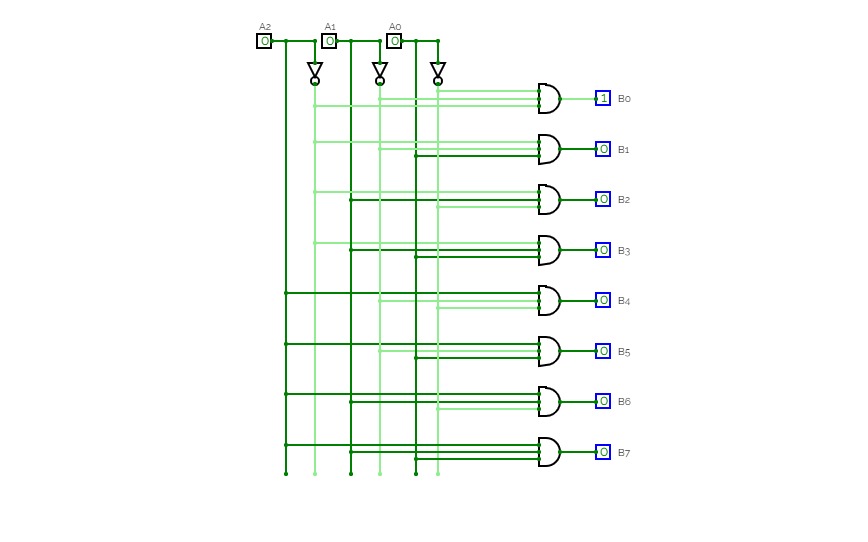

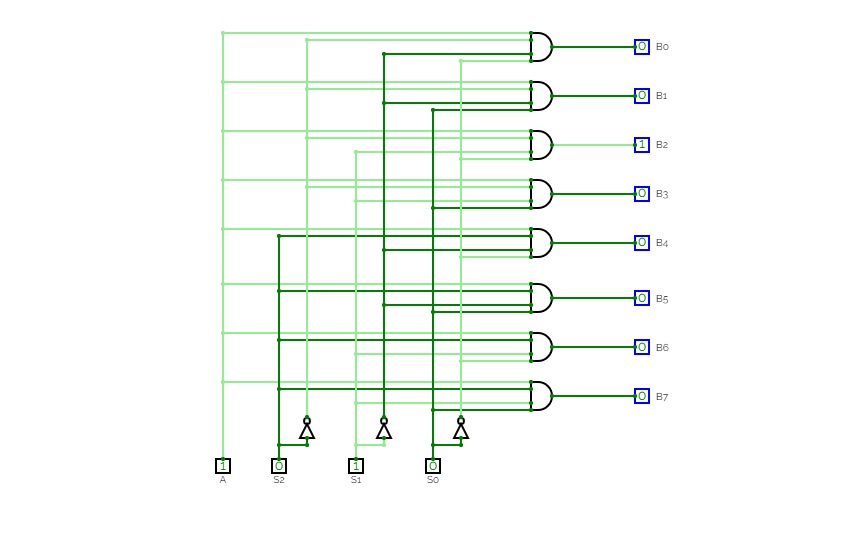

3:8 DECODER

3:8 DECODER

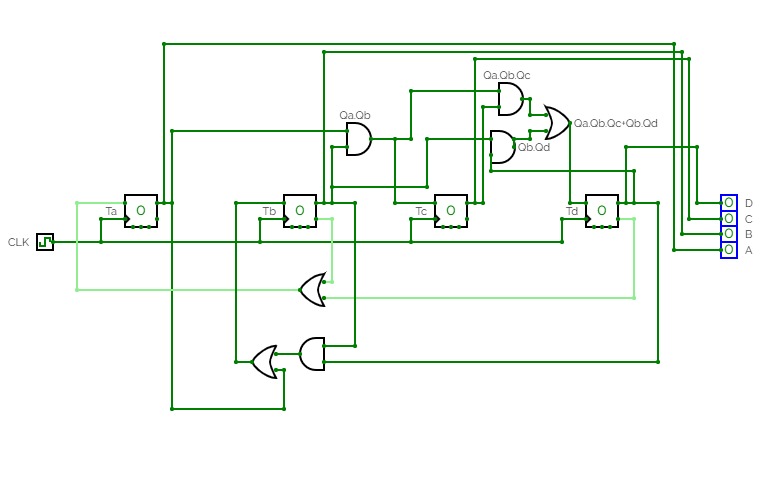

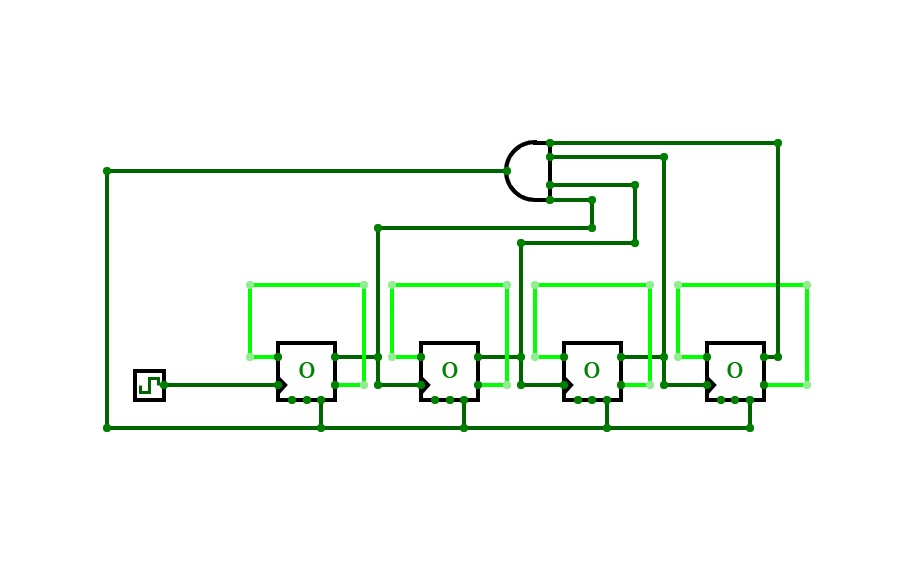

4 bit jhonson counter

4 bit jhonson counter

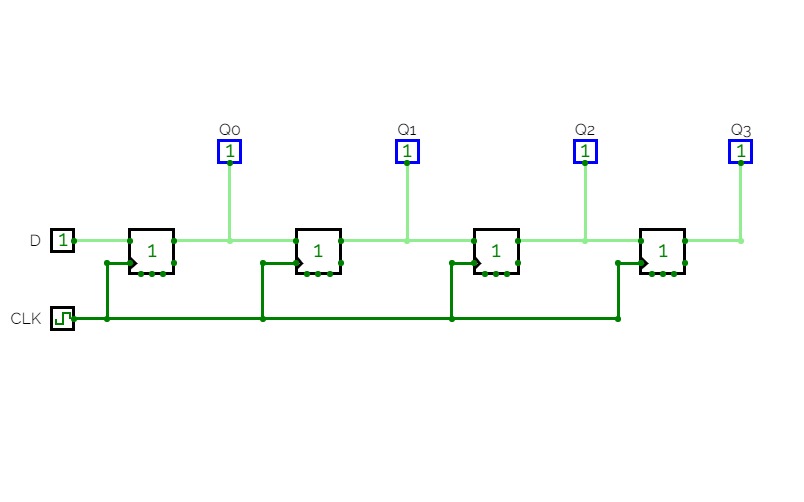

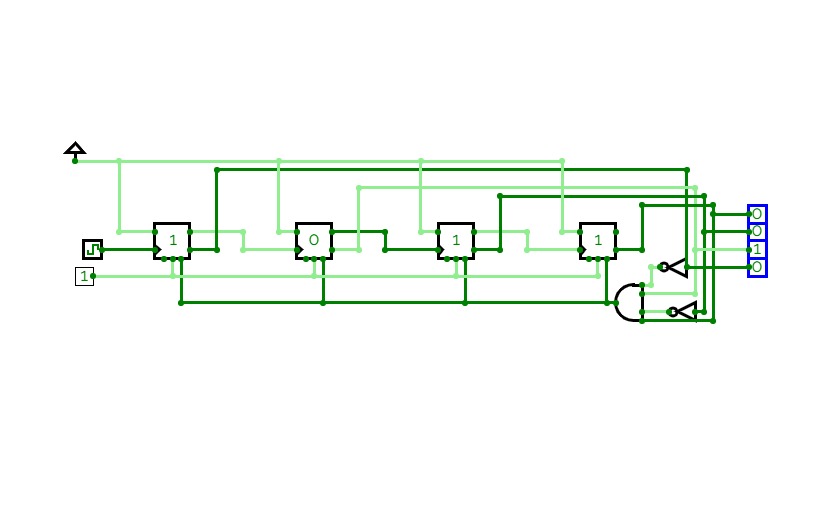

SIPO

SIPO

4 bit asynchronous counter

4 bit asynchronous counter

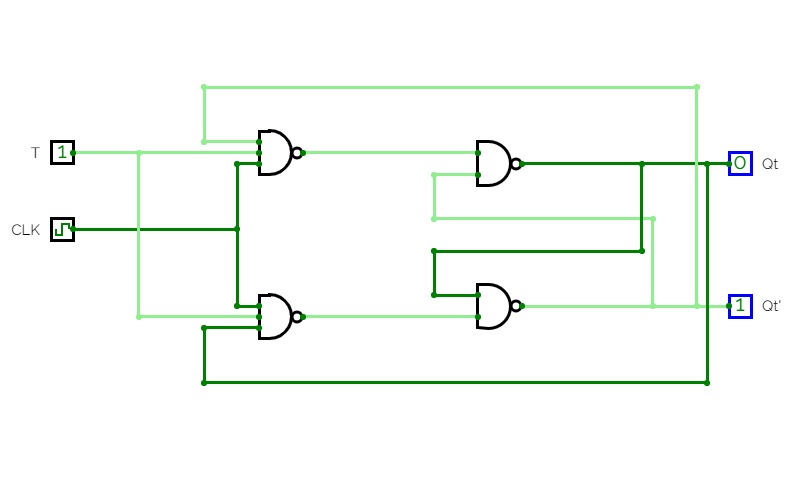

T flip flop

T flip flop

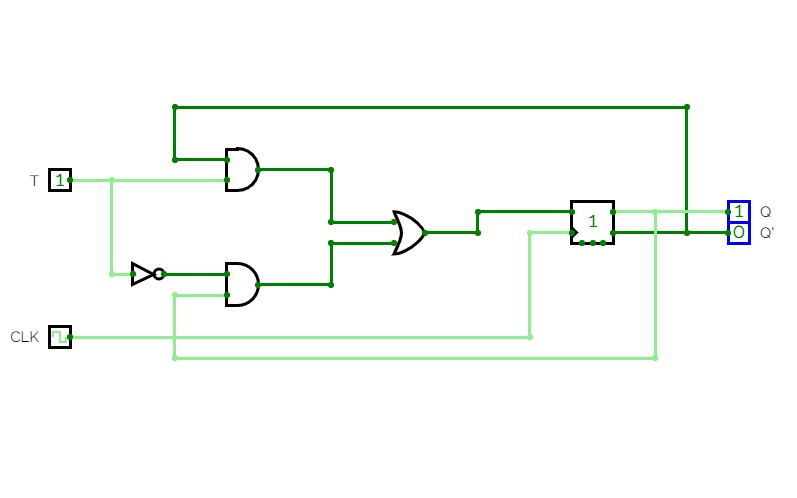

t flip flop new

t flip flop new

1 to 8 demux internal

1 to 8 demux internal

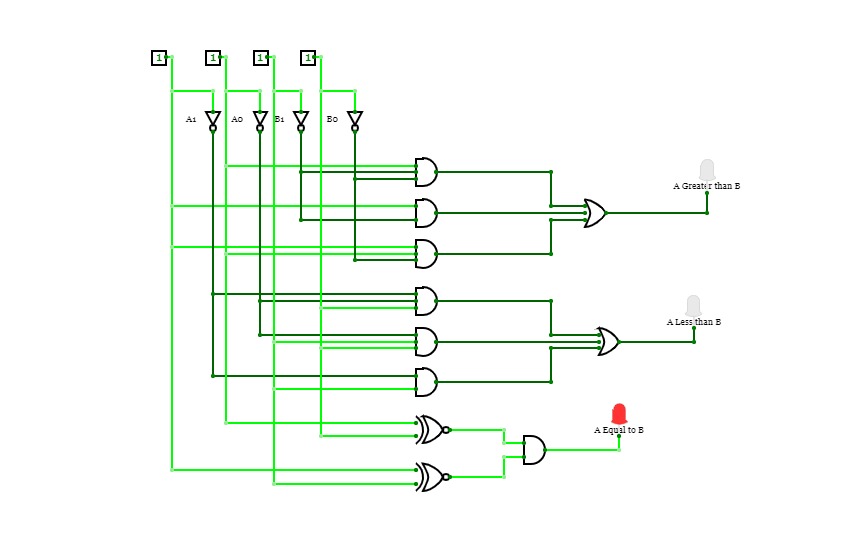

Implement a 2-bit magnitude comparator for checking < and = condtions.

Implement a 2-bit magnitude comparator for checking < and = condtions.

4-bit ring

4-bit ring

MOD-11 synchronous up counter

MOD-11 synchronous up counter

mod 12 up counter with D flip flop

mod 12 up counter with D flip flop

down counter d flip flop

down counter d flip flop

4-bit BCD synchronous up counter using inbuilt T Flip flop module.

4-bit BCD synchronous up counter using inbuilt T Flip flop module.

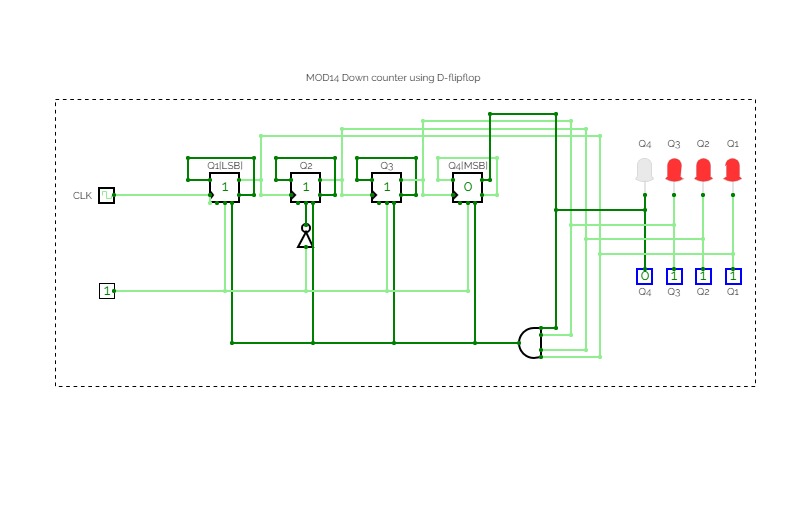

mod 14 down counter using d flip flop

mod 14 down counter using d flip flop

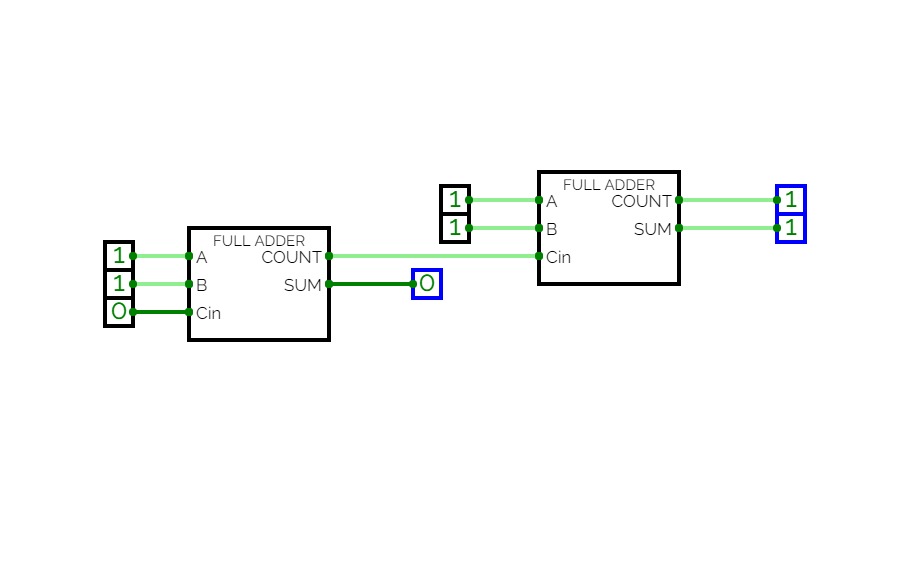

2 bit binary circuit using full adders

2 bit binary circuit using full adders

mod 14 down counter using d flip flop

mod 14 down counter using d flip flop

Digital Systems

Digital Systems

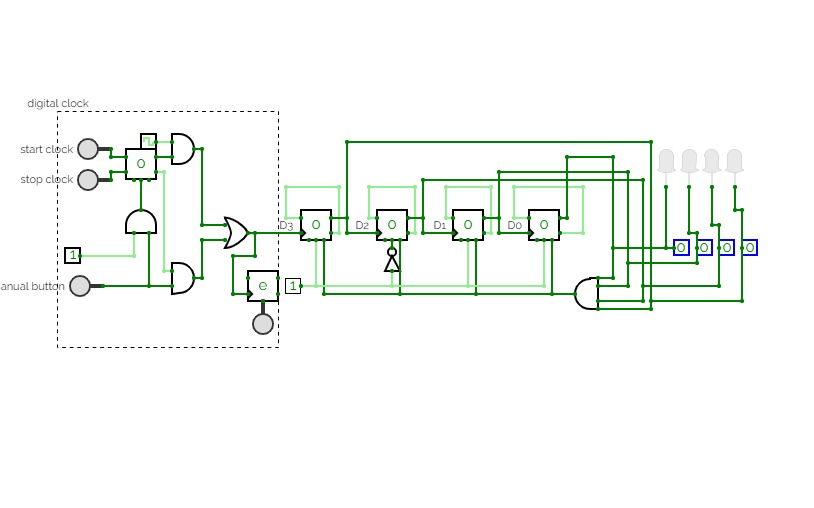

mod 14 down counter using d flip flop

mod 14 down counter using d flip flop

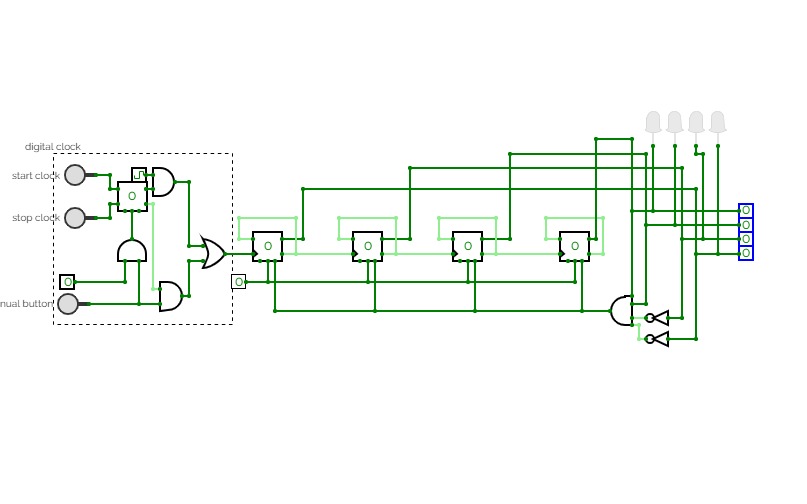

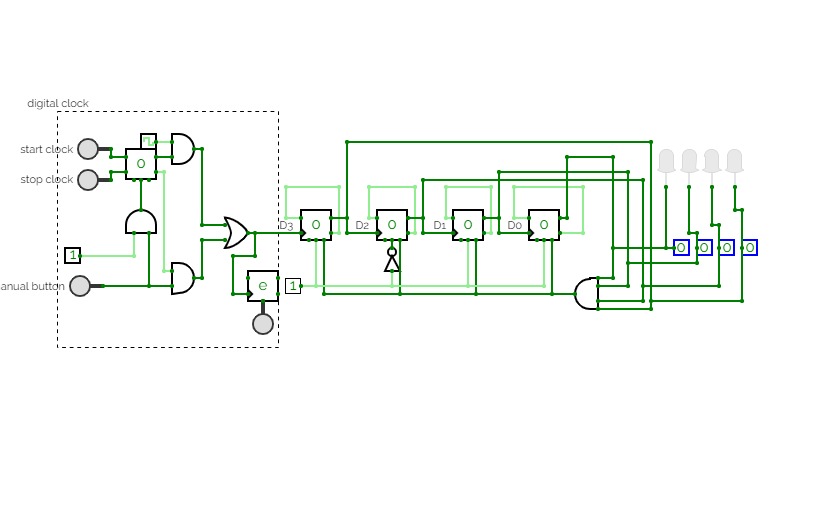

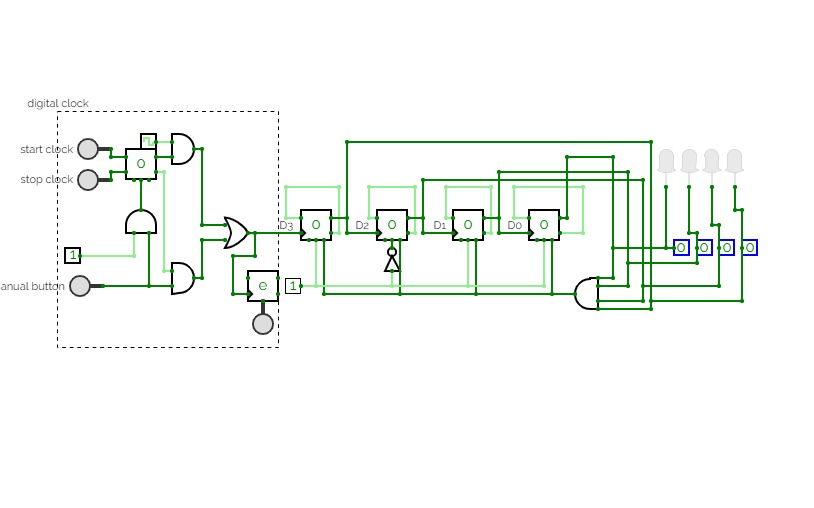

Digital Clock

Digital Clock