Kaivalya Pitale

Member since: 4 years

Educational Institution: Pune Institute of Computer Technology

Country: India

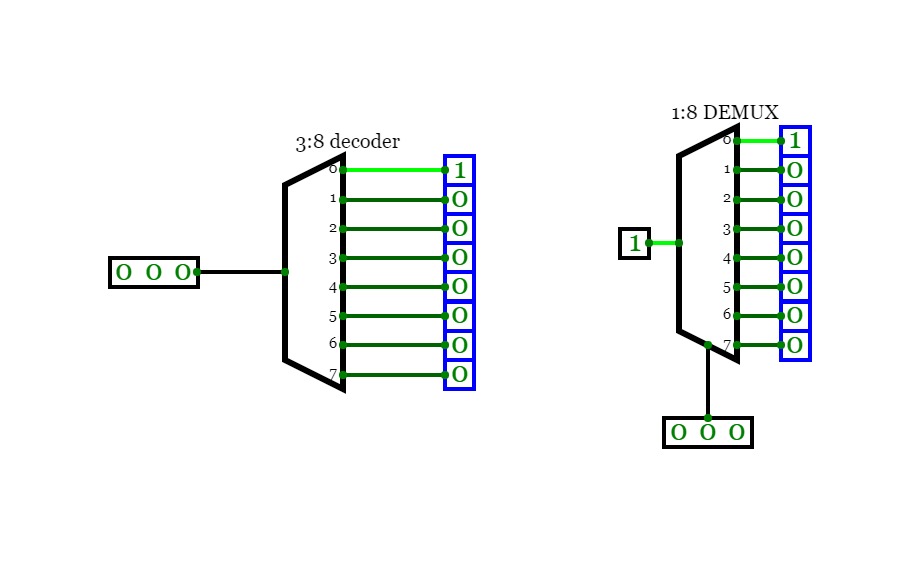

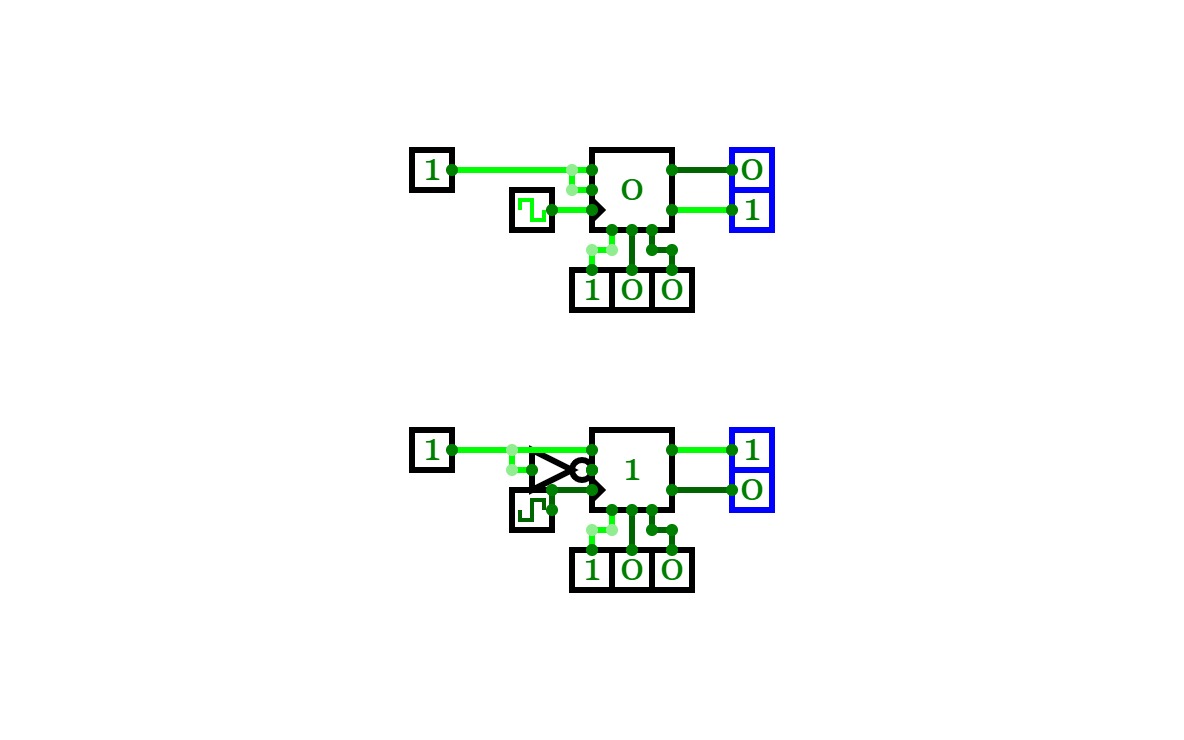

DEMUX and Decoder

DEMUX and Decoder

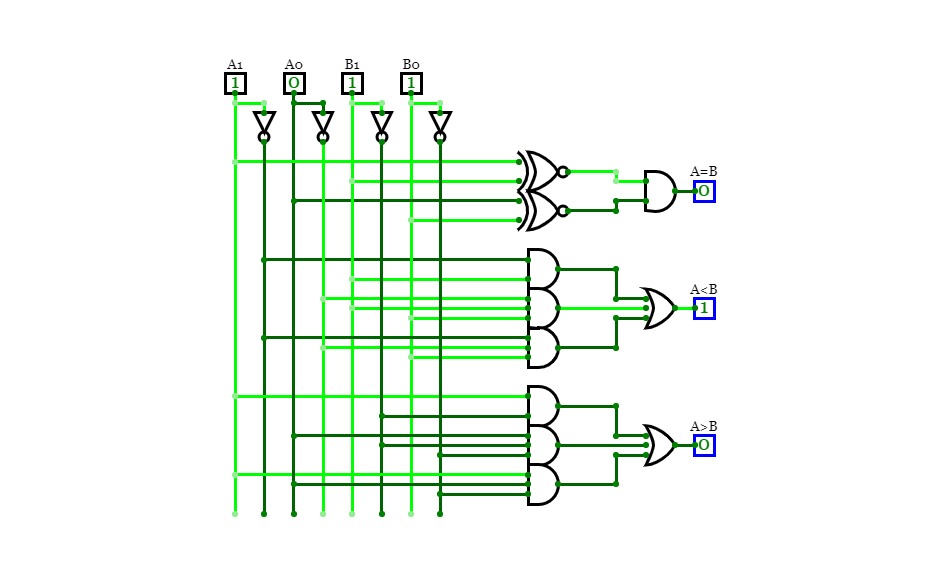

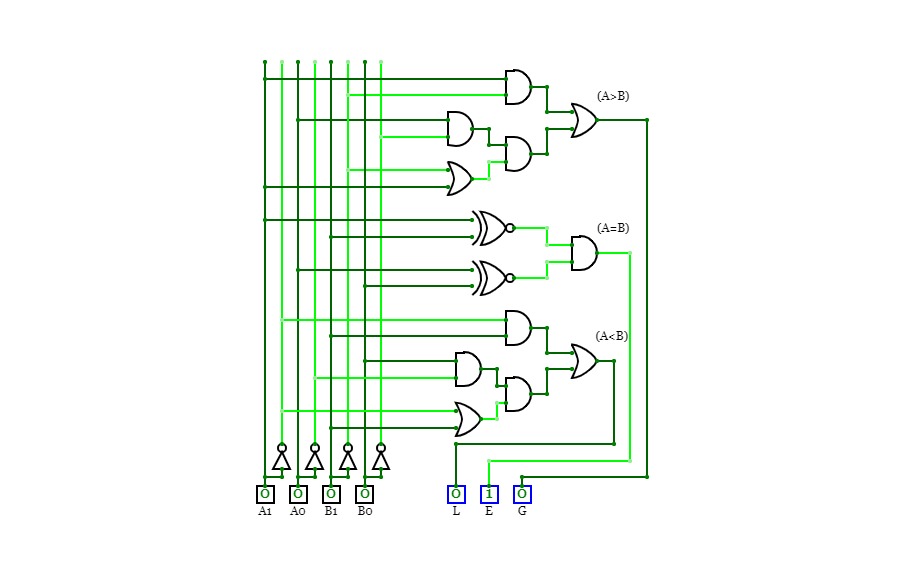

Implementation of 2 bit comparators using logic gates

Implementation of 2 bit comparators using logic gates

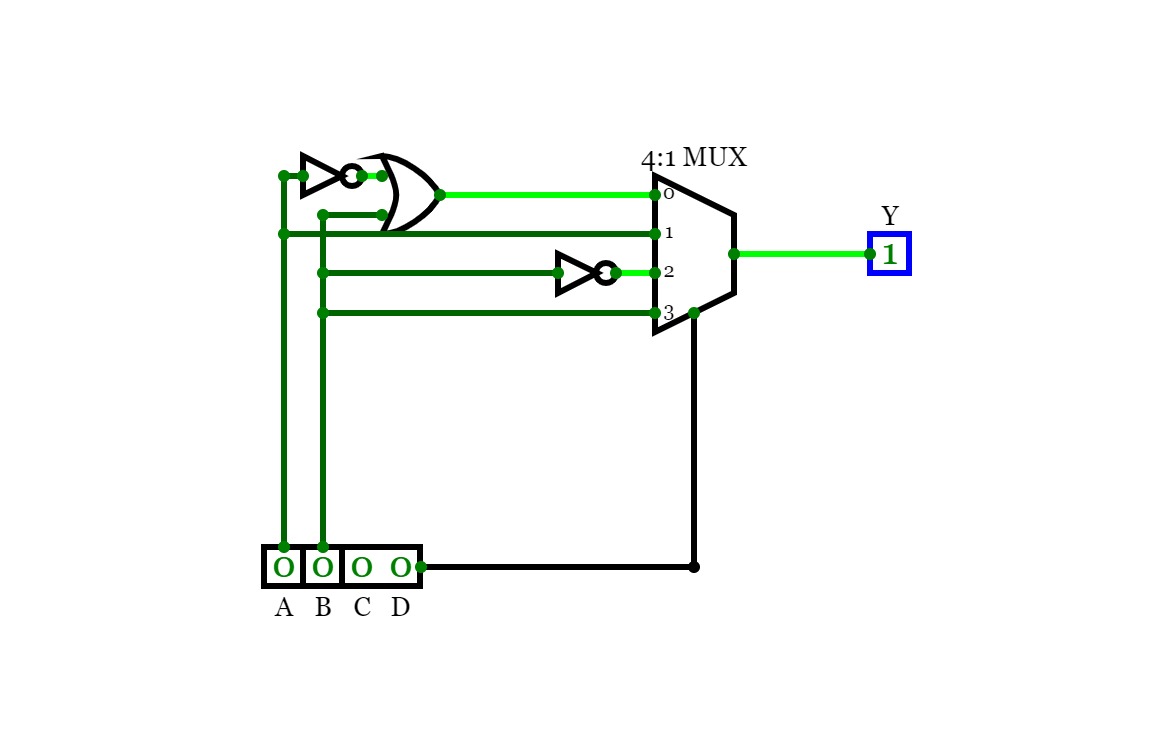

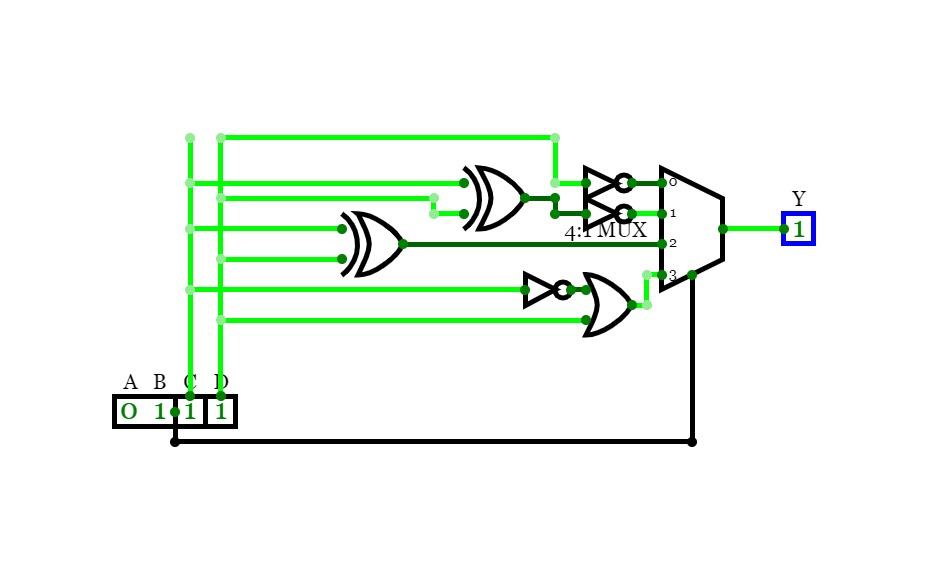

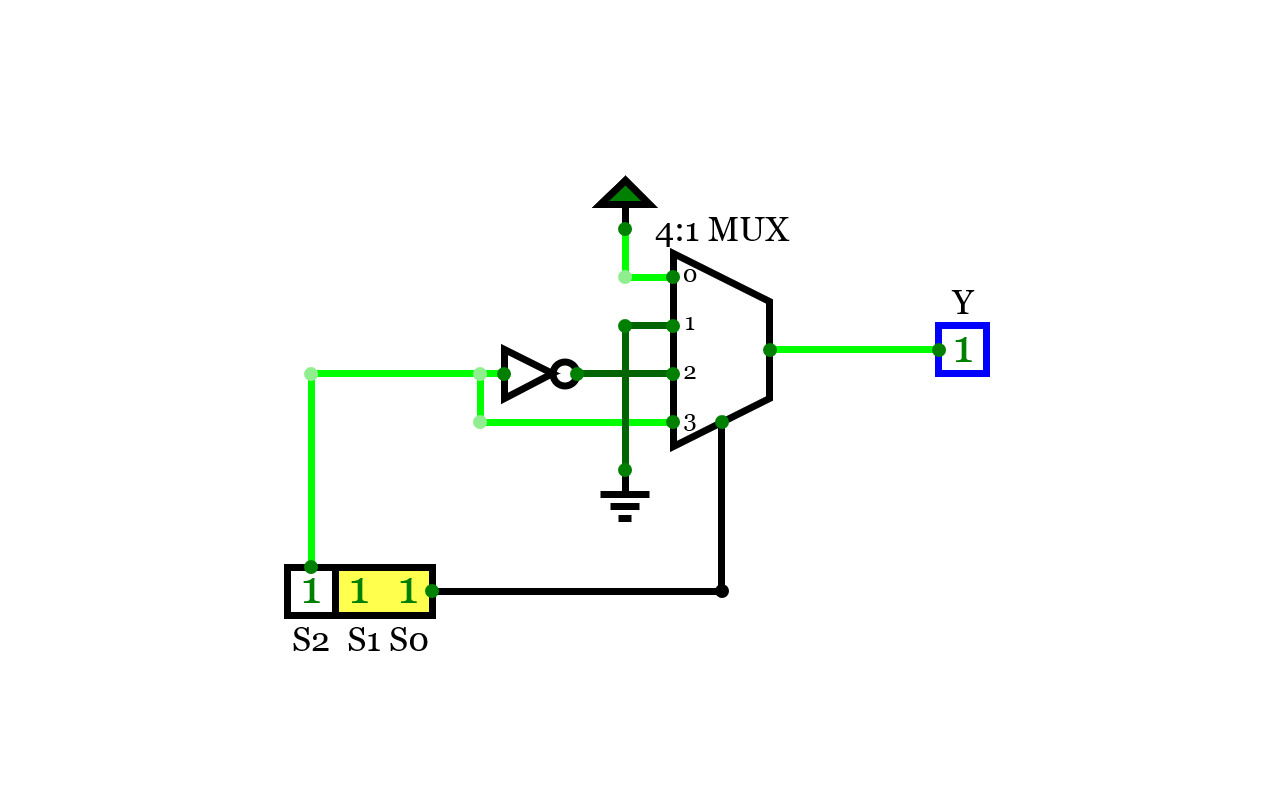

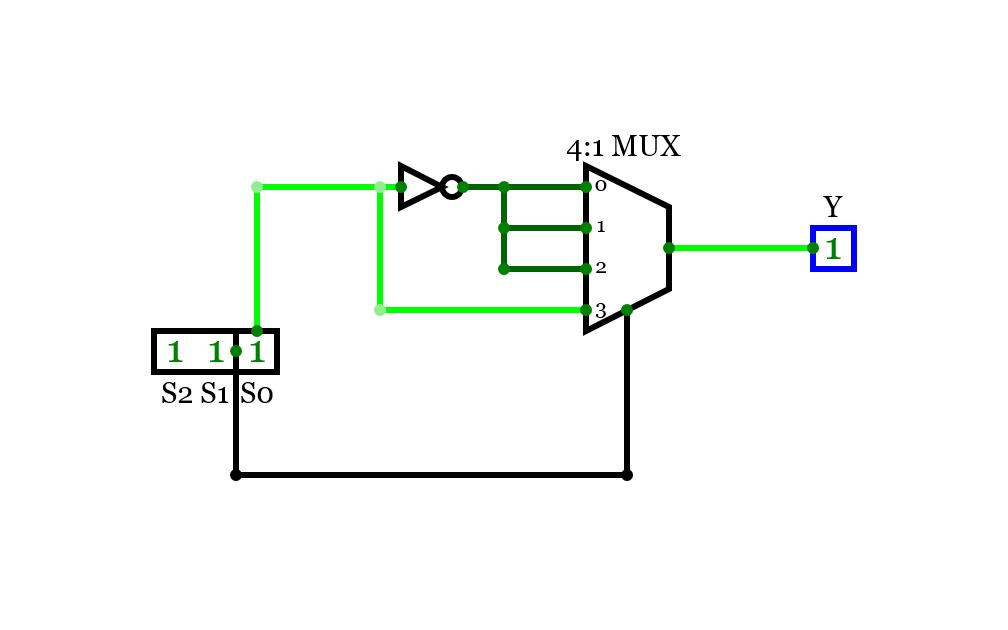

Implementation of Boolean expression using Single 4:1 MUX MSB reduction

Implementation of Boolean expression using Single 4:1 MUX MSB reduction

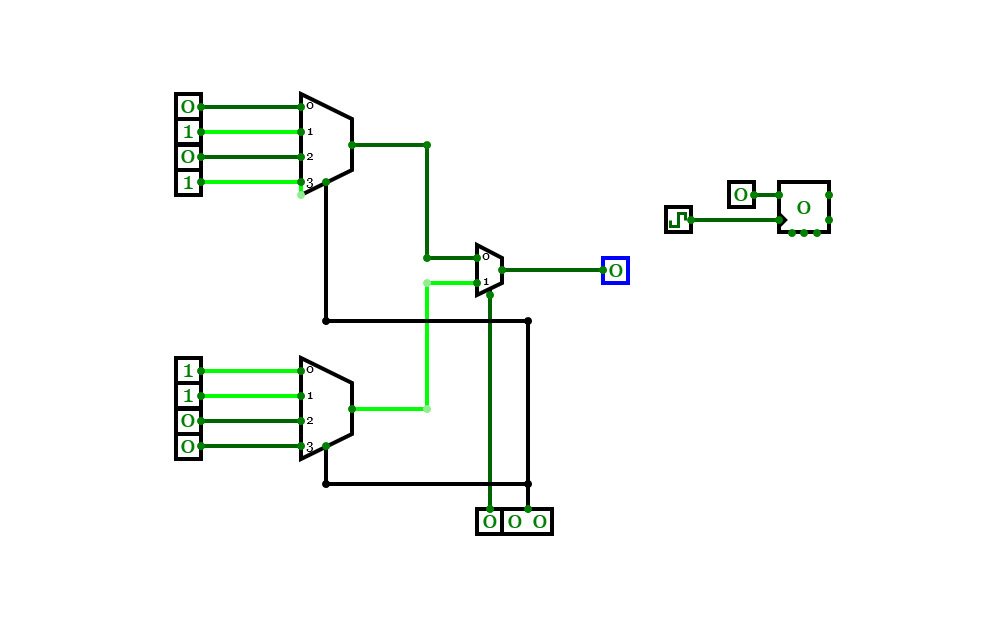

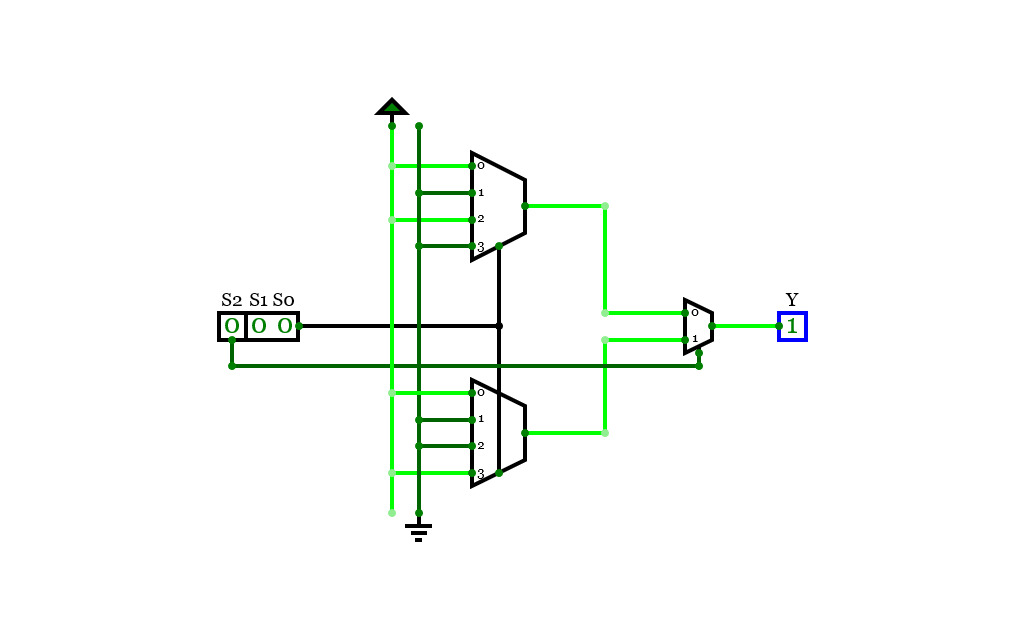

Kaivalya 21444 implementation of 8:1 MUX using two 4:1 MUX

Kaivalya 21444 implementation of 8:1 MUX using two 4:1 MUX

Parity Generator and Parity Checker

Parity Generator and Parity Checker

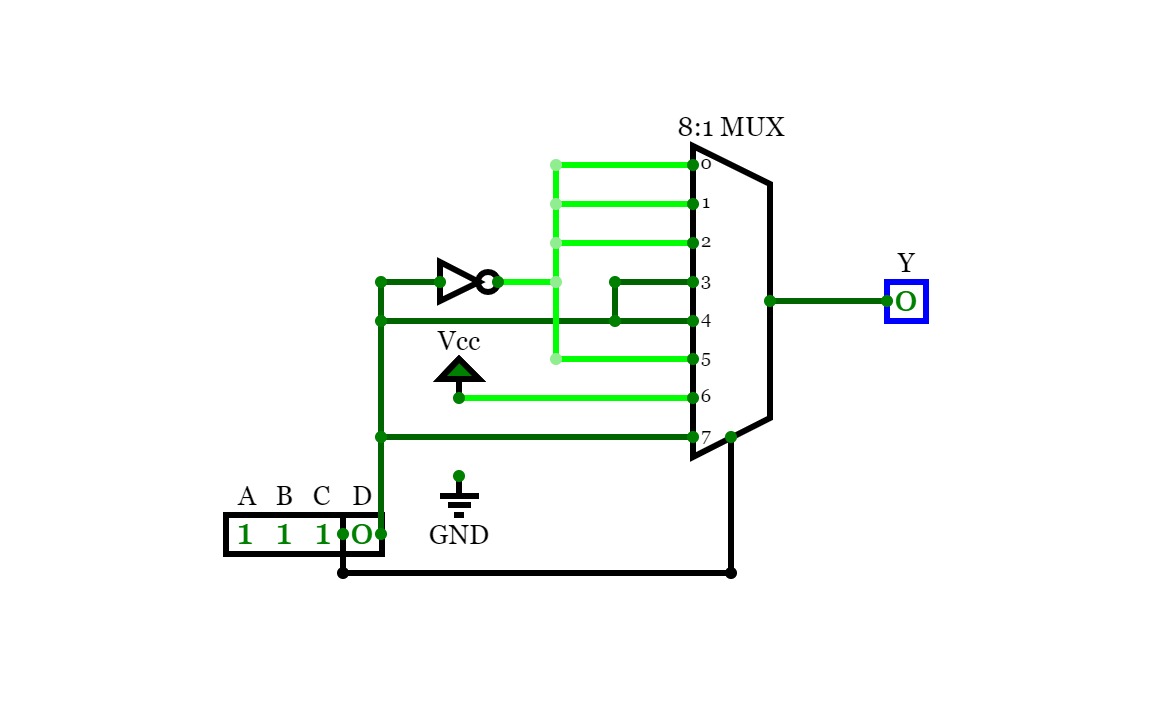

Implementation of Boolean expression using 8:1 MUX

Implementation of Boolean expression using 8:1 MUX

Asynchronous UP and Down counter

Asynchronous UP and Down counter

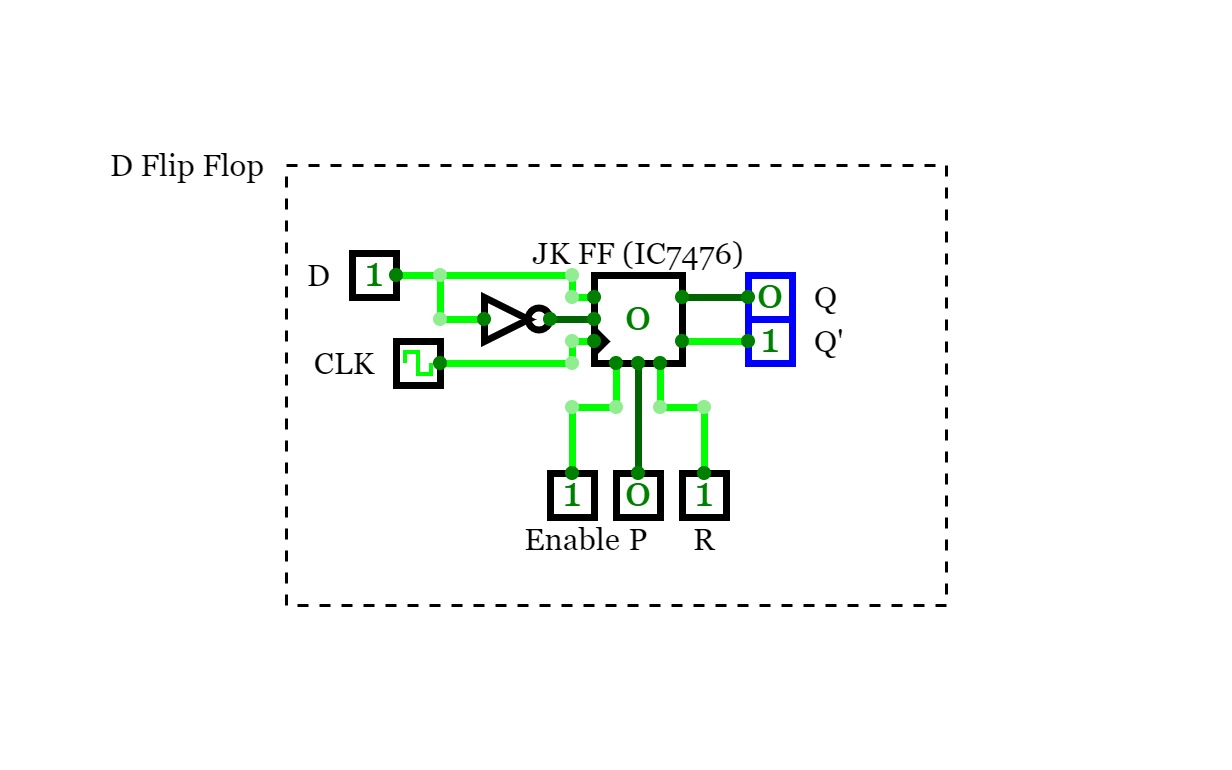

conversion of ff

conversion of ff

Implementation of Boolean expression using single 8:1 MUX

Implementation of Boolean expression using single 8:1 MUX

Implementation of 2-bit comparator

Implementation of 2-bit comparator

Parity Generator and Parity Checker

Parity Generator and Parity Checker

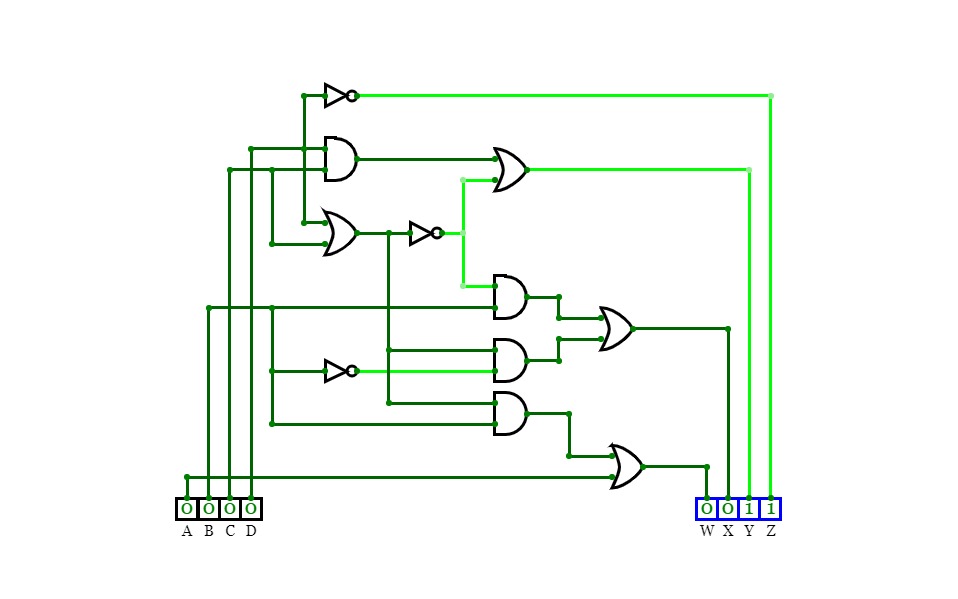

BCD to XS3 code converter

BCD to XS3 code converter

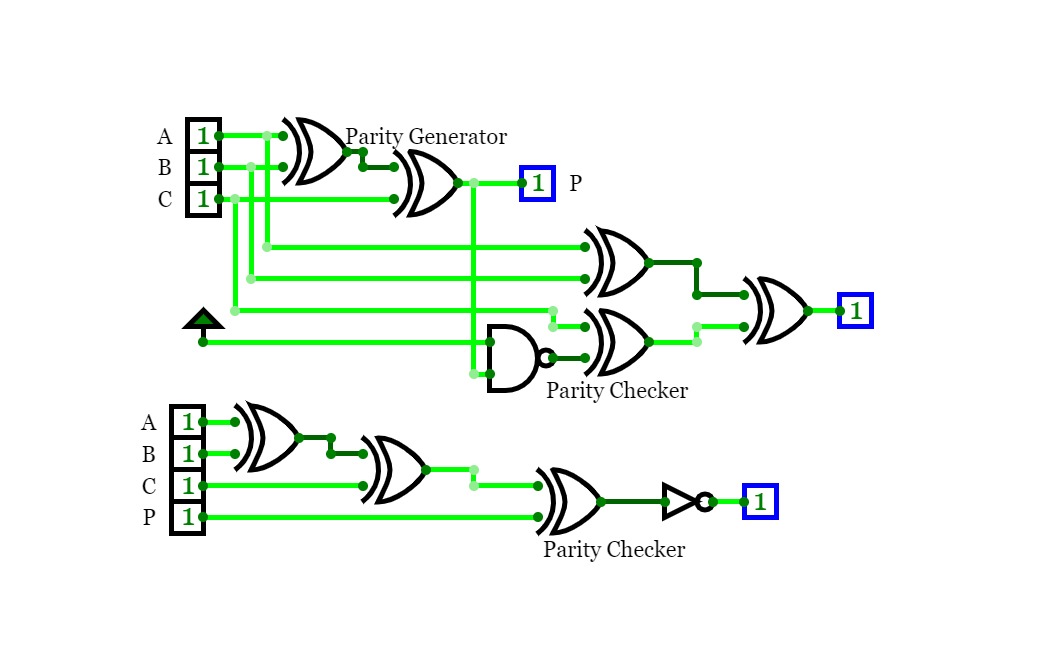

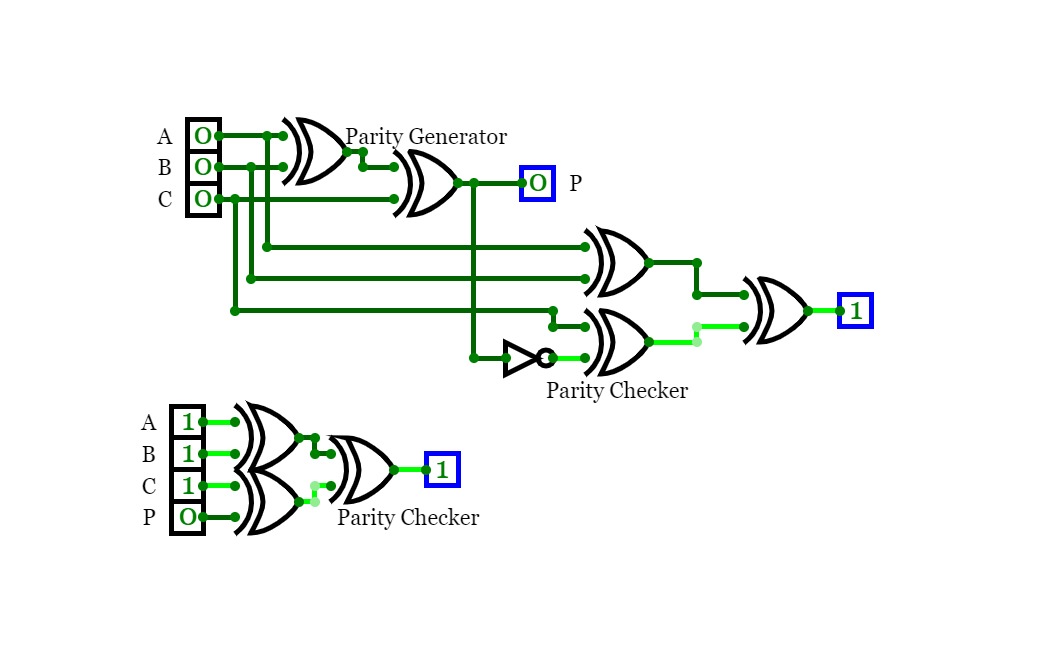

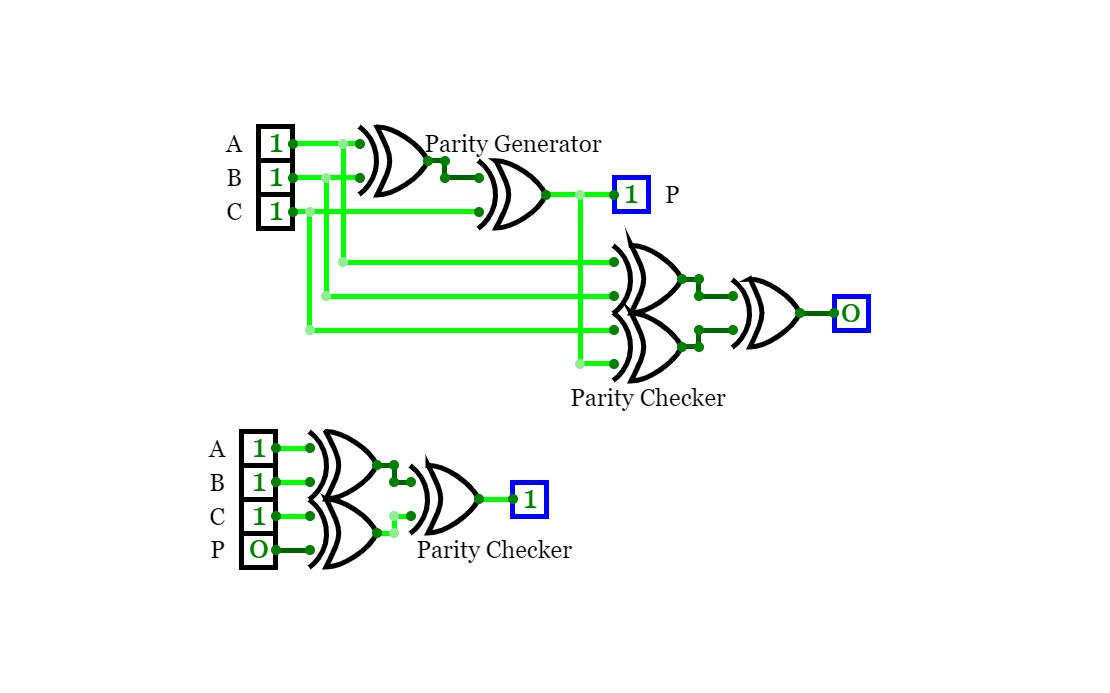

Even Parity Generator and Parity Checker

Even Parity Generator and Parity Checker

Implementation of Boolean expression using Single 4:1 MUX LSB reduction

Implementation of Boolean expression using Single 4:1 MUX LSB reduction

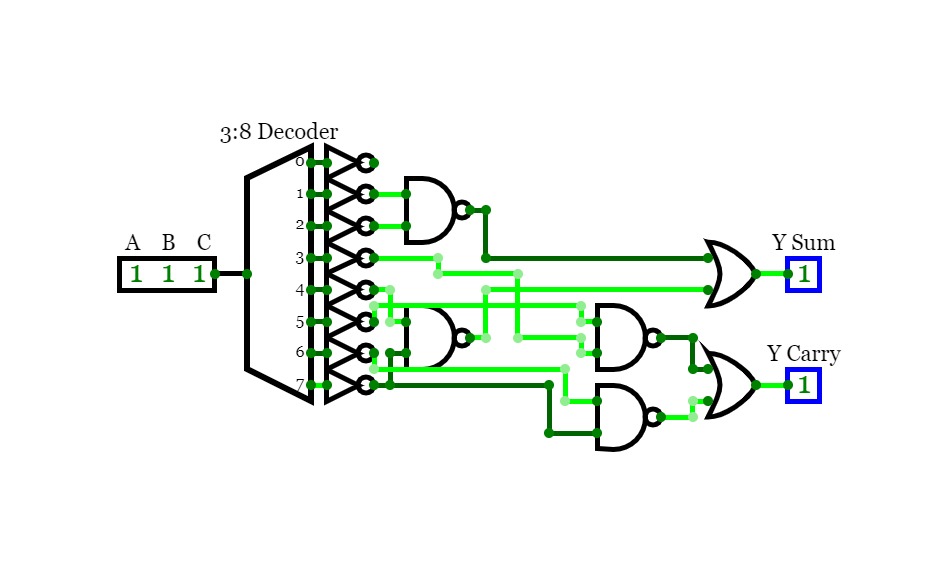

Implementation of 3 bit Adder using Decoder in boolean expressions

Implementation of 3 bit Adder using Decoder in boolean expressions

Boolean expression realization with 4:1 MUX using MSB reduction method

Boolean expression realization with 4:1 MUX using MSB reduction method

Untitled

Untitled

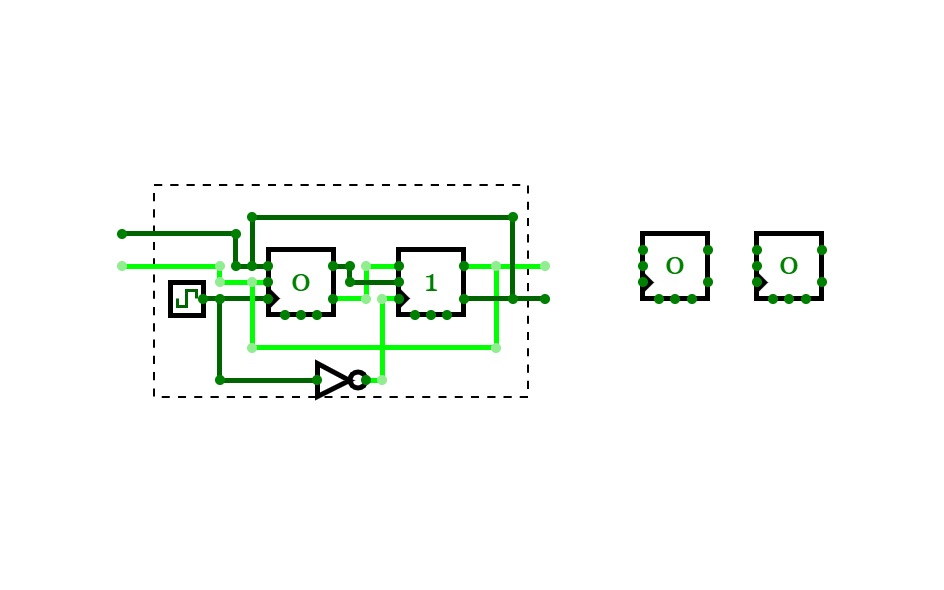

Design D flip flop using IC7476

Design D flip flop using IC7476

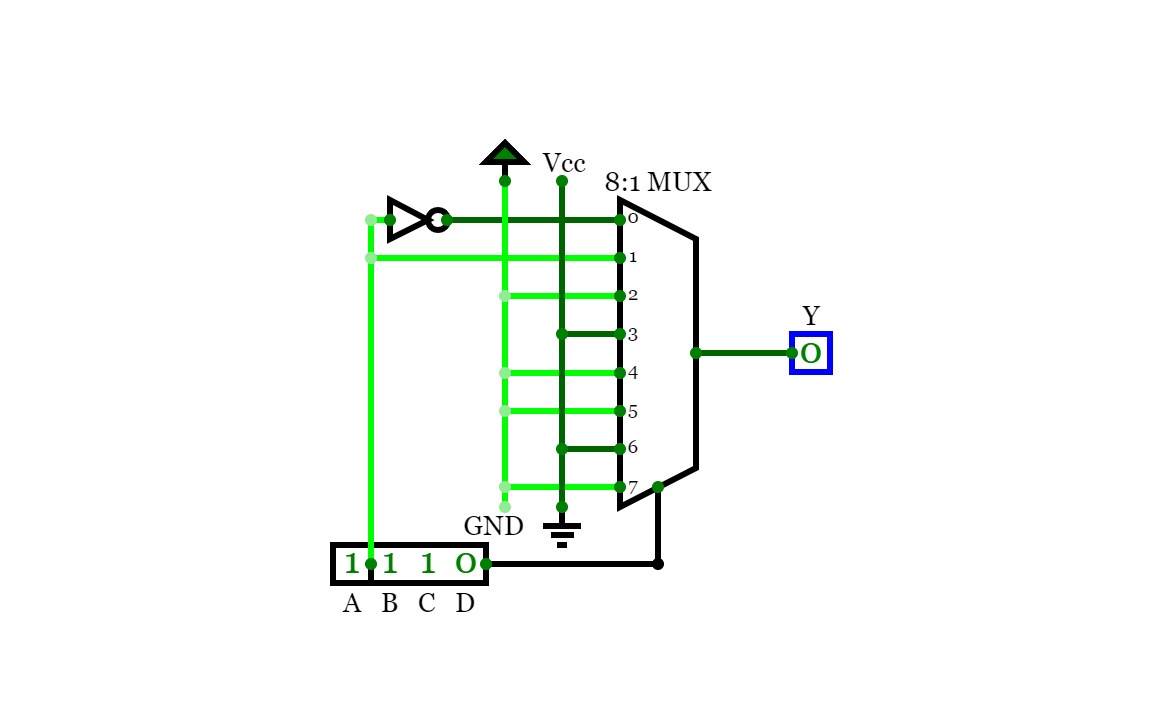

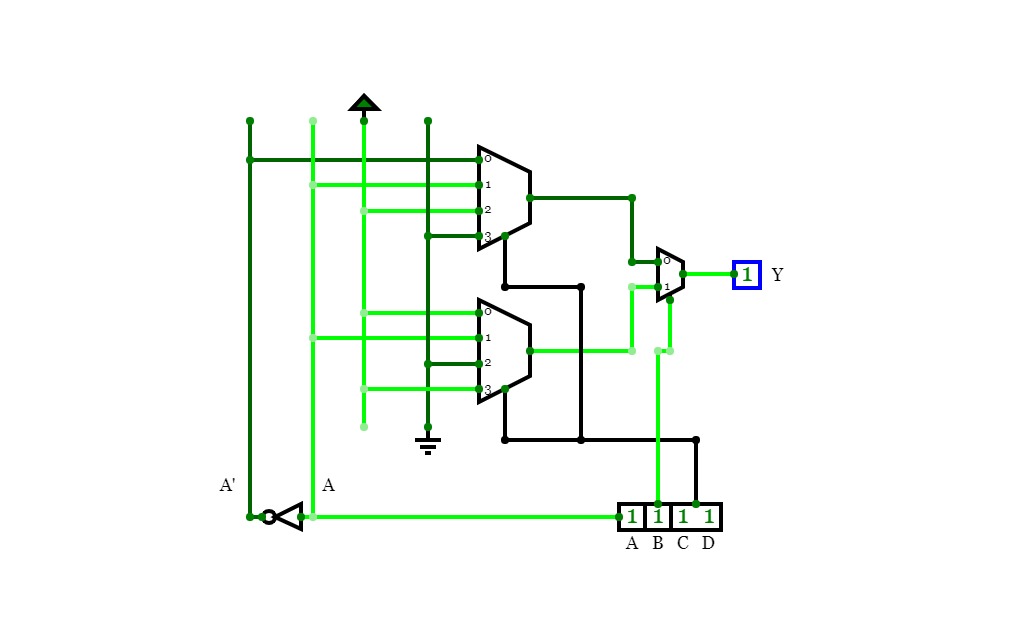

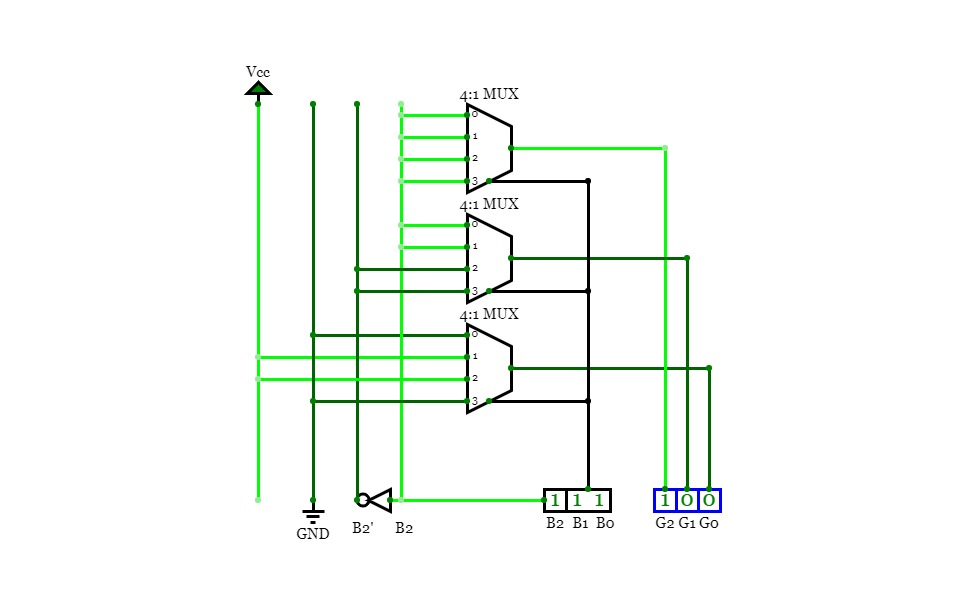

Implement f(A,B,C,D)=(0,2,4,7,9,10,12,13,15) using IC 74153

Implement f(A,B,C,D)=(0,2,4,7,9,10,12,13,15) using IC 74153

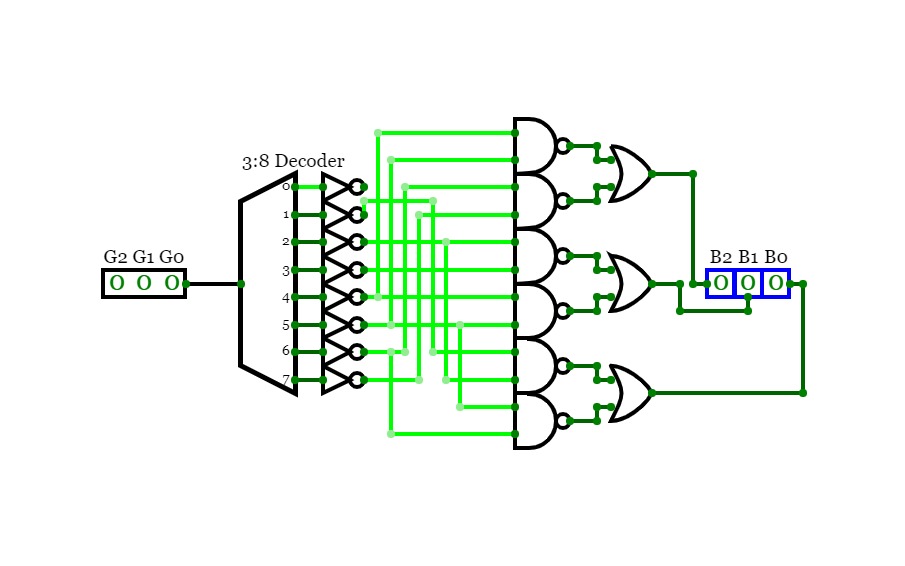

Implement 3 bit Gray to Binary code converter using 3:8 decoder.

Implement 3 bit Gray to Binary code converter using 3:8 decoder.

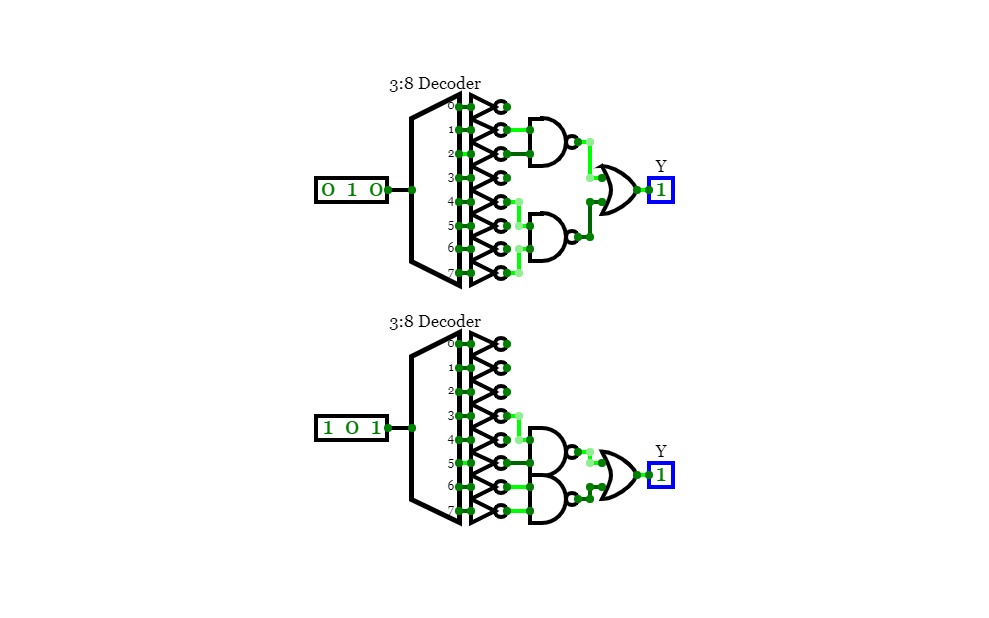

Implementation of Decoder in boolean expressions

Implementation of Decoder in boolean expressions

3-bit binary to gray code converter using 4:1 MUX

3-bit binary to gray code converter using 4:1 MUX

Boolean expression realization using single 4:1 MUX using LSB reduction

Boolean expression realization using single 4:1 MUX using LSB reduction

Boolean expression implementation with 4:1 MUX usisng LSB reduction method

Boolean expression implementation with 4:1 MUX usisng LSB reduction method

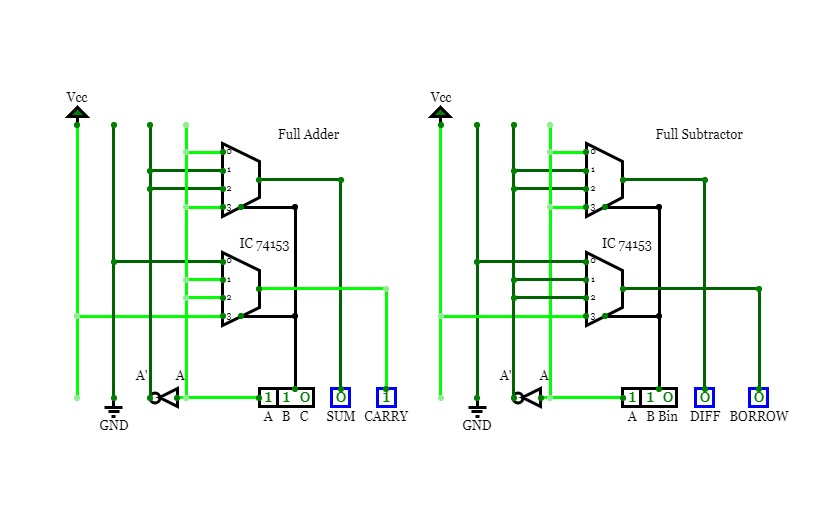

Implement full adder and full subtractor using IC 74153 (Dual 4:1 MUX)

Implement full adder and full subtractor using IC 74153 (Dual 4:1 MUX)

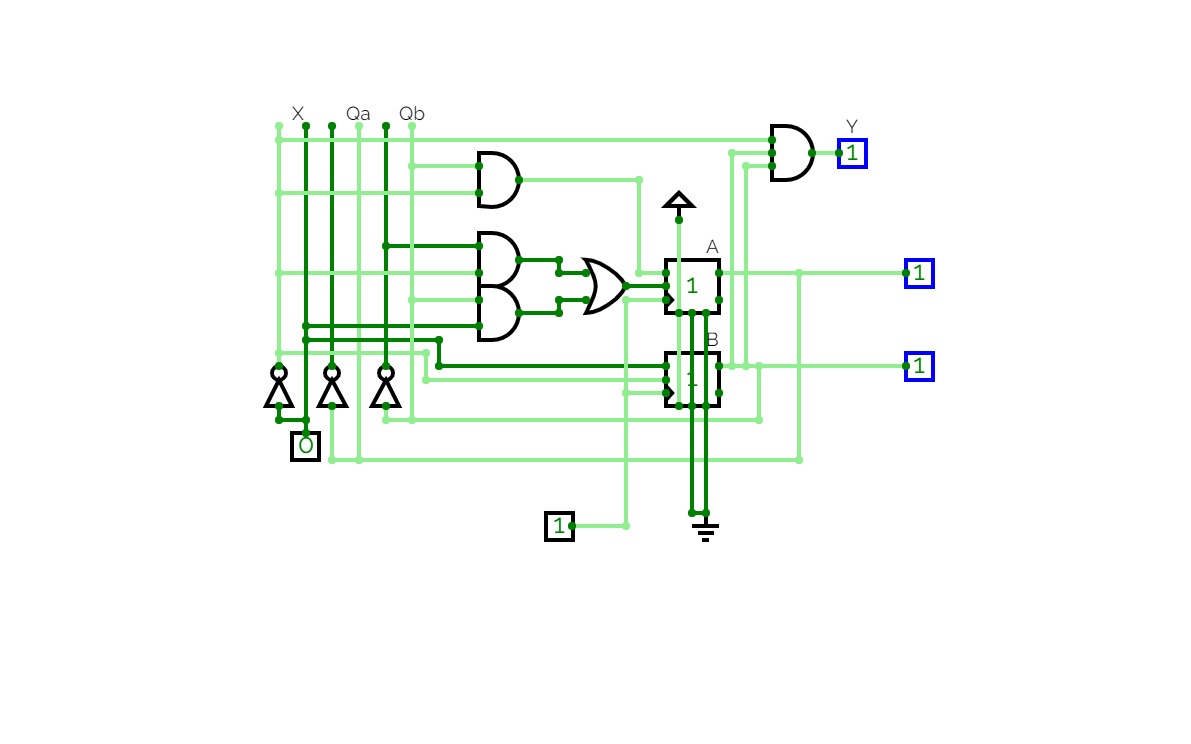

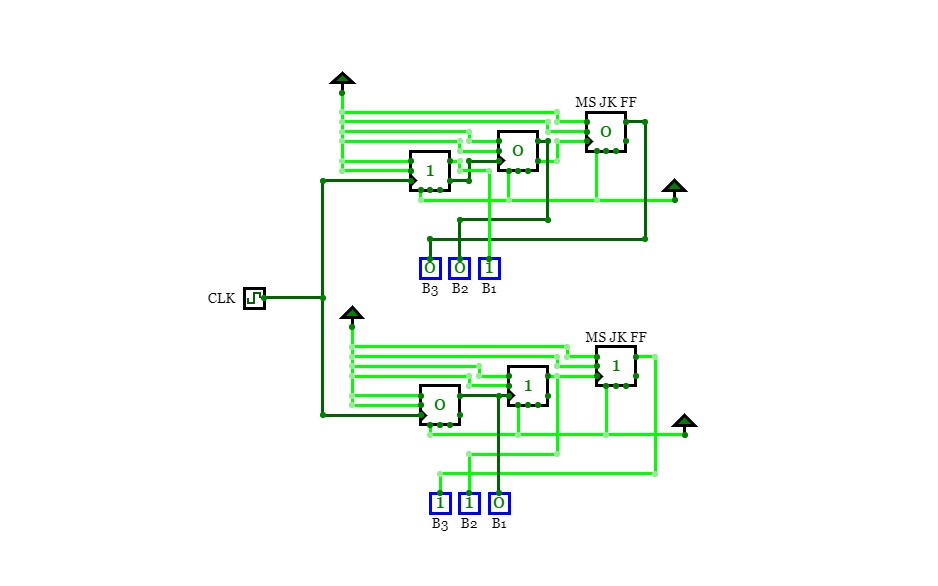

Sequence detector

Sequence detector