A.Srinivasan

Member since: 4 years

Educational Institution: Not Entered

Country: Not Entered

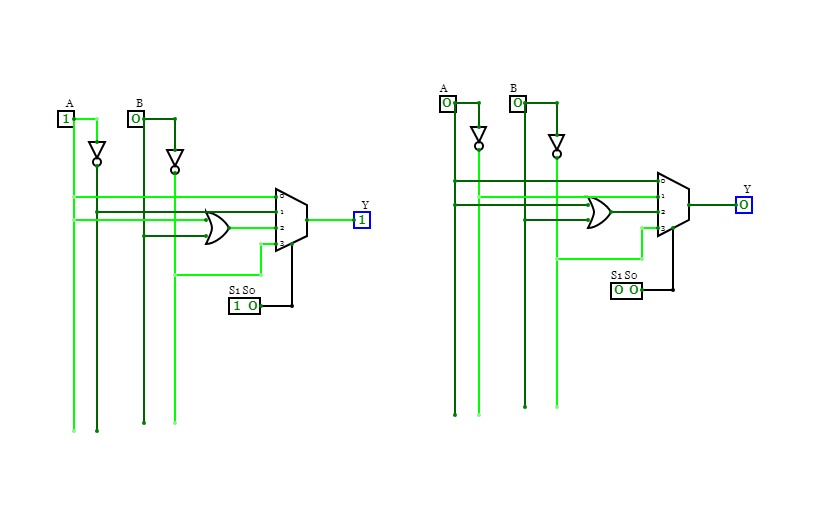

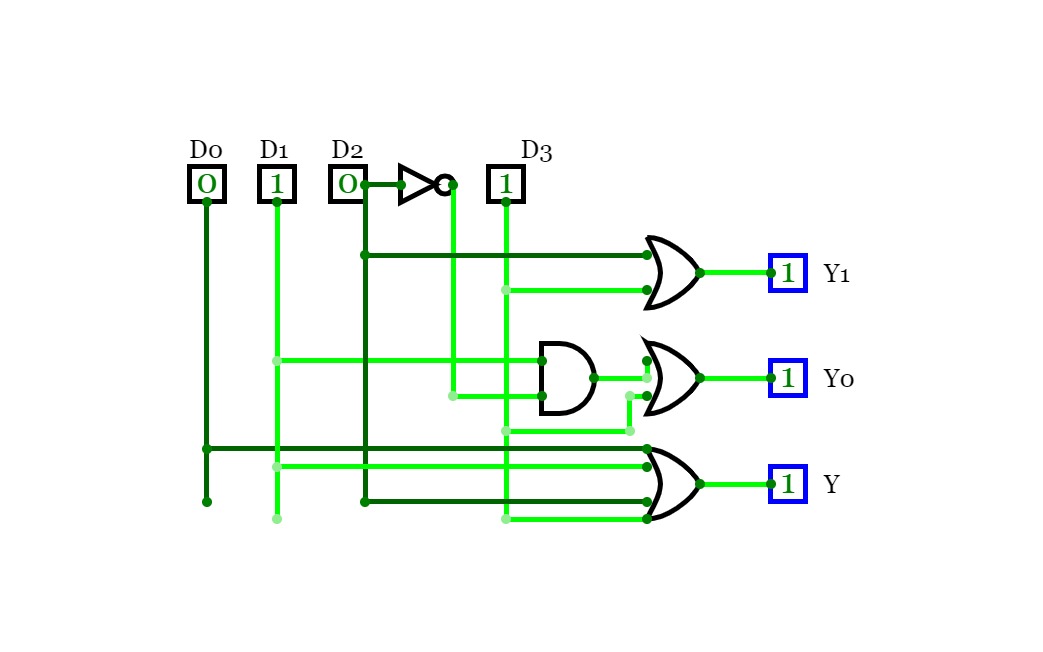

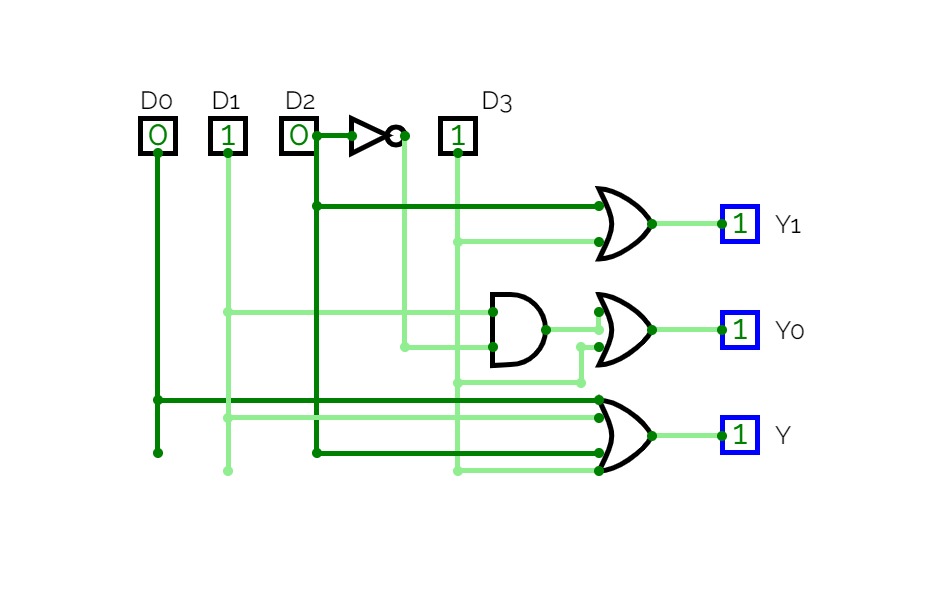

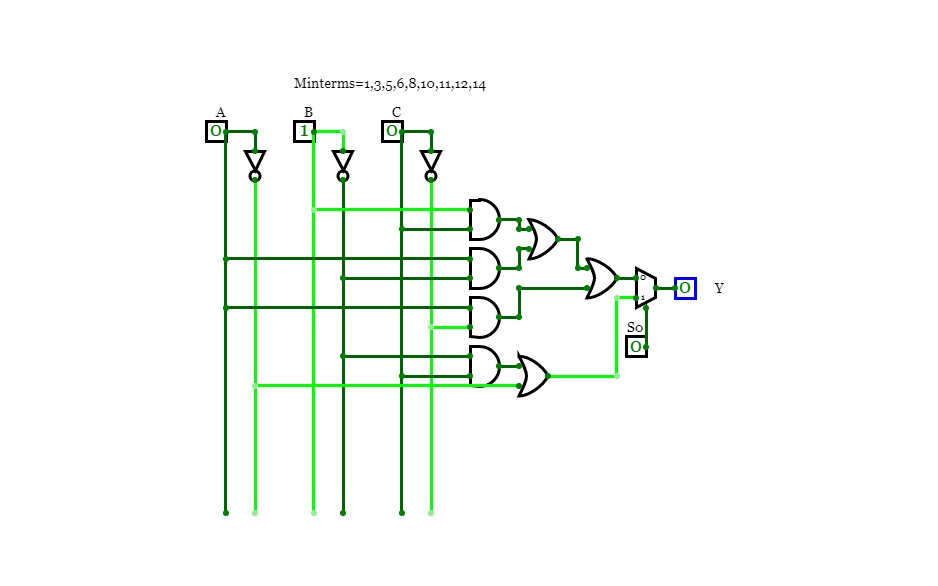

IMPLEMENTATION USING MINTERMS WITH 4:1 MUX

IMPLEMENTATION USING MINTERMS WITH 4:1 MUX

2 to 1 Encoder

2 to 1 Encoder

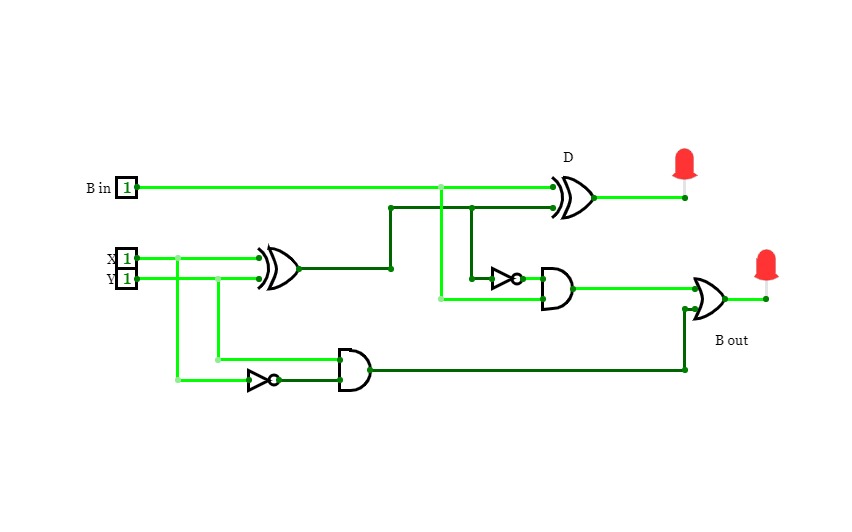

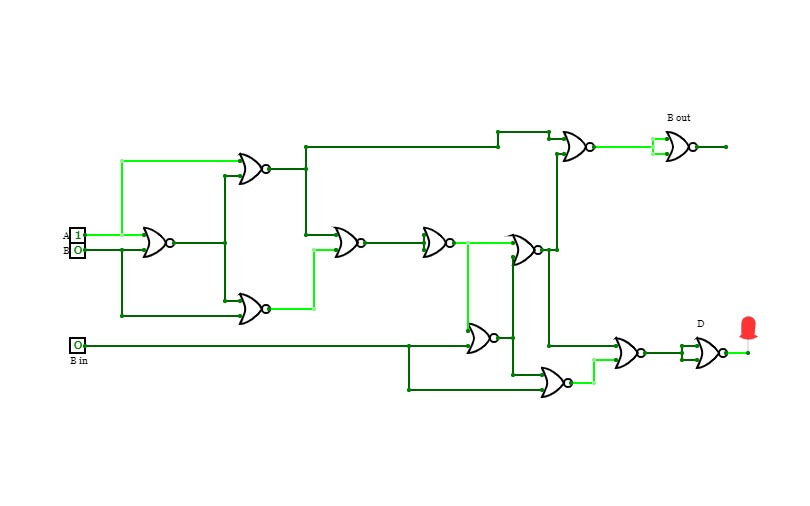

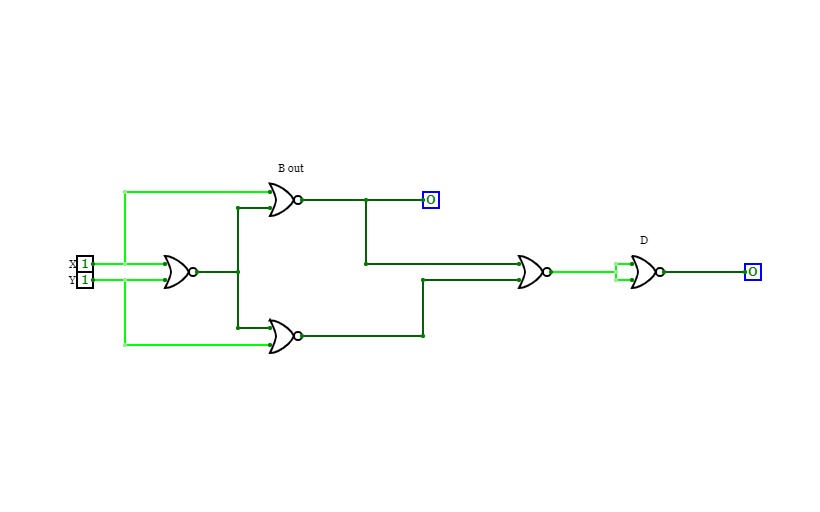

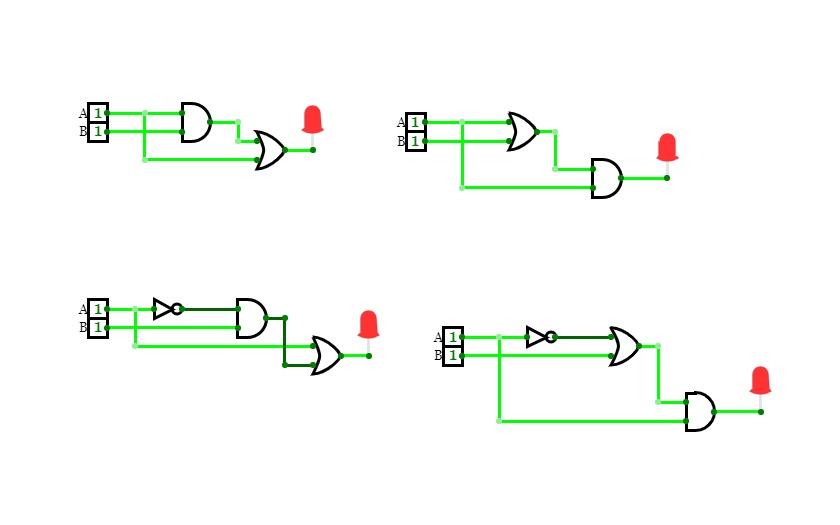

Full subtractor using NAND gate

Full subtractor using NAND gate

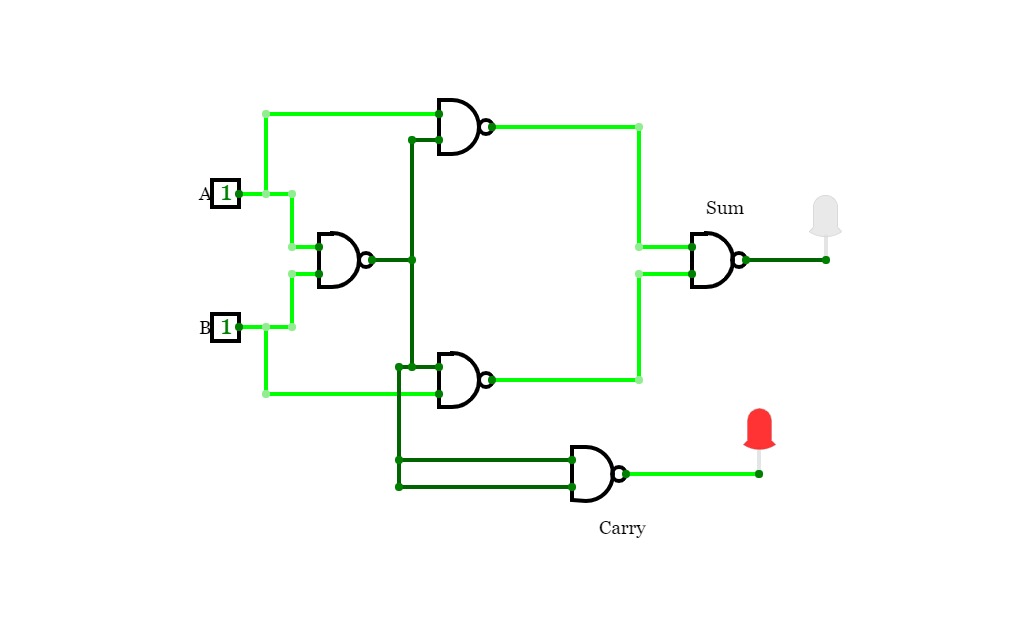

Half adder using NAND gate

Half adder using NAND gate

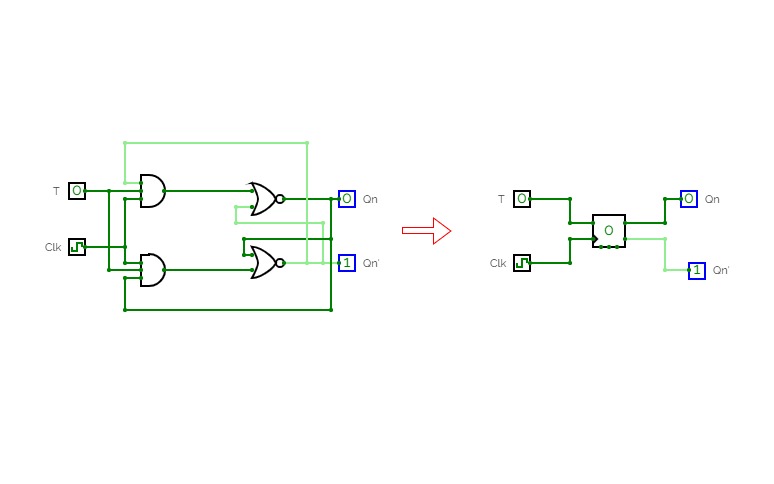

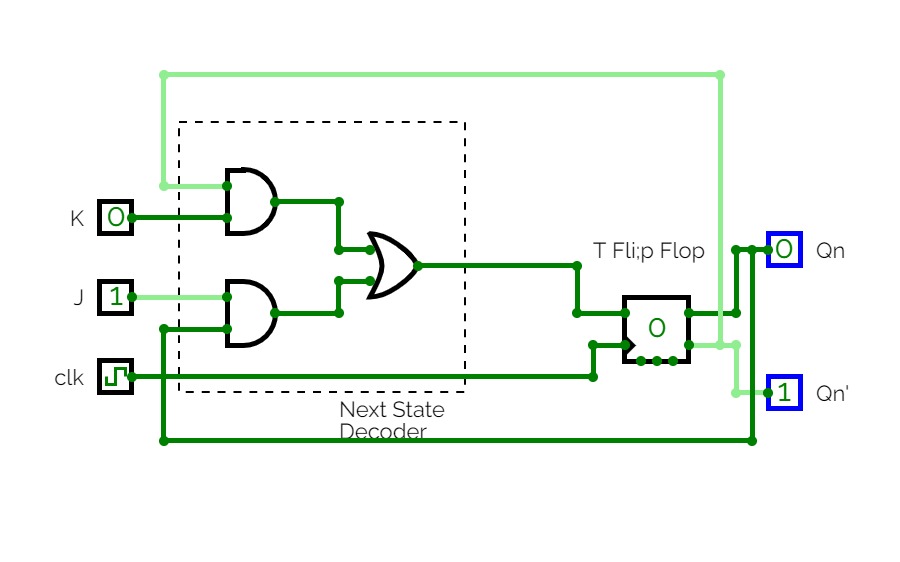

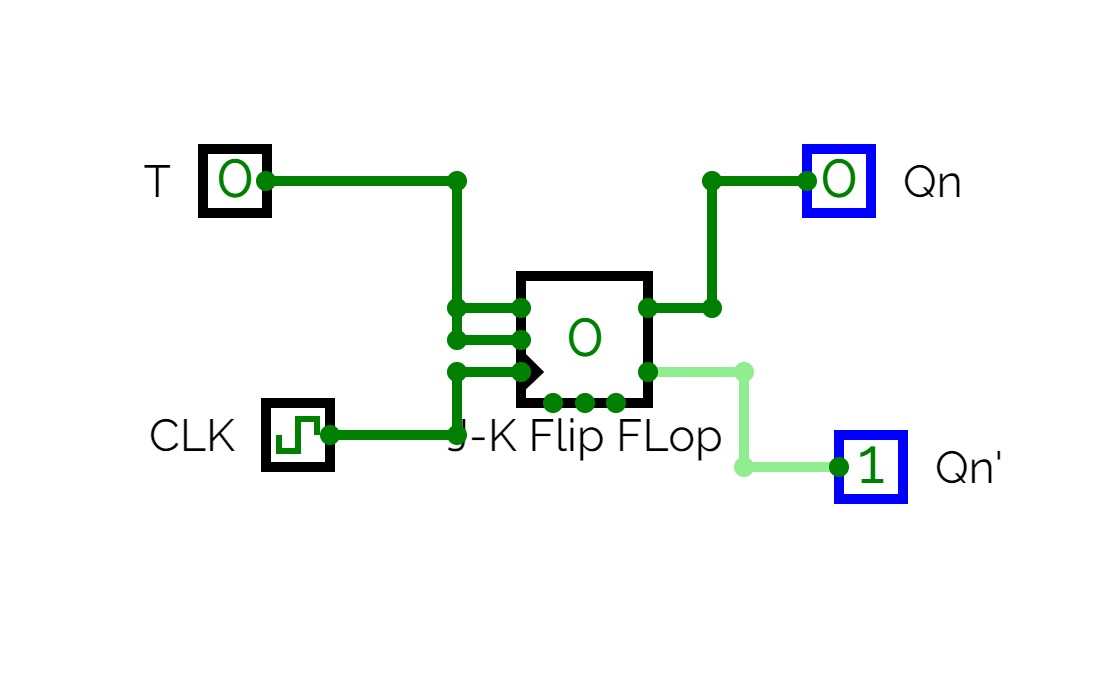

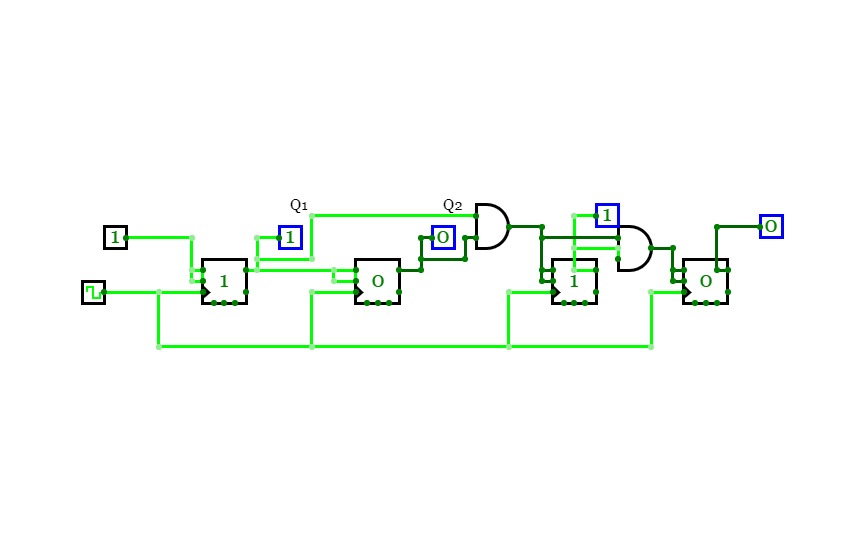

T Flip Flop

T Flip Flop

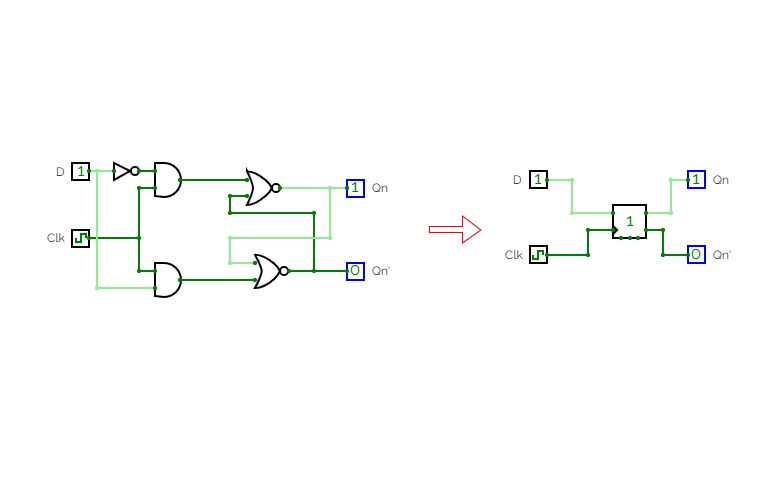

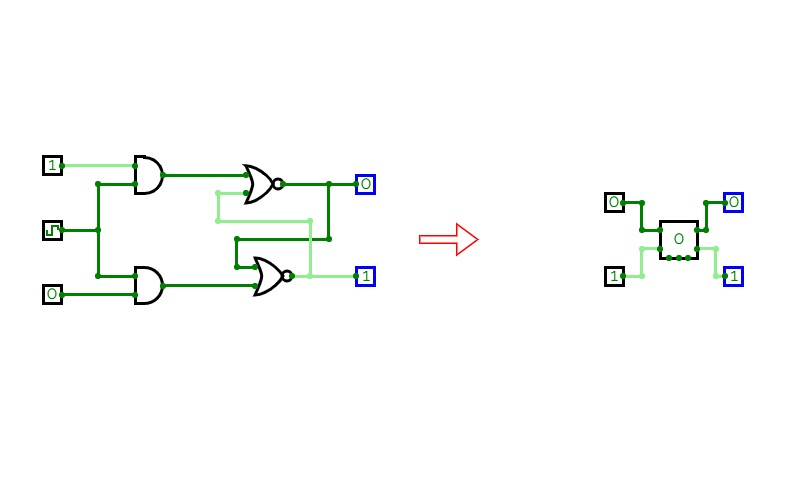

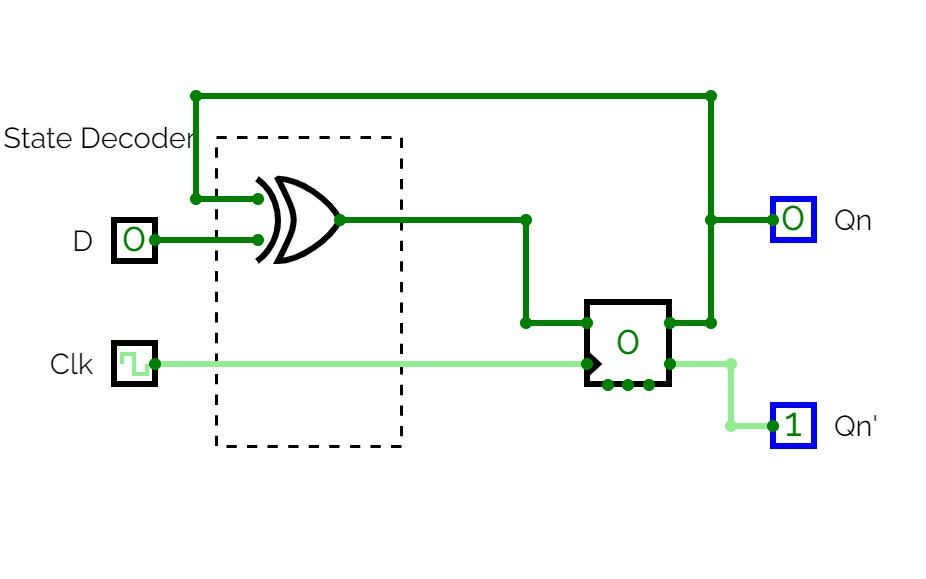

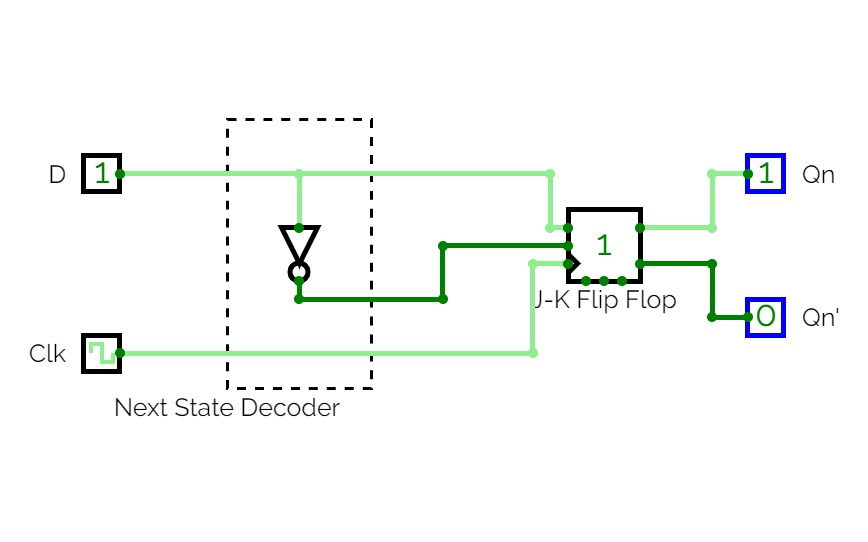

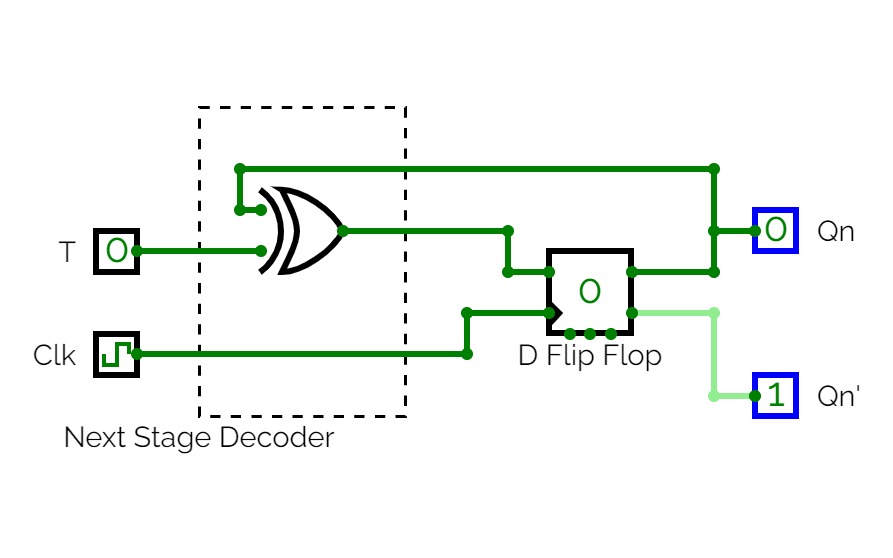

D Flip-Flop

D Flip-Flop

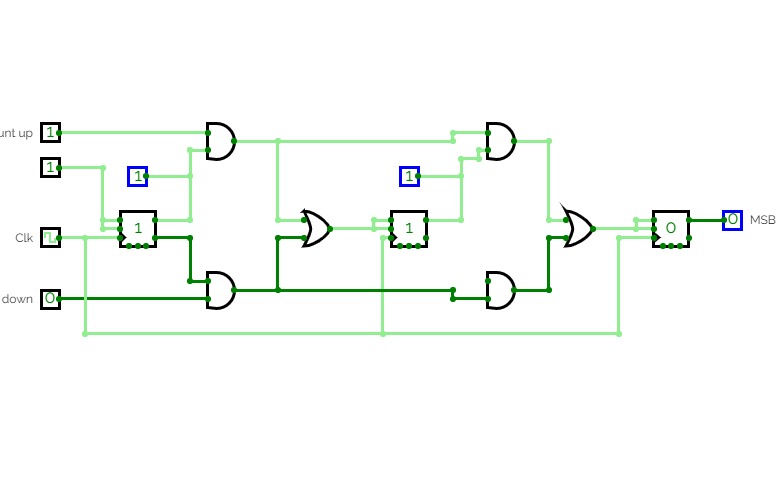

3 Synchronous up-down Counter

3 Synchronous up-down Counter

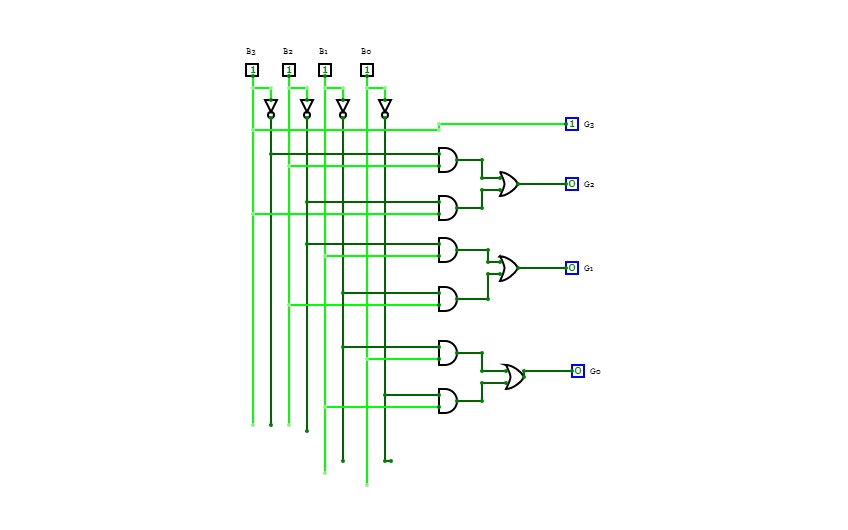

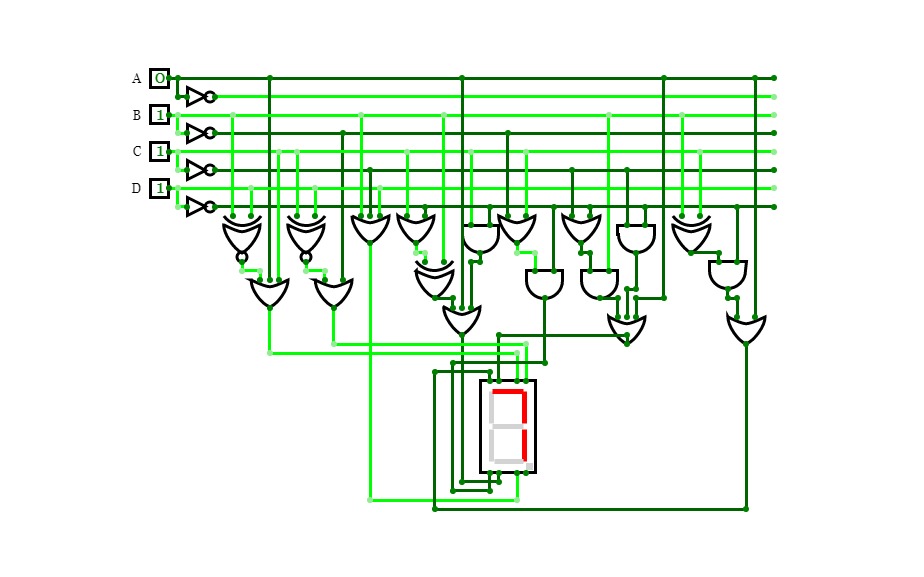

4 Bit GRAY to BINARY

4 Bit GRAY to BINARY

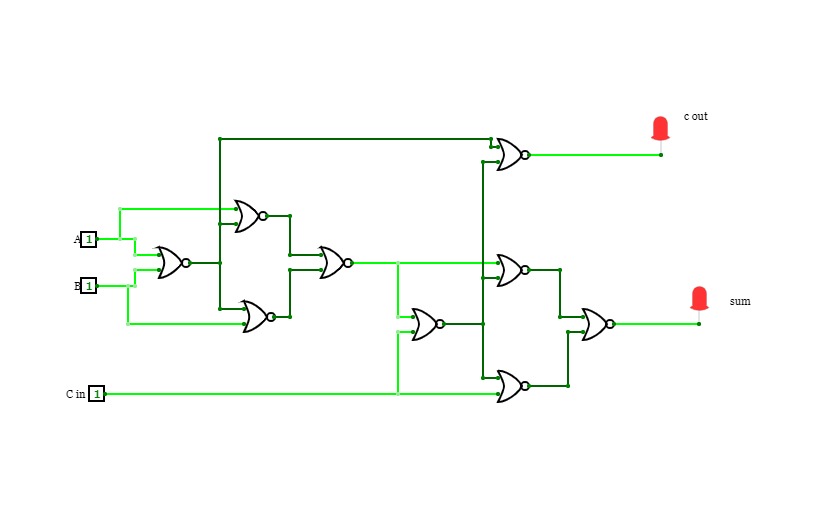

Full Adder using NOR gates

Full Adder using NOR gates

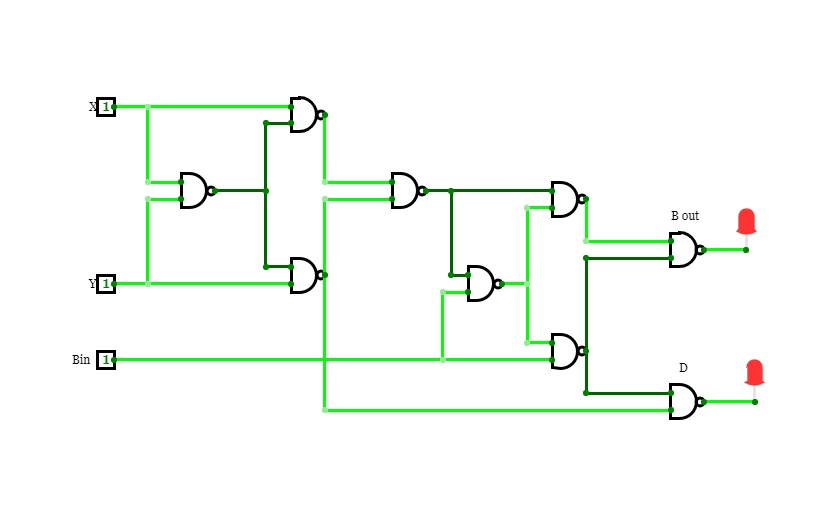

Full subtractor

Full subtractor

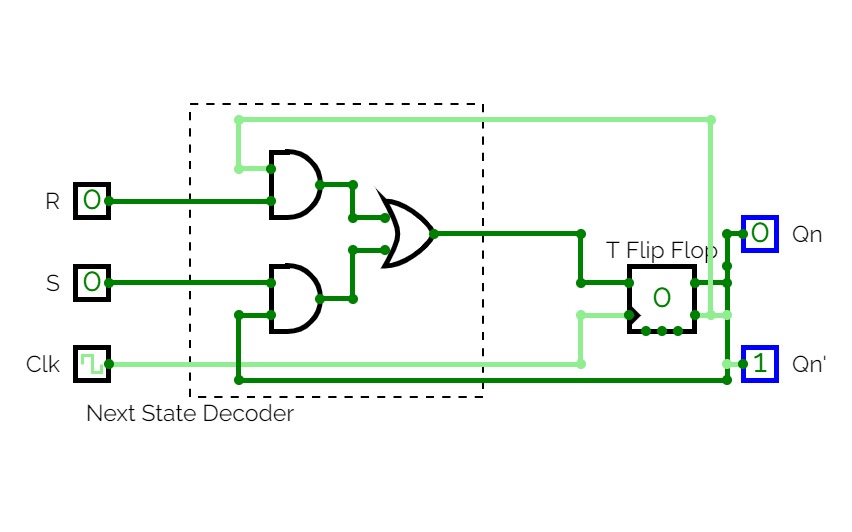

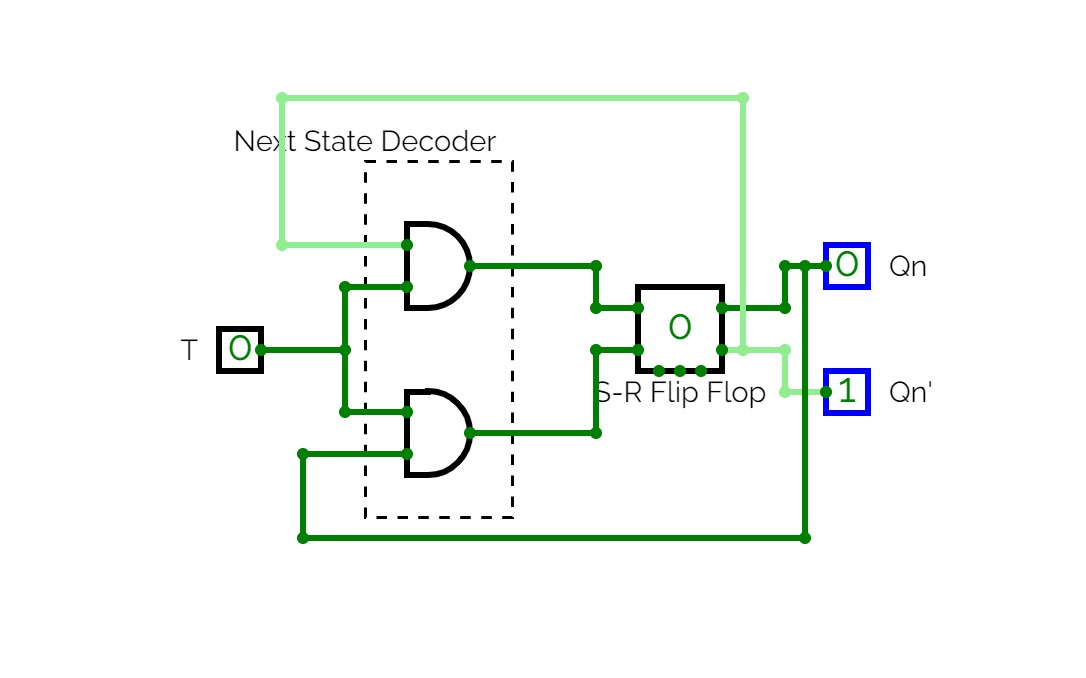

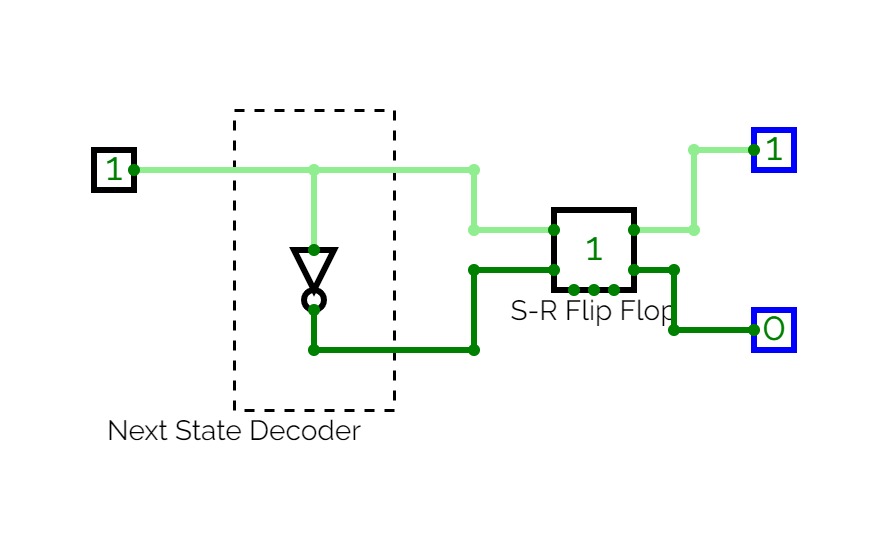

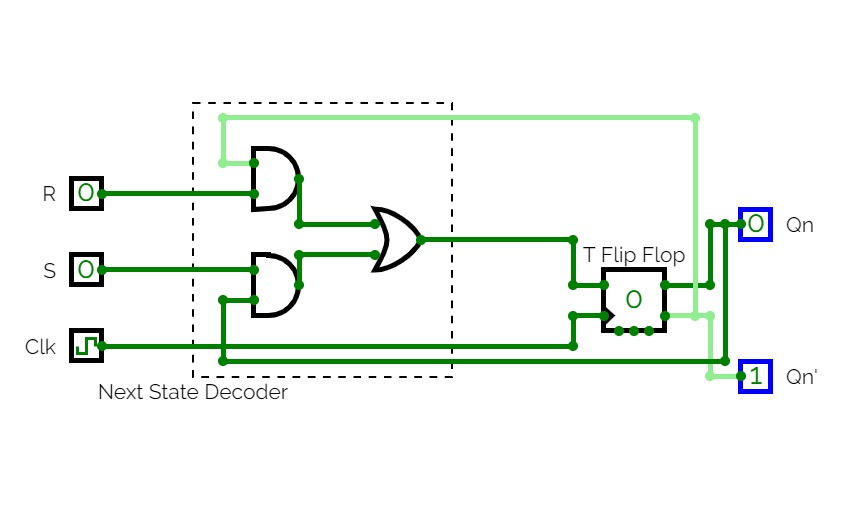

T Flip Flop to S-R Flip Flop

T Flip Flop to S-R Flip Flop

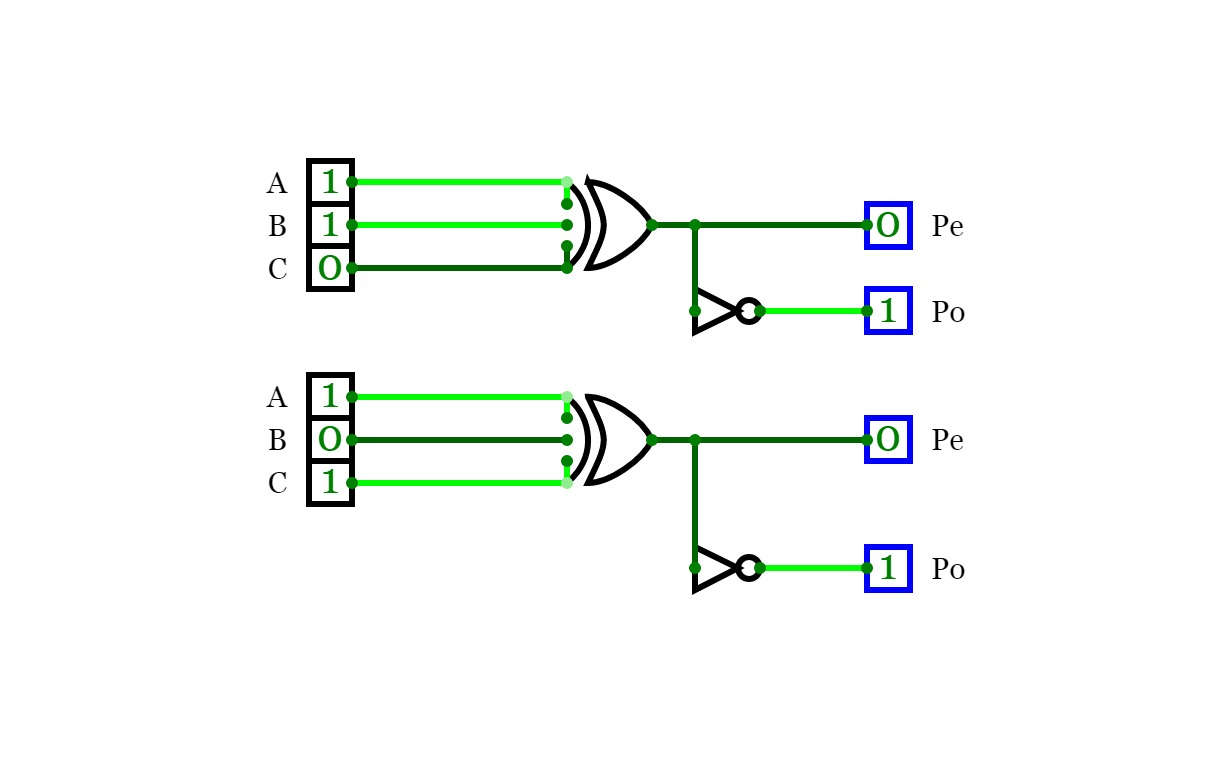

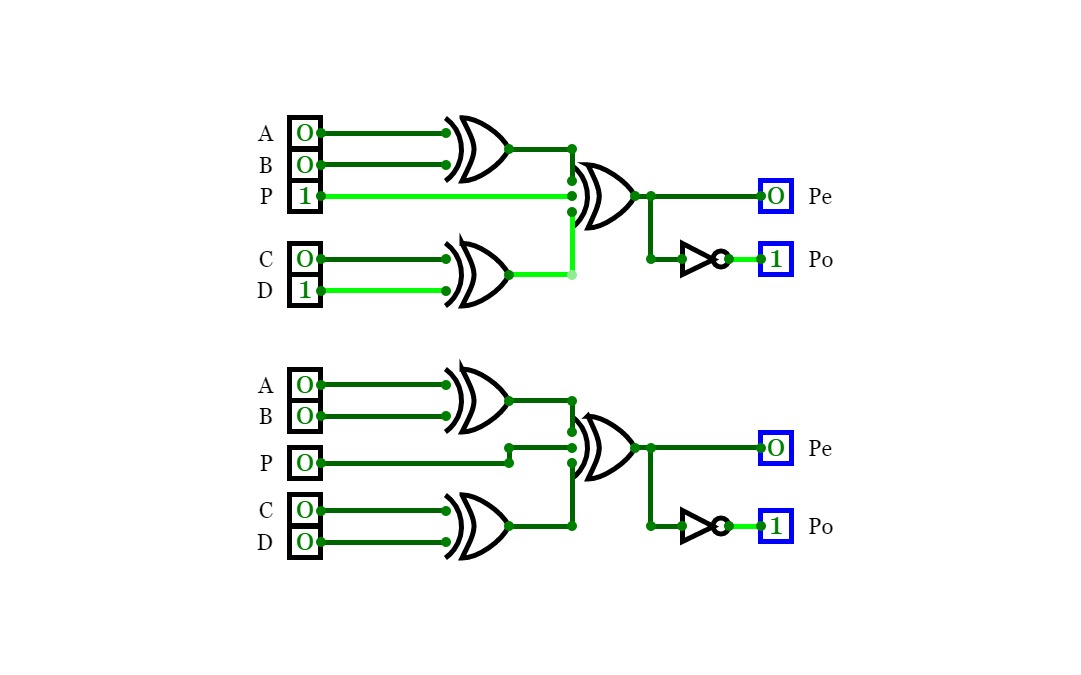

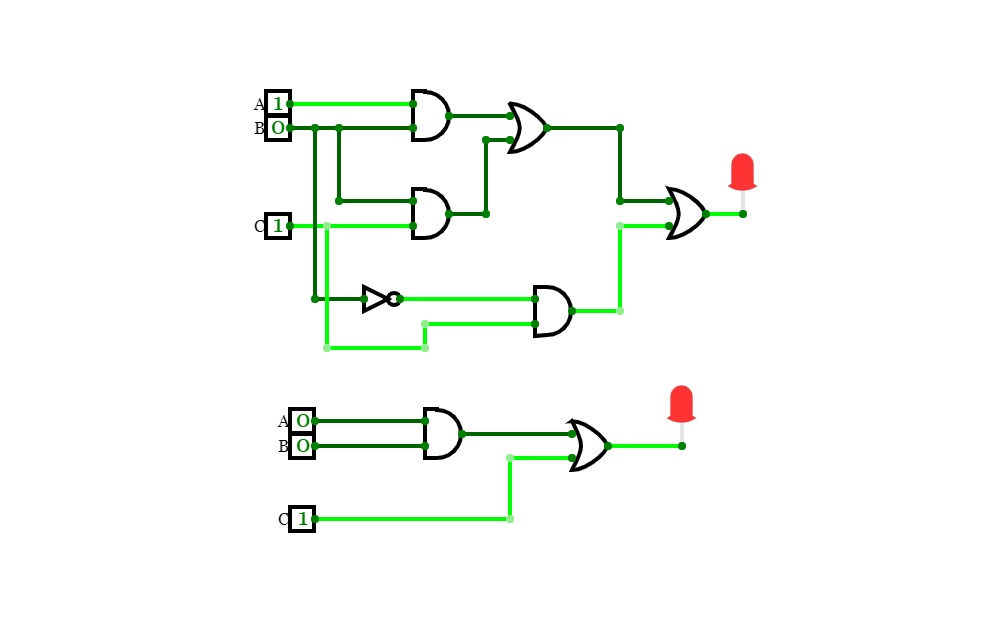

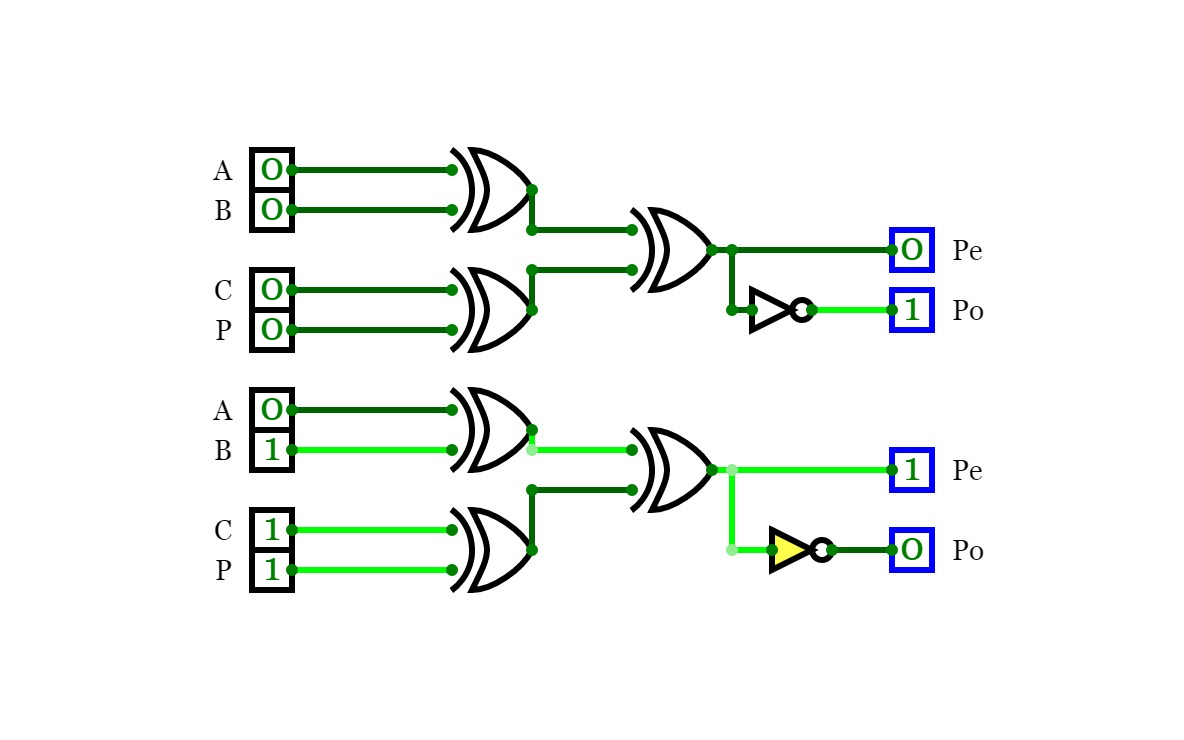

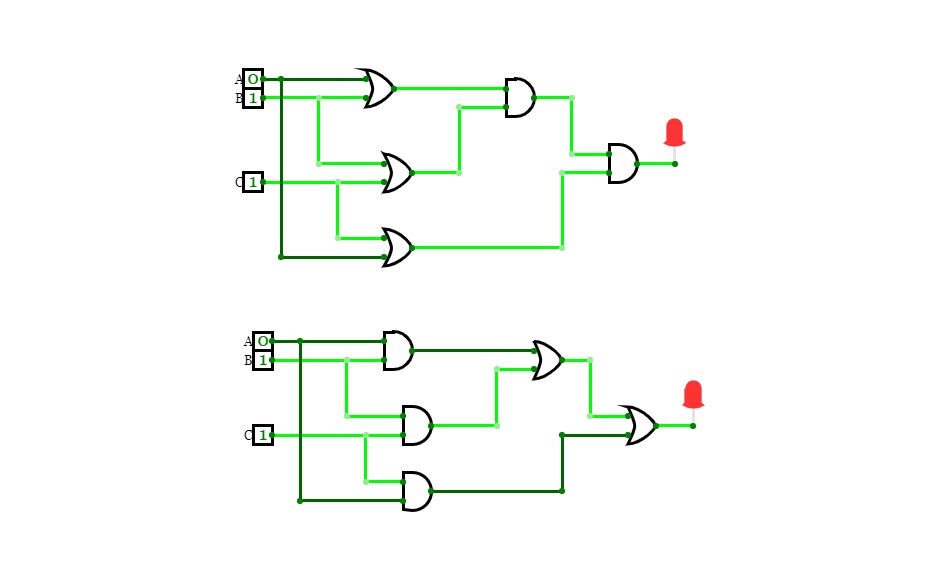

3 Parity Generator

3 Parity Generator

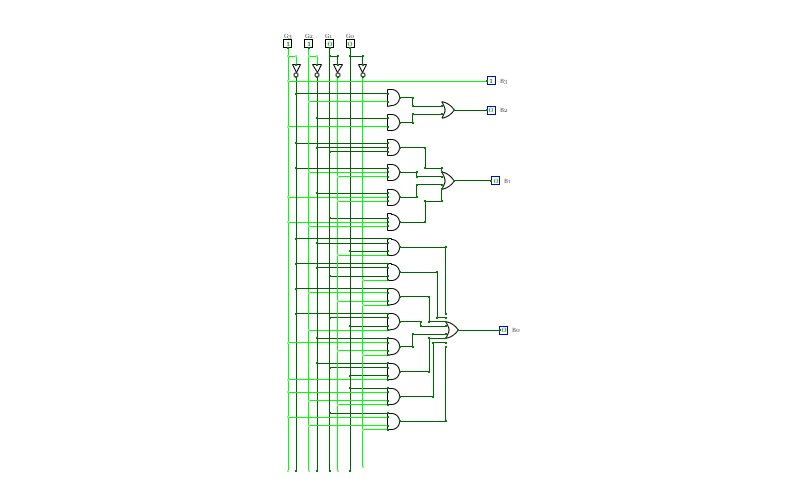

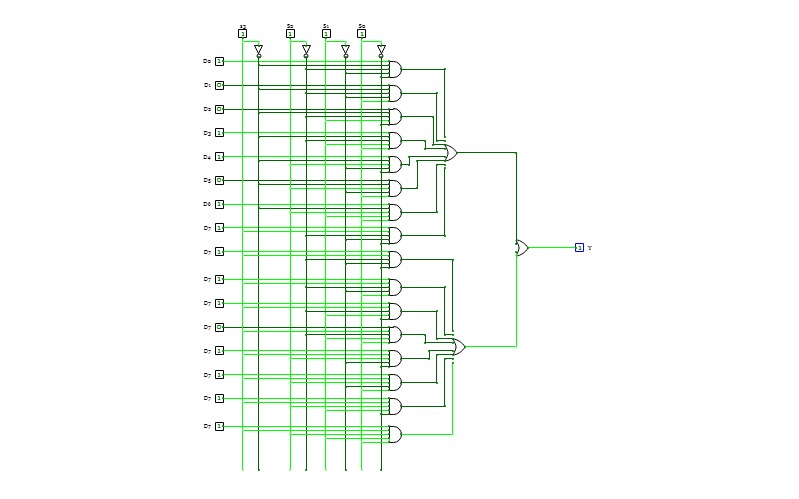

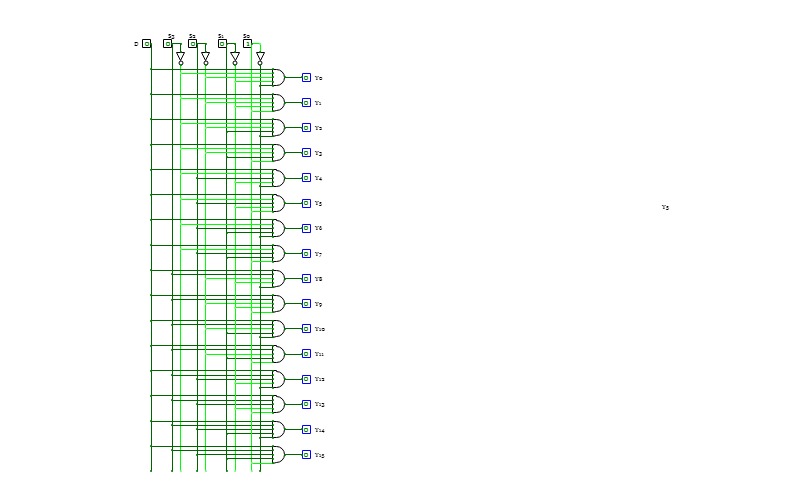

4 to 16 decoder

4 to 16 decoder

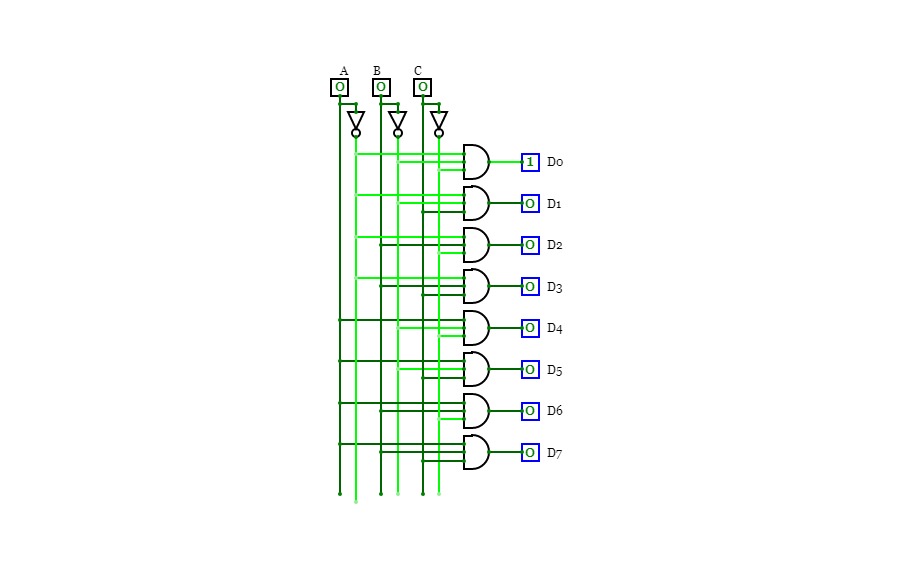

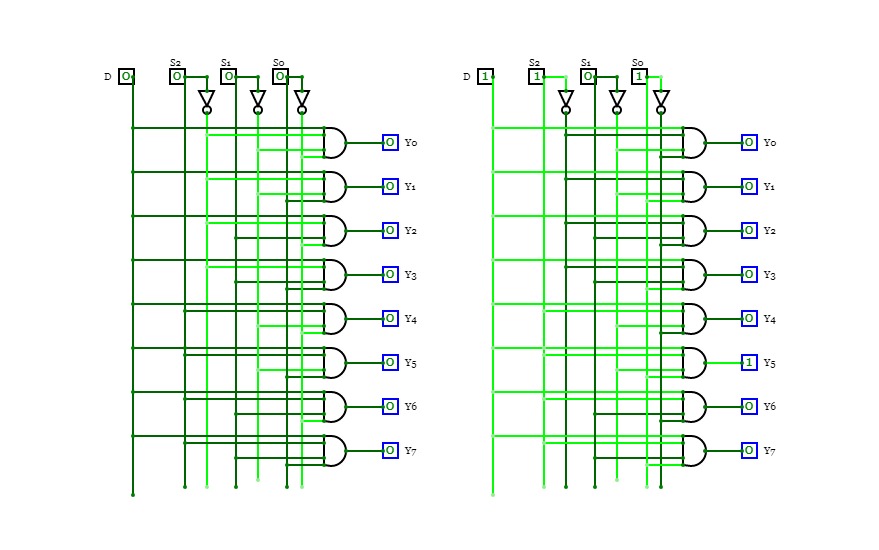

3 to 8 decoder

3 to 8 decoder

4 Bit BINARY to GRAY

4 Bit BINARY to GRAY

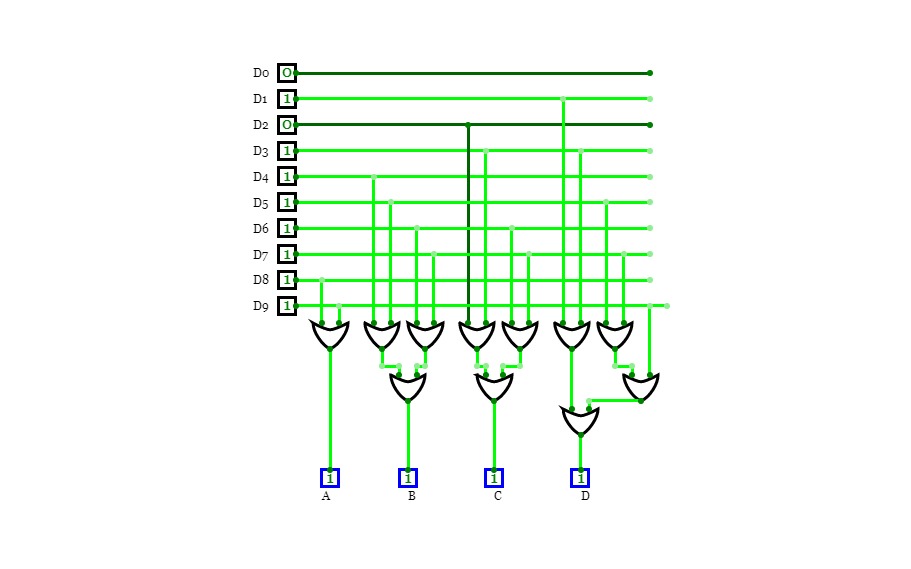

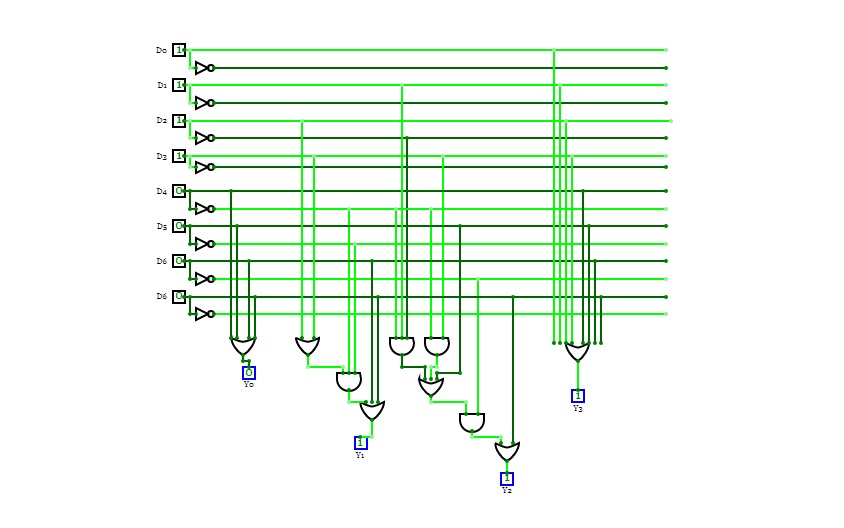

Decimal to BCD Encoder

Decimal to BCD Encoder

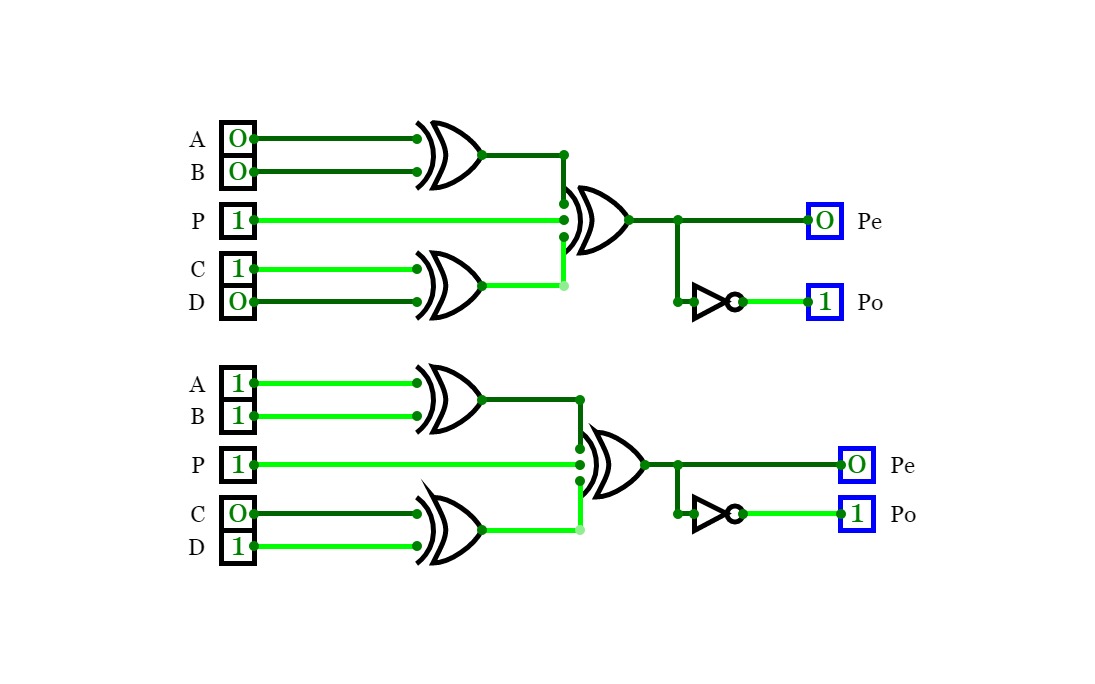

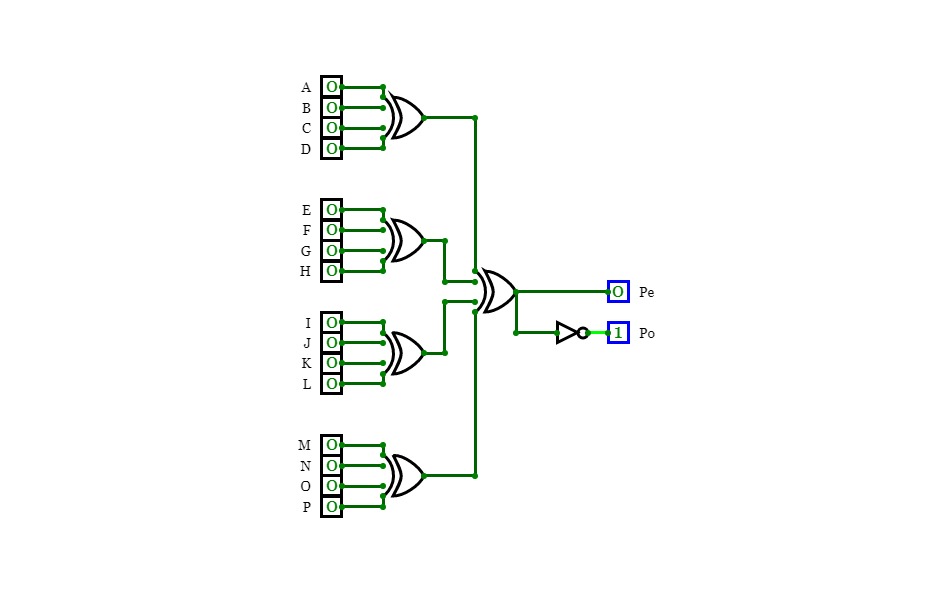

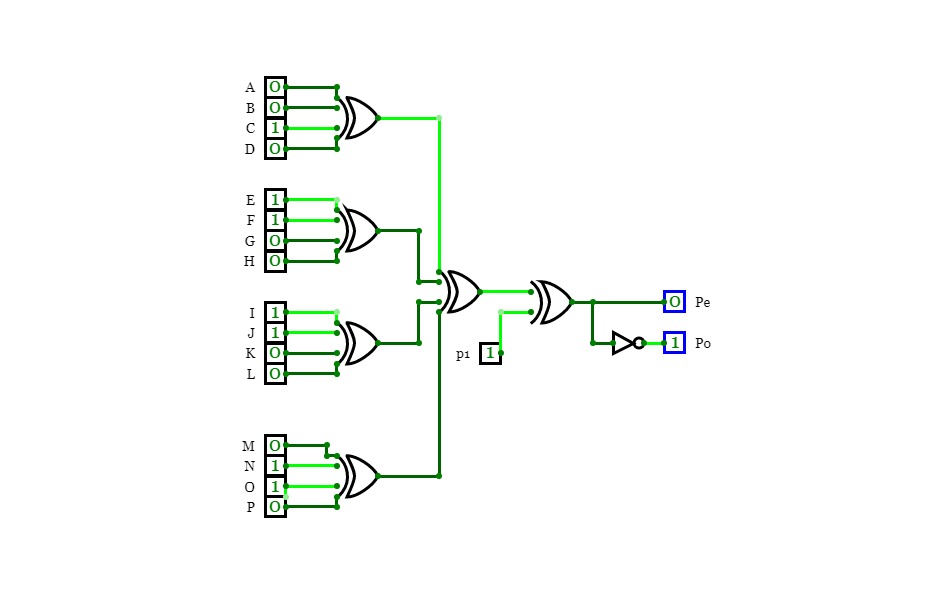

4 BIT PARITY GENERATOR

4 BIT PARITY GENERATOR

4 BIT PARITY CHECKER

4 BIT PARITY CHECKER

IMPLEMENTATION USING MINTERMS WITH 16:1 MUX

IMPLEMENTATION USING MINTERMS WITH 16:1 MUX

16 to 1 MUX

16 to 1 MUX

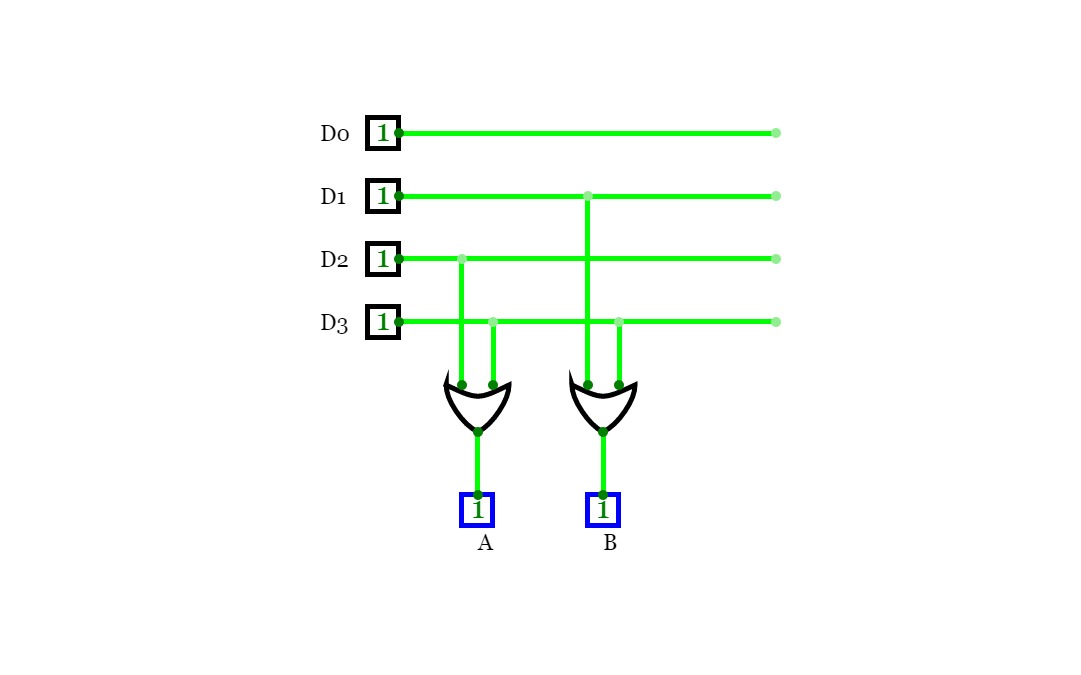

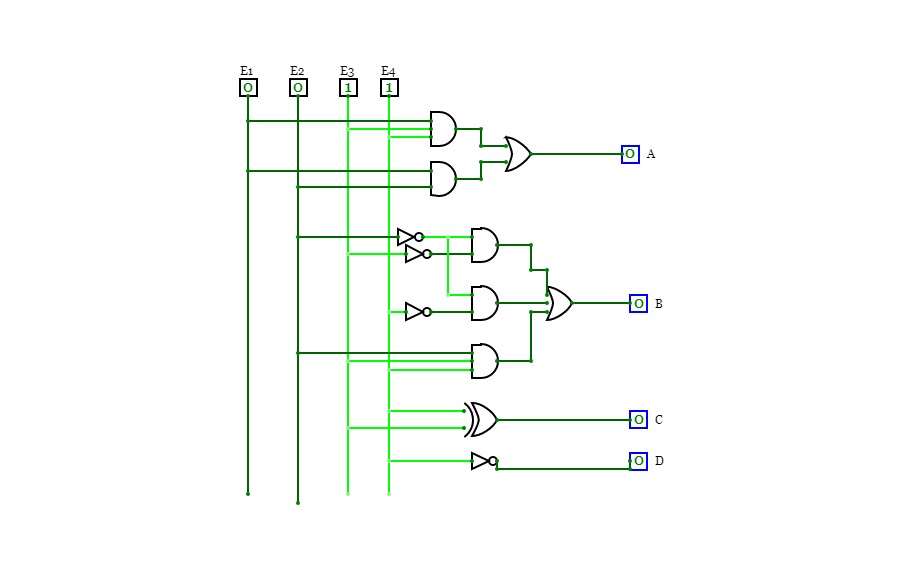

4 to 2 Encoder

4 to 2 Encoder

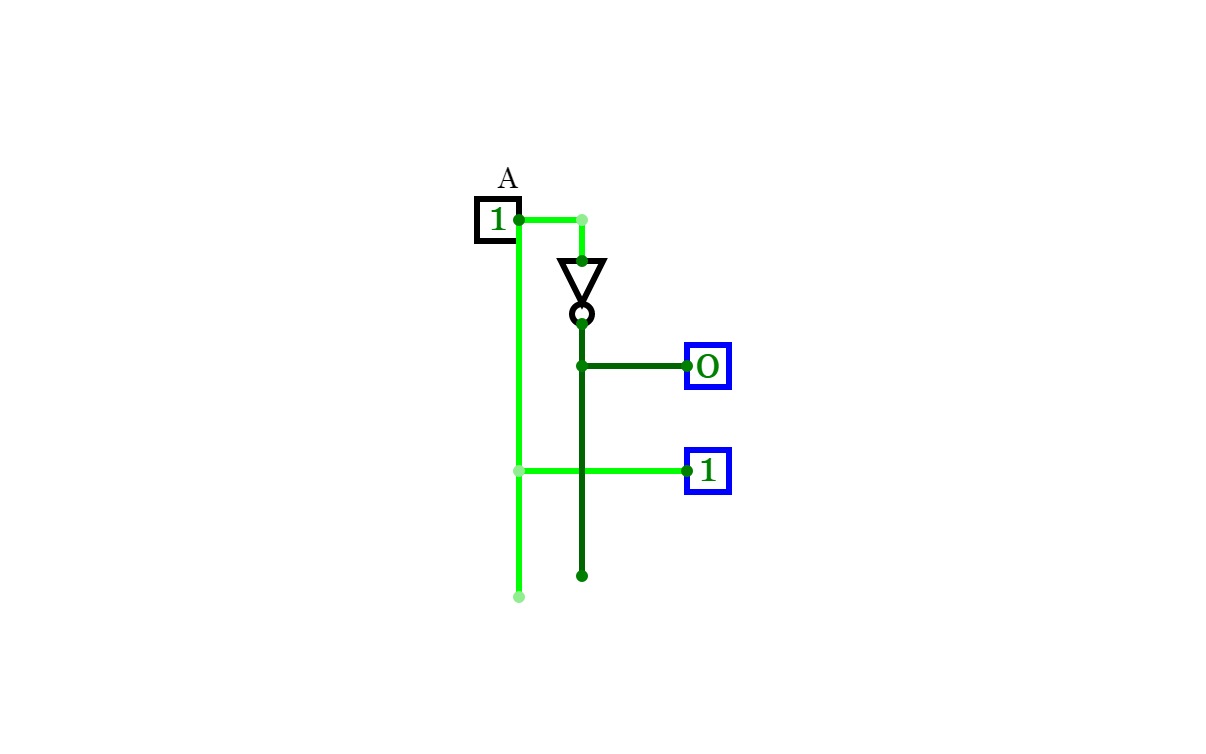

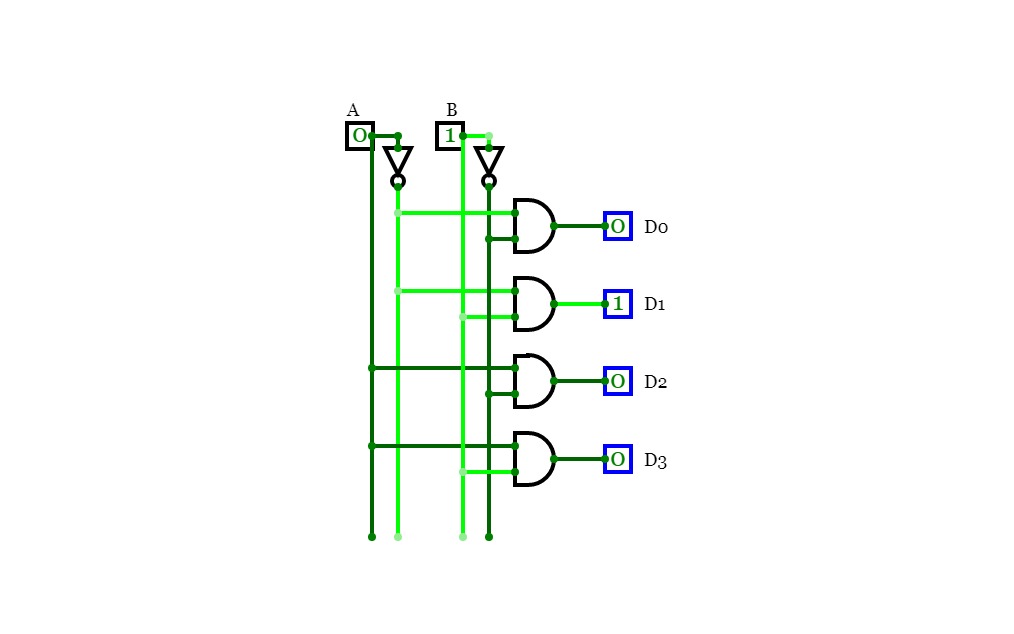

1 to 2 decoder

1 to 2 decoder

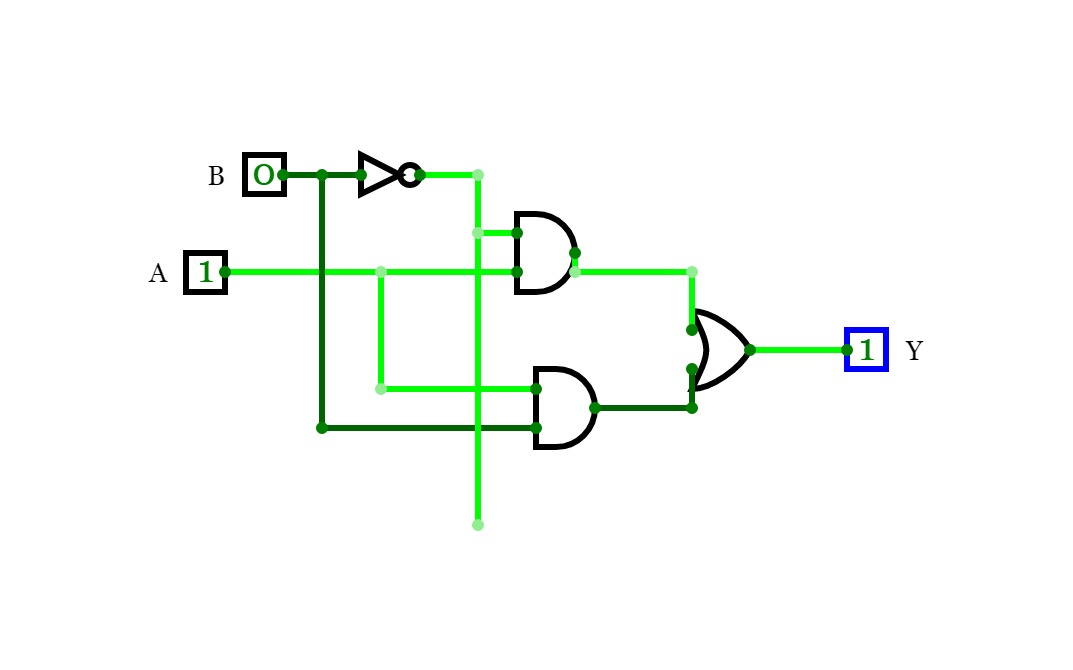

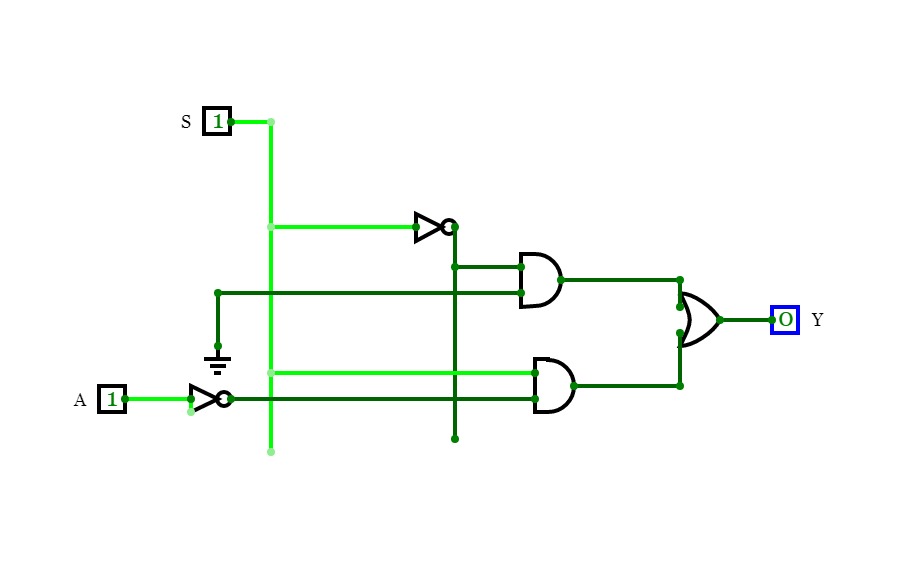

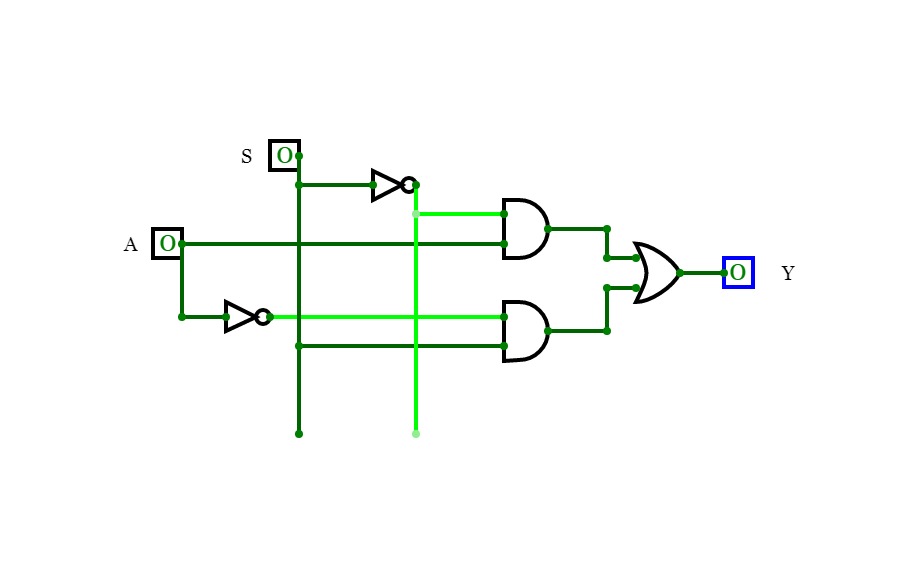

2 to 1 MUX using NOT gate

2 to 1 MUX using NOT gate

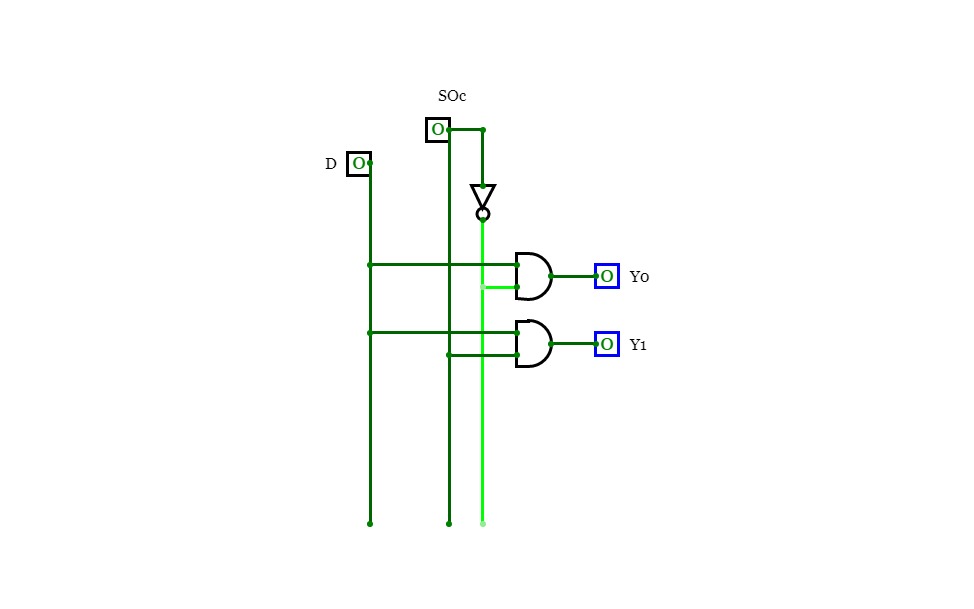

1 to 2 DEMUX

1 to 2 DEMUX

16 BIT Parity Generator

16 BIT Parity Generator

S-R Flip-flop

S-R Flip-flop

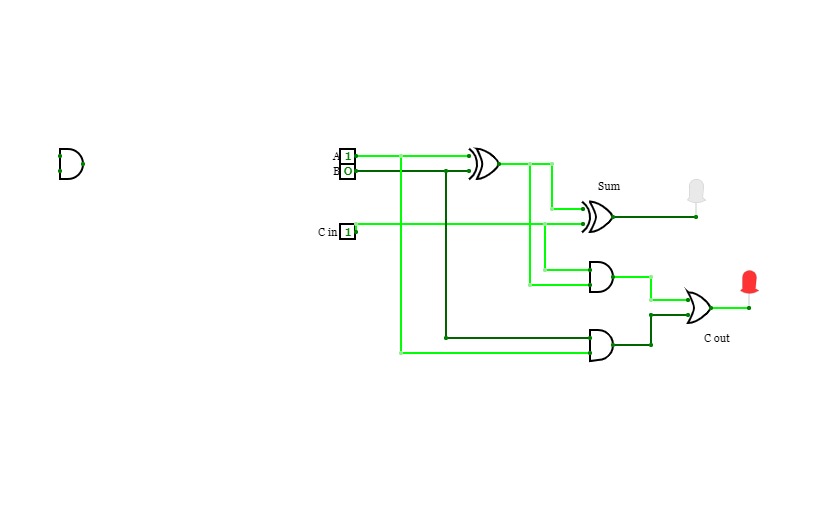

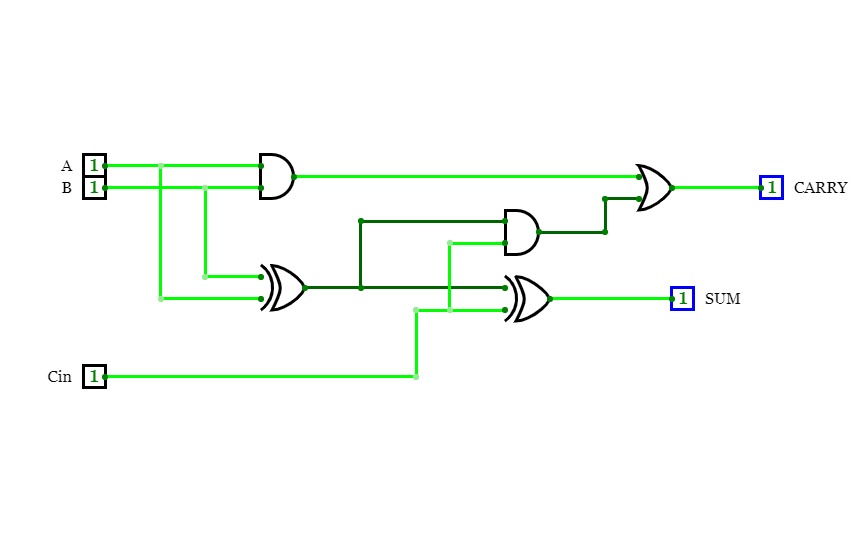

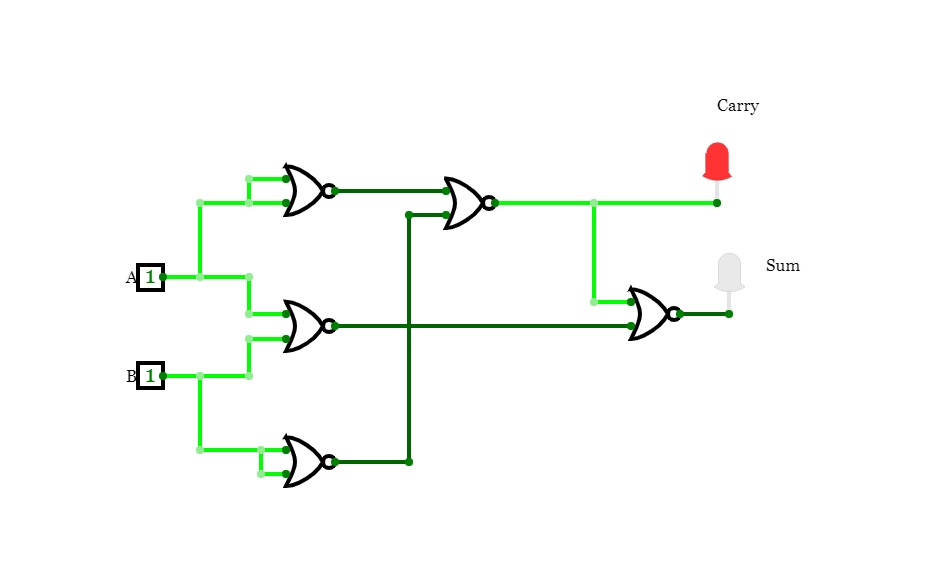

Full adder

Full adder

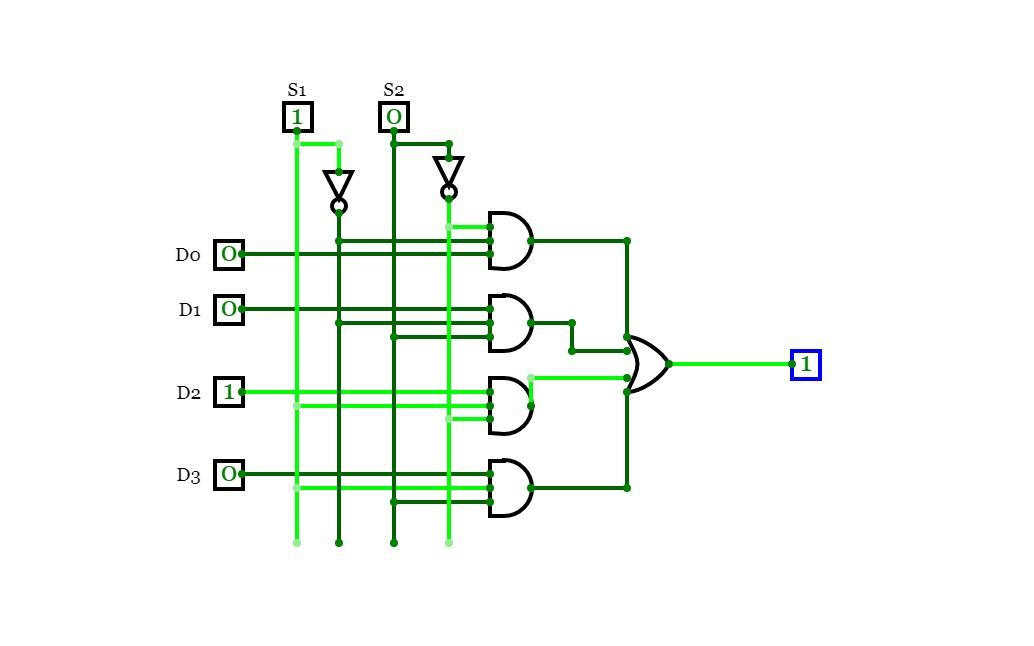

4 to 1 MUX

4 to 1 MUX

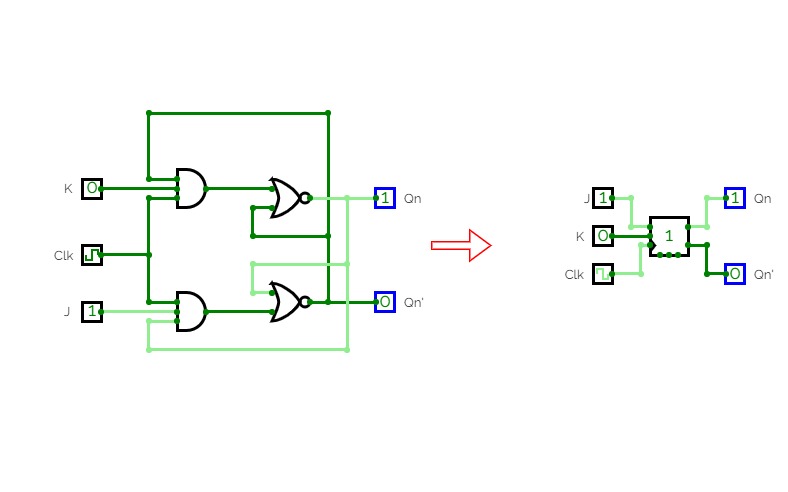

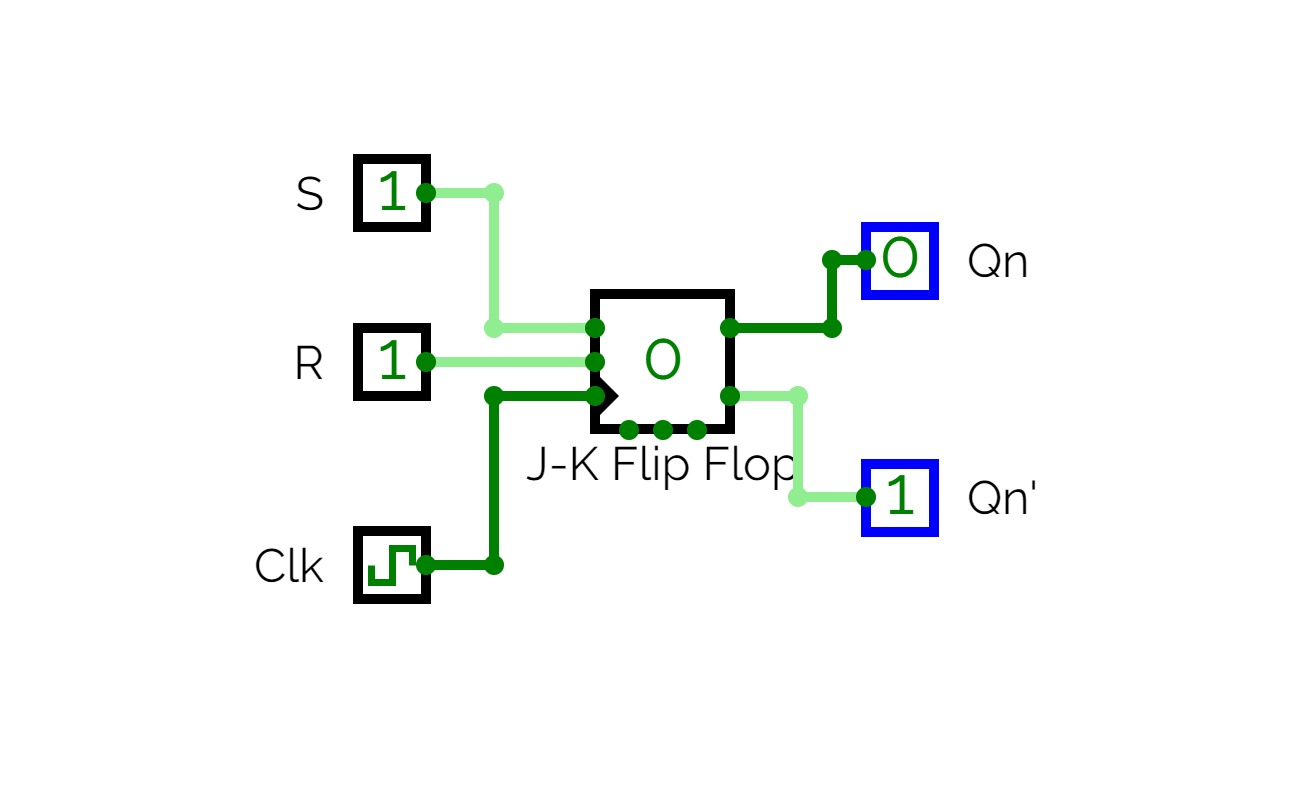

S-R Flip Flop to J-K Flip Flop

S-R Flip Flop to J-K Flip Flop

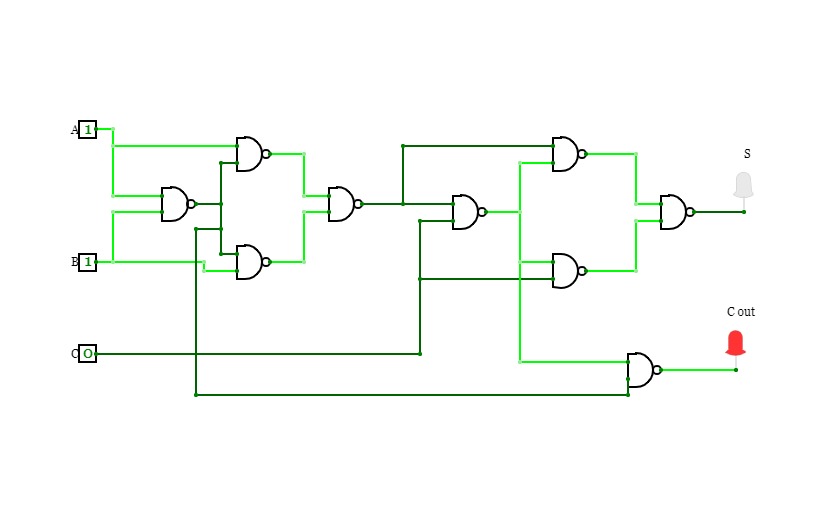

Full Adder using NAND gates

Full Adder using NAND gates

T Flip Flop to J-K Flip Flop

T Flip Flop to J-K Flip Flop

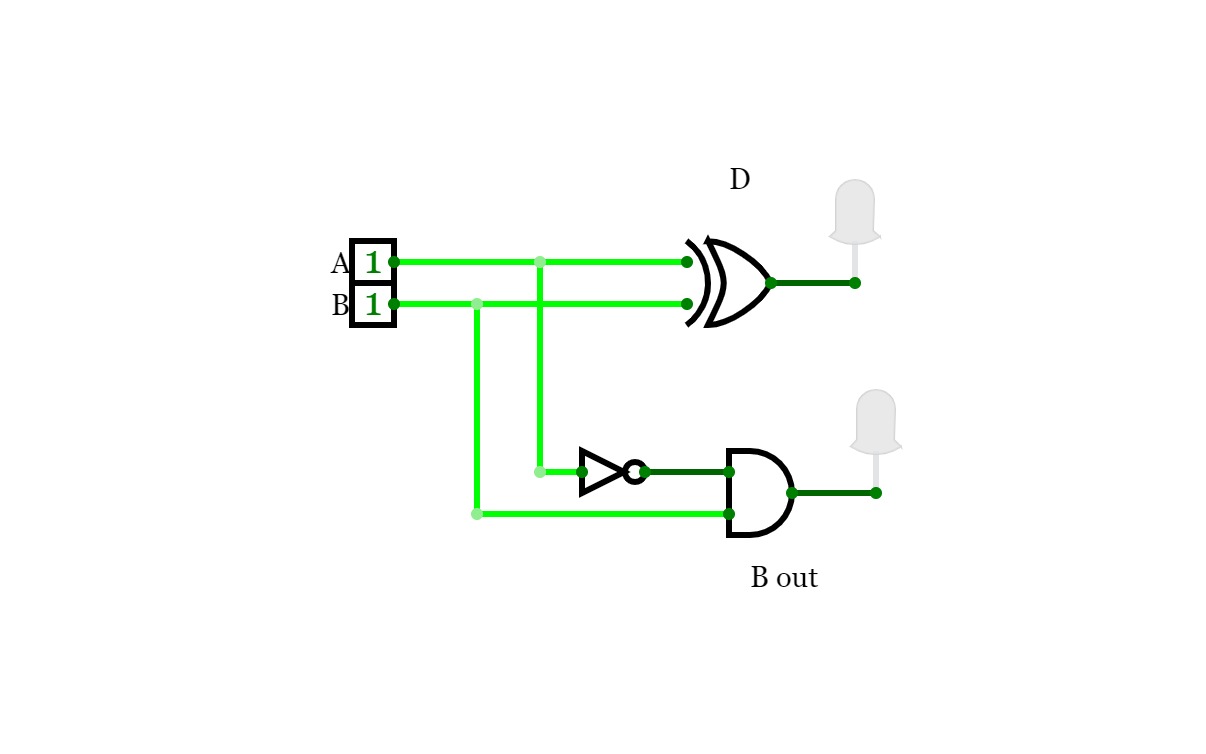

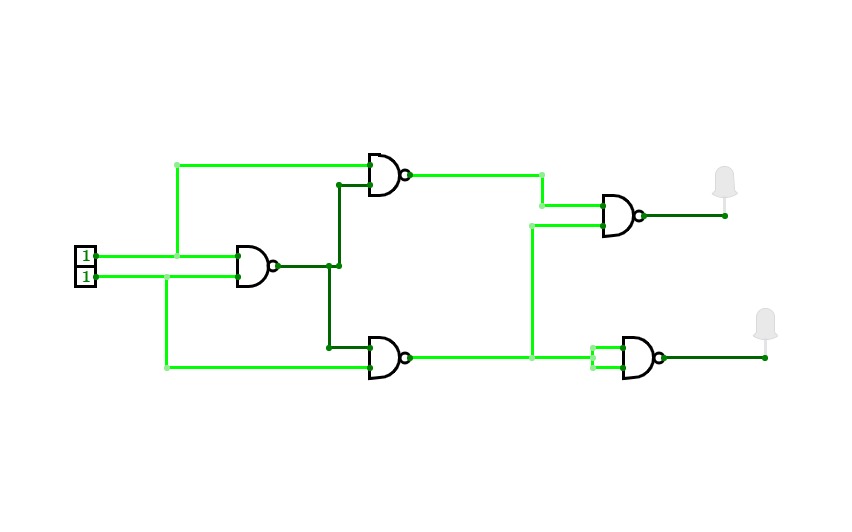

Half subtractor

Half subtractor

Full subtractor using NOR gates

Full subtractor using NOR gates

Associative propertty

Associative propertty

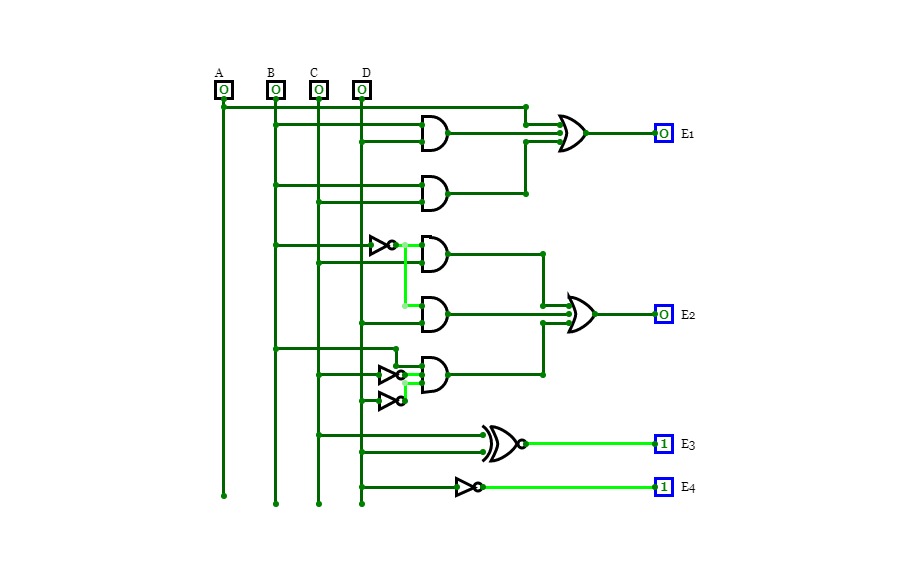

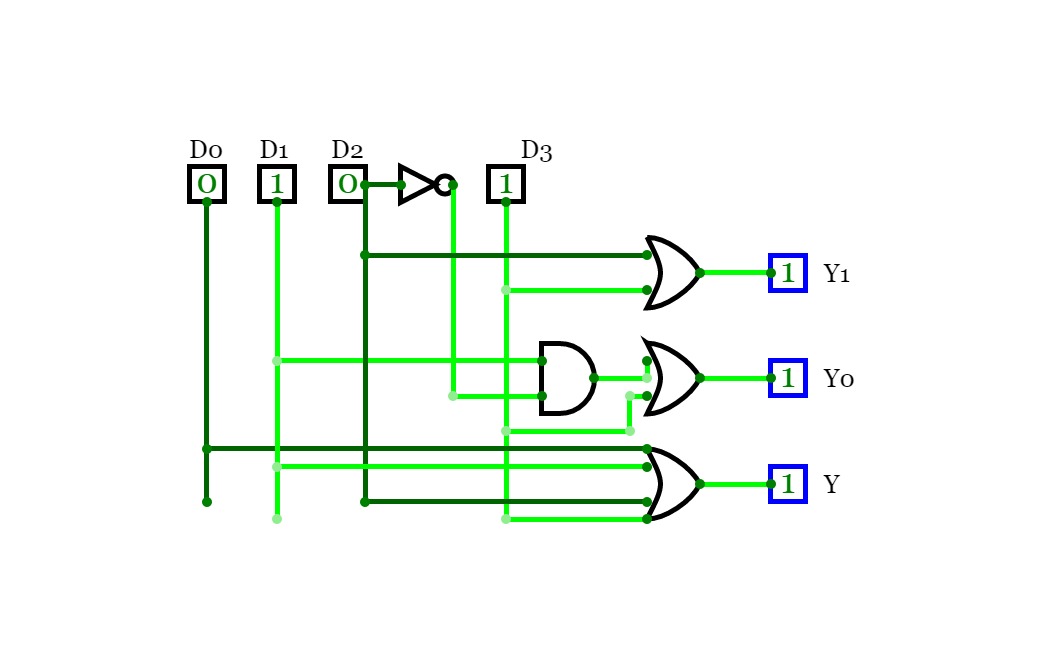

4 to 2 priority encoder

4 to 2 priority encoder

4 to 2 priority encoder

4 to 2 priority encoder

Counters

Counters

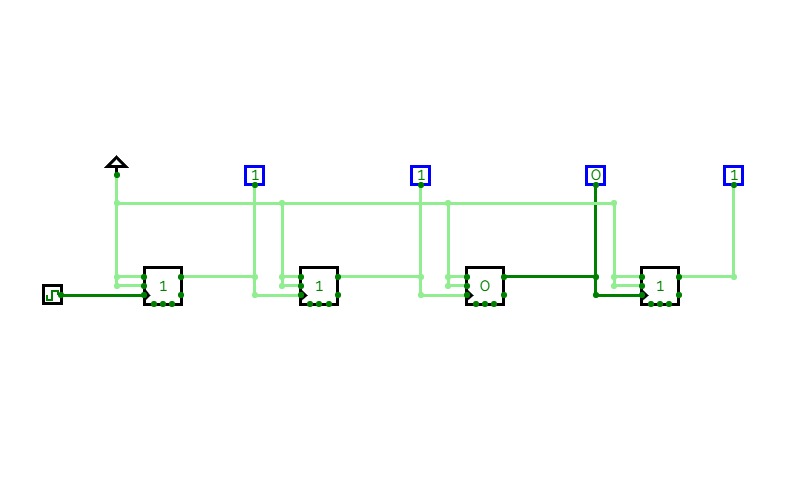

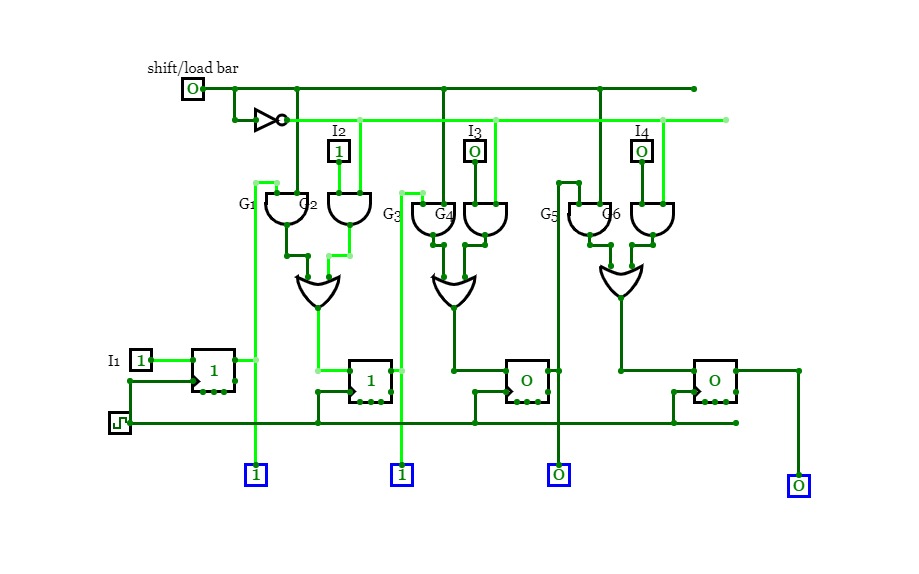

Serial in Serial out

Serial in Serial out

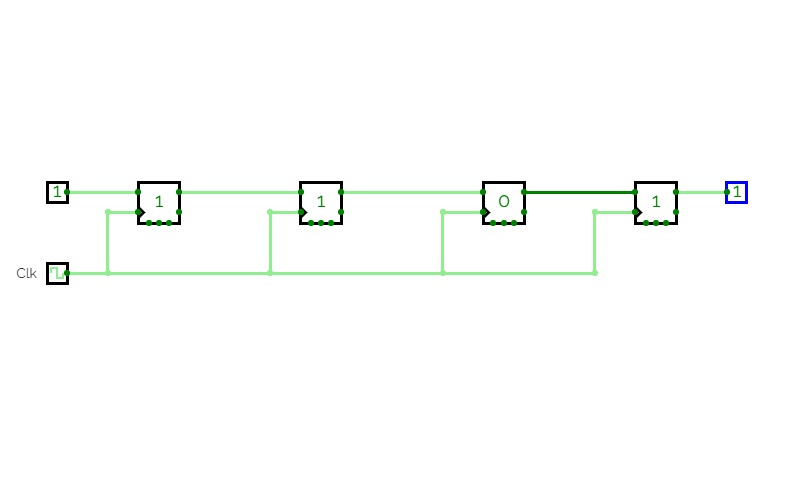

Serial in Parallel out

Serial in Parallel out

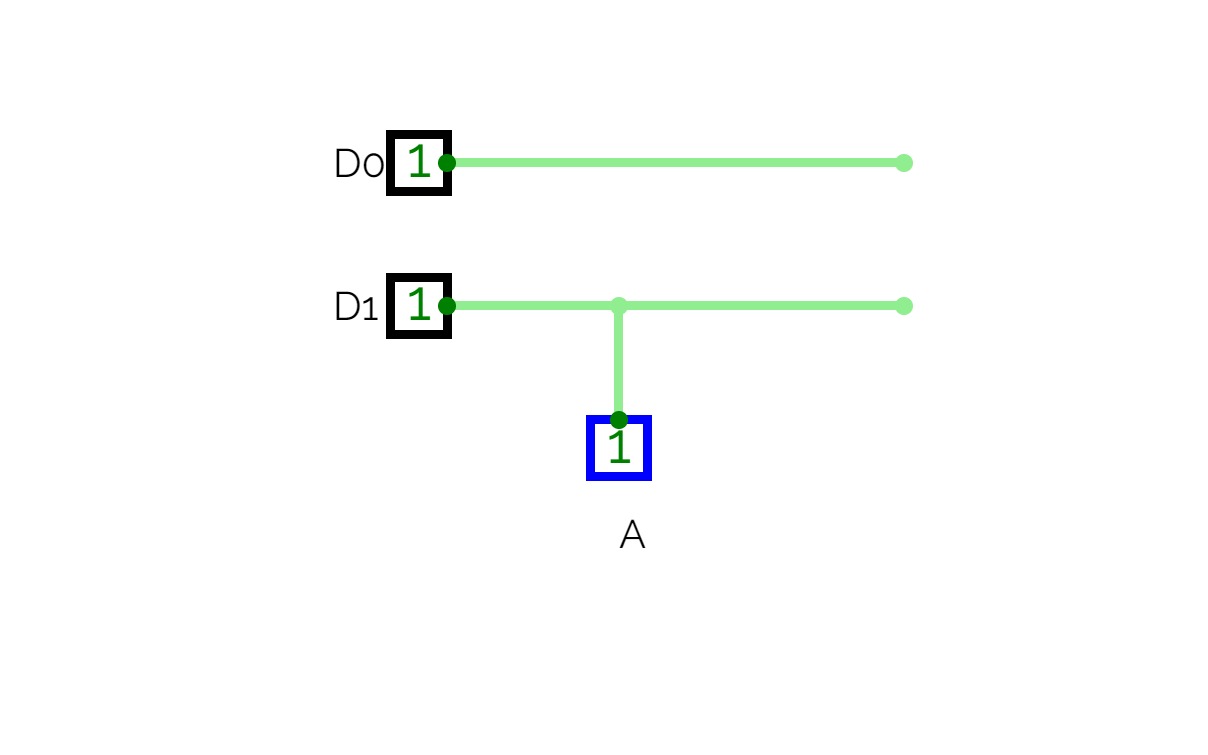

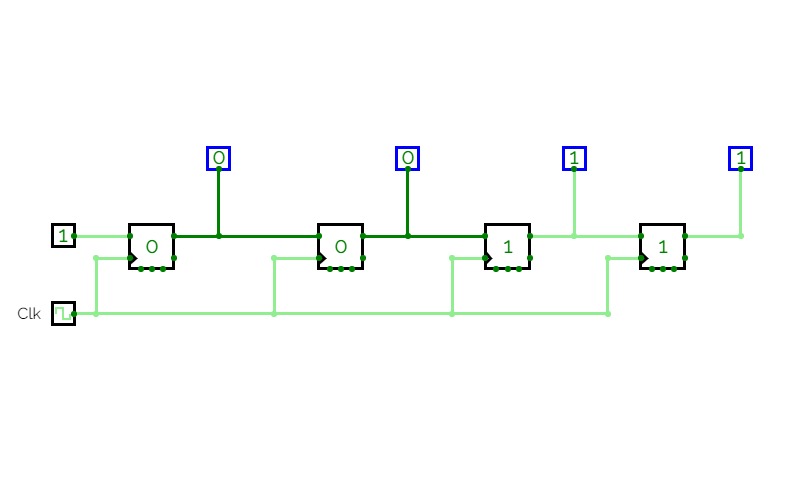

PARALLEL in PARALLEL out

PARALLEL in PARALLEL out

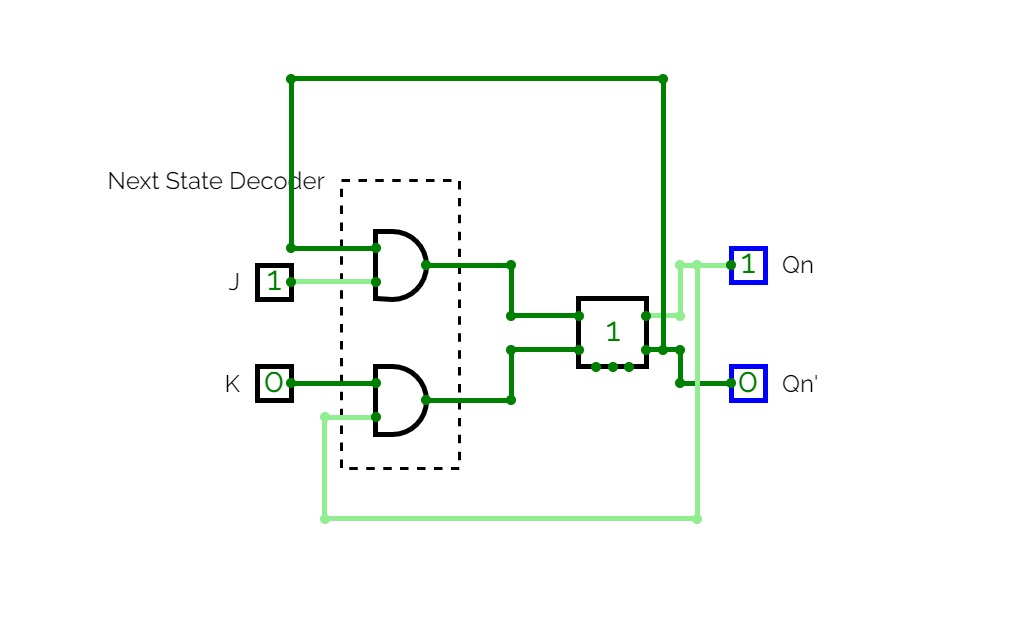

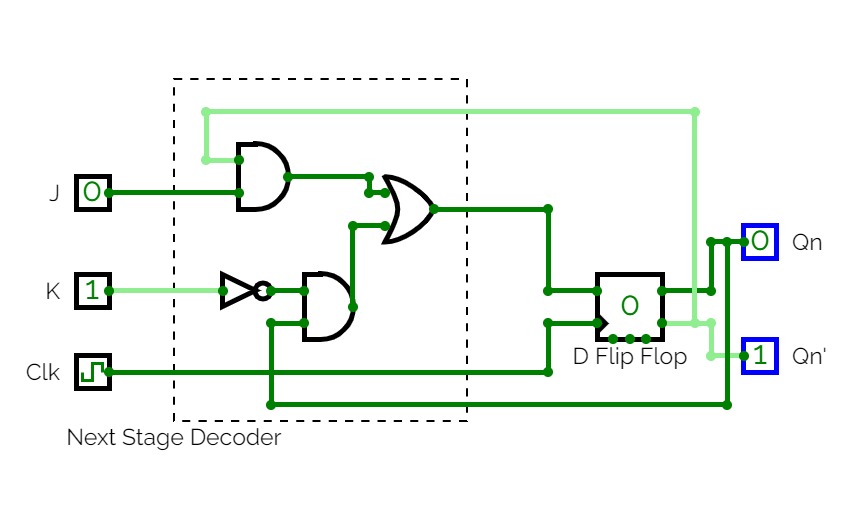

JK Flip Flop

JK Flip Flop

T Flip Flop to D Flip Flop

T Flip Flop to D Flip Flop

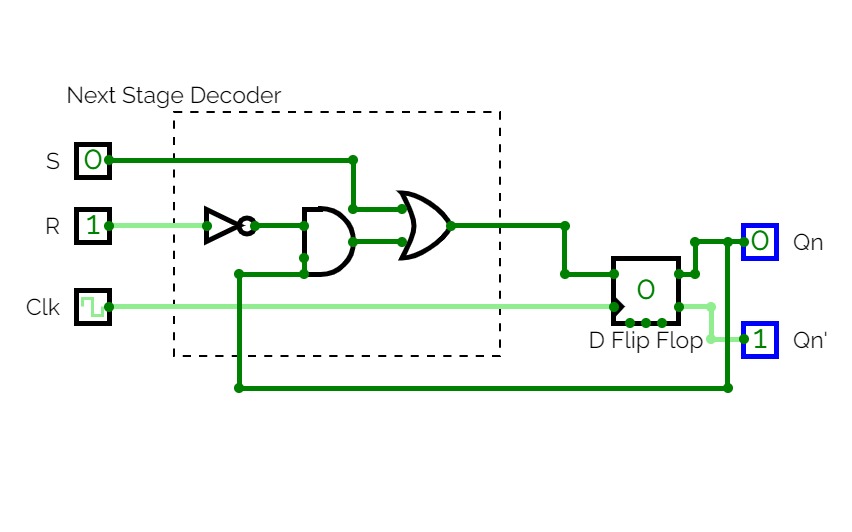

D Flip Flop To S-R Flip Flop

D Flip Flop To S-R Flip Flop

AB+BC+B'C=AB+C

AB+BC+B'C=AB+C

Half subtractor using NOR gate

Half subtractor using NOR gate

Full adder

Full adder

Half subtractor using NAND gate

Half subtractor using NAND gate

S-R Flip Flop to T Flip Flop

S-R Flip Flop to T Flip Flop

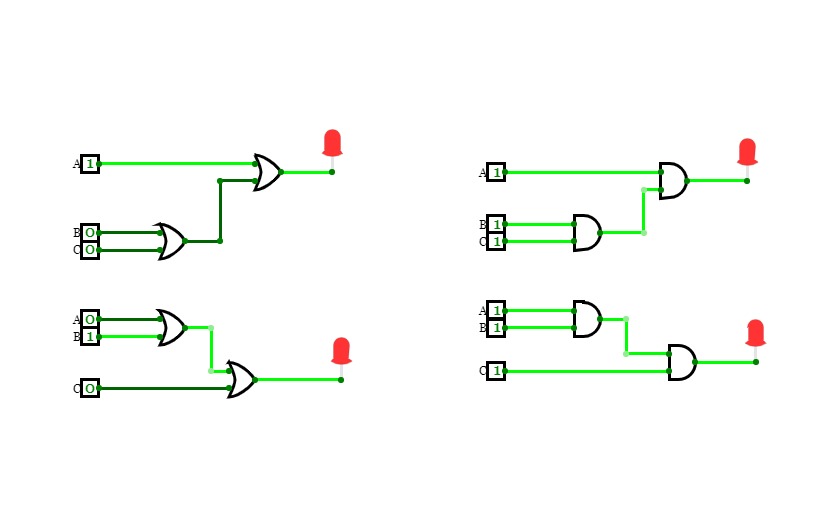

Commutative property

Commutative property

Distributive property

Distributive property

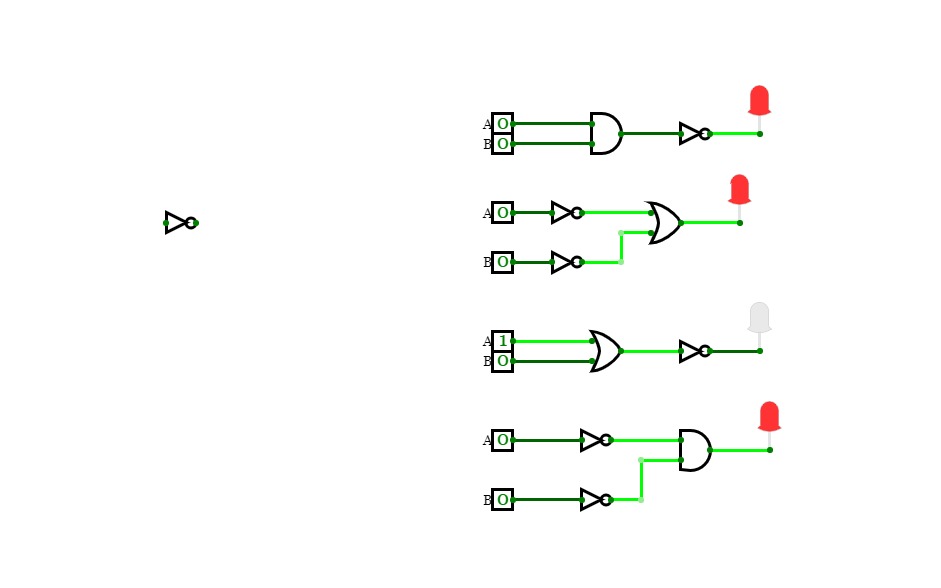

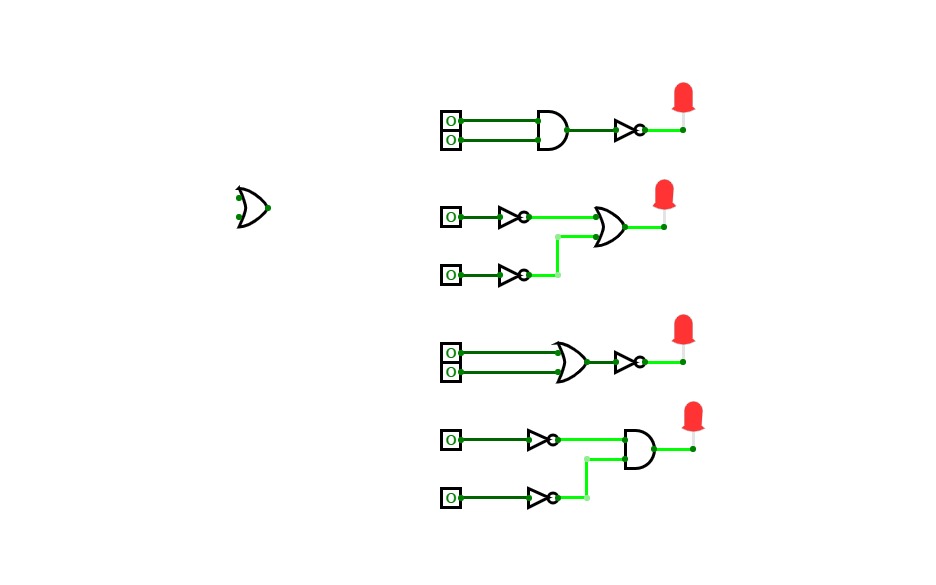

De Morgans Law

De Morgans Law

De Morgans Law

De Morgans Law

J-K Flip Flop to T Flip Flop

J-K Flip Flop to T Flip Flop

Consensus theorem

Consensus theorem

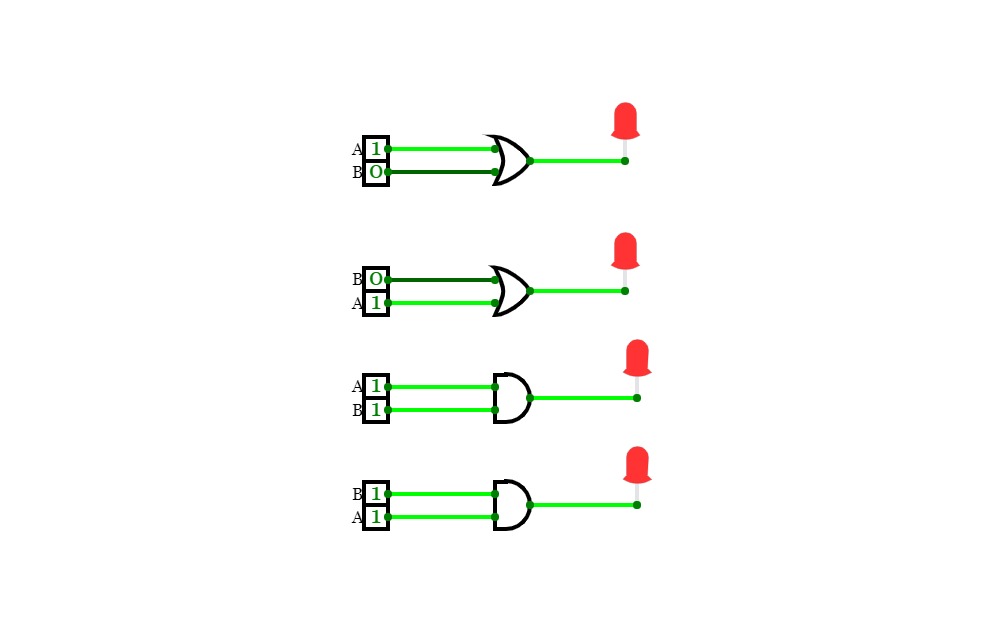

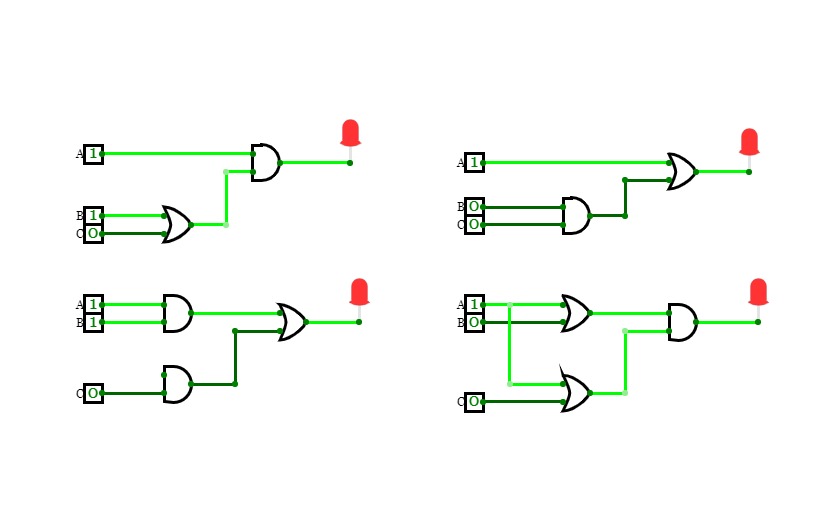

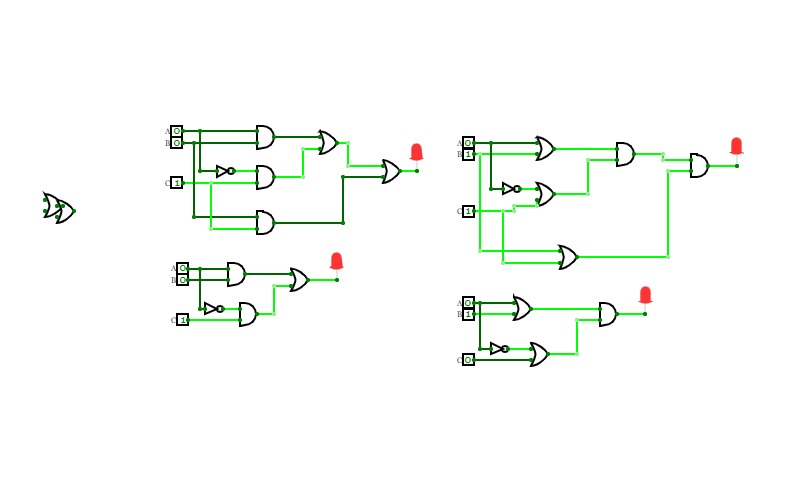

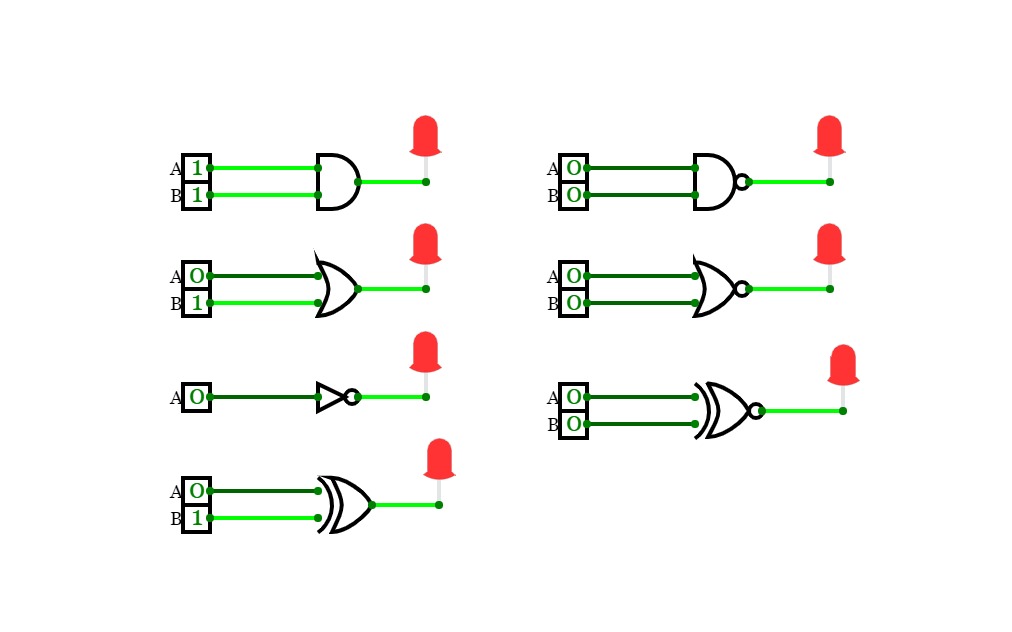

Logic Gates

Logic Gates

J-K Flip Flop to D Flip Flop

J-K Flip Flop to D Flip Flop

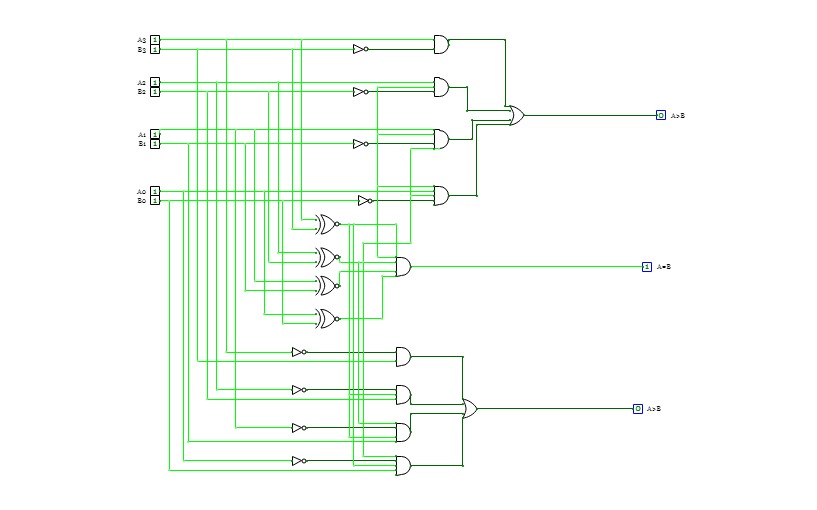

4 bit MC

4 bit MC

Half Adder using NOR gates

Half Adder using NOR gates

Absorption Law

Absorption Law

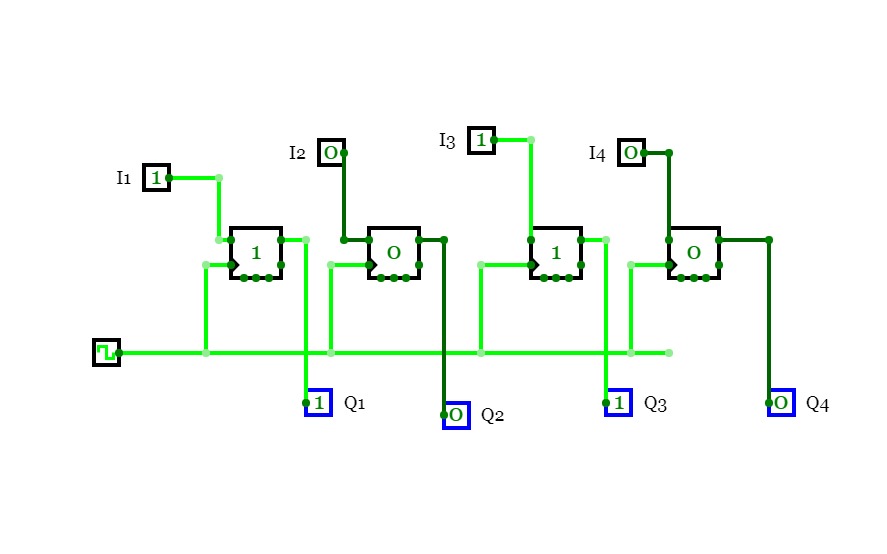

parallel in serial out

parallel in serial out

BCD to 7 segment Decoder

BCD to 7 segment Decoder

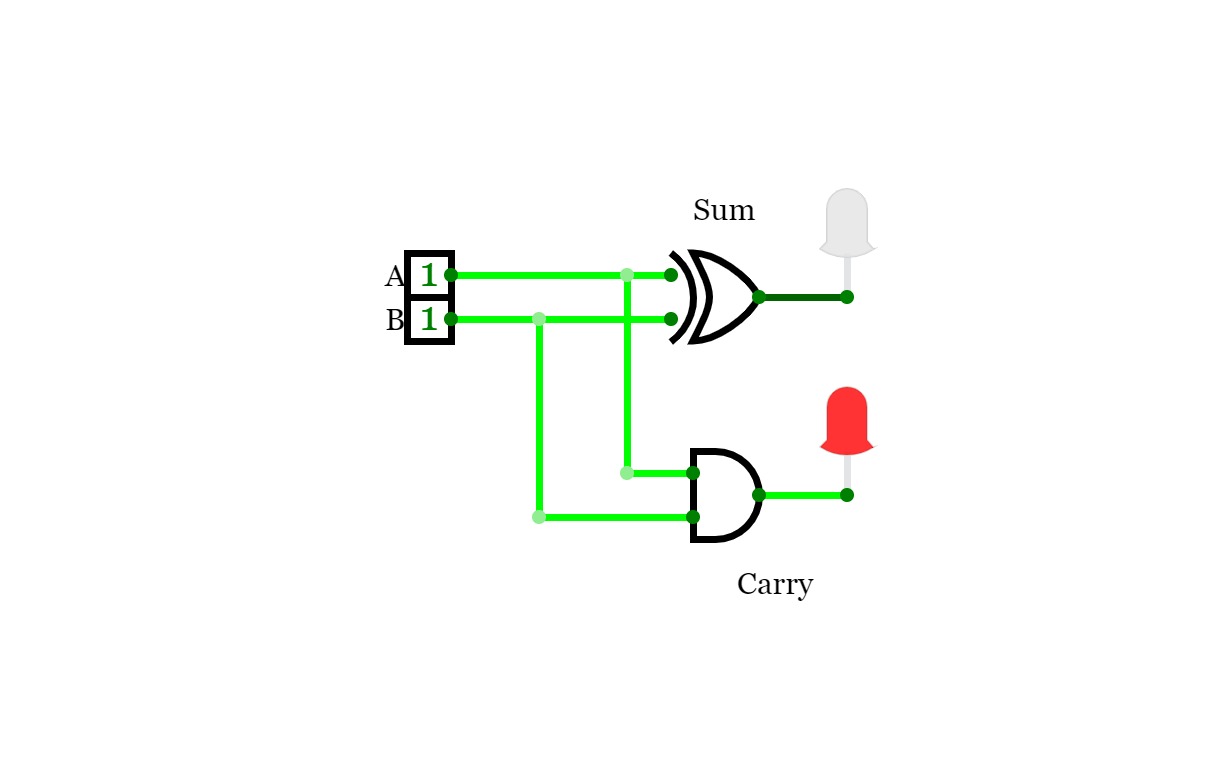

Half adder

Half adder

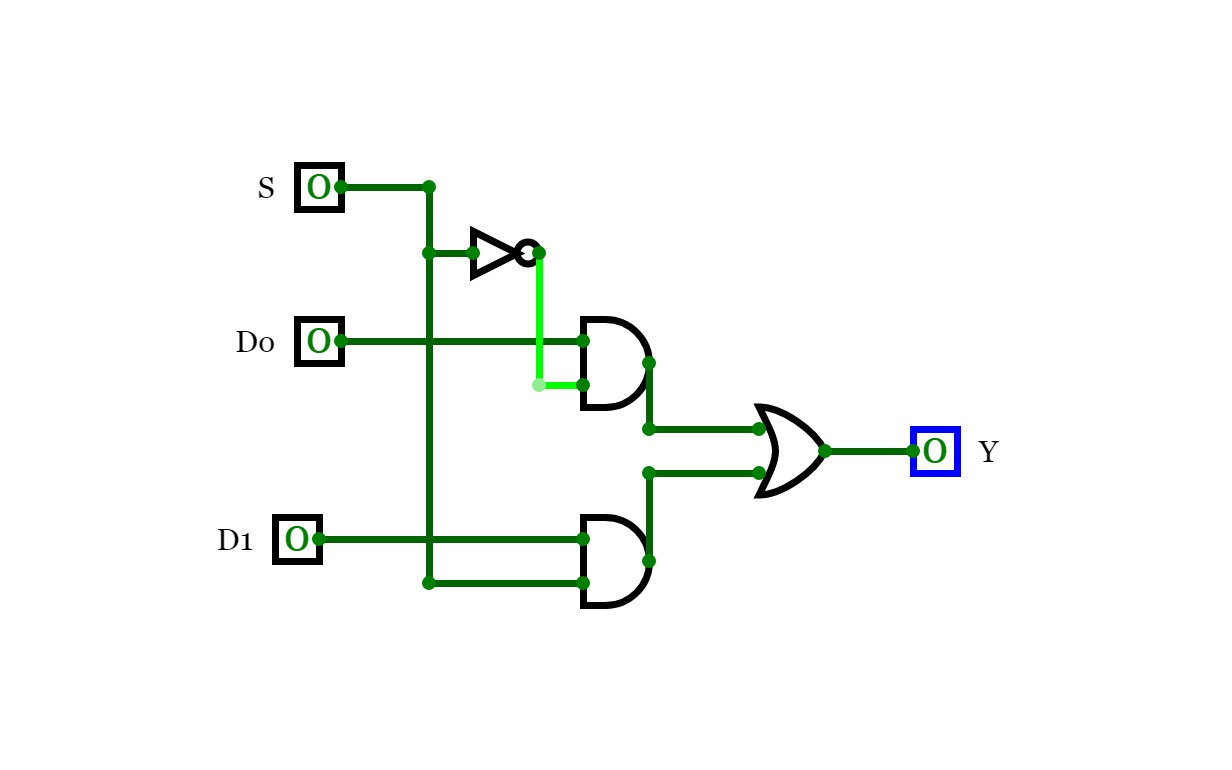

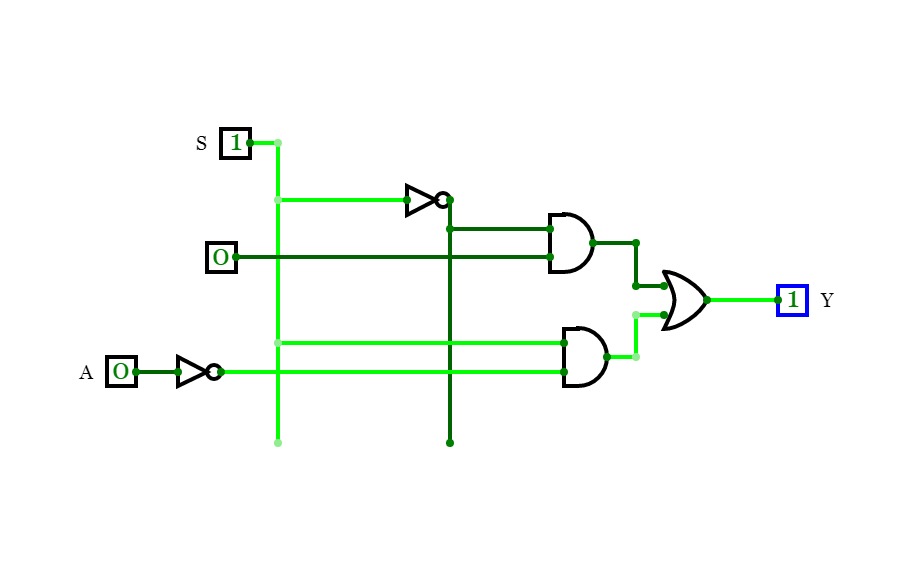

2 to 1 MUX

2 to 1 MUX

2 to 1 MUX using NOR gate

2 to 1 MUX using NOR gate

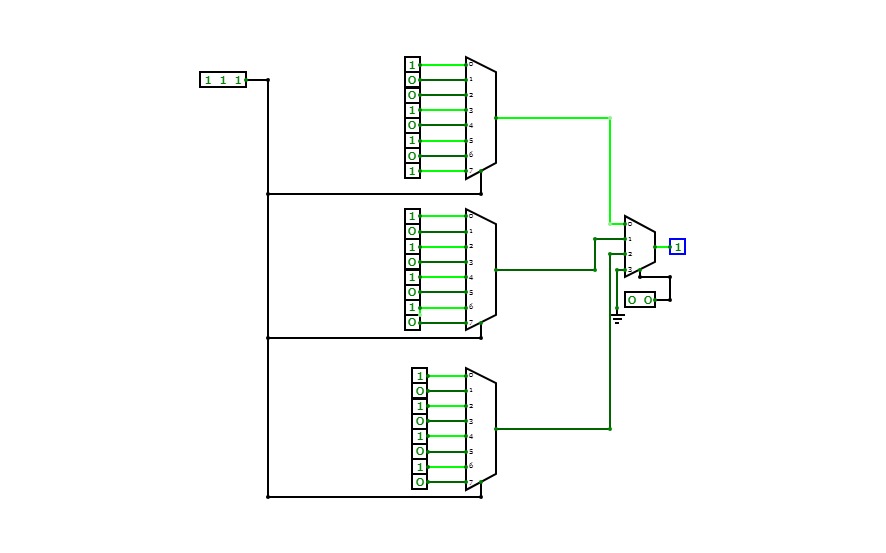

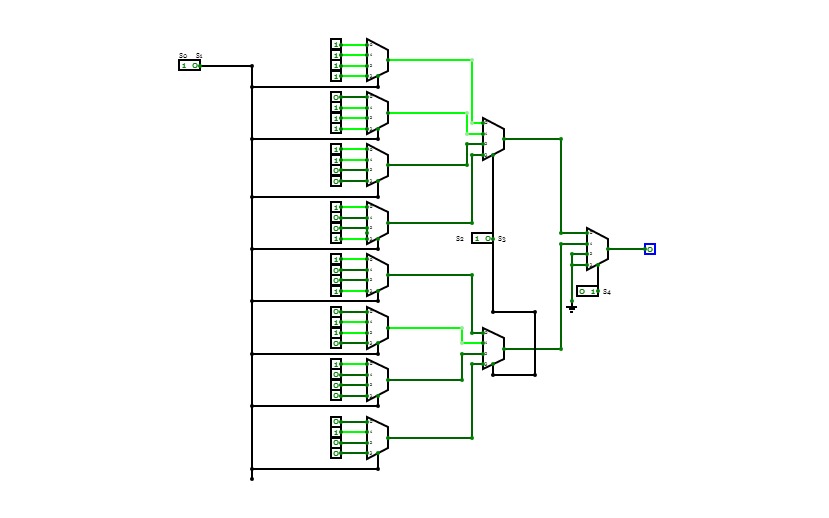

24 to 1 MUX using 8 to 1 MUX

24 to 1 MUX using 8 to 1 MUX

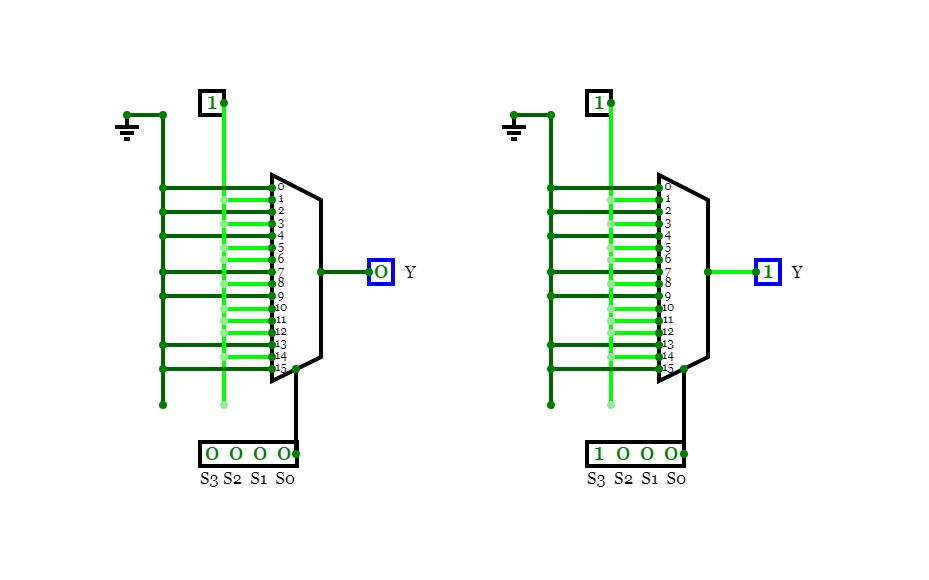

IMPLEMENTATION USING MINTERMS WITH 8:1 MUX

IMPLEMENTATION USING MINTERMS WITH 8:1 MUX

8 TO 3 Priority ENCODER

8 TO 3 Priority ENCODER

1:16 DEMUX

1:16 DEMUX

1:8 DEMUX

1:8 DEMUX

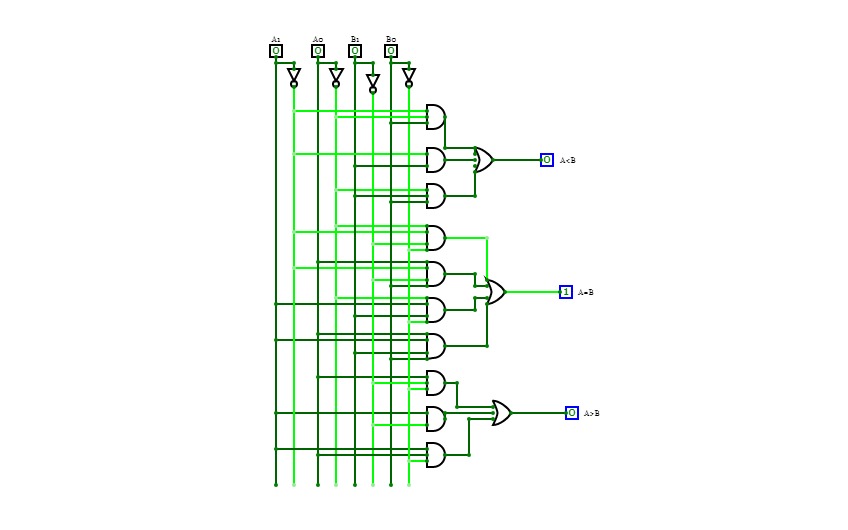

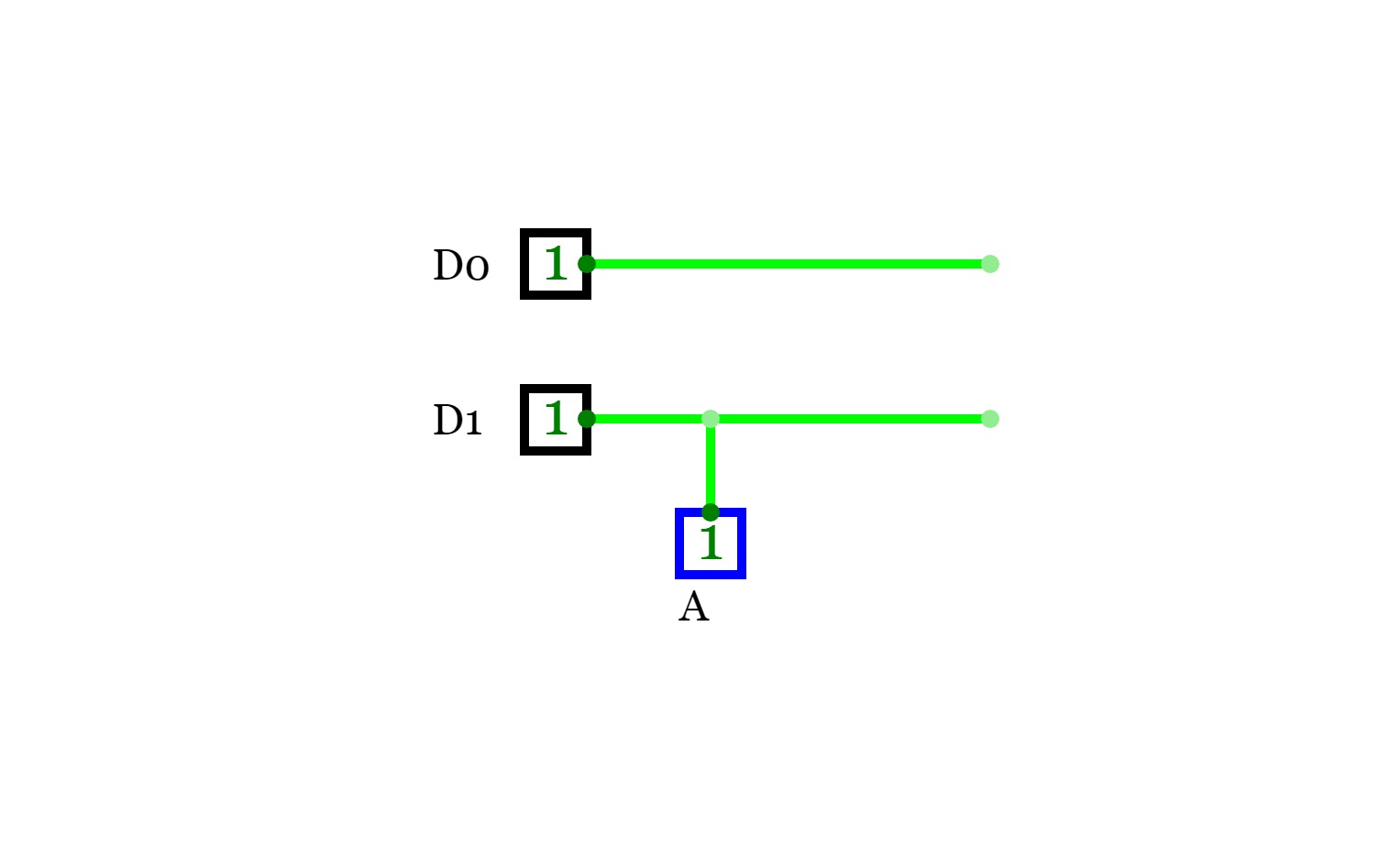

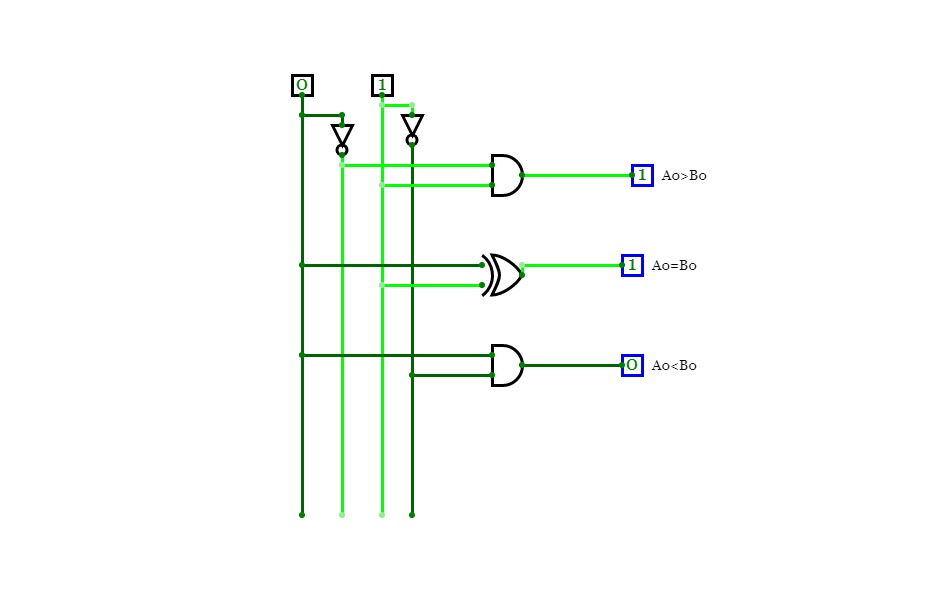

2 bit MC

2 bit MC

1 to 4 DEMUX

1 to 4 DEMUX

4 Bit Excess 3 to BCD

4 Bit Excess 3 to BCD

4 Bit BCD to Excess 3

4 Bit BCD to Excess 3

32 to 1 MUX using to 1Mux

32 to 1 MUX using to 1Mux

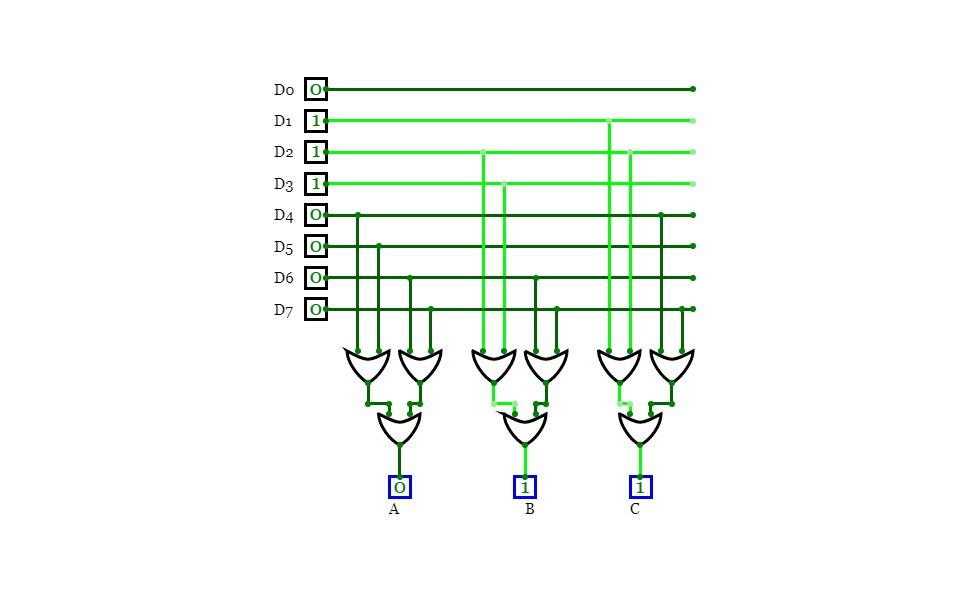

Octal to Binary Encoder

Octal to Binary Encoder

16 BIT PARITY CHECKER

16 BIT PARITY CHECKER

3 BIT PARITY CHEKER

3 BIT PARITY CHEKER

S-R Flip Flop to D Flip Flop

S-R Flip Flop to D Flip Flop

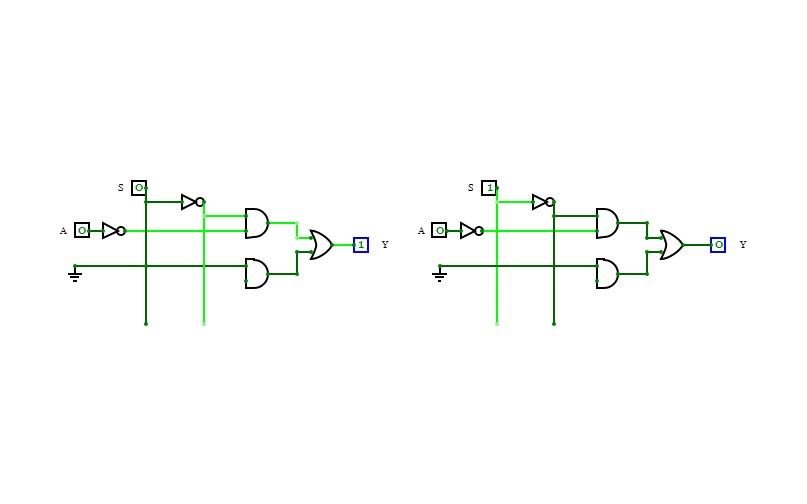

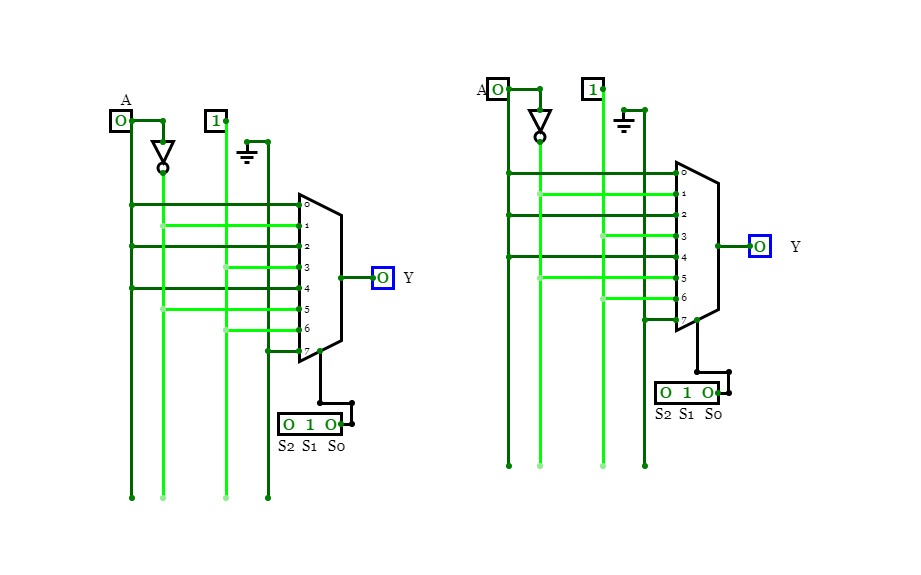

IMPLEMENTATION USING MINTEMS WITH 2:1 MUX

IMPLEMENTATION USING MINTEMS WITH 2:1 MUX

J-K Flip Flop to S-R Flip Flop

J-K Flip Flop to S-R Flip Flop

D Flip Flop to T Flip Flop

D Flip Flop to T Flip Flop

T Flip Flop to S-R Flip Flop

T Flip Flop to S-R Flip Flop

2 to 1 Encoder

2 to 1 Encoder

2 to 1 MUX using EXOR gate

2 to 1 MUX using EXOR gate

4 BIT SYNCHRONOUS up COUNTER

4 BIT SYNCHRONOUS up COUNTER

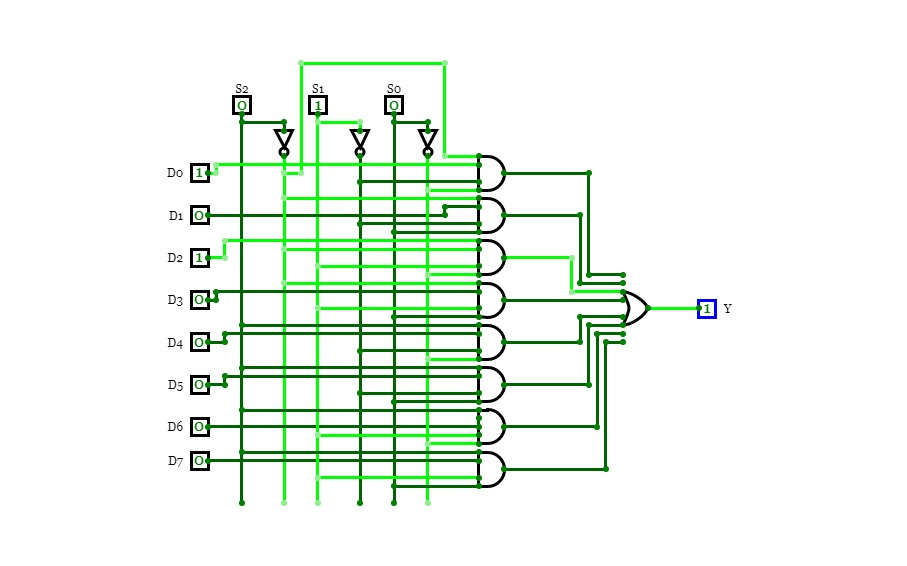

8 TO 1 MUX

8 TO 1 MUX

Single bit MC

Single bit MC

4 to 2 priority encoder

4 to 2 priority encoder

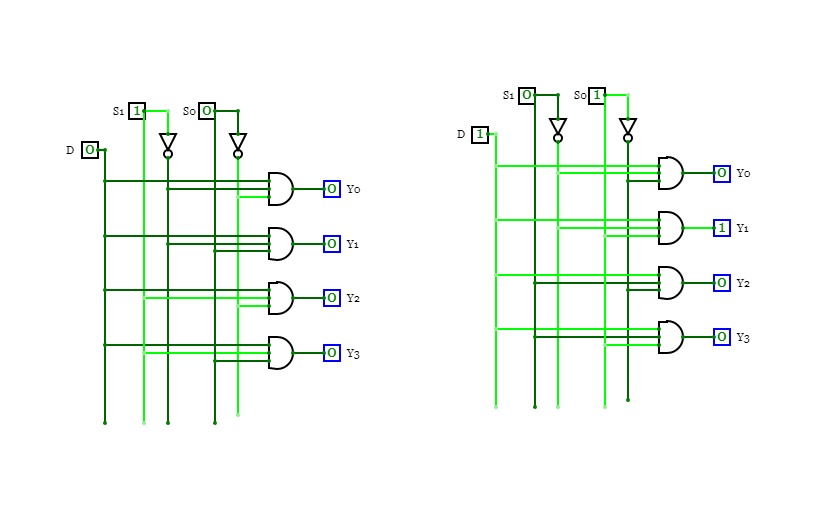

2 to 4 Decoder

2 to 4 Decoder

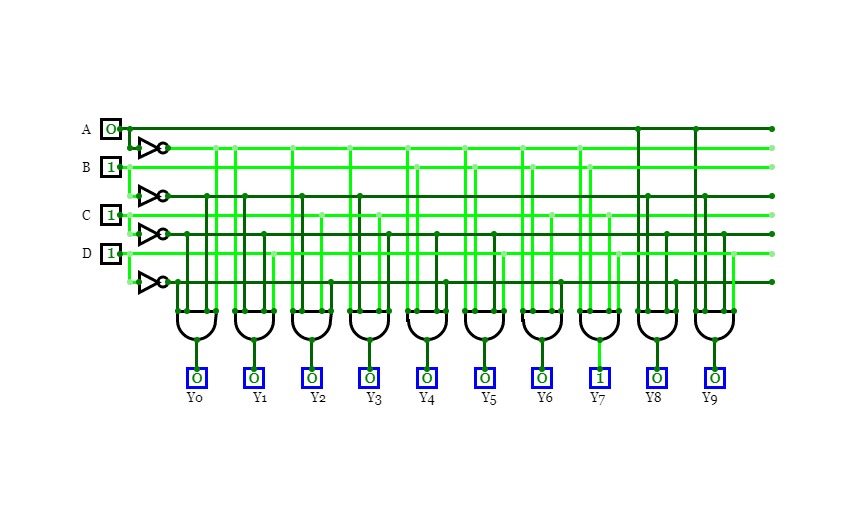

BCD to Decimal Decoder

BCD to Decimal Decoder

D Flip Flop to J-K Flip Flop

D Flip Flop to J-K Flip Flop

(A+B)(B+C)(C+A)=AB+BC+CA

(A+B)(B+C)(C+A)=AB+BC+CA

2 to 1 MUX using NAND gate

2 to 1 MUX using NAND gate

2 to 1 MUX using OR Gate

2 to 1 MUX using OR Gate