Sufiya

Member since: 3 years

Educational Institution: Not Entered

Country: Not Entered

8:1 MUX using Dual 4:1 MUX

8:1 MUX using Dual 4:1 MUX

Public

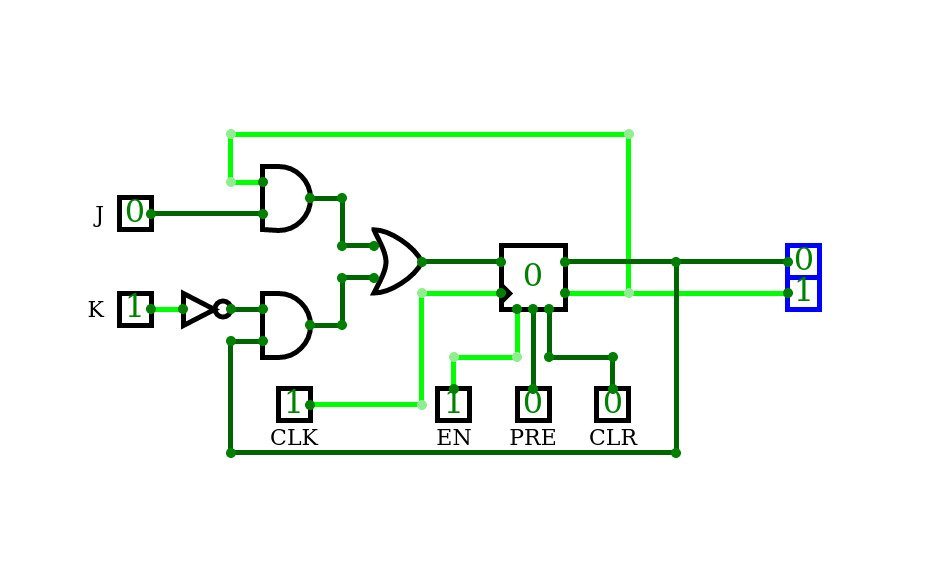

JK to D

JK to D

Public

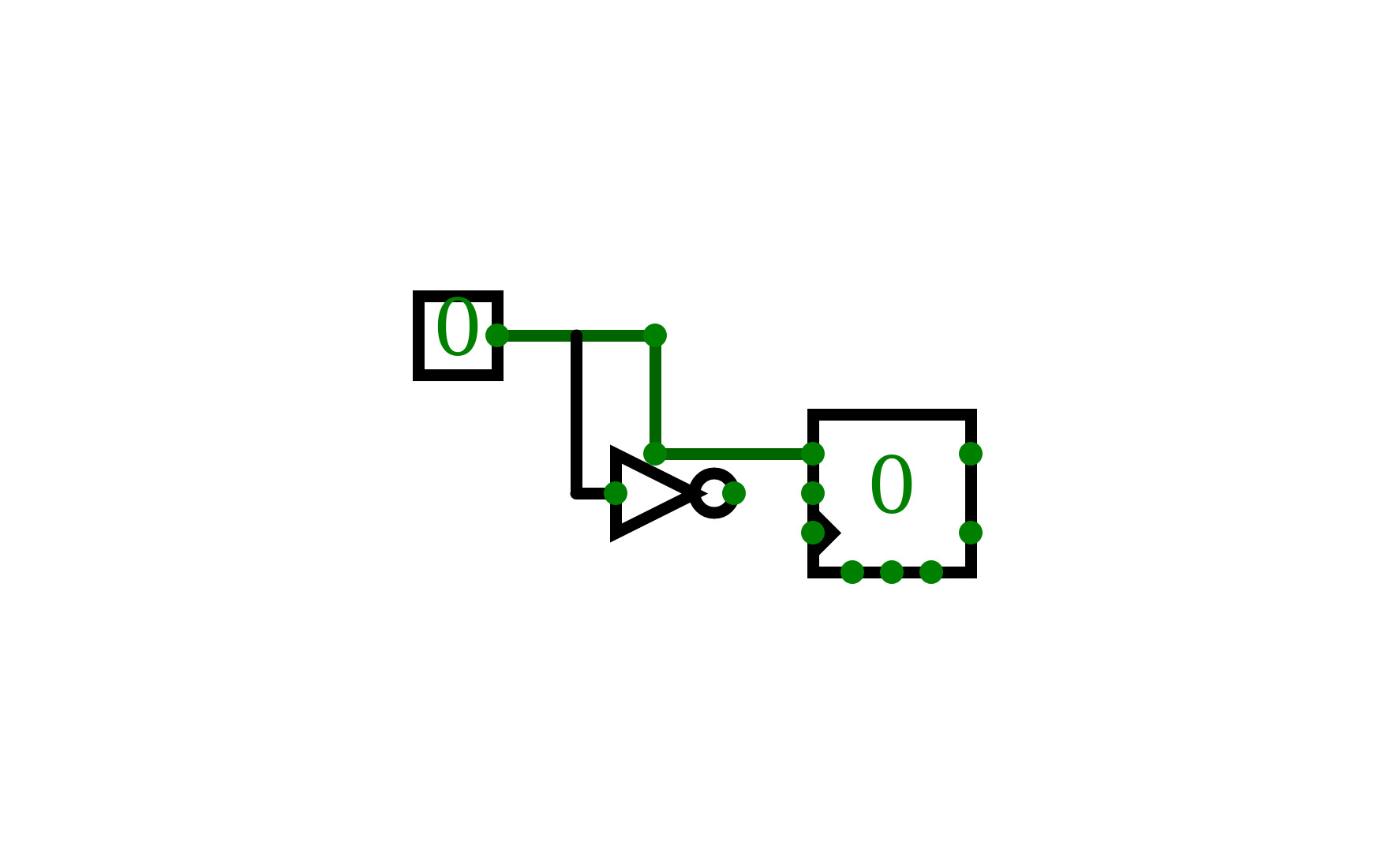

LSB reduction

LSB reduction

Public

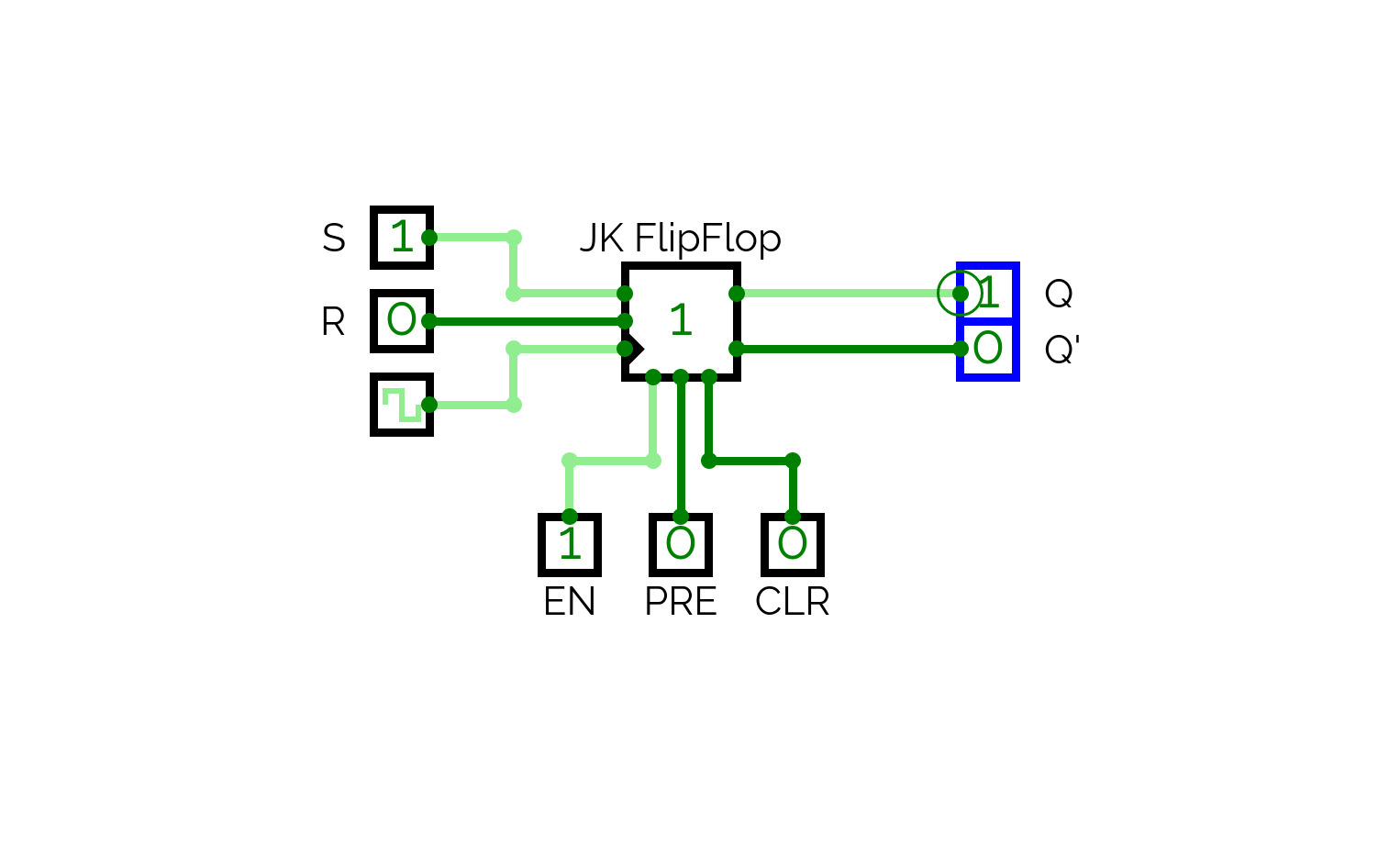

JK to SR

JK to SR

Public

Verification of D and T flipflop

Verification of D and T flipflop

Public

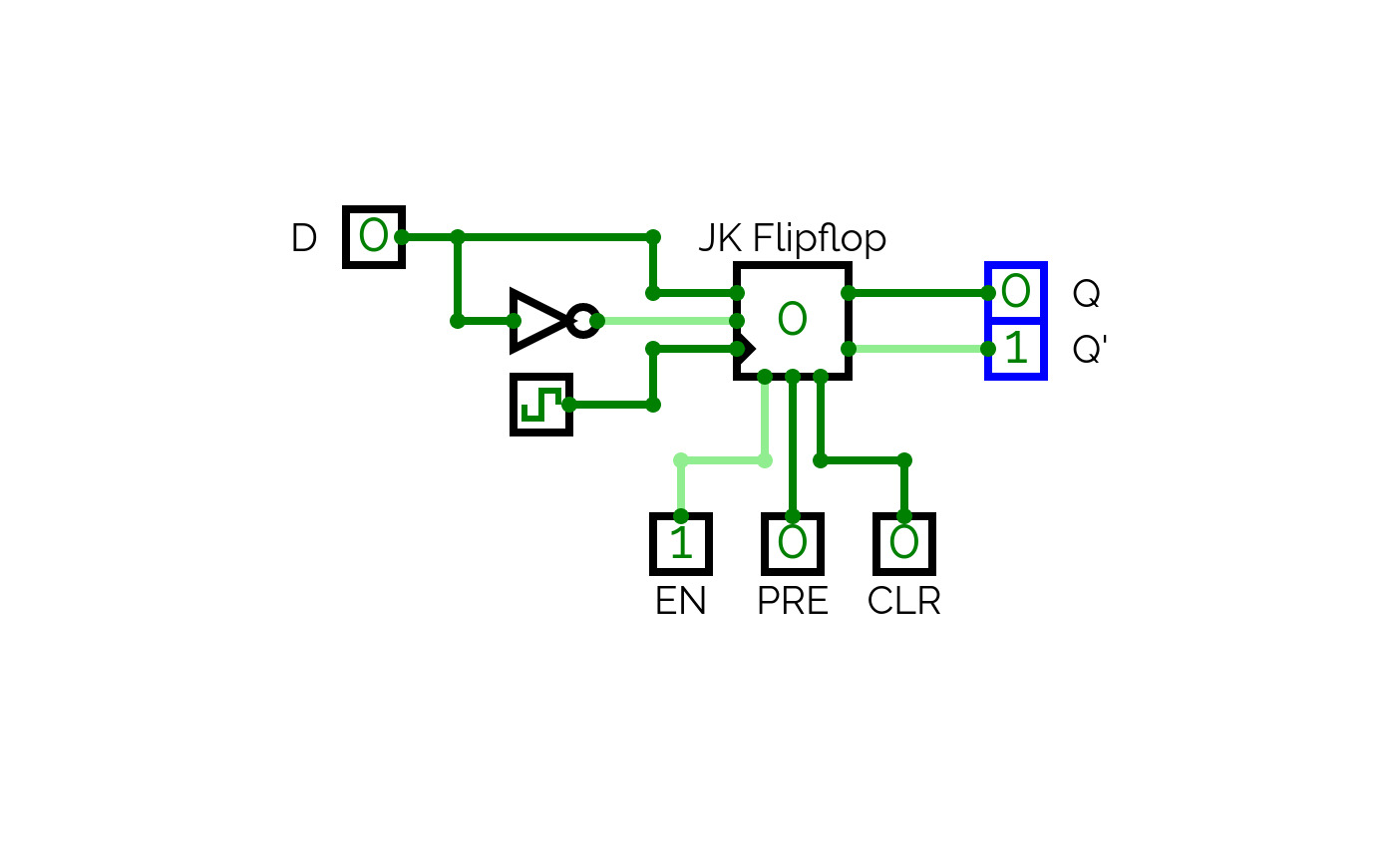

D to JK

D to JK

Public

T to JK

T to JK

Public

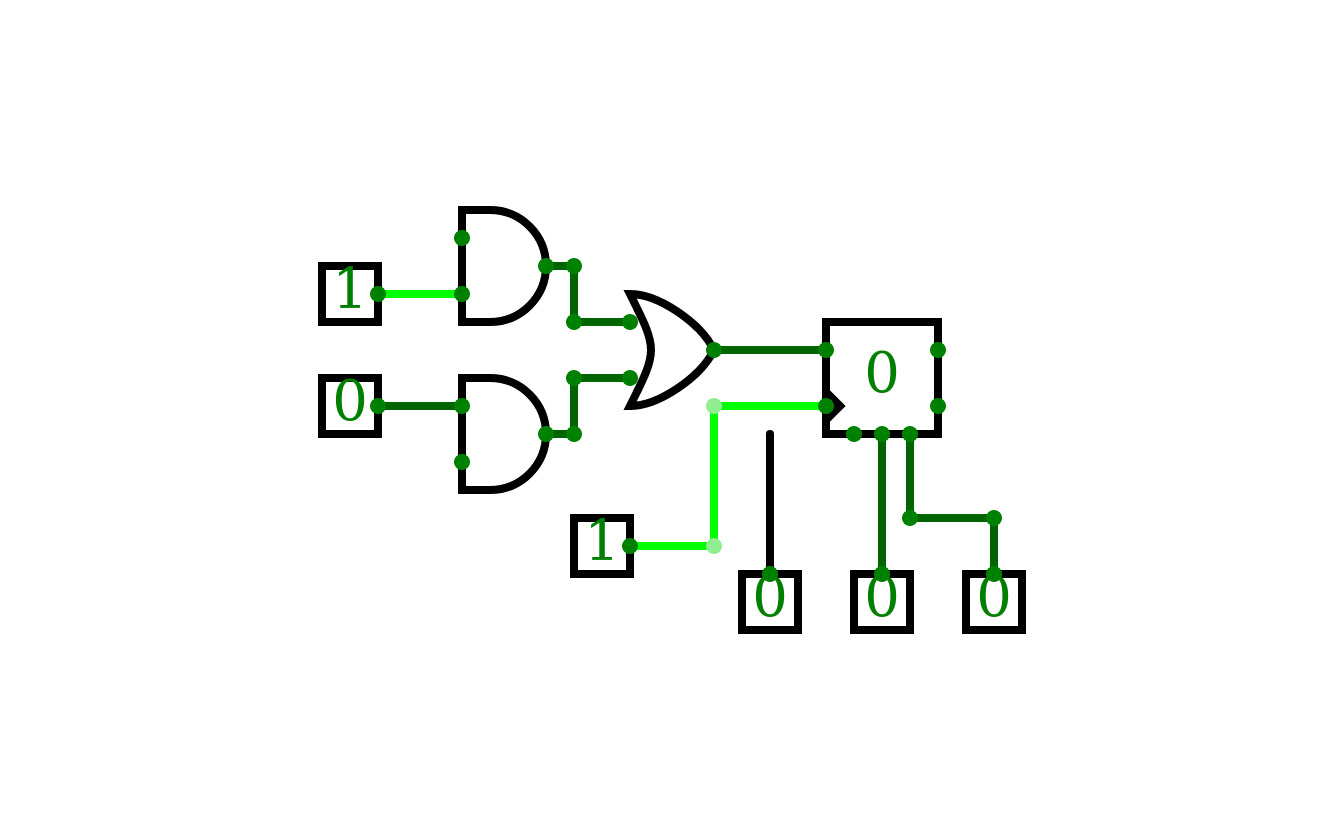

JK flipflop to D flipflop

JK flipflop to D flipflop

Public

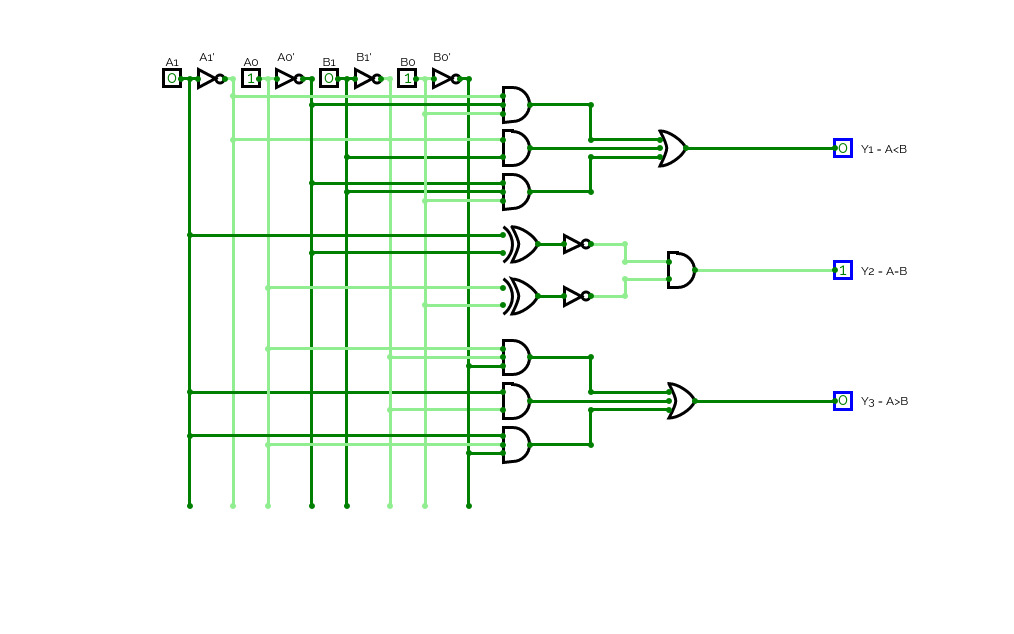

2 - bit digital comparator

2 - bit digital comparator

Public

Even and odd parity generator and checker

Even and odd parity generator and checker

Public

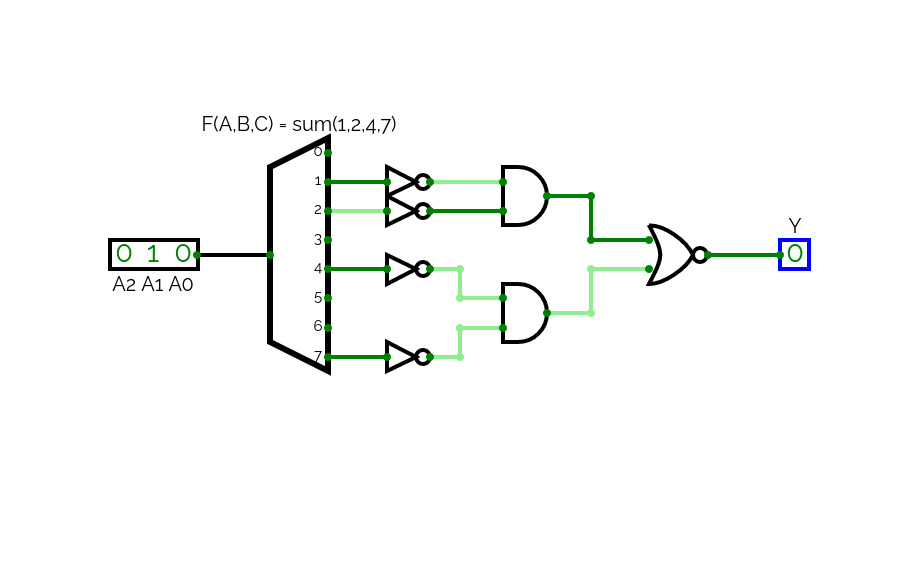

Boolean representation using decoder

Boolean representation using decoder

Public

Boolean expression representation

Boolean expression representation

Public

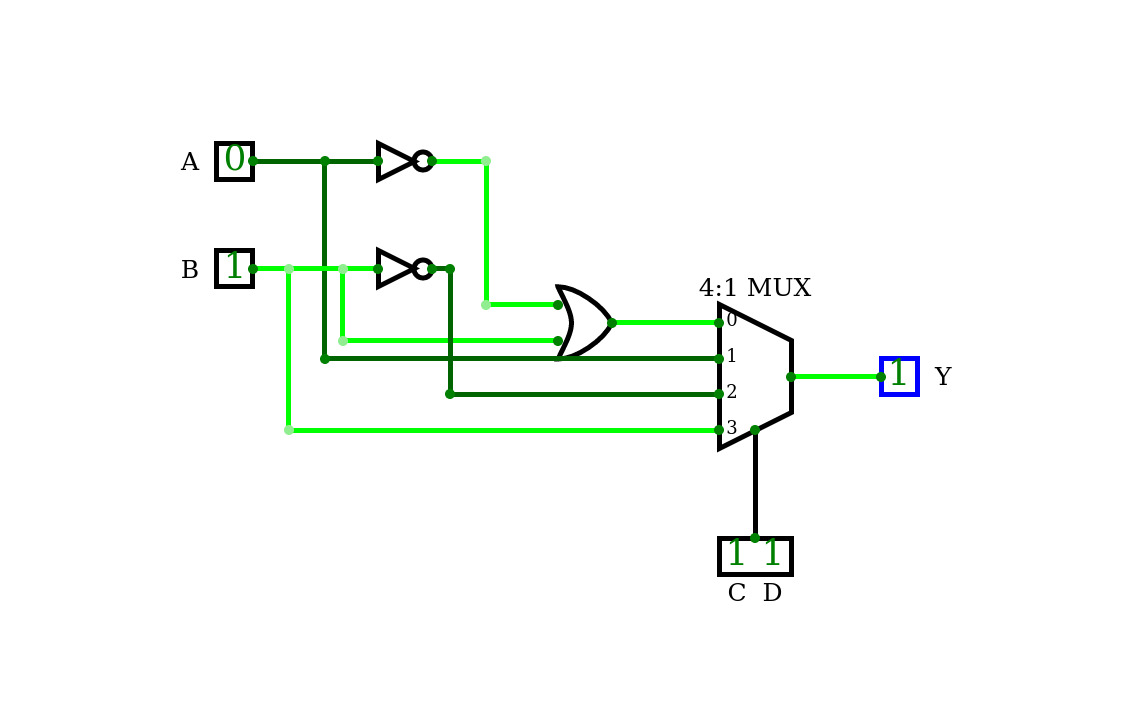

16:1 MUX using 8:1 MUX

16:1 MUX using 8:1 MUX

Public

Implementation of (0,2,4,7,9,10,12,13,15) using 8:1 LSB

Implementation of (0,2,4,7,9,10,12,13,15) using 8:1 LSB

Public

Untitled

Untitled

Public

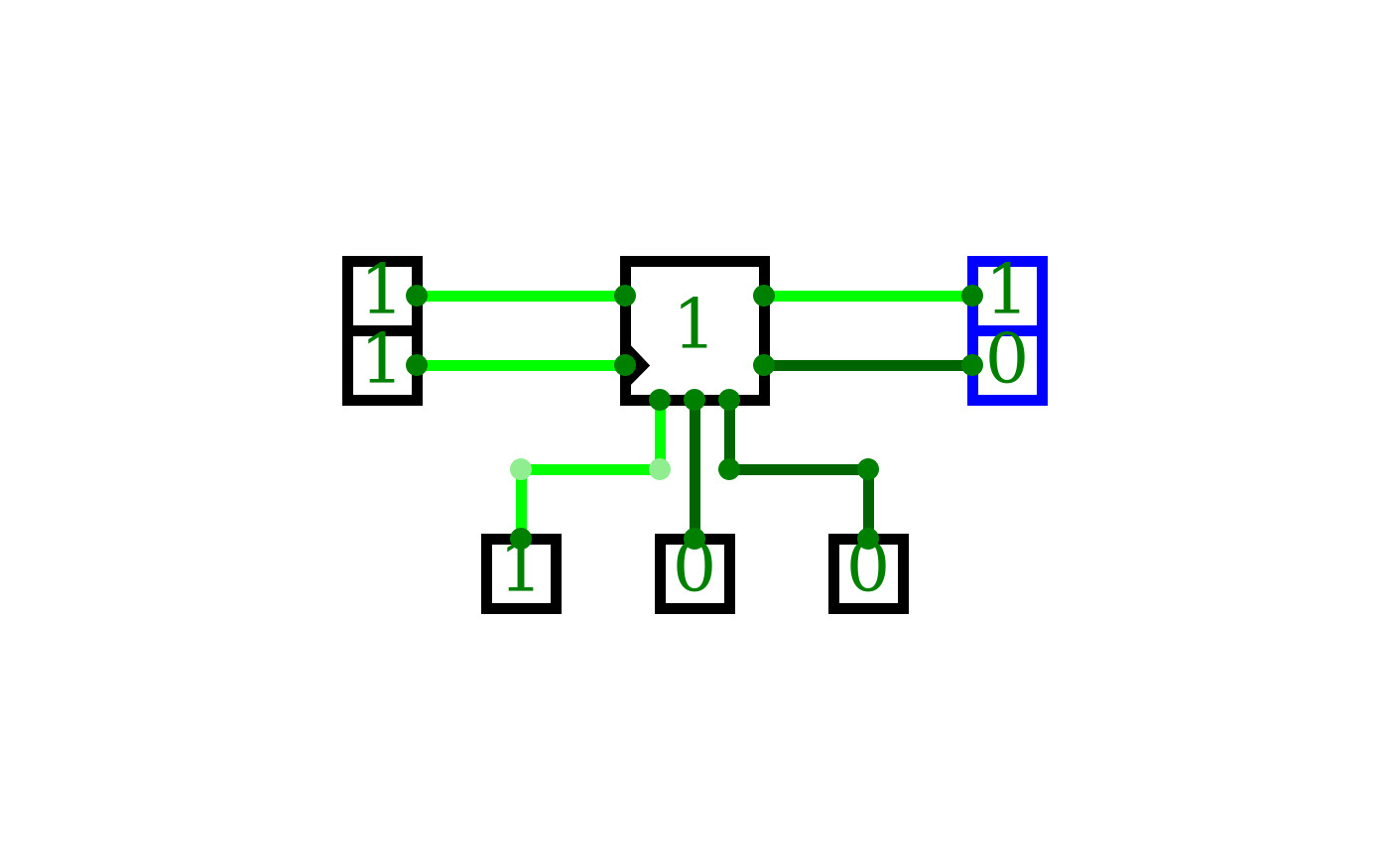

JK flipflop to T flipflop

JK flipflop to T flipflop

Public

Even and odd parity generator and checker

Even and odd parity generator and checker

Public