J.Angelene Vidhya

Member since: 4 years

Educational Institution: Not Entered

Country: Not Entered

Untitled

Untitled

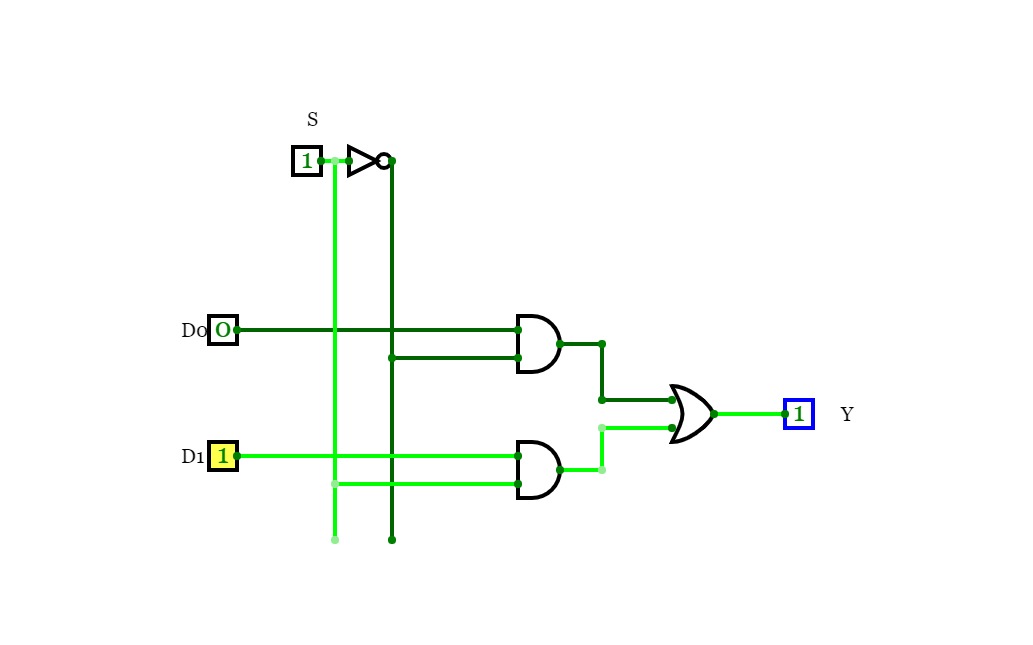

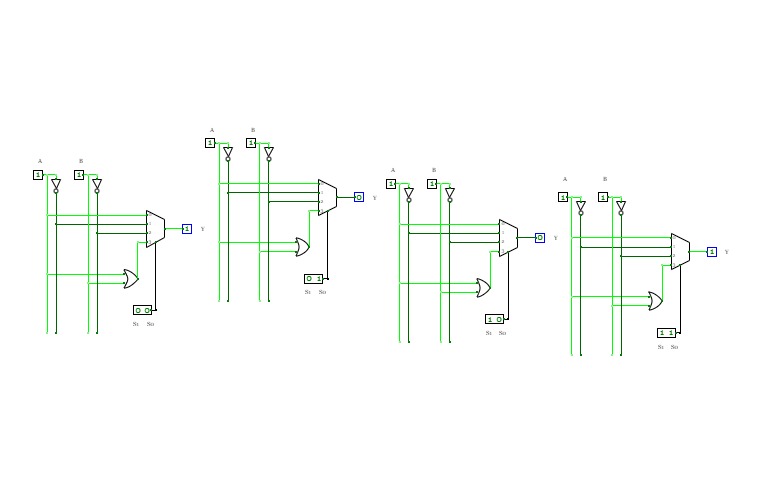

2 to 1 mux

2 to 1 mux

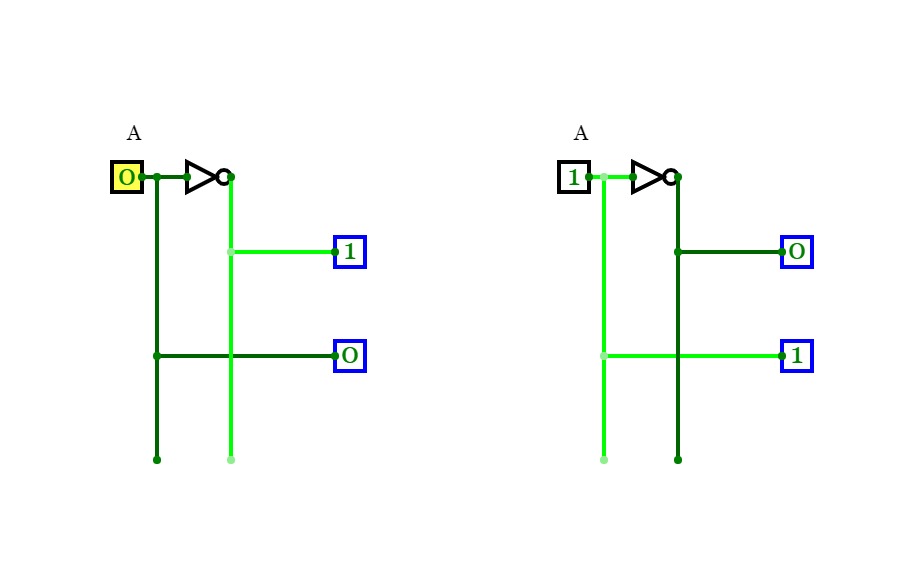

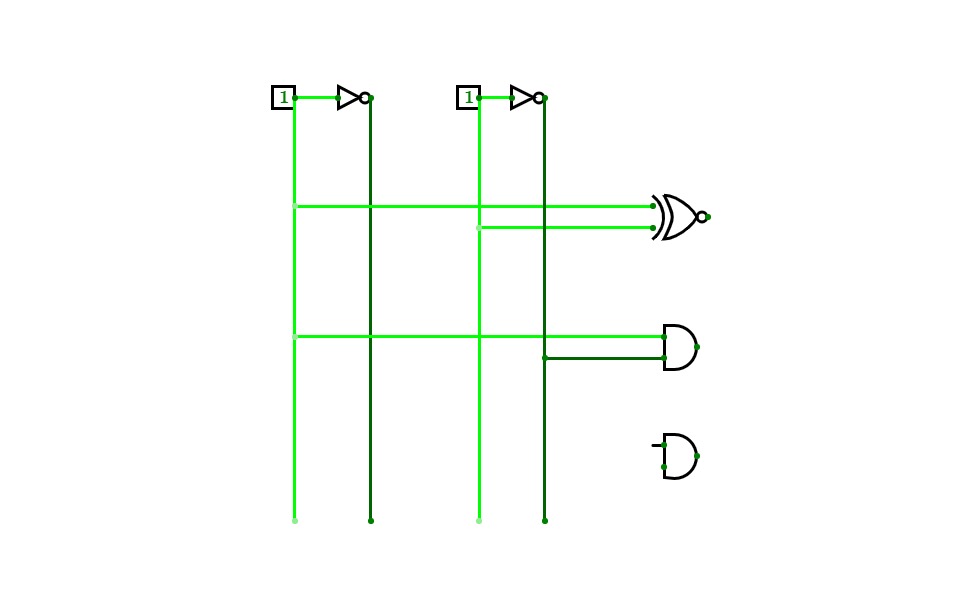

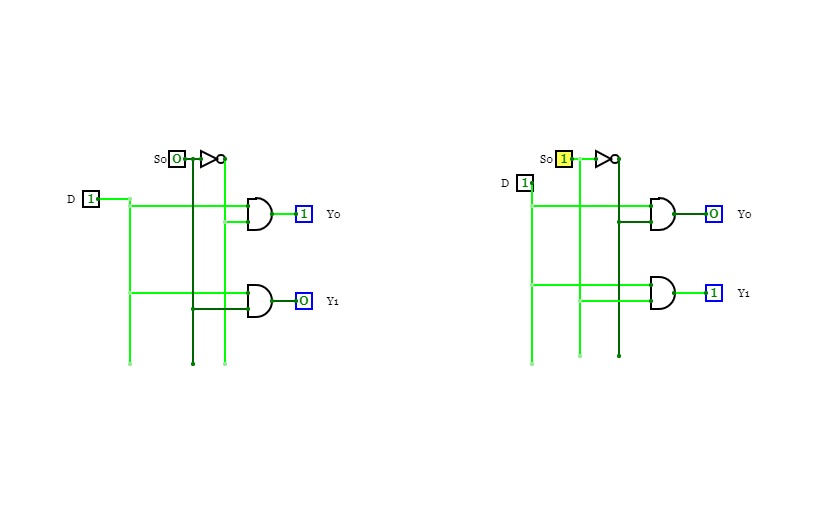

1 T0 2 DECODER

1 T0 2 DECODER

Untitled

Untitled

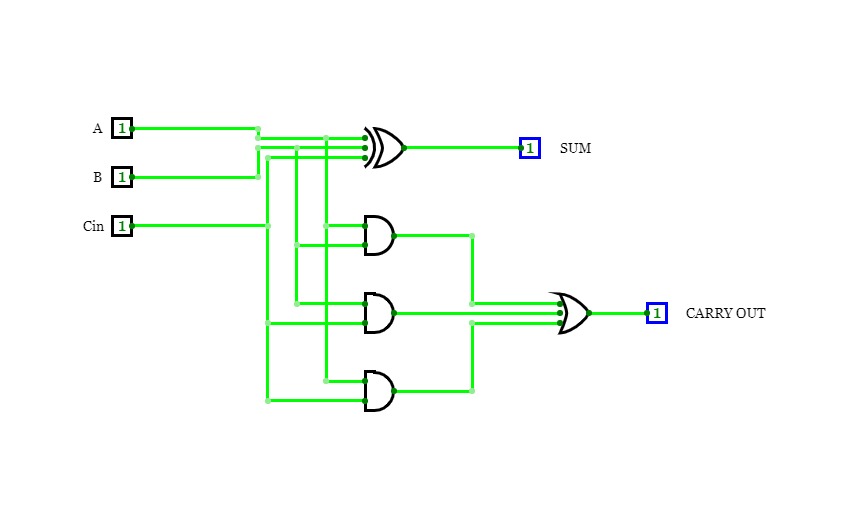

full adder

full adder

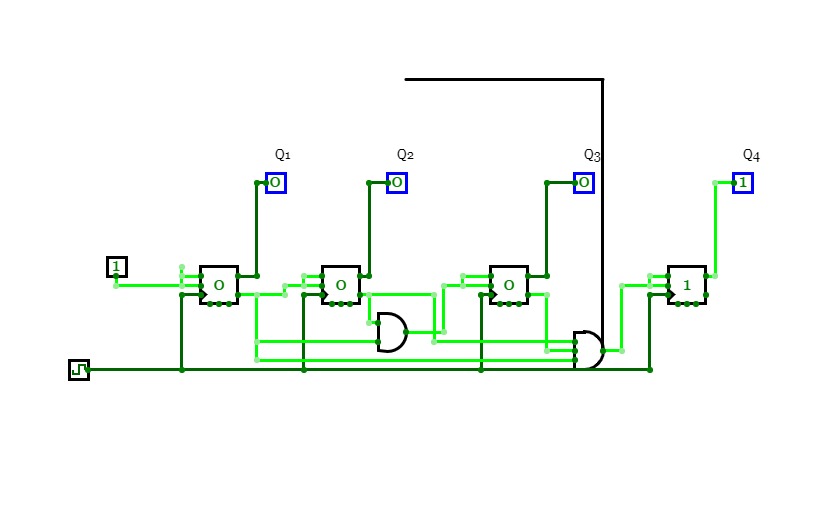

synchronous down counter

synchronous down counter

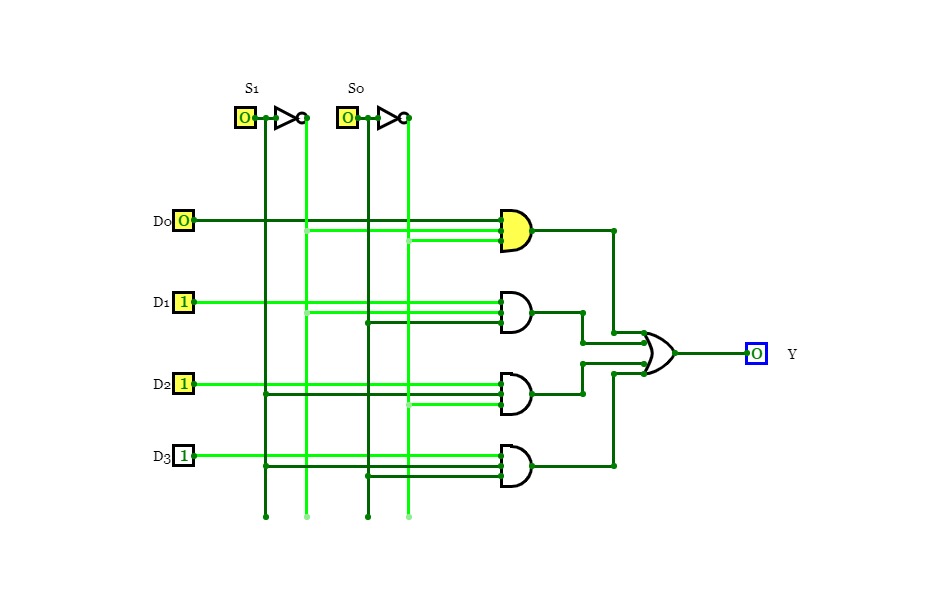

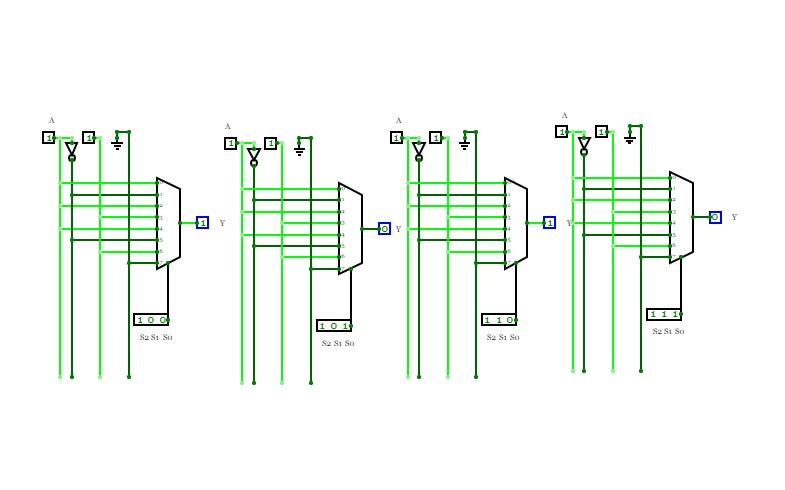

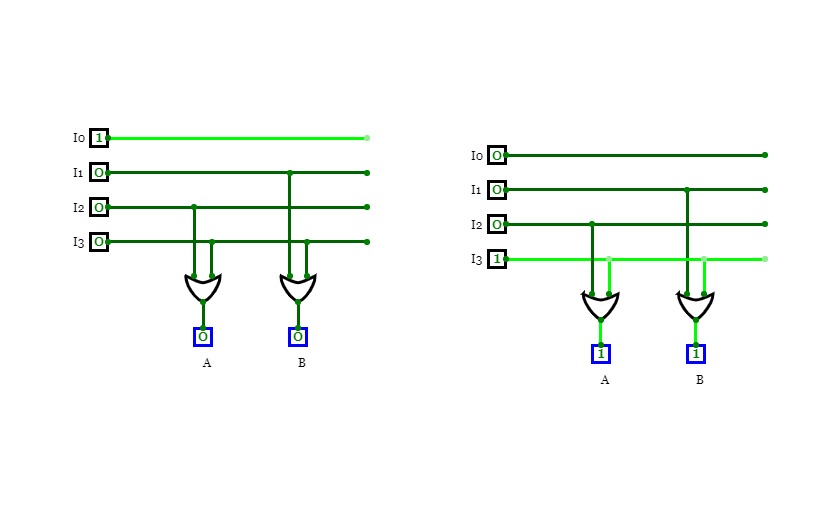

4 to 1 mux

4 to 1 mux

D FF USING T FLIP FLOP

D FF USING T FLIP FLOP

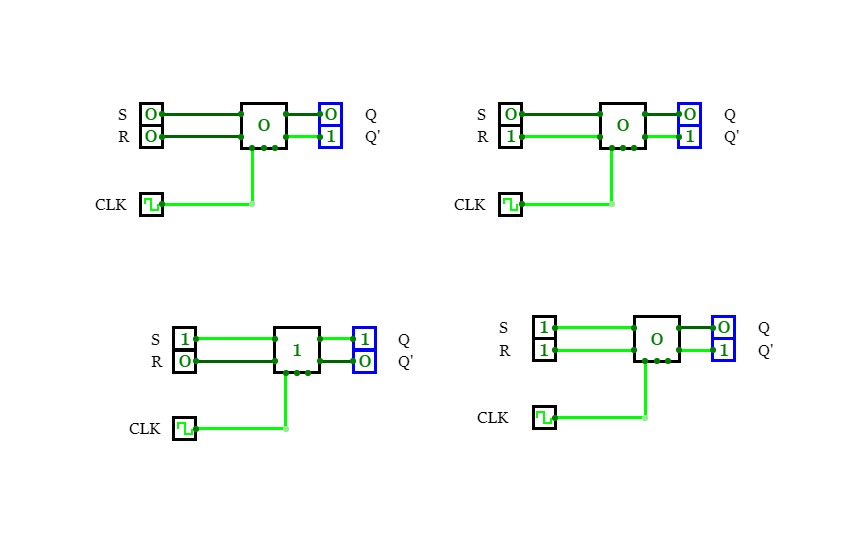

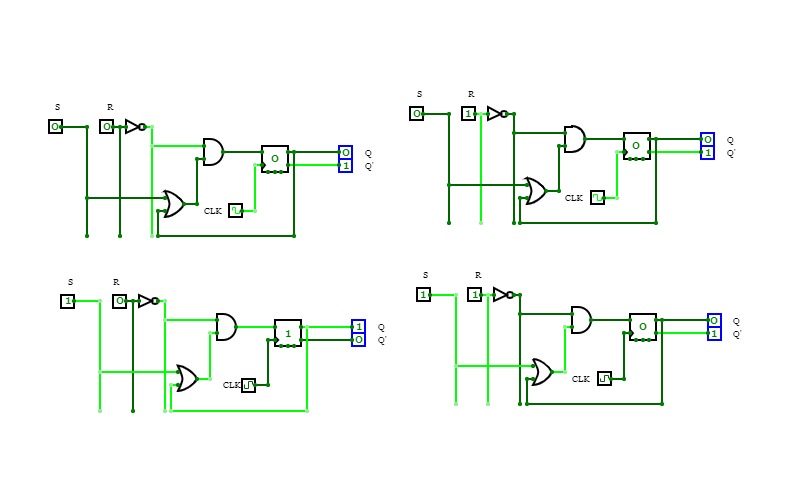

SR USING D FF

SR USING D FF

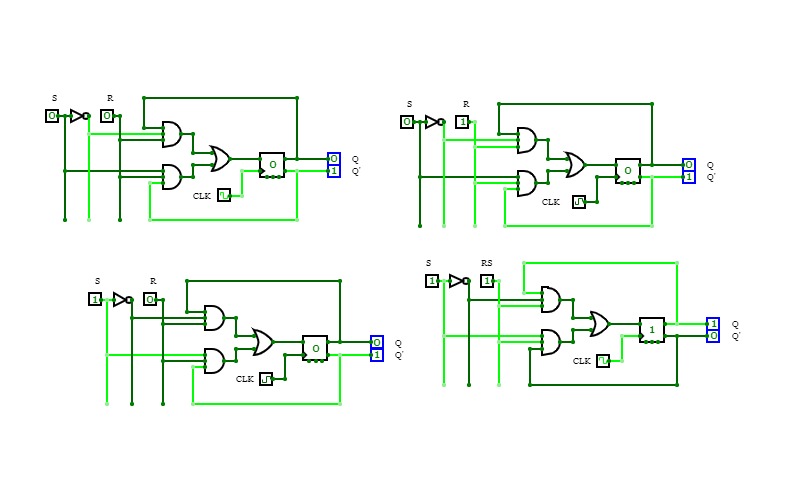

SR FF USING TFF

SR FF USING TFF

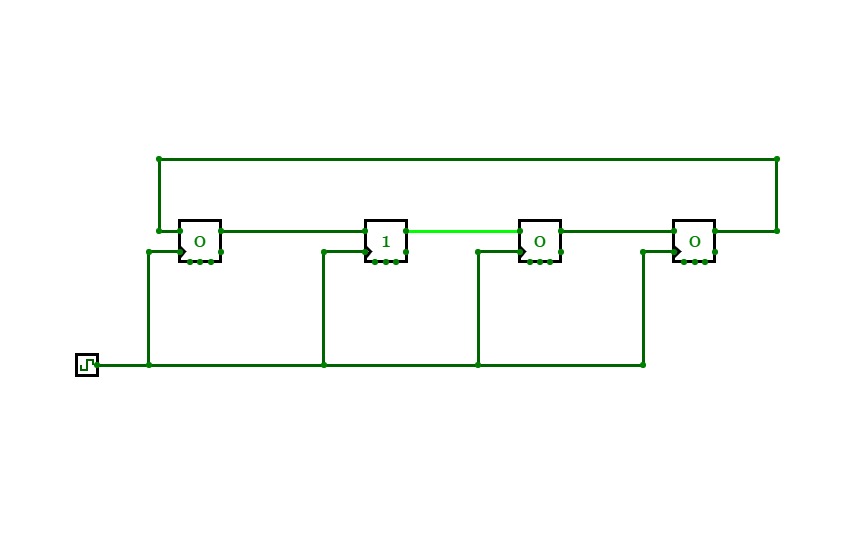

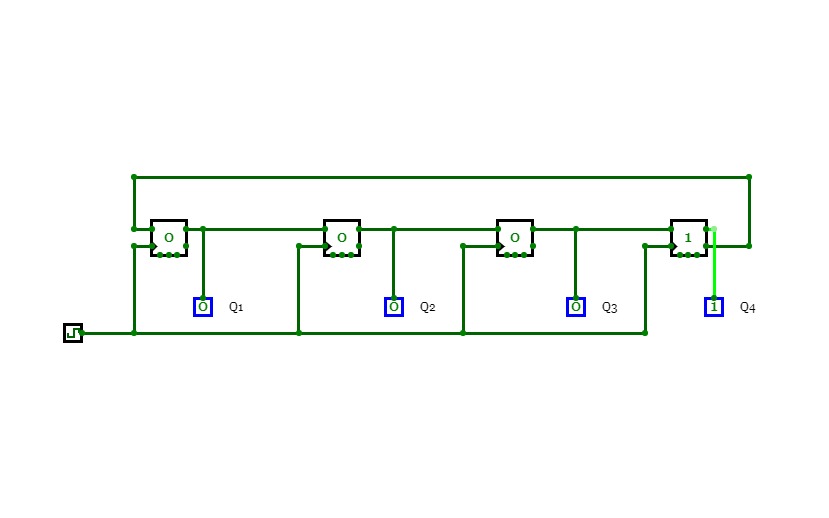

Asynchronous 4 bit ripple down counter

Asynchronous 4 bit ripple down counter

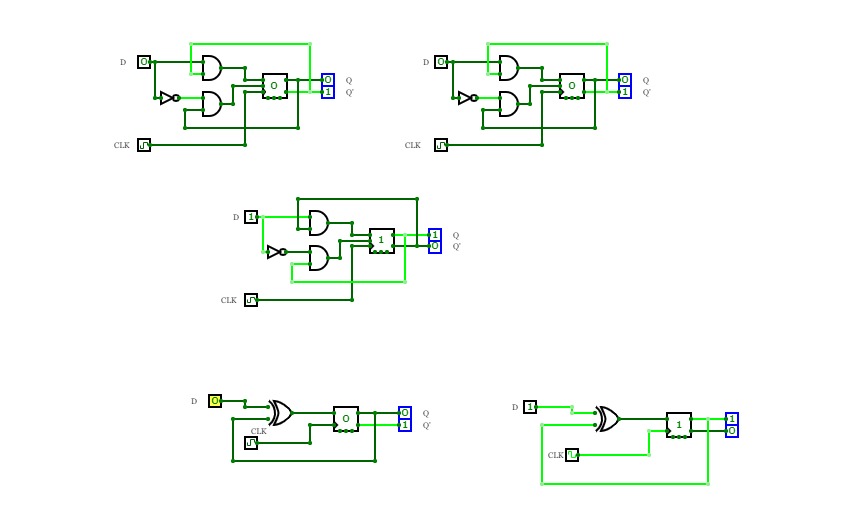

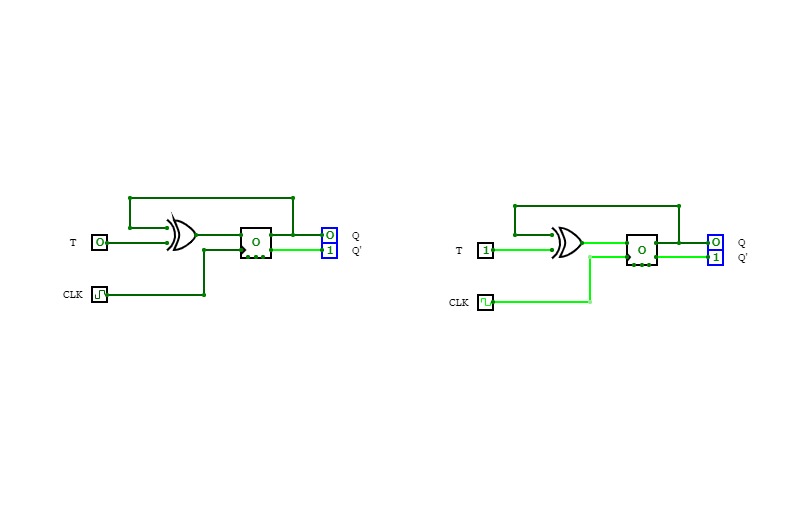

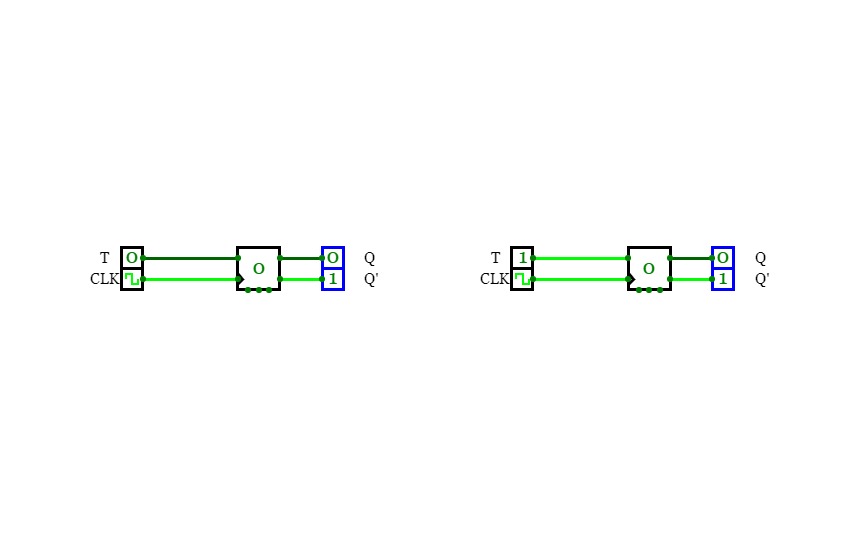

T FF USING D FF

T FF USING D FF

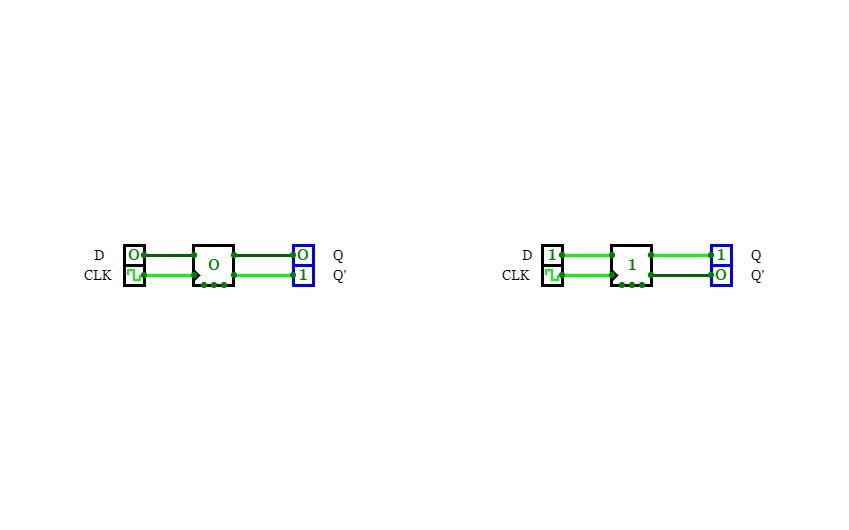

D FLIP FLOP USING INBUILT

D FLIP FLOP USING INBUILT

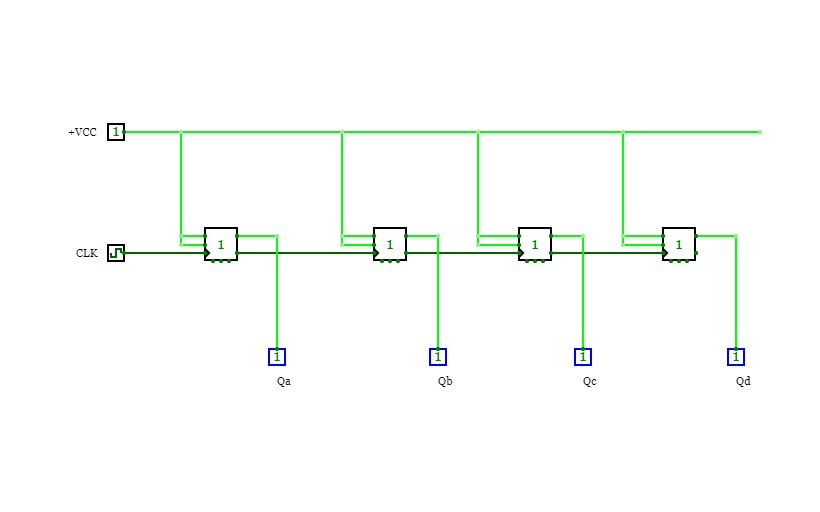

RING COUNTER

RING COUNTER

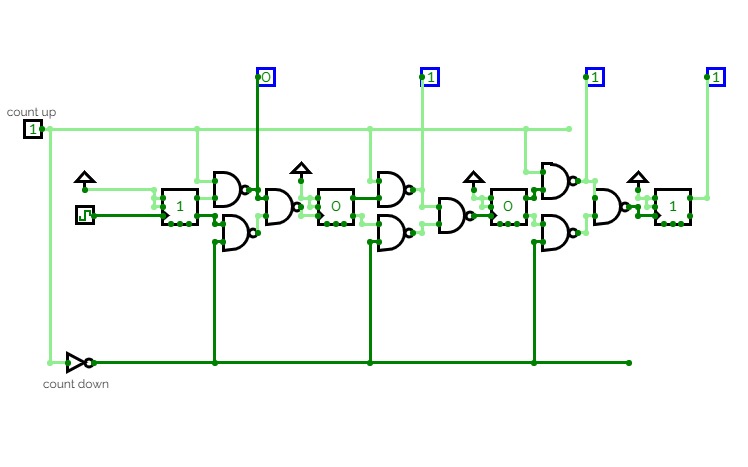

circuit that counts (0,2,4...14)when input is 1 and counts (1,3...15)when input is 0

circuit that counts (0,2,4...14)when input is 1 and counts (1,3...15)when input is 0

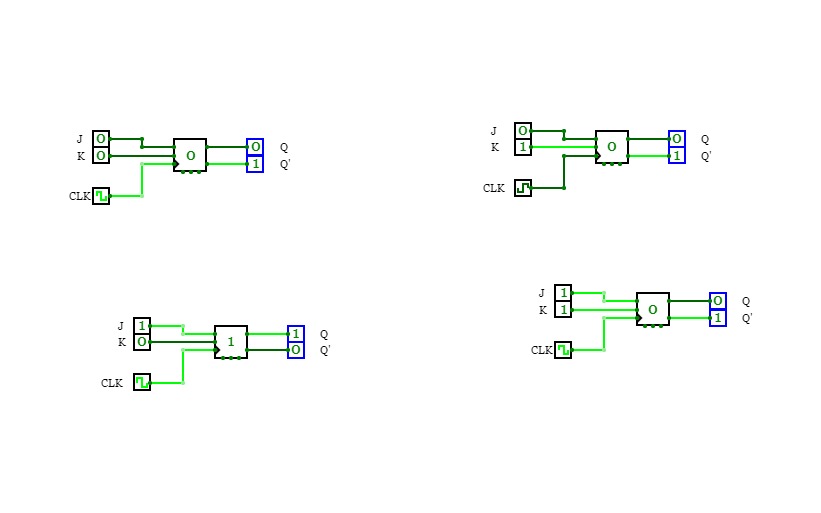

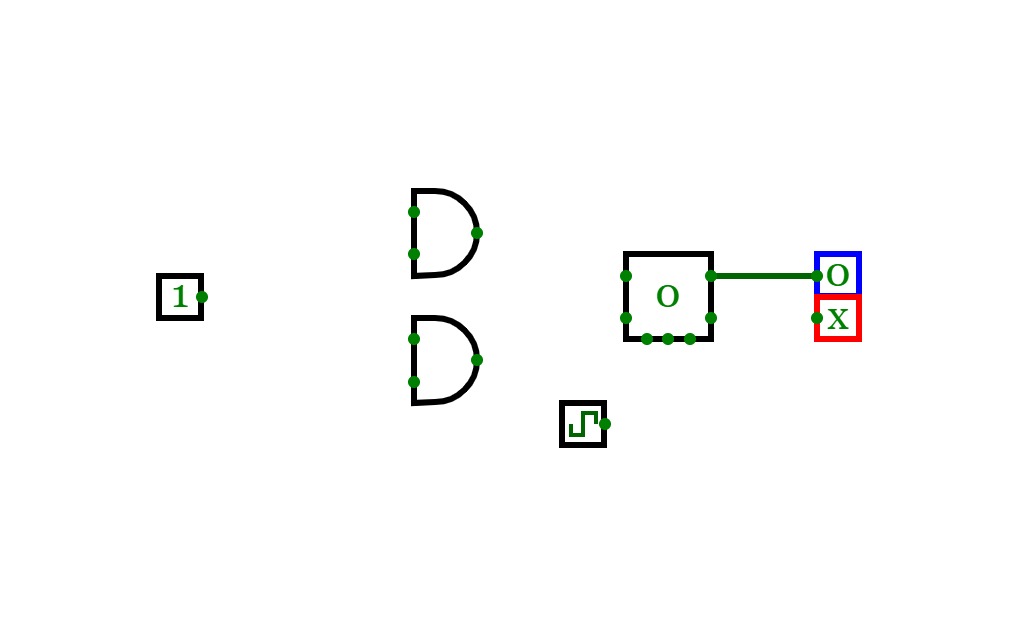

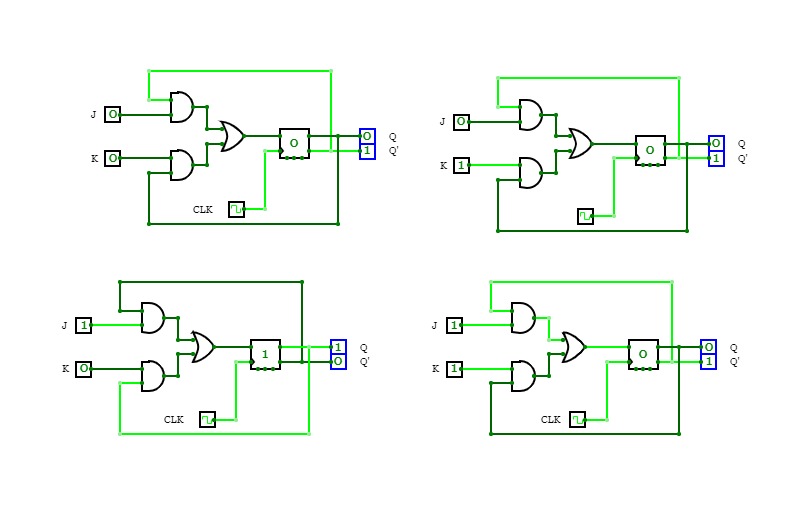

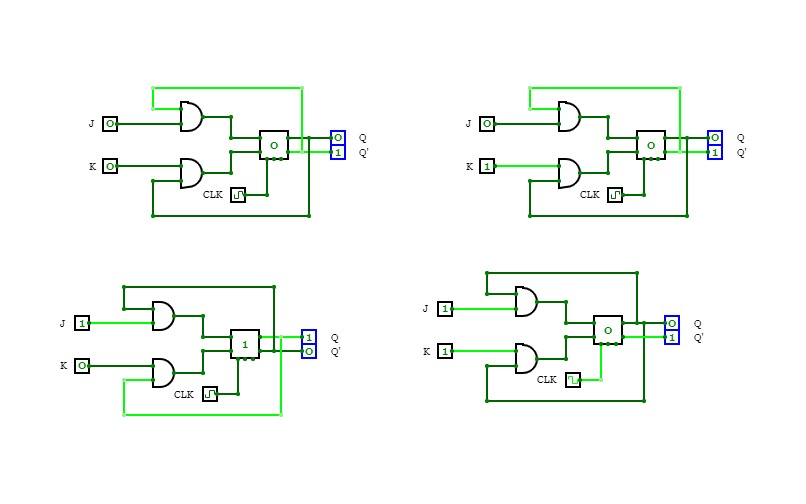

JK FLIP FLOP USING INBUILT

JK FLIP FLOP USING INBUILT

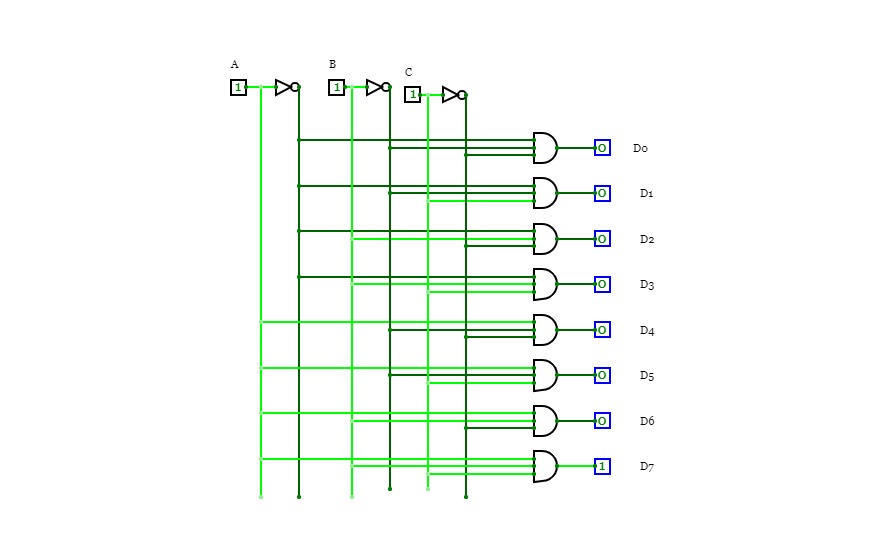

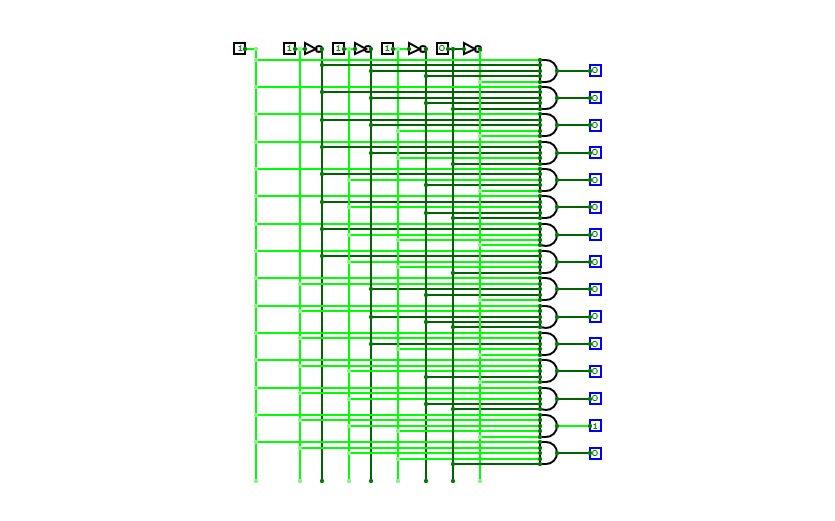

3 TO 8 DECODER

3 TO 8 DECODER

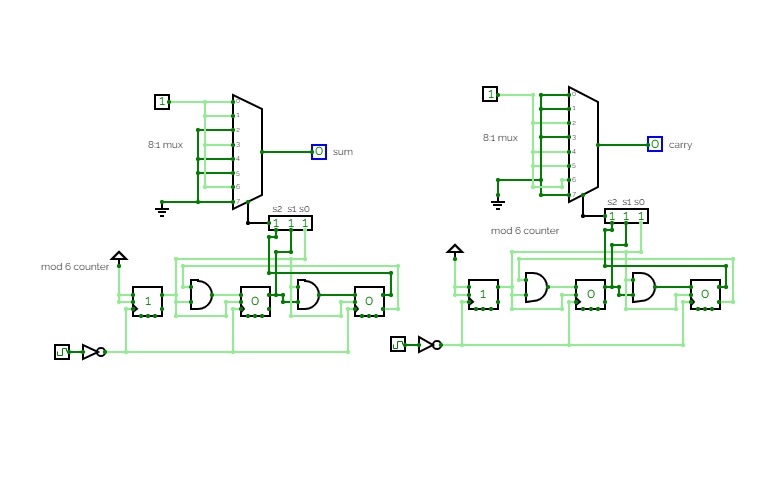

implementation of full adder with mux and counter

implementation of full adder with mux and counter

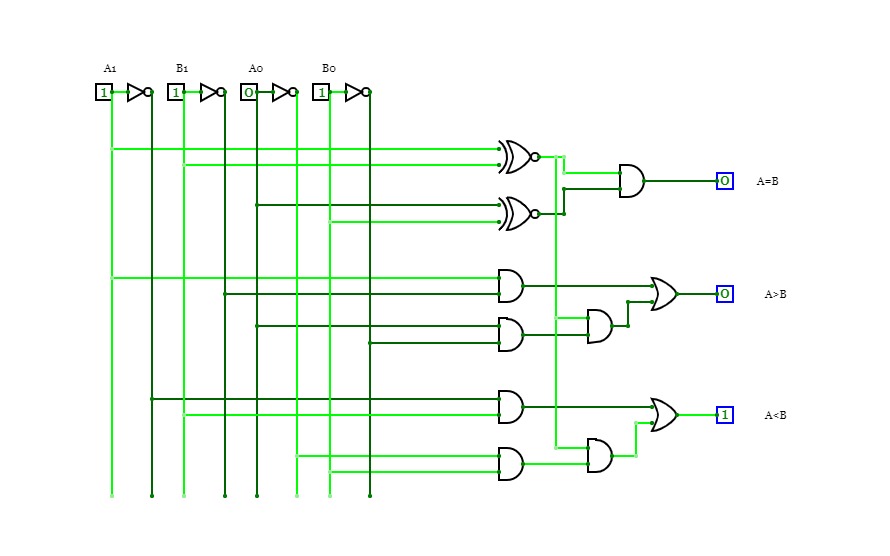

2 BIT MAGNITUDE COMPARATOR

2 BIT MAGNITUDE COMPARATOR

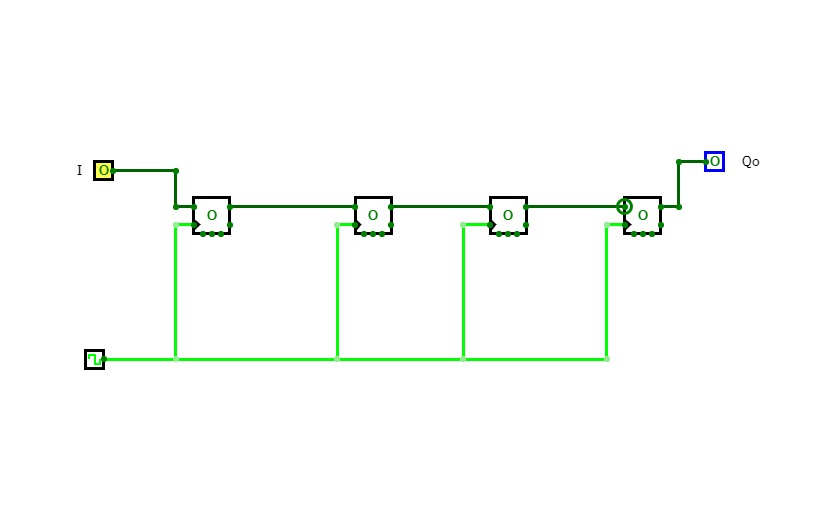

SERIAL IN SERIAL OUT

SERIAL IN SERIAL OUT

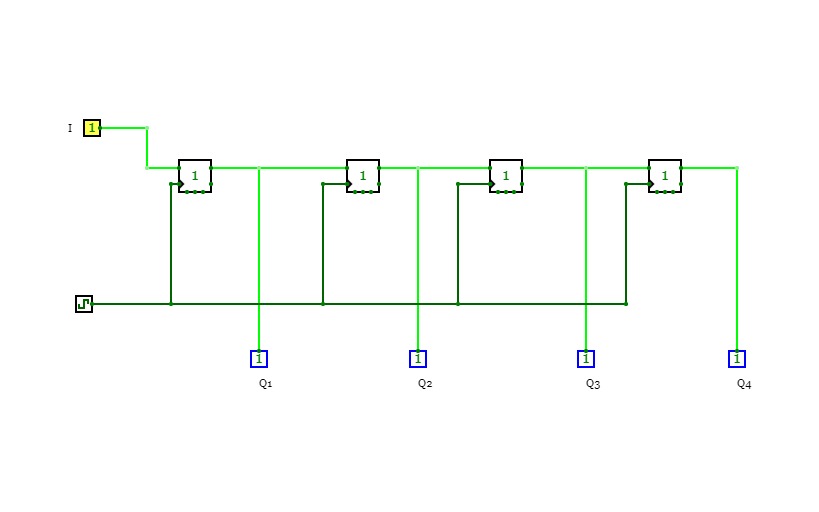

SERIAL IN PARALLEL OUT

SERIAL IN PARALLEL OUT

1 T0 8 DEMUX

1 T0 8 DEMUX

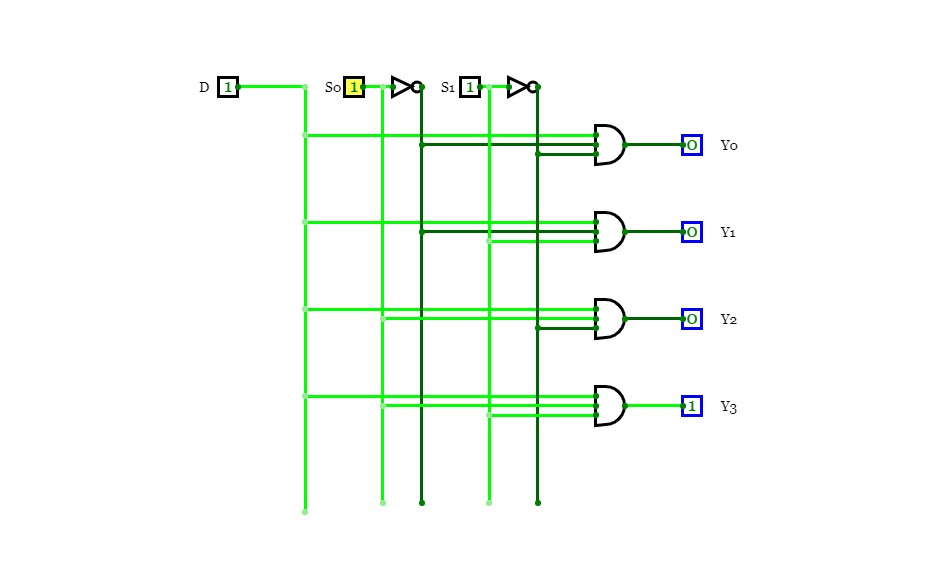

1 T0 4 DEMUX

1 T0 4 DEMUX

2 TO 1 ENCODER

2 TO 1 ENCODER

FUL

FUL

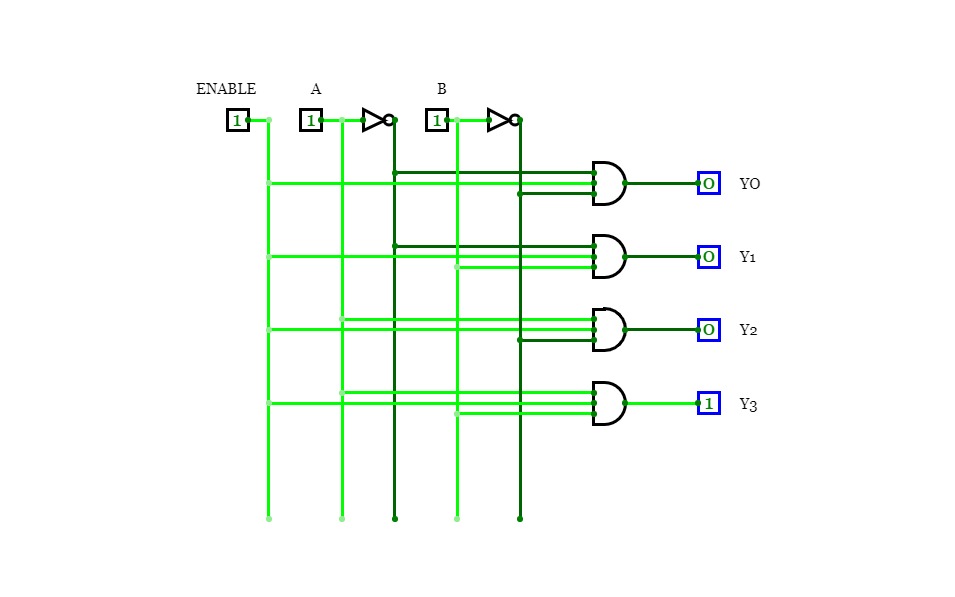

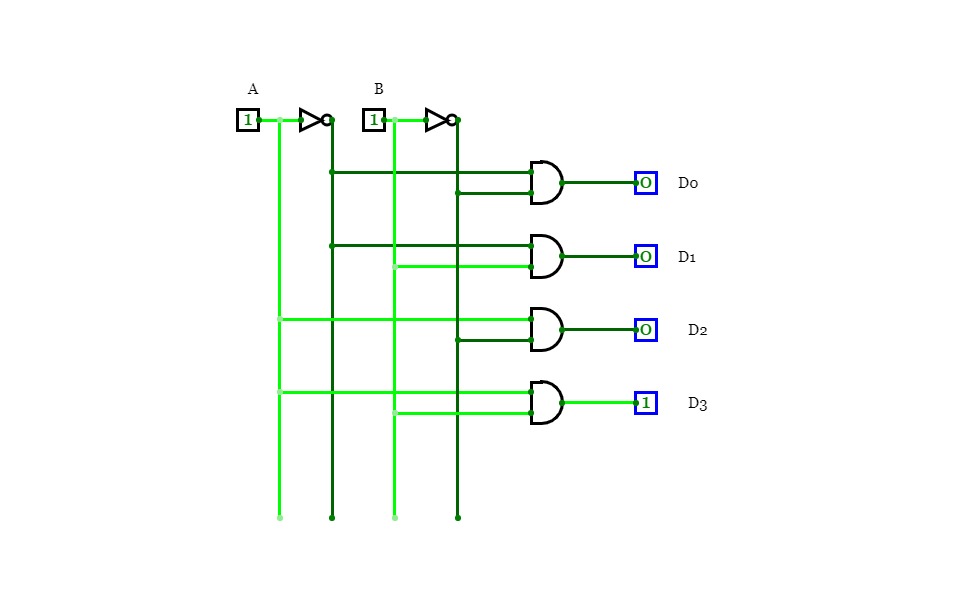

2 T0 4 DECODER

2 T0 4 DECODER

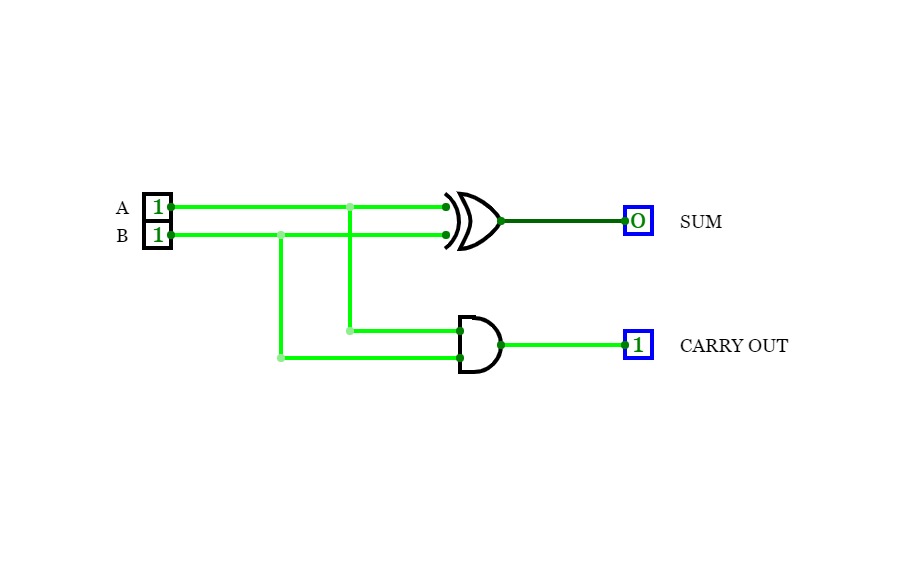

HALF ADDER

HALF ADDER

EXNOR gate

EXNOR gate

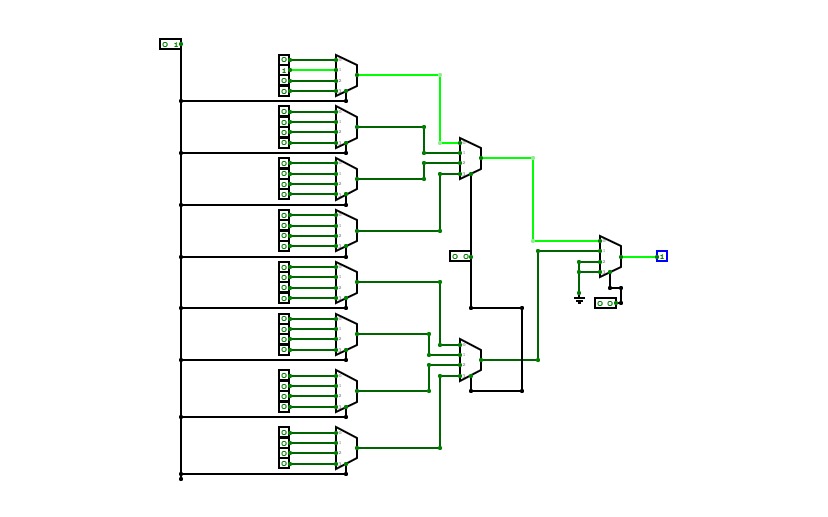

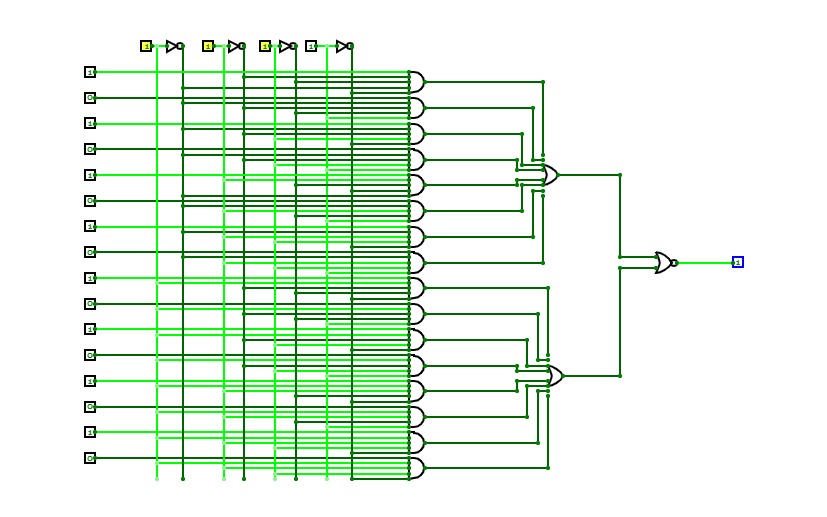

32 to 1 mux using 4 to1 mux

32 to 1 mux using 4 to1 mux

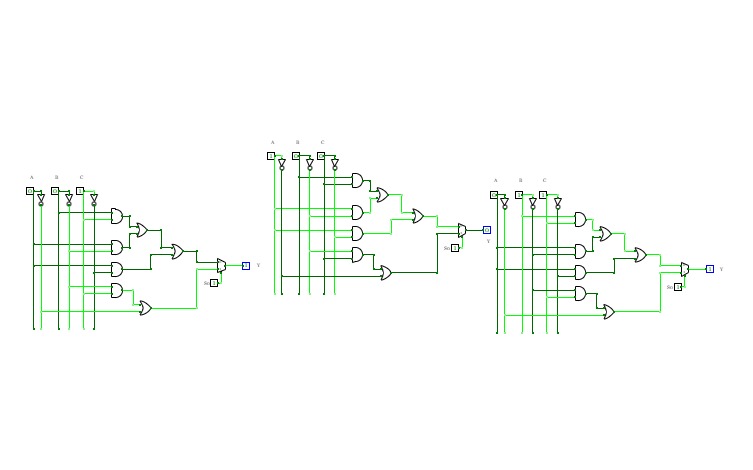

implementation using 2 to 1

implementation using 2 to 1

implementation using 2 to 1 mux

implementation using 2 to 1 mux

IMPLEMENTATION USING 4 TO 1

IMPLEMENTATION USING 4 TO 1

IMPLEMENTATION USING 8 TO1

IMPLEMENTATION USING 8 TO1

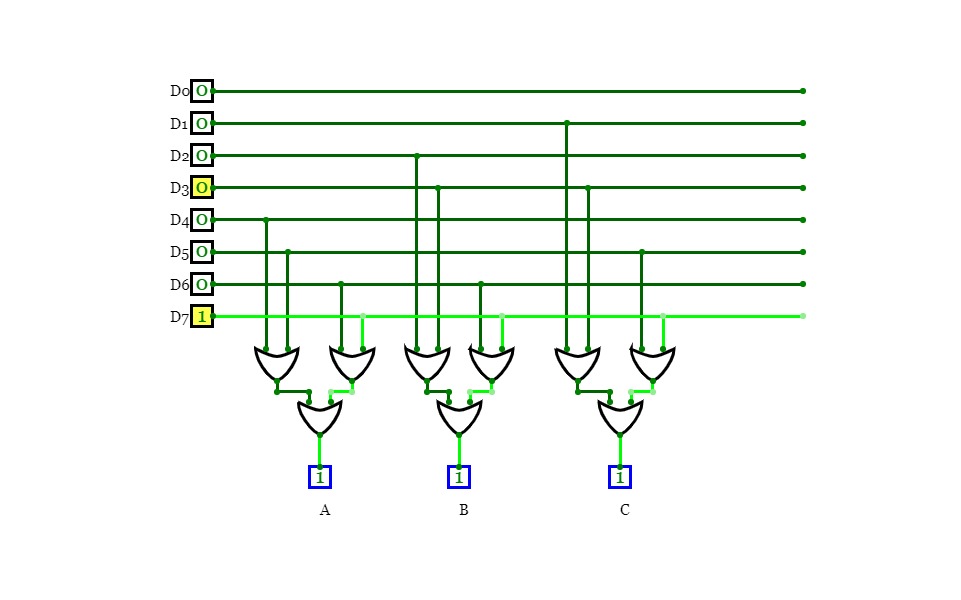

8 TO 3 OCTAL TO BINARY ENCODER

8 TO 3 OCTAL TO BINARY ENCODER

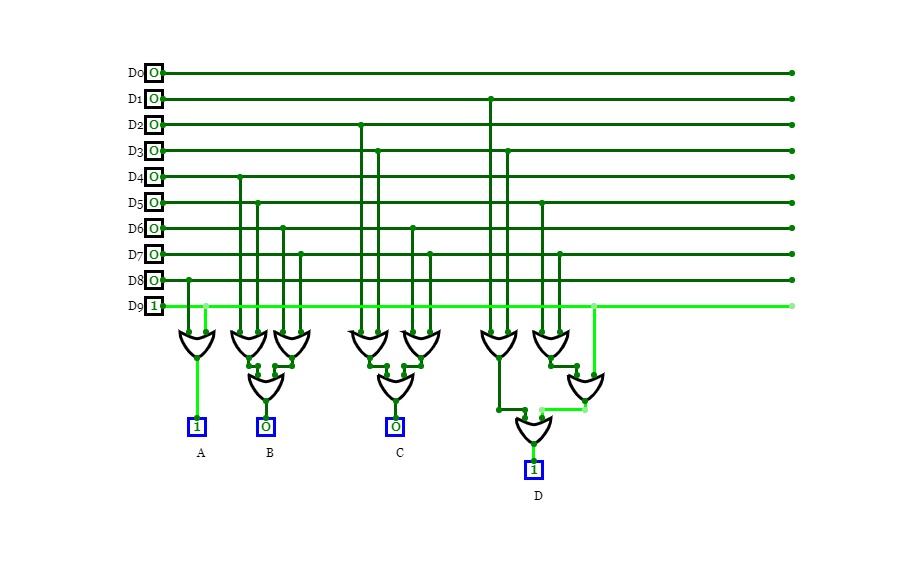

DECIMAL TO BCD ENCODER

DECIMAL TO BCD ENCODER

4TO 2 ENCODER

4TO 2 ENCODER

SHIFT COUNTER

SHIFT COUNTER

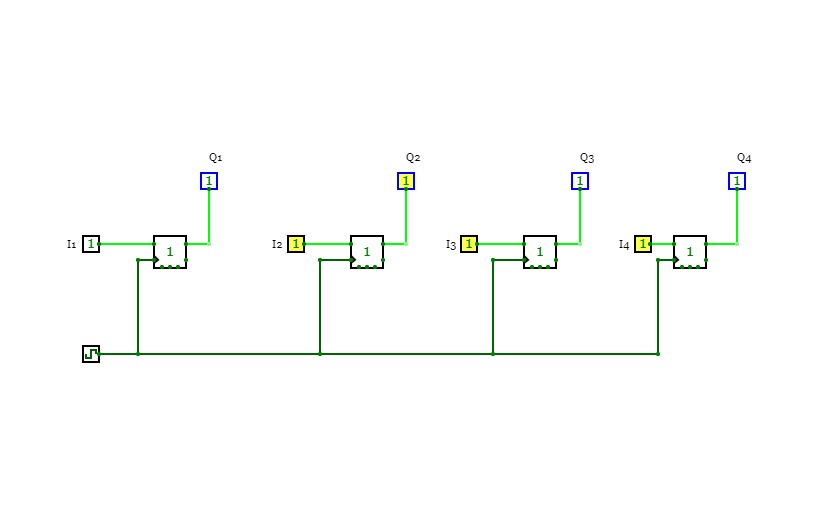

parrallel in parallel out

parrallel in parallel out

T FF USING SR FF

T FF USING SR FF

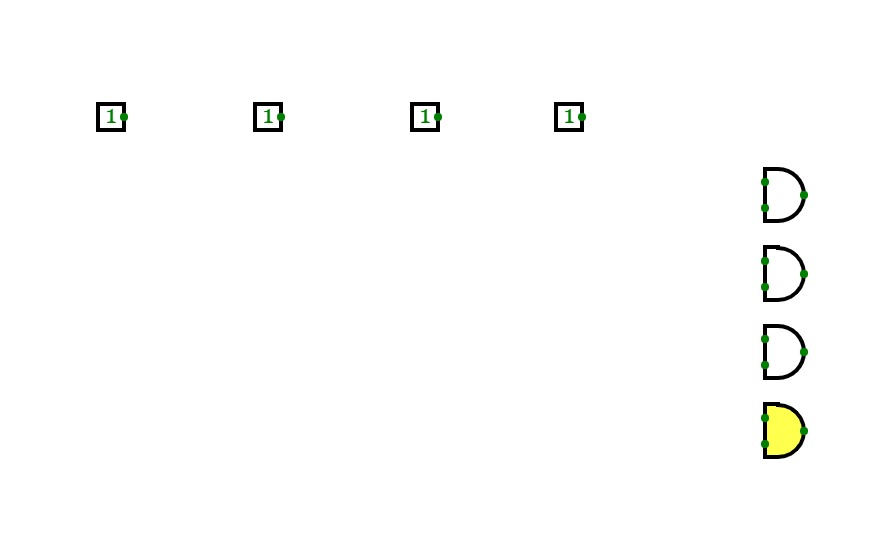

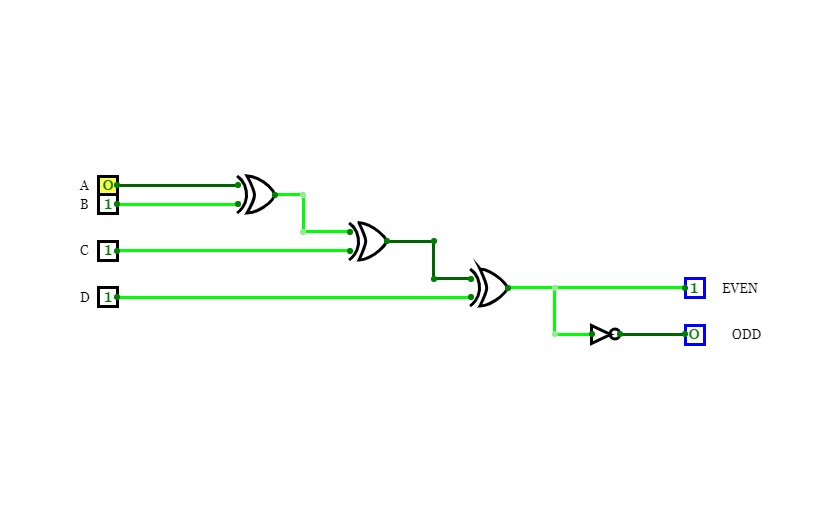

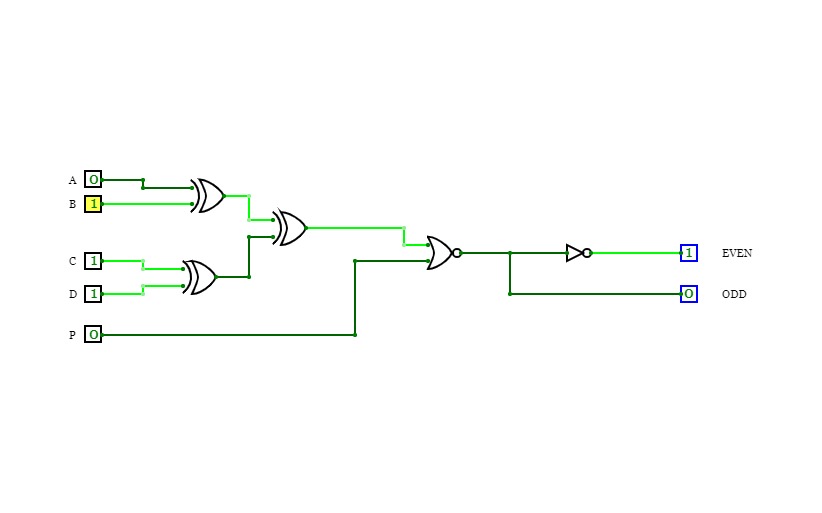

4 BIT PARITY GENERATOR

4 BIT PARITY GENERATOR

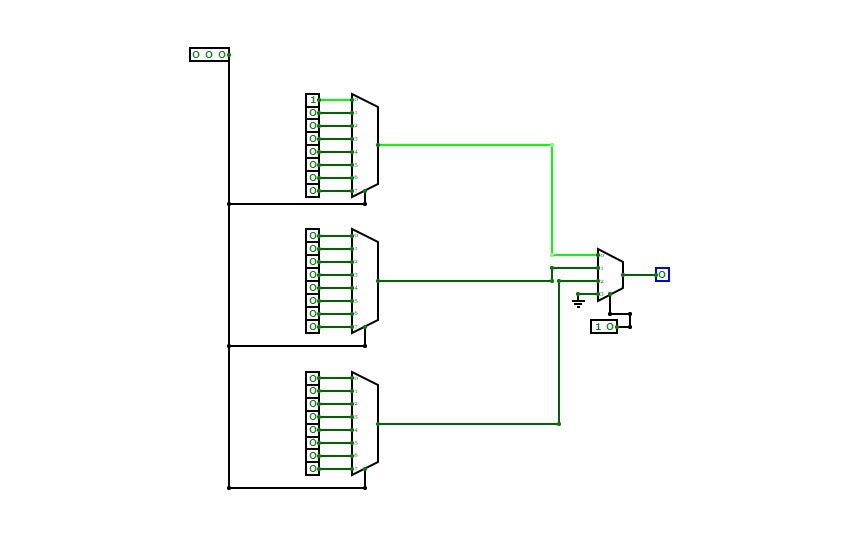

24 to1 using 8to 1 mux

24 to1 using 8to 1 mux

1 TO 16 DEMUX

1 TO 16 DEMUX

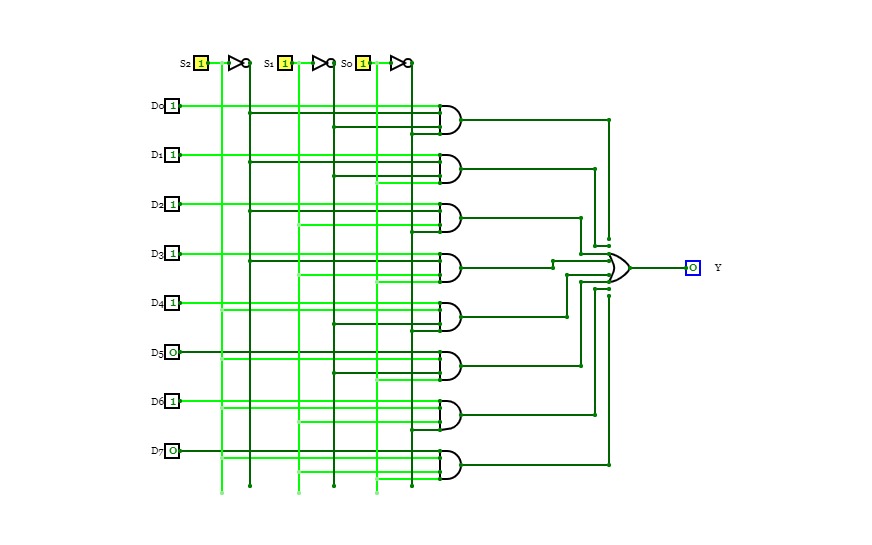

8to1mux

8to1mux

BIDERECTIONALSHIFT REGISTER

BIDERECTIONALSHIFT REGISTER

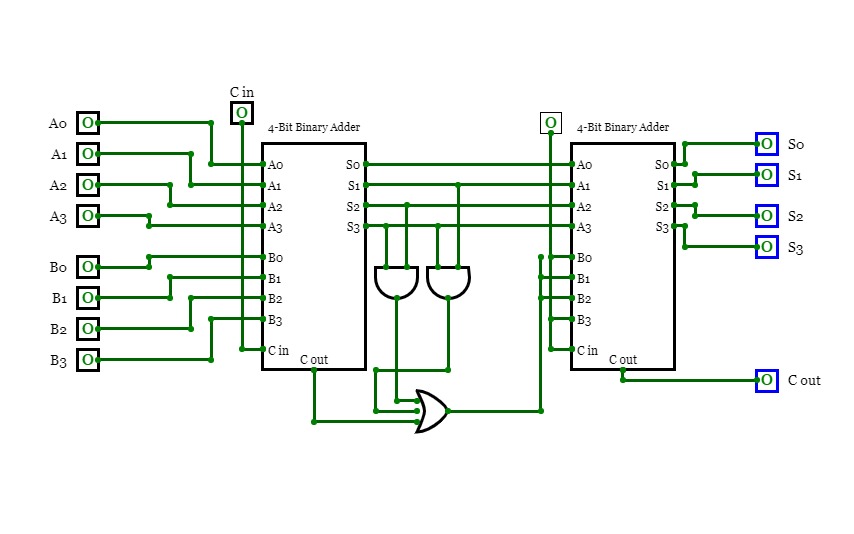

BCD ADDER

BCD ADDER

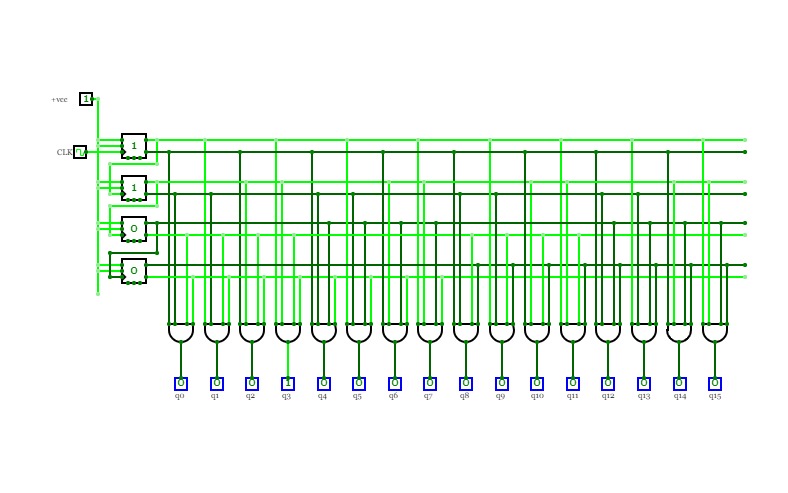

asynchronous 4 bit ripple counter with decoded output

asynchronous 4 bit ripple counter with decoded output

SR FF USING JK FF

SR FF USING JK FF

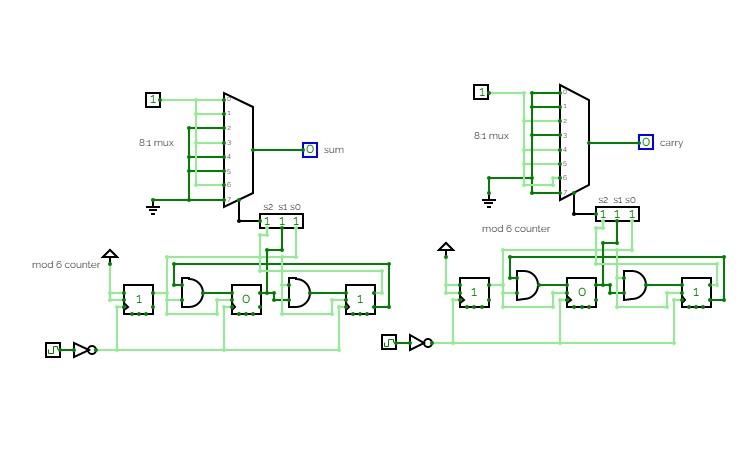

implementation of full adder with mux and counter

implementation of full adder with mux and counter

T FLIP FLOP USING INBUILT

T FLIP FLOP USING INBUILT

implementation using 2 to 1 mux

implementation using 2 to 1 mux

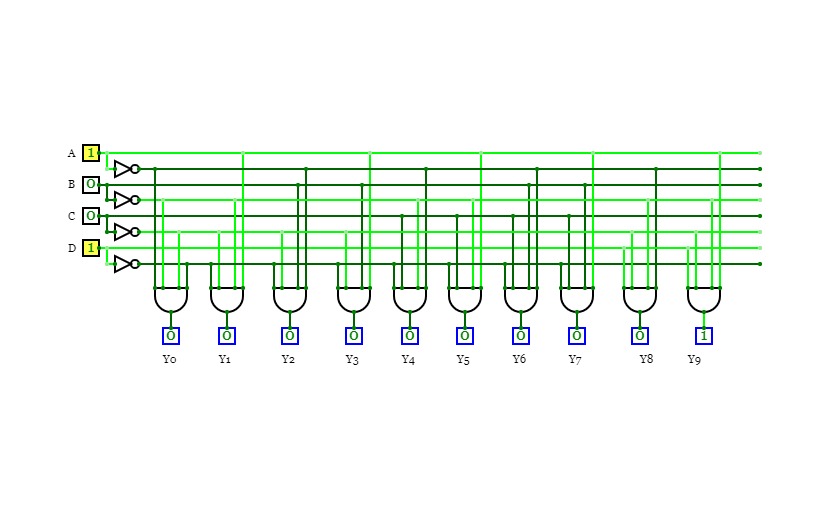

BCD TO DECIMAL DECODER

BCD TO DECIMAL DECODER

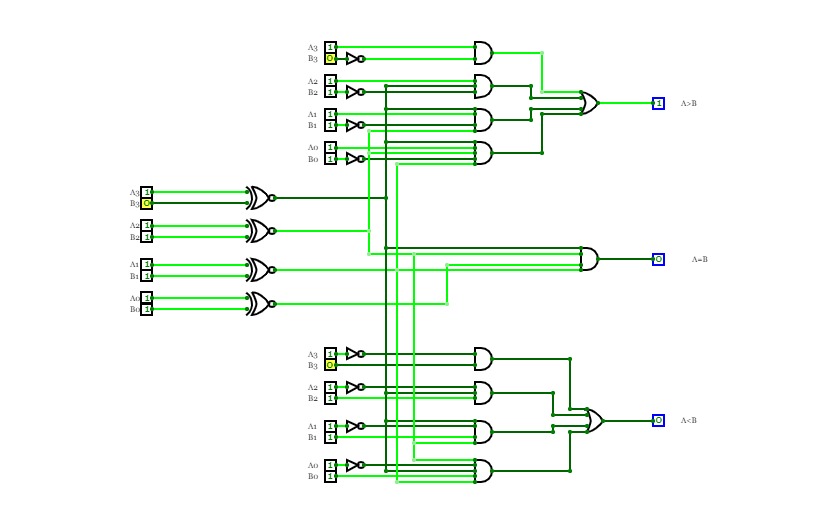

4- BIT MAGNITUDE COMPARATOR

4- BIT MAGNITUDE COMPARATOR

circuit that counts (0,2,4...14)when input is 1 and counts (1,3...15)when input is 0

circuit that counts (0,2,4...14)when input is 1 and counts (1,3...15)when input is 0

4 BIT PARITY CHECKER

4 BIT PARITY CHECKER

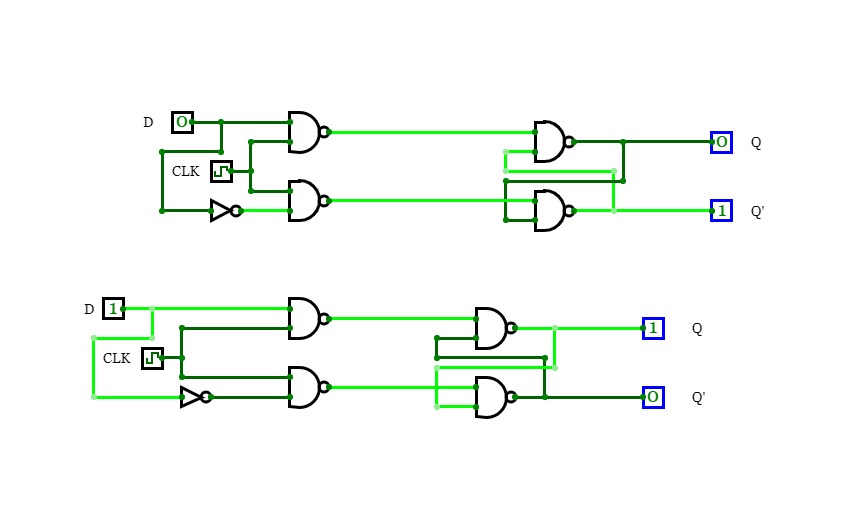

D FLIPFLOP USING LOGIC GATES

D FLIPFLOP USING LOGIC GATES

JK USING TFF

JK USING TFF

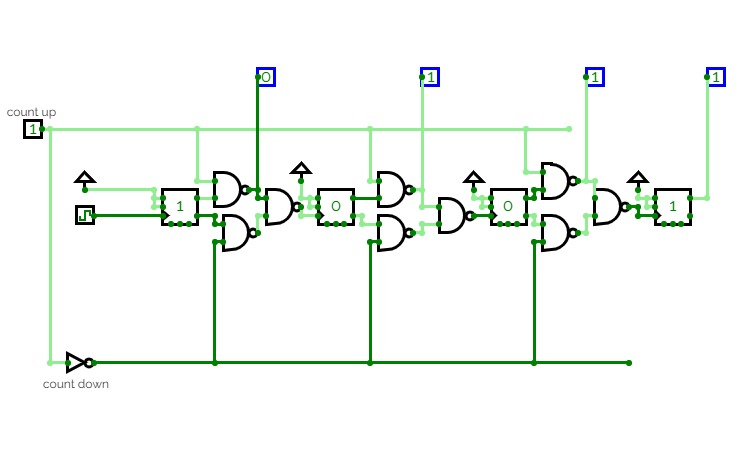

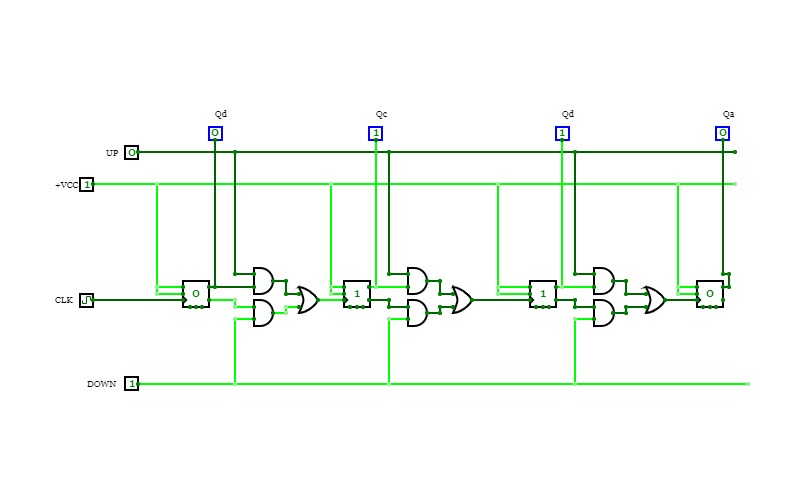

4 BIT RIPPLE UP/DOWN ASYNCHRONOUS COUNTER

4 BIT RIPPLE UP/DOWN ASYNCHRONOUS COUNTER

JK FF USING SRFF

JK FF USING SRFF

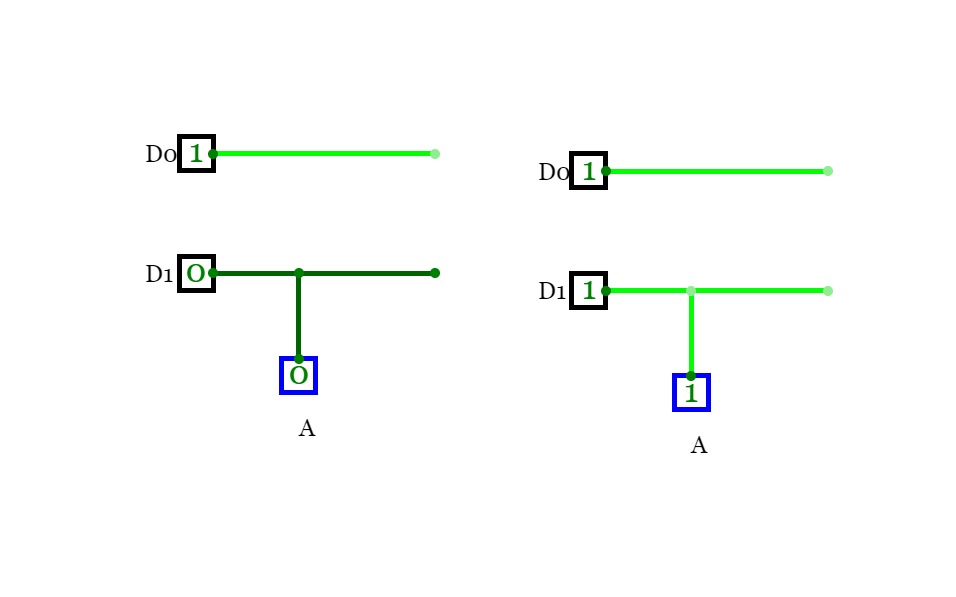

1 T0 2 DEMUX

1 T0 2 DEMUX

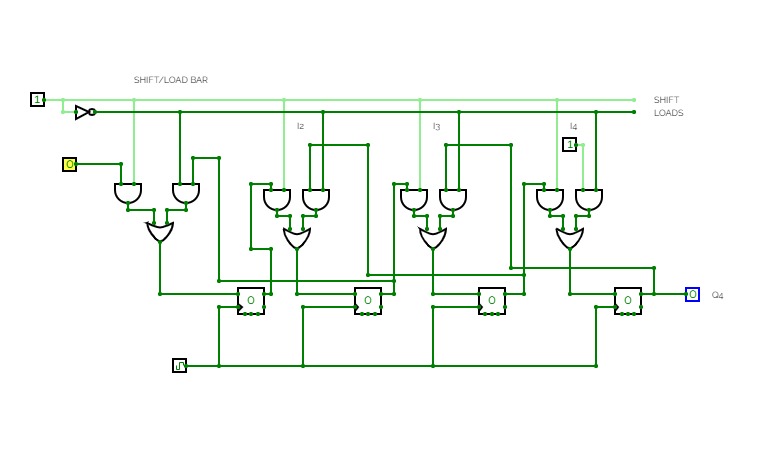

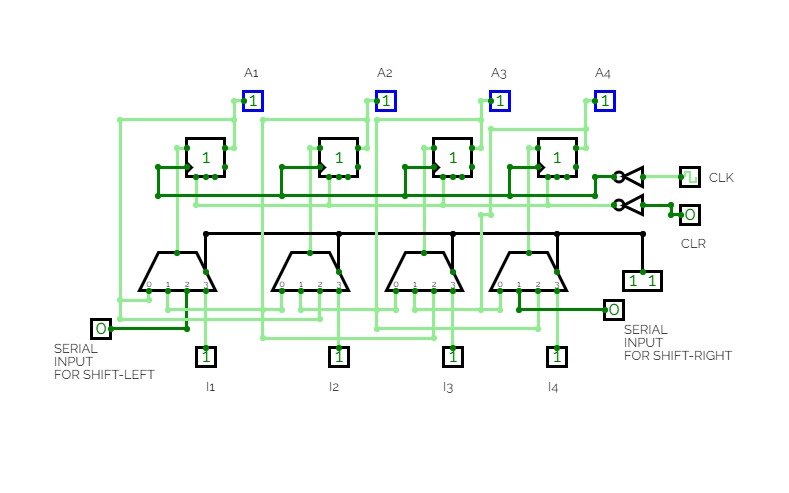

4 BIT UNIVERSAL SHIFT REGISTER

4 BIT UNIVERSAL SHIFT REGISTER

16 to 1 mux

16 to 1 mux

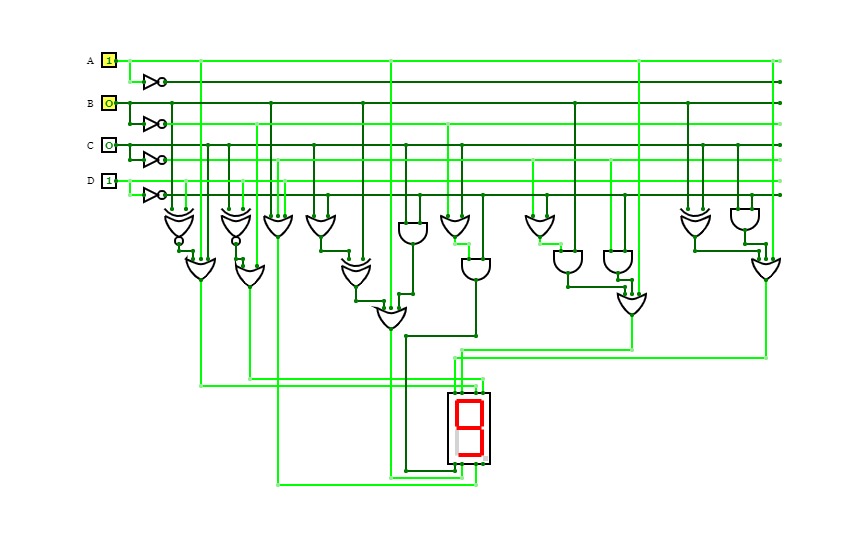

BCD TO SEVEN SEGMENT DISPLAY

BCD TO SEVEN SEGMENT DISPLAY

HALF ADDER USING BASIC GATES

HALF ADDER USING BASIC GATES

SR FLIPFLOP USING INBUILT

SR FLIPFLOP USING INBUILT