NIKITA GAUTAM

Member since: 3 years

Educational Institution: Not Entered

Country: Not Entered

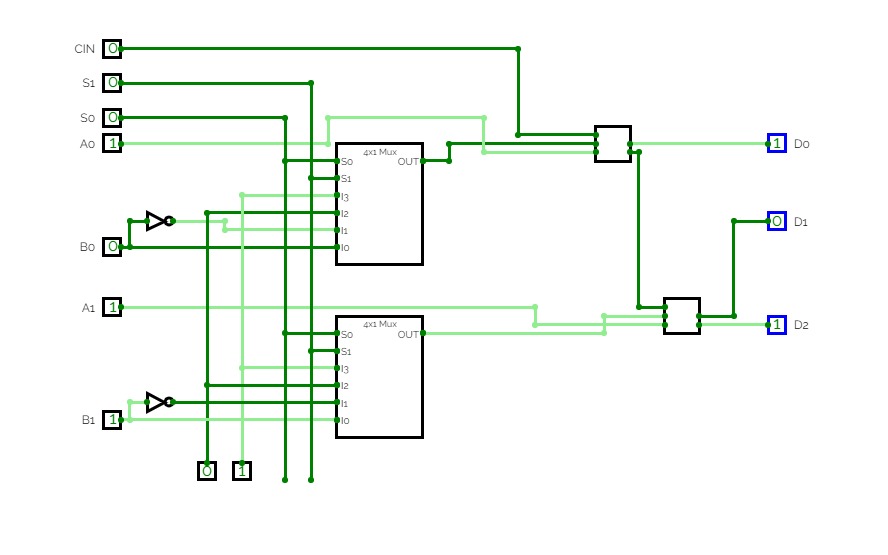

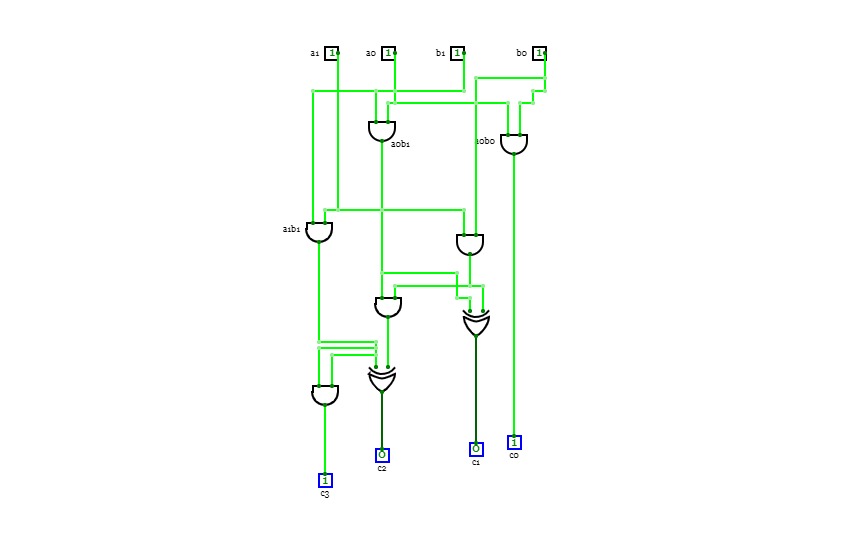

Experiment-14-a

Experiment-14-a

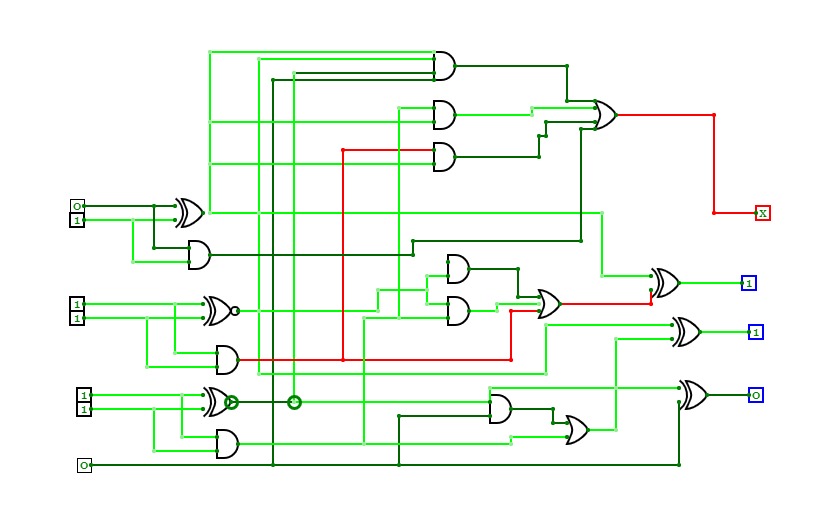

EXP 14 b

EXP 14 b

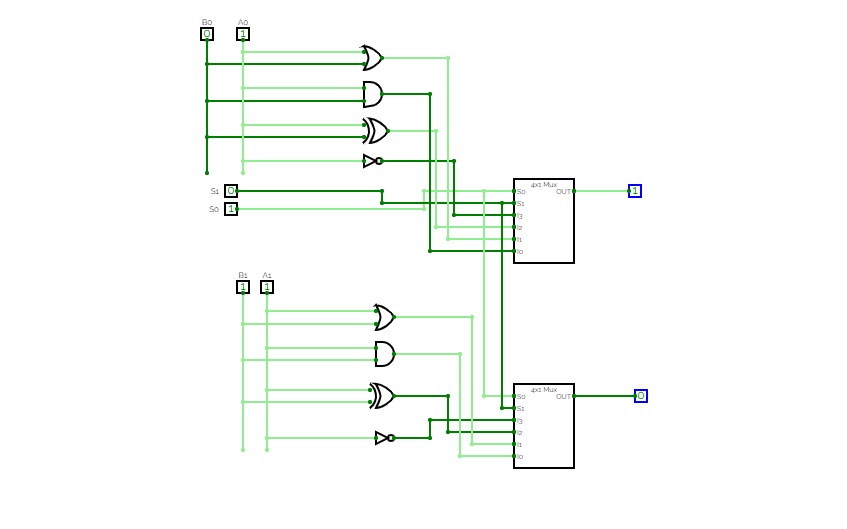

Experiment-16

Experiment-16

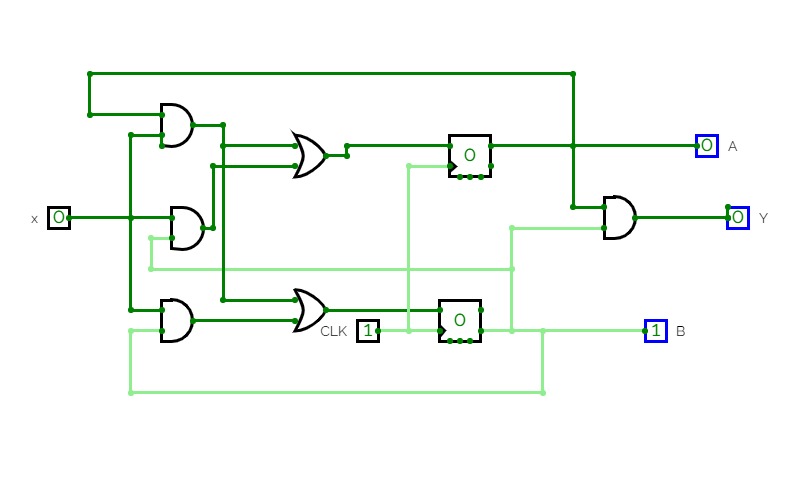

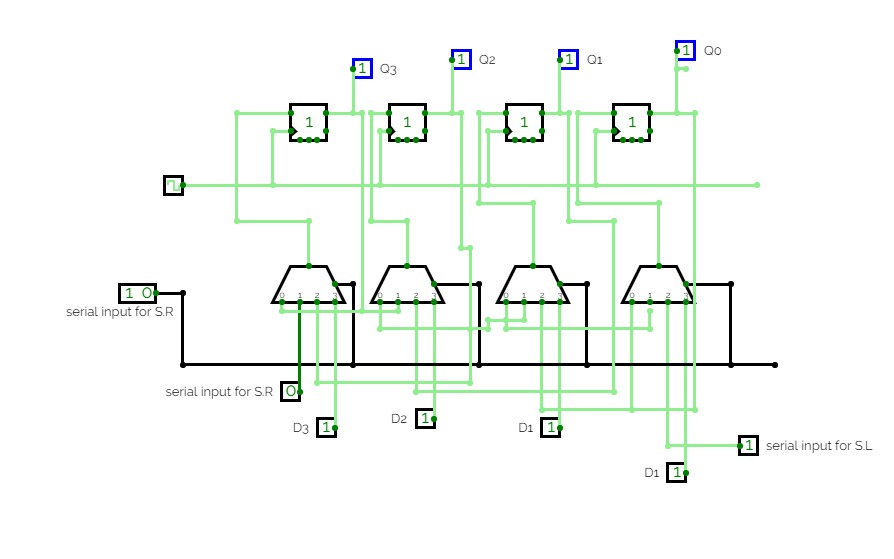

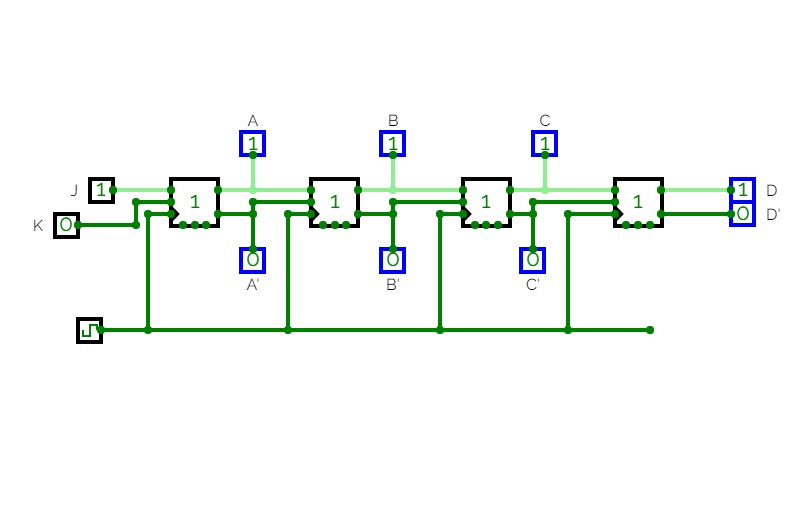

Exp-17(universal register)

Exp-17(universal register)

Experiment.5b

Experiment.5b

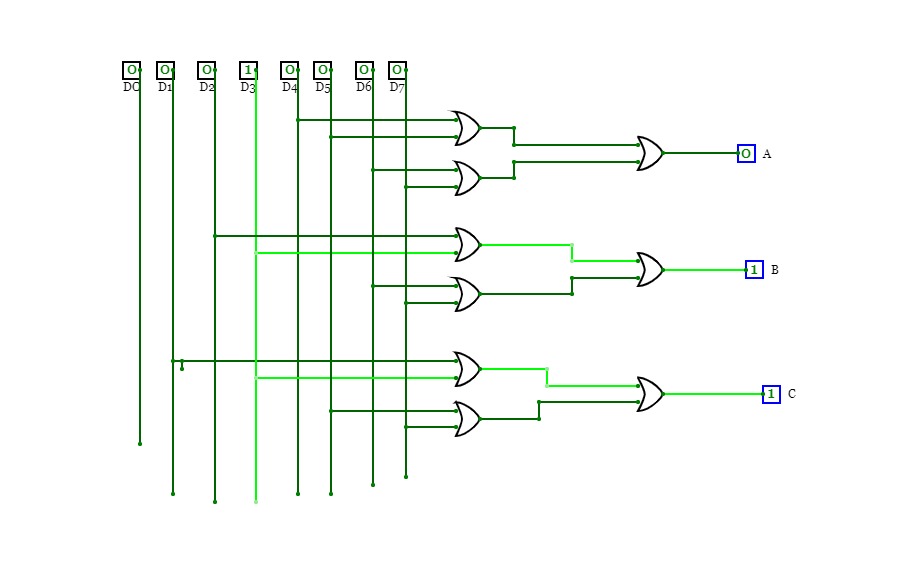

EXPERIMENT-7(8*2)

EXPERIMENT-7(8*2)

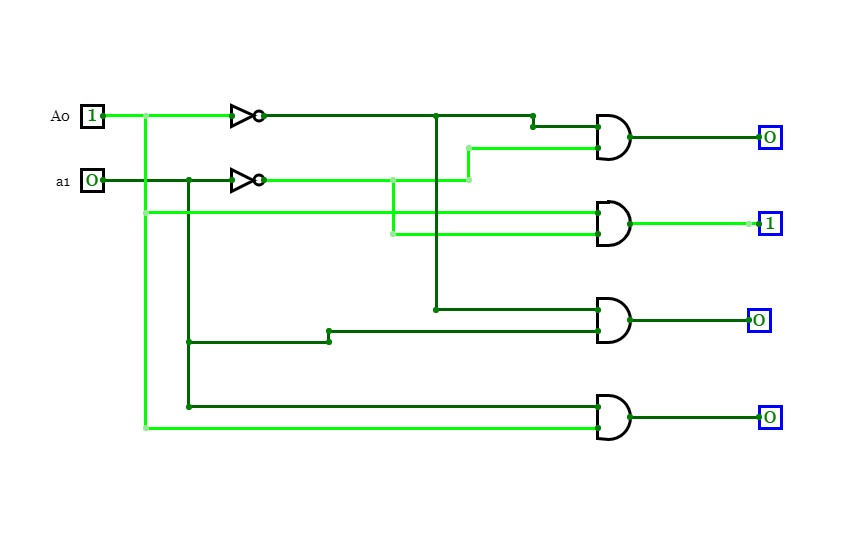

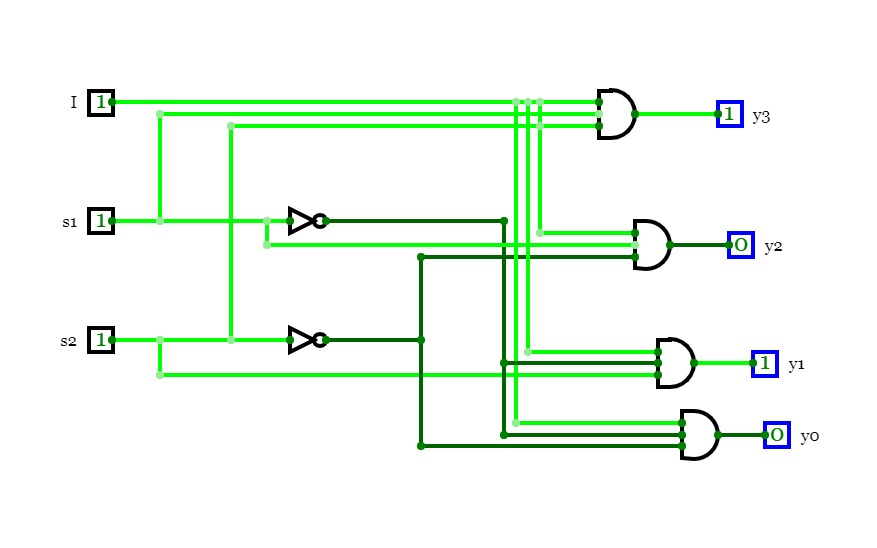

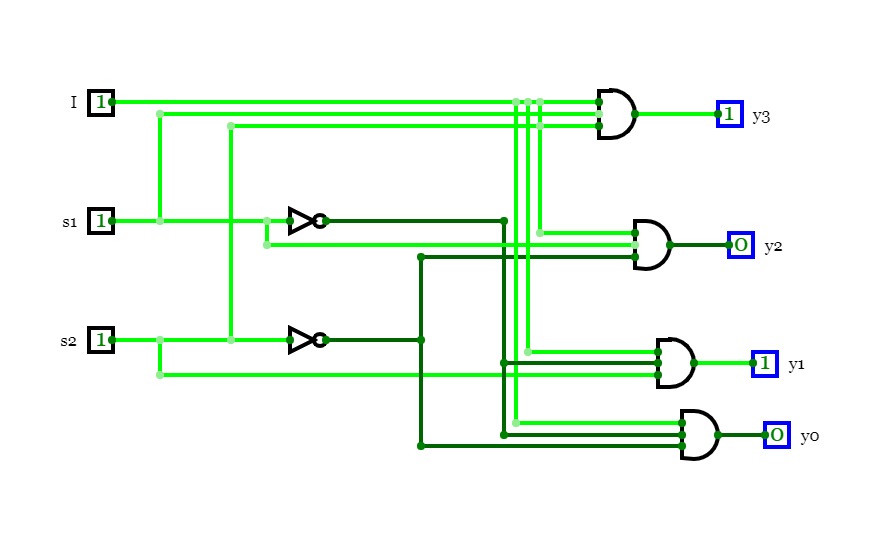

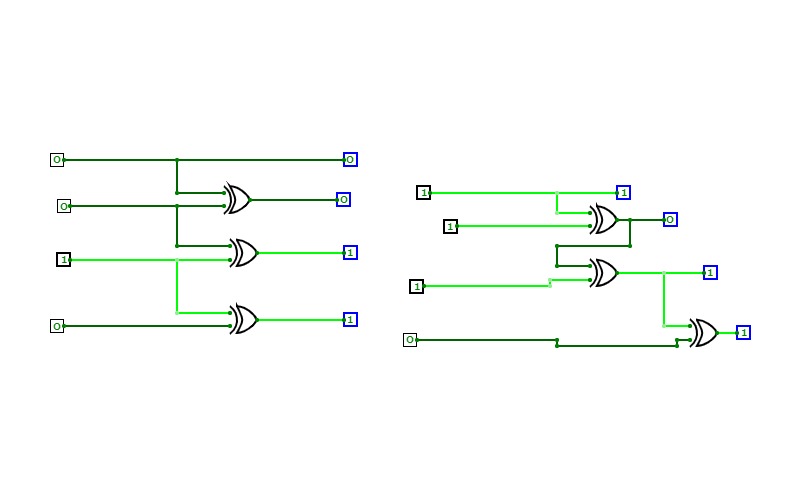

EXPERIMENT-8(2 *4 decoder)

EXPERIMENT-8(2 *4 decoder)

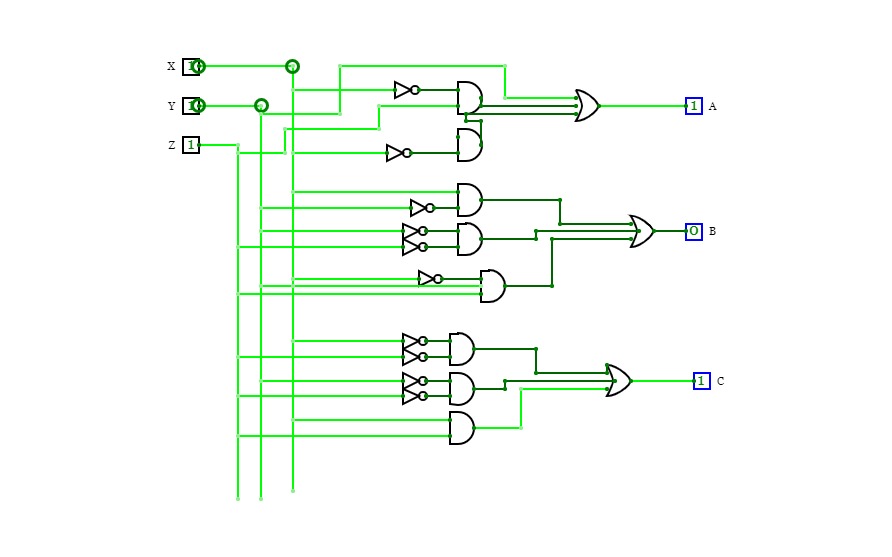

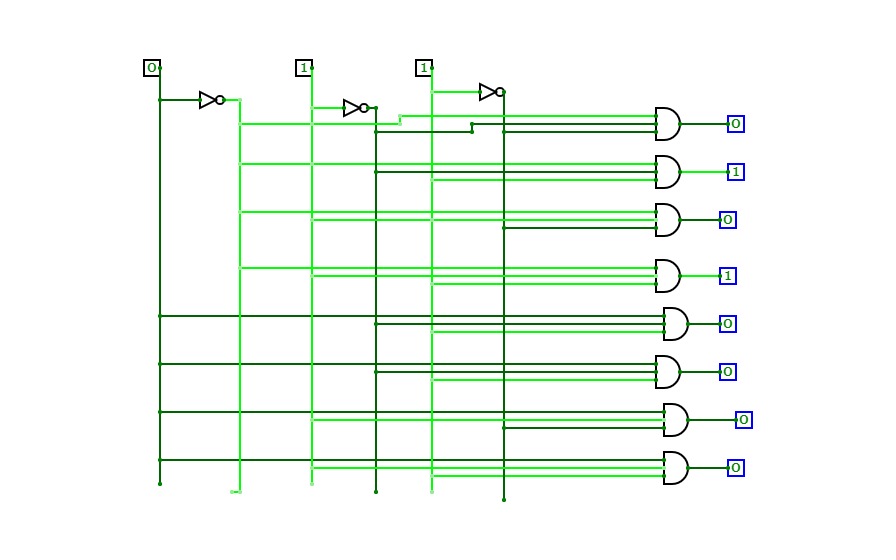

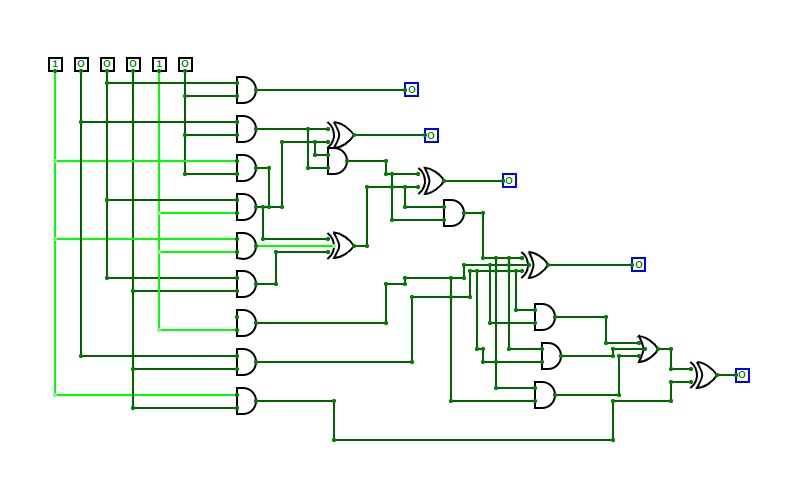

Experiment 8-(3to8decoder)

Experiment 8-(3to8decoder)

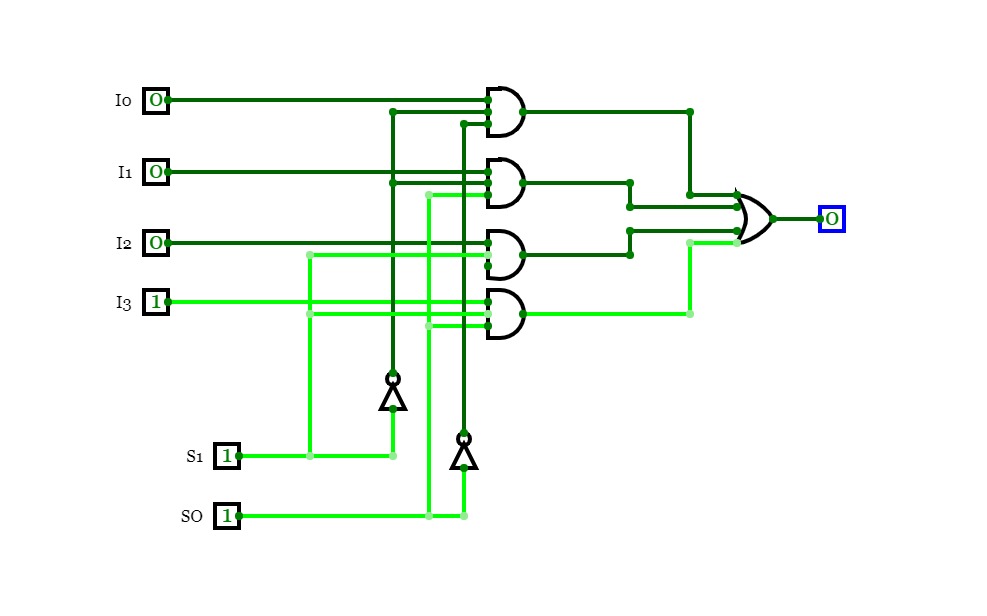

EXPERIMENT-9B

EXPERIMENT-9B

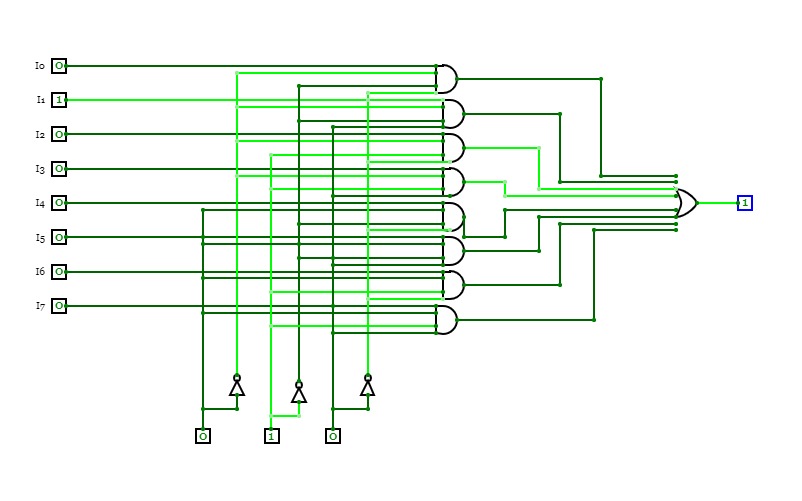

EXPERIMENT-9

EXPERIMENT-9

experiment-10

experiment-10

experiment-10

experiment-10

Experiment-12

Experiment-12

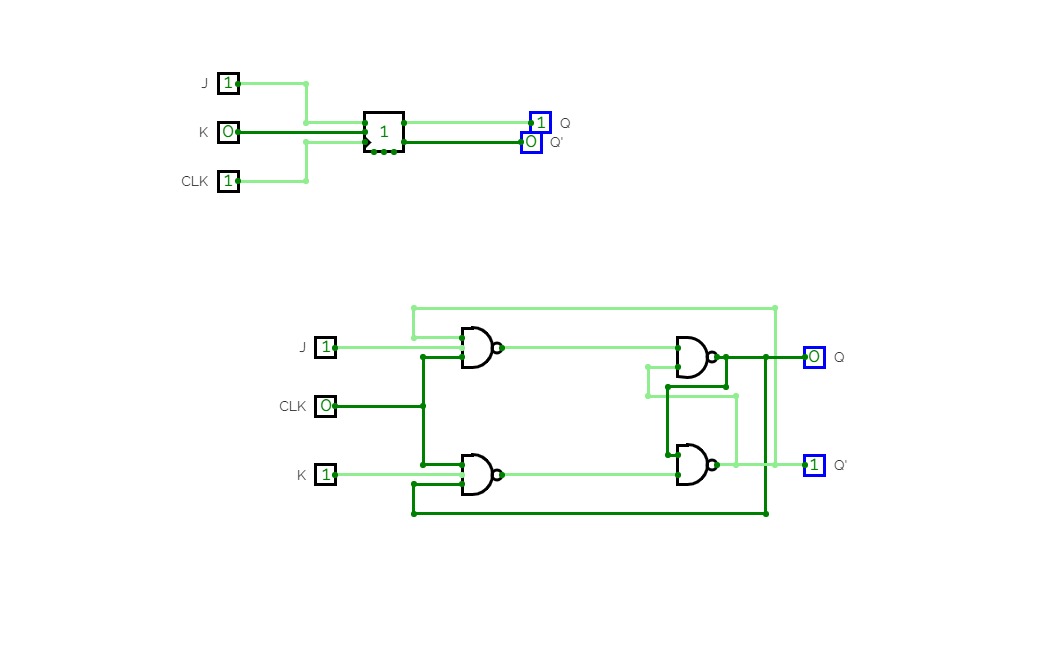

JK flipflop

JK flipflop

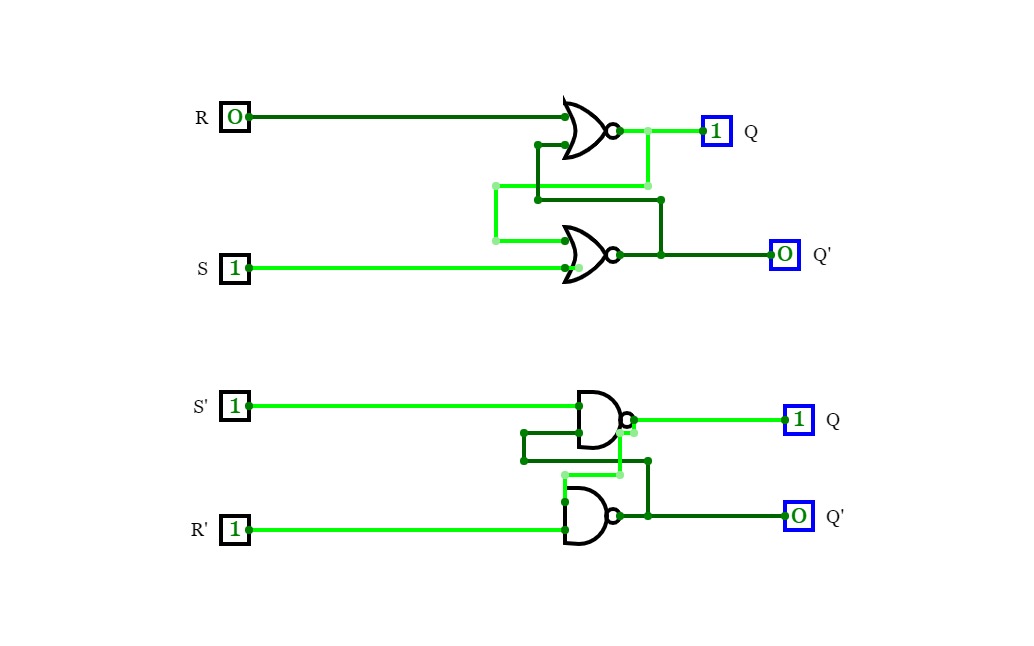

exp-11(SR latch NAND and OR)

exp-11(SR latch NAND and OR)

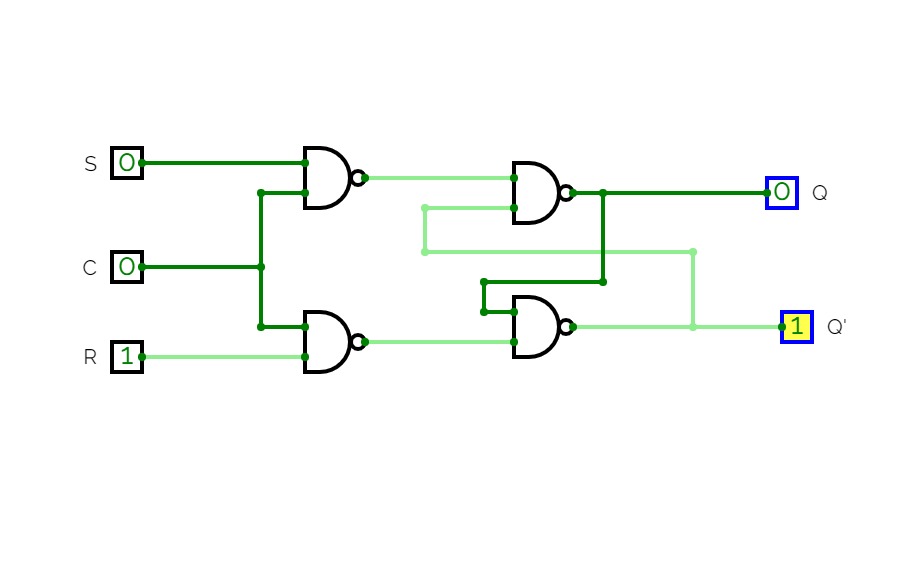

Clocked SR using NAND

Clocked SR using NAND

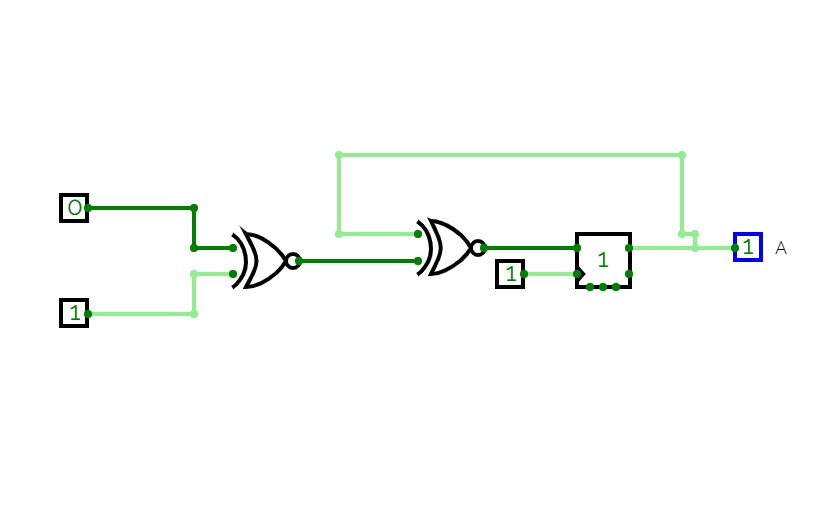

Untitled

Untitled

Experiment-14-b

Experiment-14-b

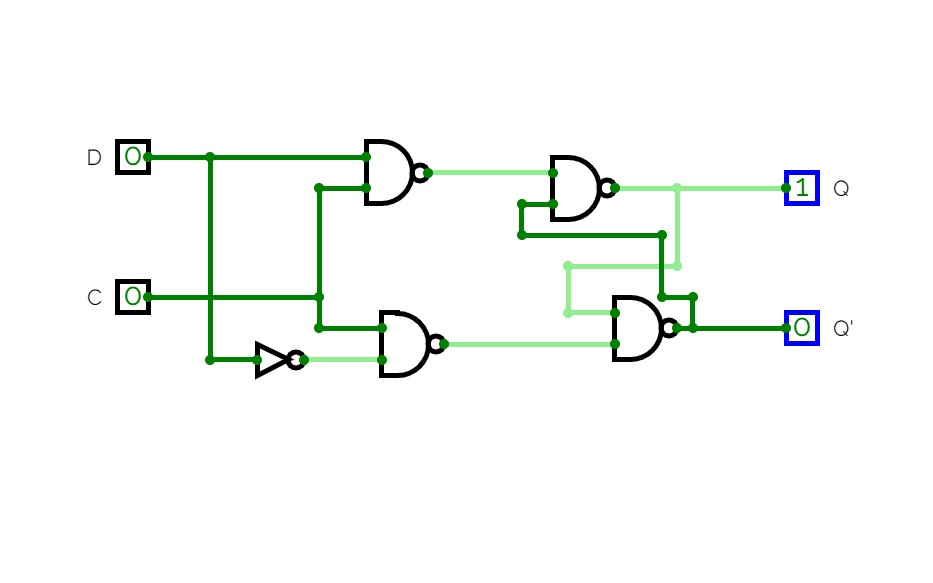

D latch using NOR

D latch using NOR

EXPERMINENT-15

EXPERMINENT-15

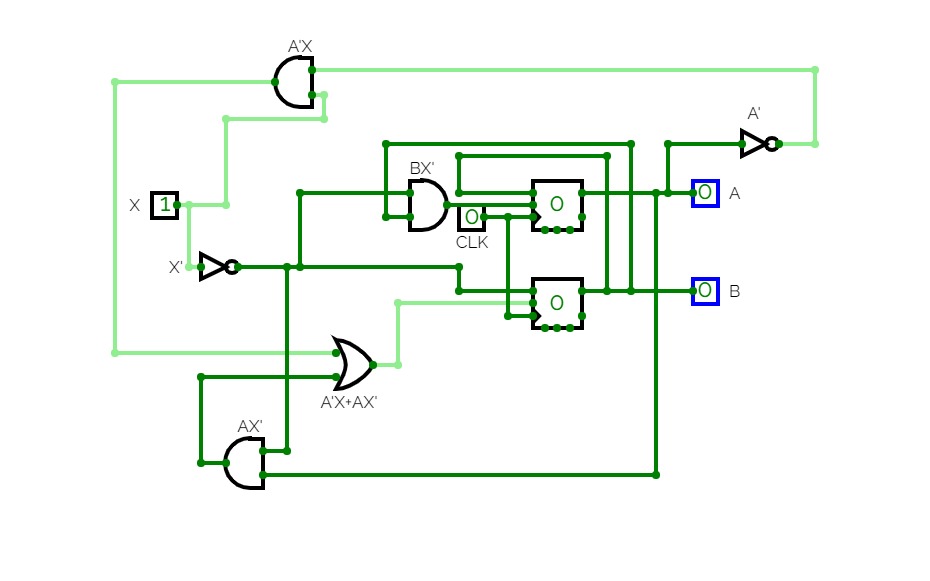

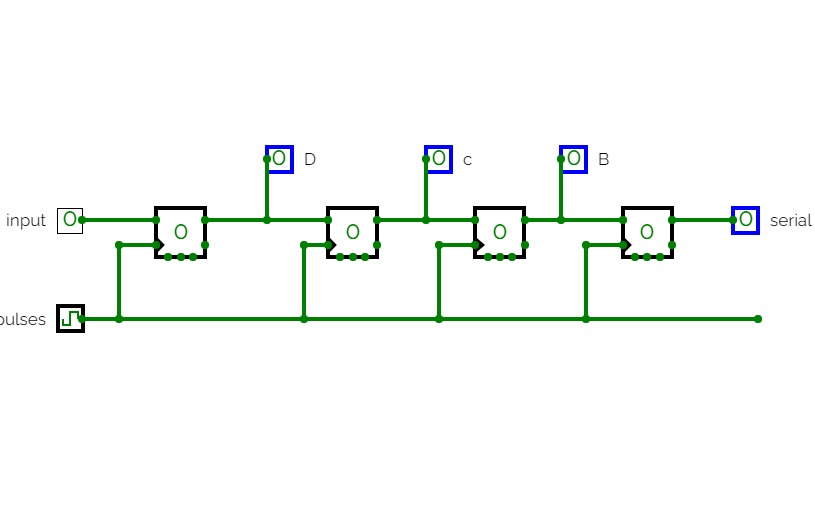

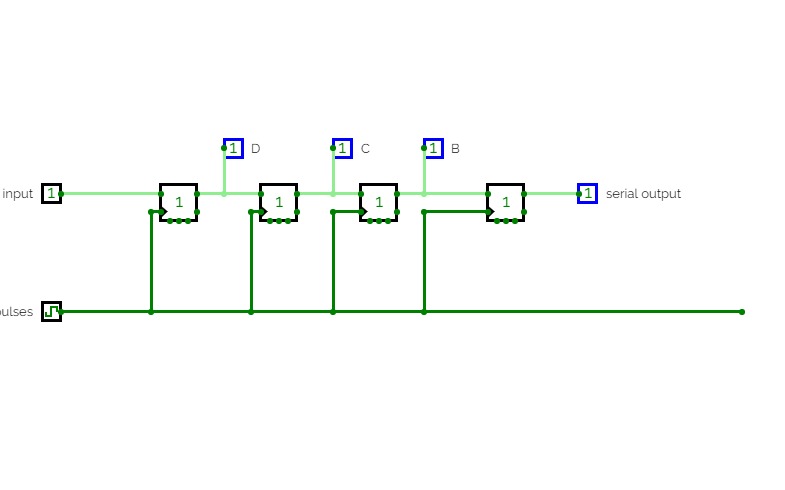

Exp-17 shift left using D

Exp-17 shift left using D

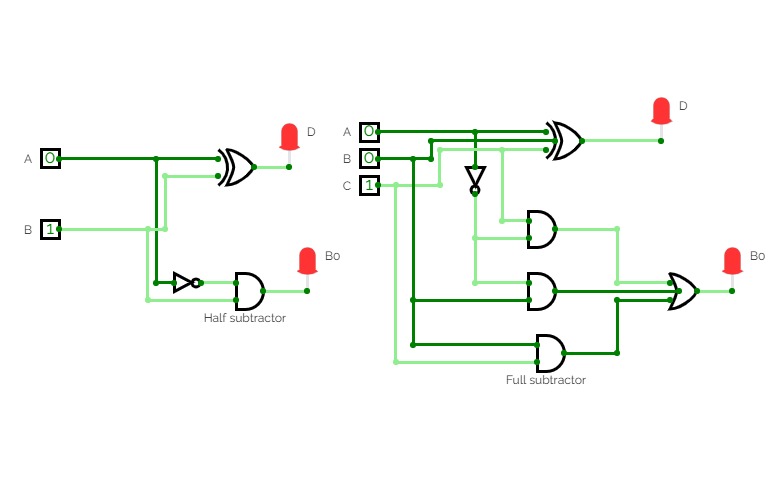

internal-half and full subtractor

internal-half and full subtractor

full subtractor

full subtractor

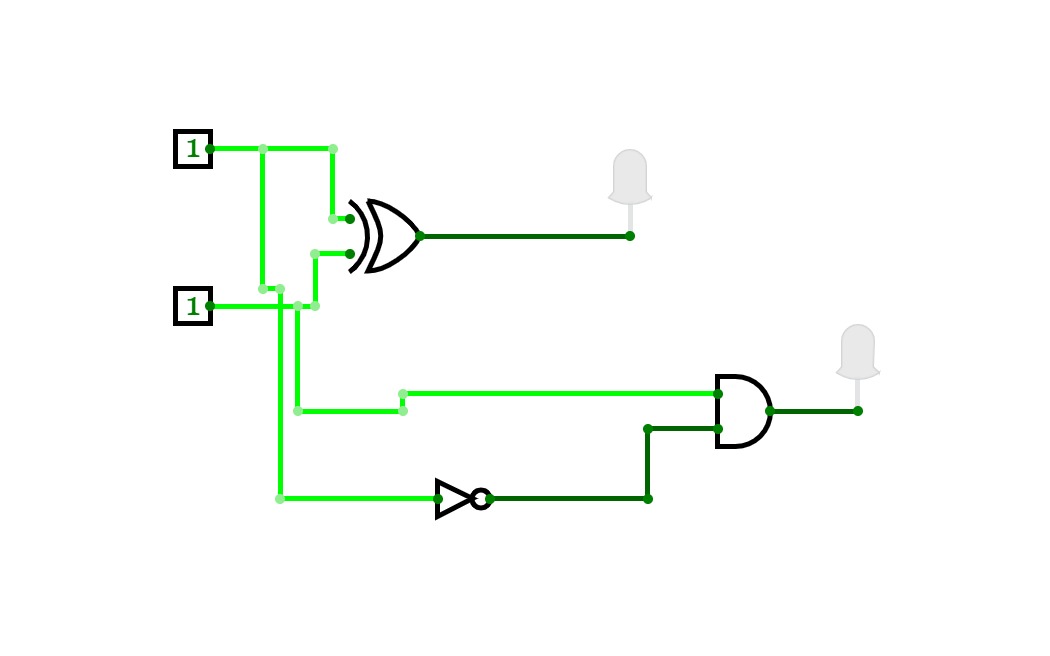

Half subtactor

Half subtactor

Experiment-6b

Experiment-6b

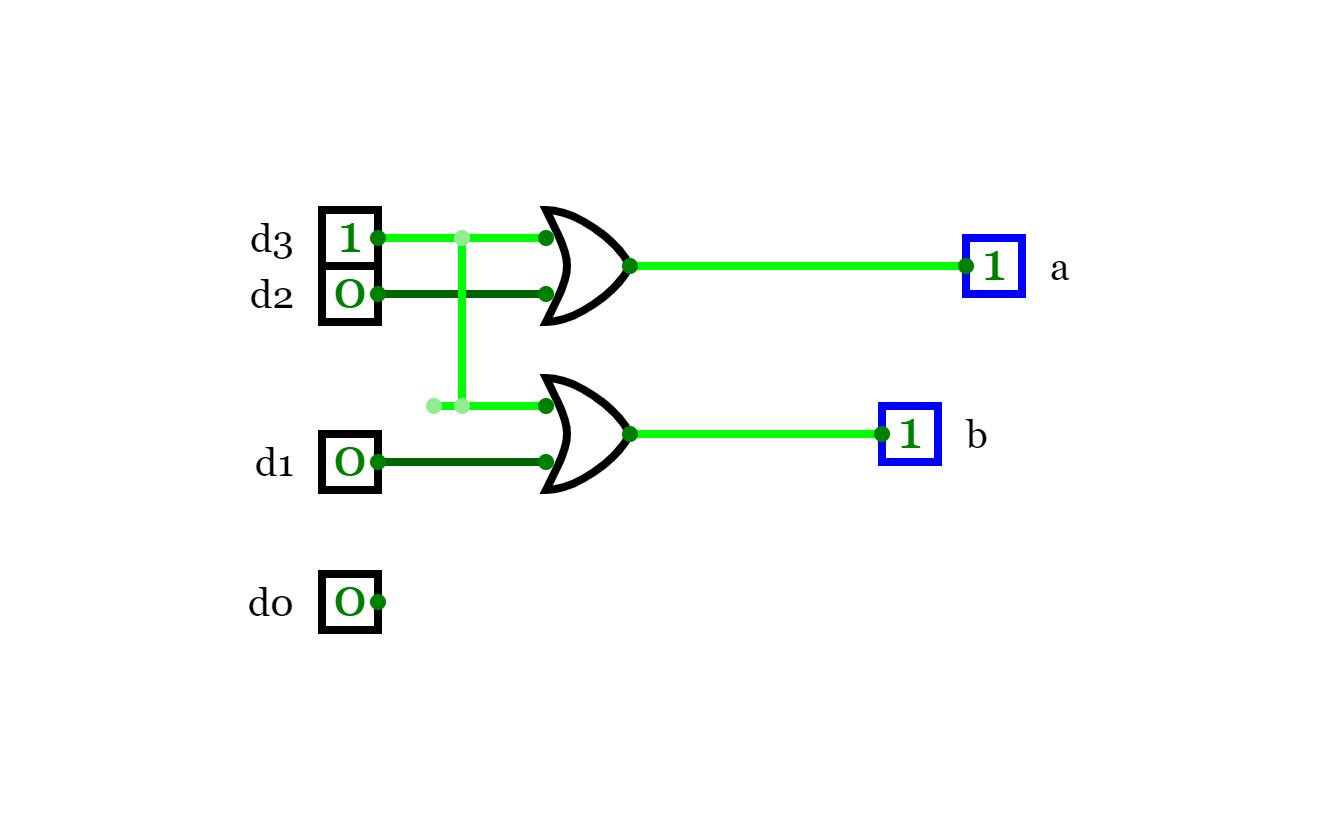

Experiment -7(4*2)

Experiment -7(4*2)

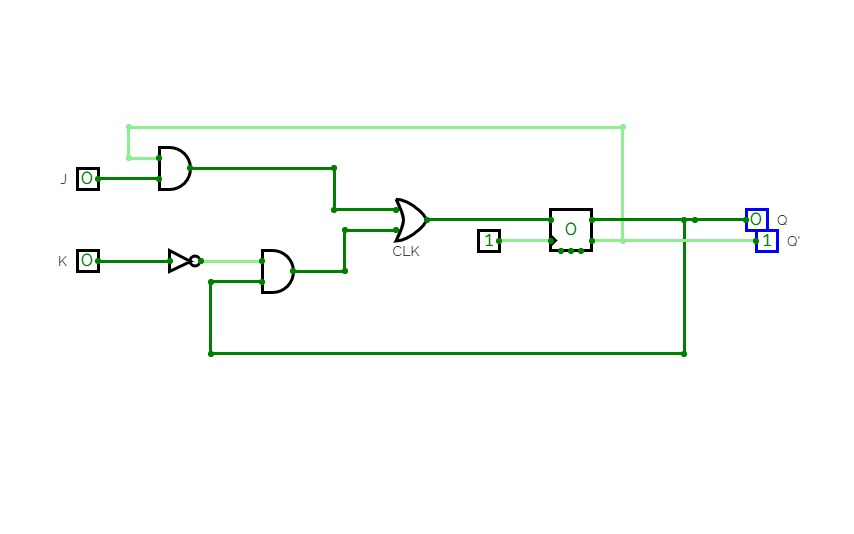

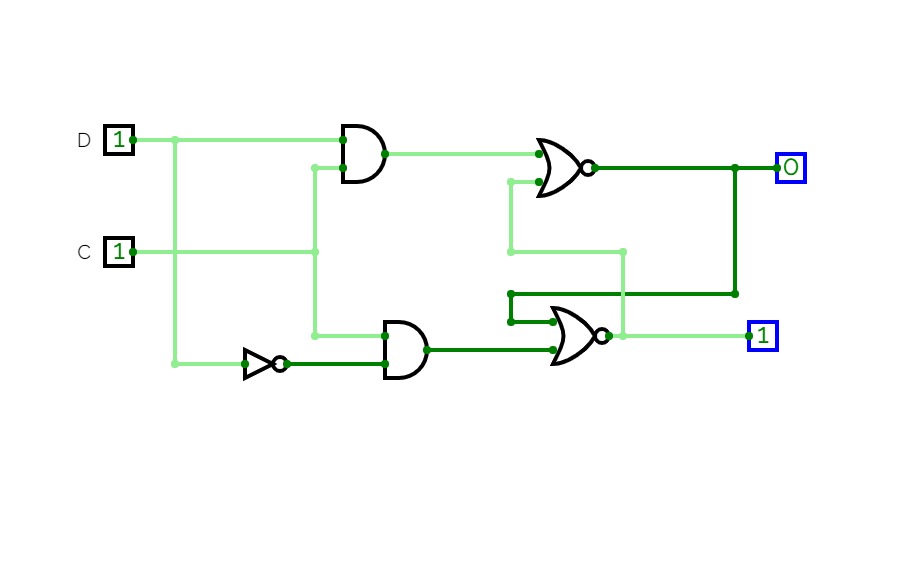

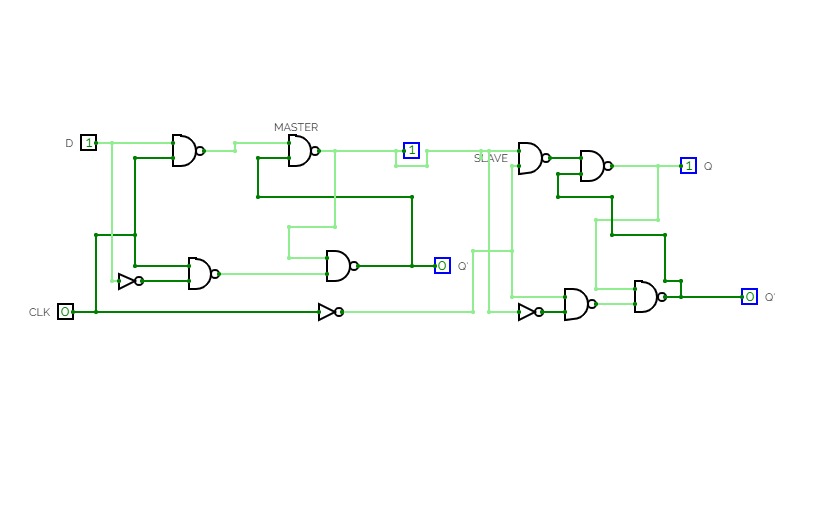

Master slave d flipflop

Master slave d flipflop

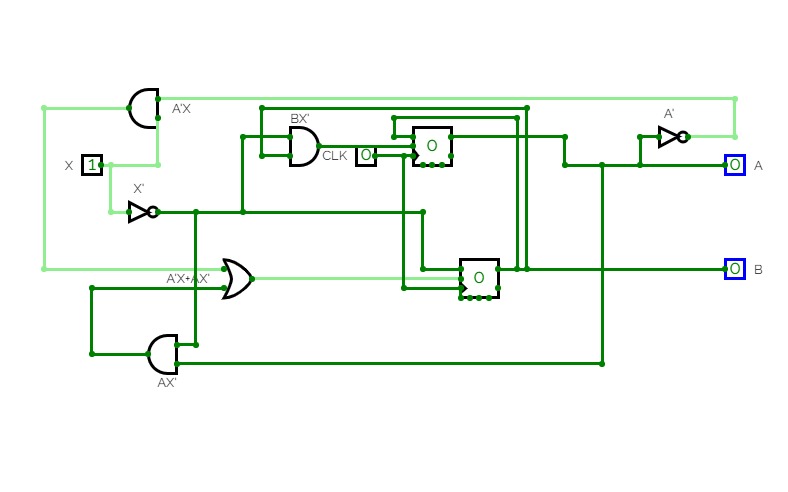

left shift using jk

left shift using jk

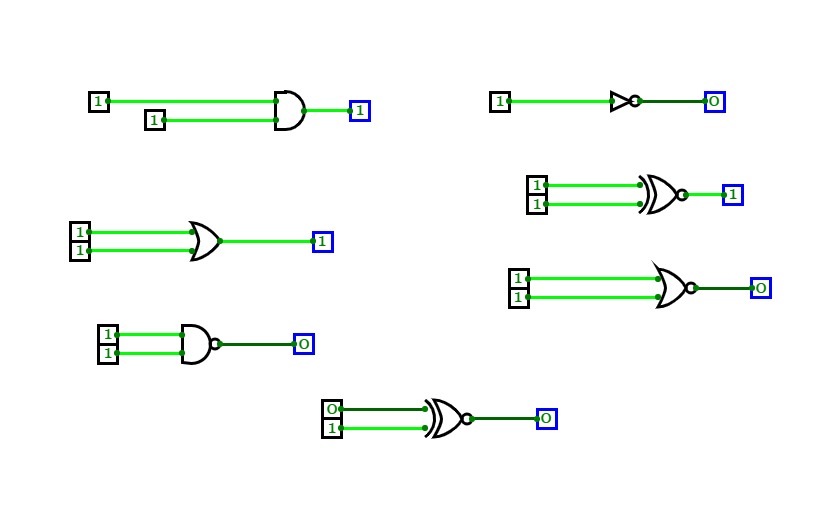

EXPERIMENT 1

EXPERIMENT 1

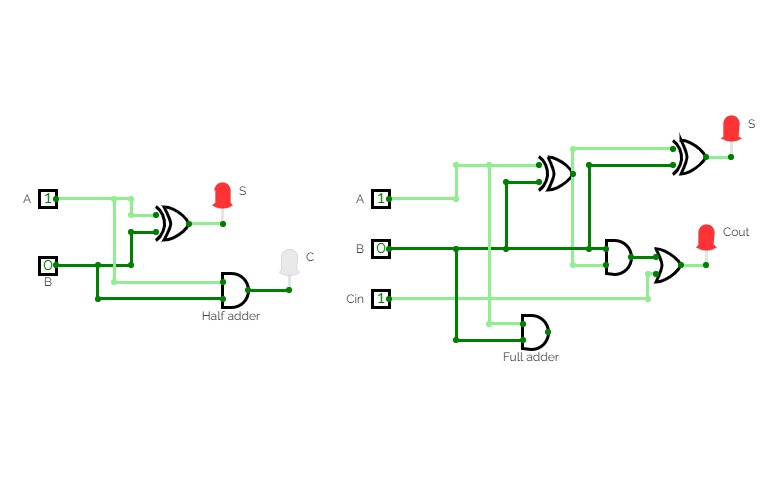

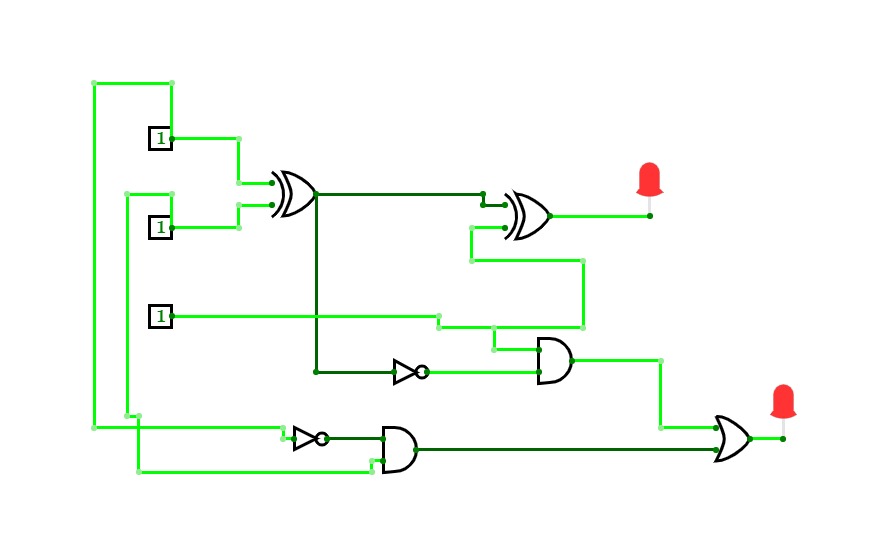

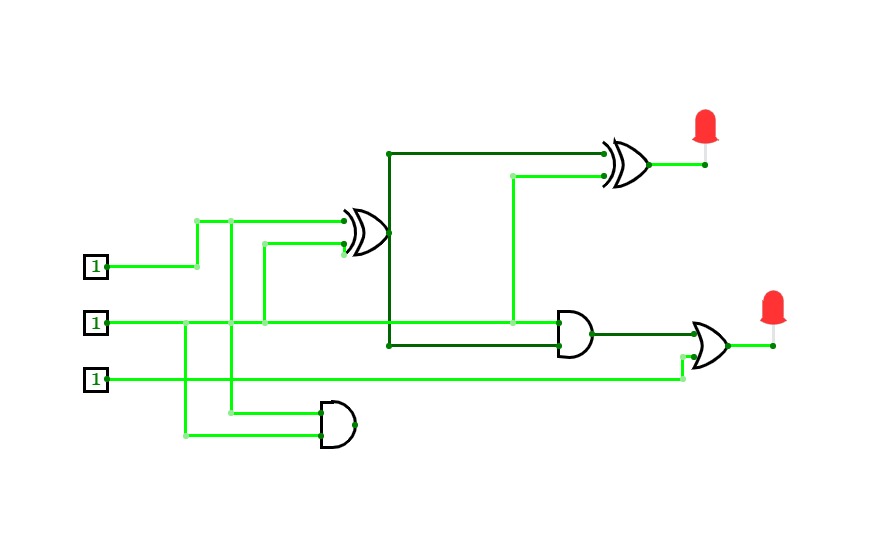

FULL ADDER

FULL ADDER

exp.5

exp.5

Experiment -6

Experiment -6

EXPERIMENT.4

EXPERIMENT.4

EXPERIMENT-15B

EXPERIMENT-15B

Exp-17(shift right using D)

Exp-17(shift right using D)

internal-half adder and full adder

internal-half adder and full adder