Nilanjan Das

Member since: 4 years

Educational Institution: Techno India University kolkata

Country: India

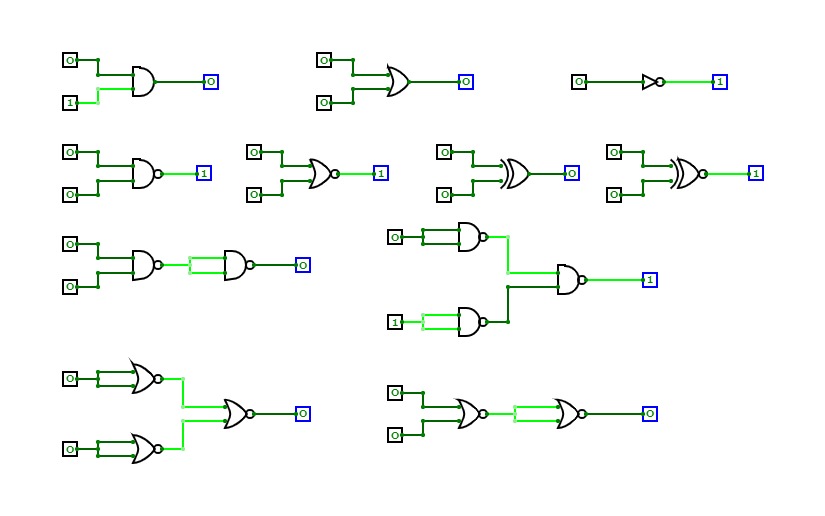

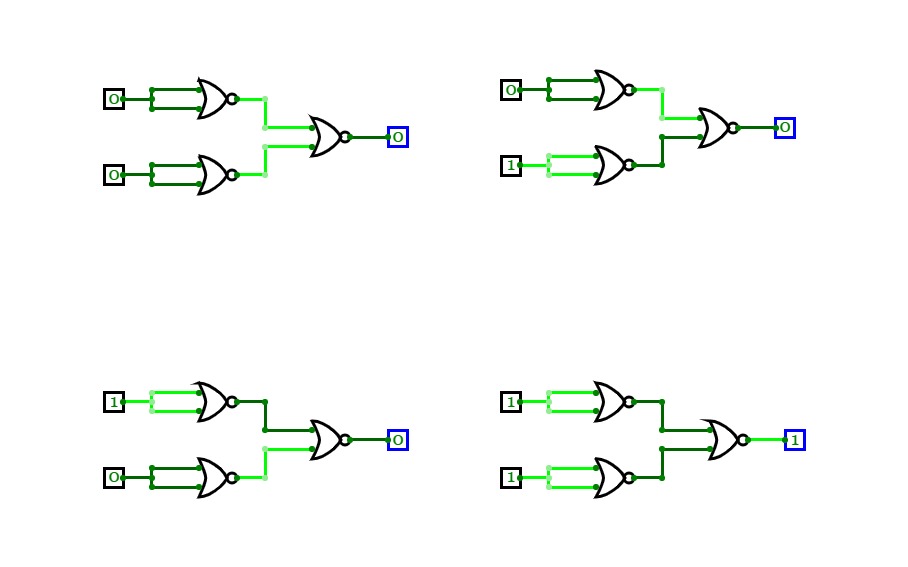

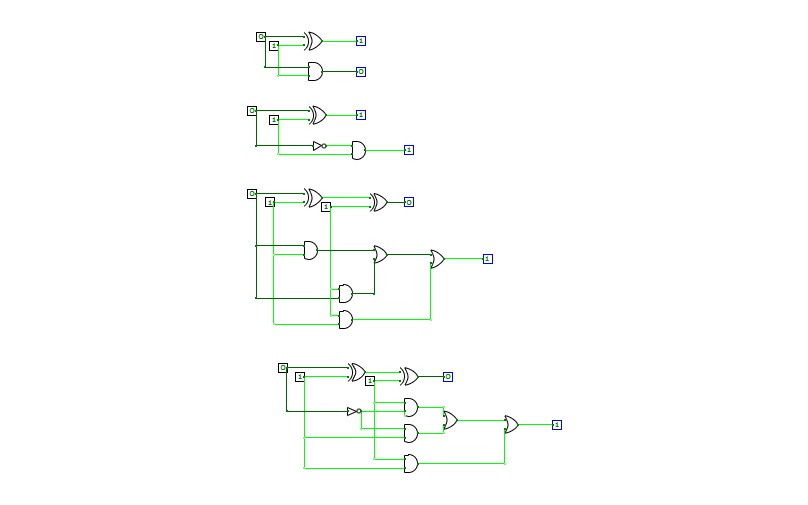

AND from NAND

AND from NAND

OR from NAND

OR from NAND

NOT from NAND

NOT from NAND

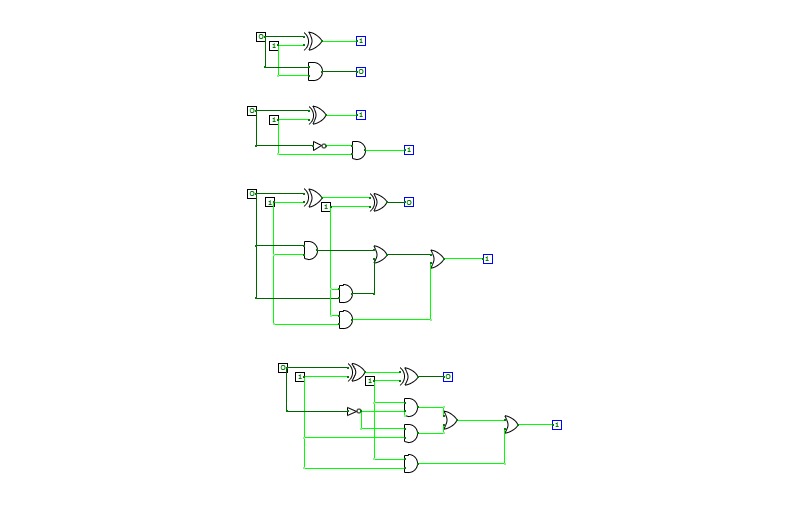

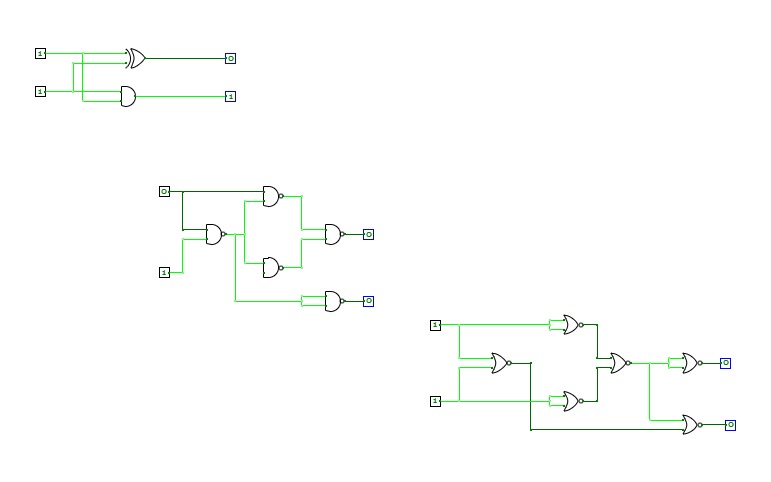

All Gates

All Gates

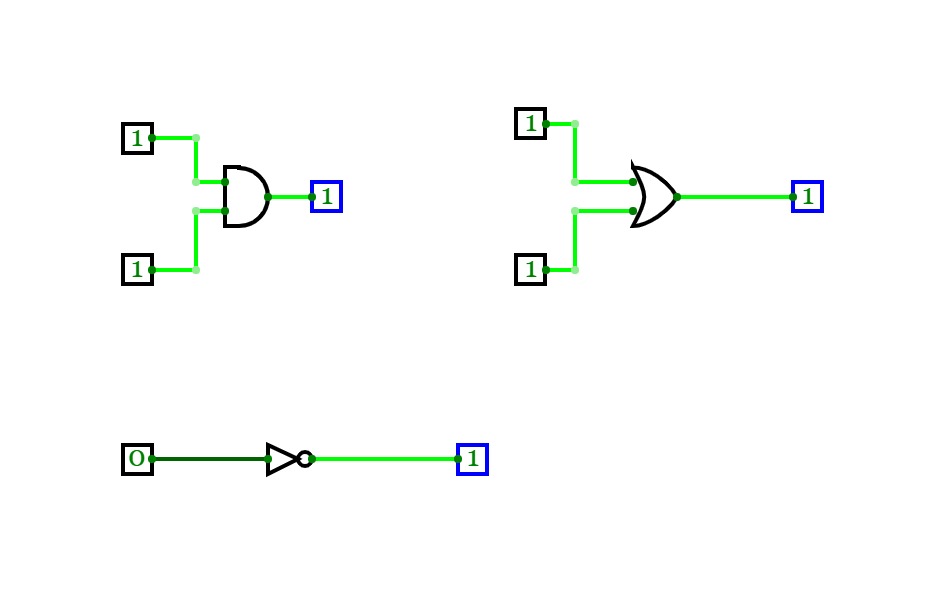

AND

AND

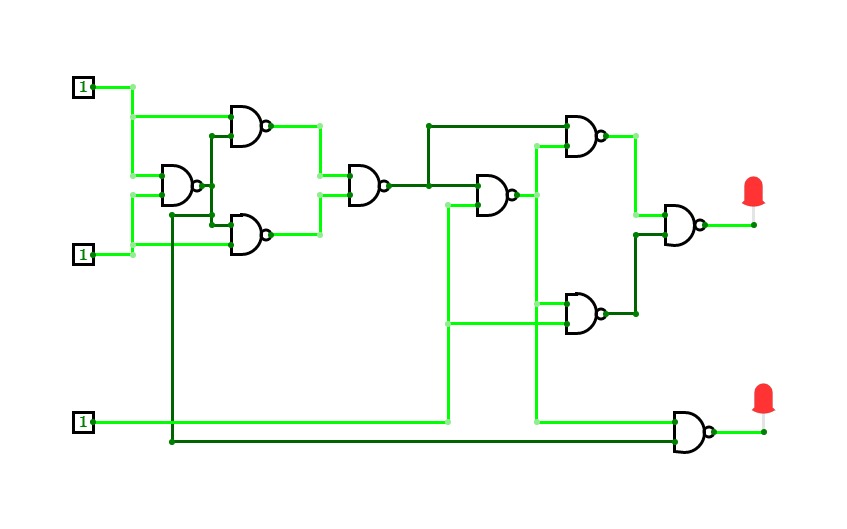

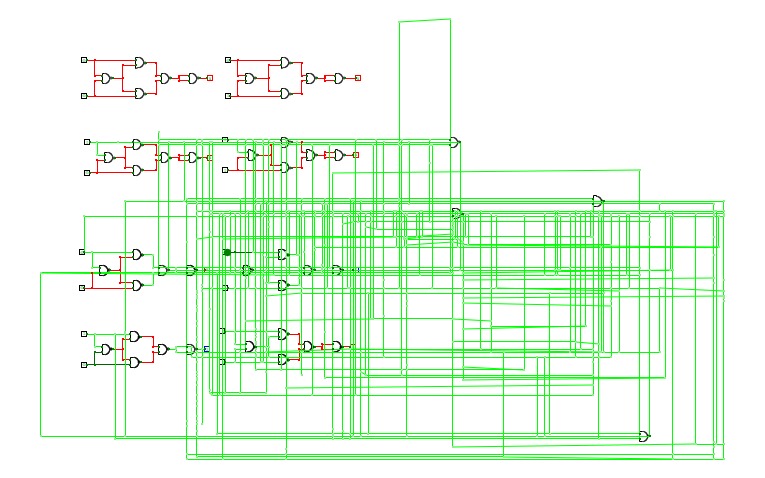

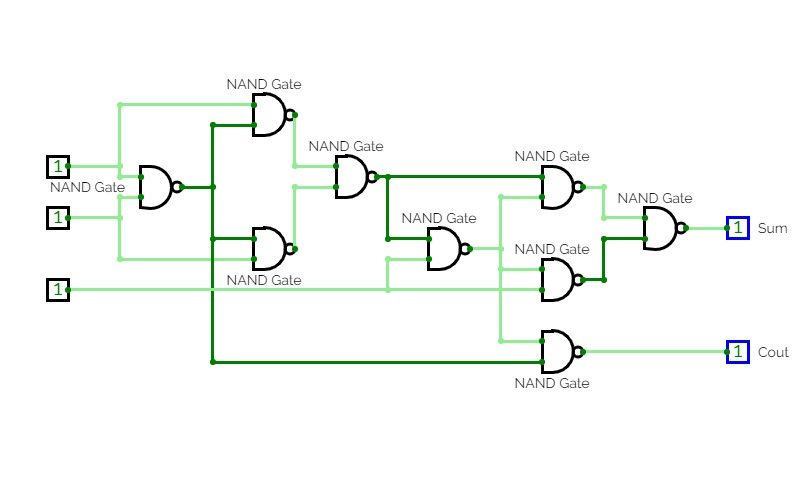

Full Adder Using NAND gate

Full Adder Using NAND gate

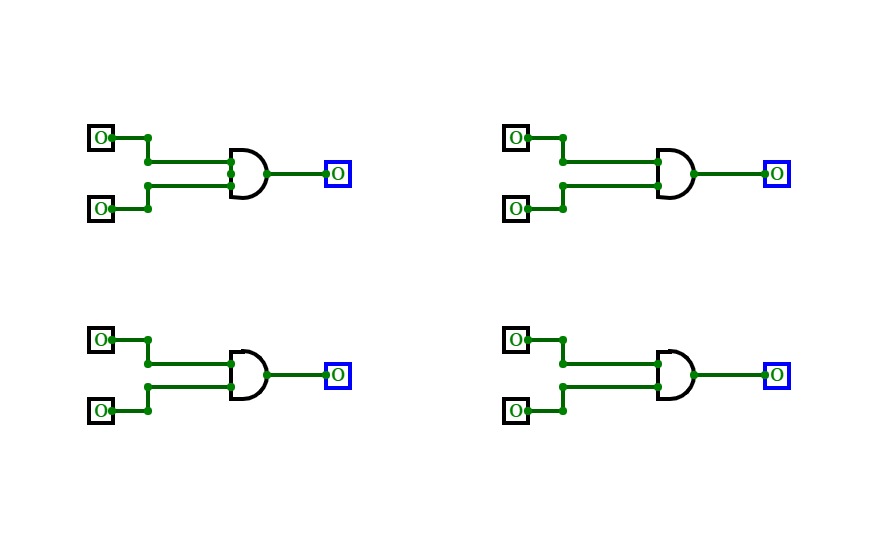

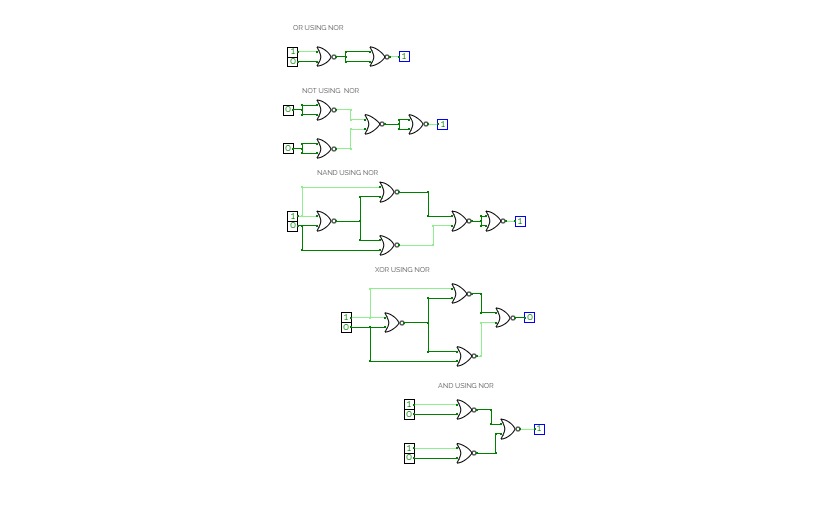

OR using NOR

OR using NOR

AND using NAND

AND using NAND

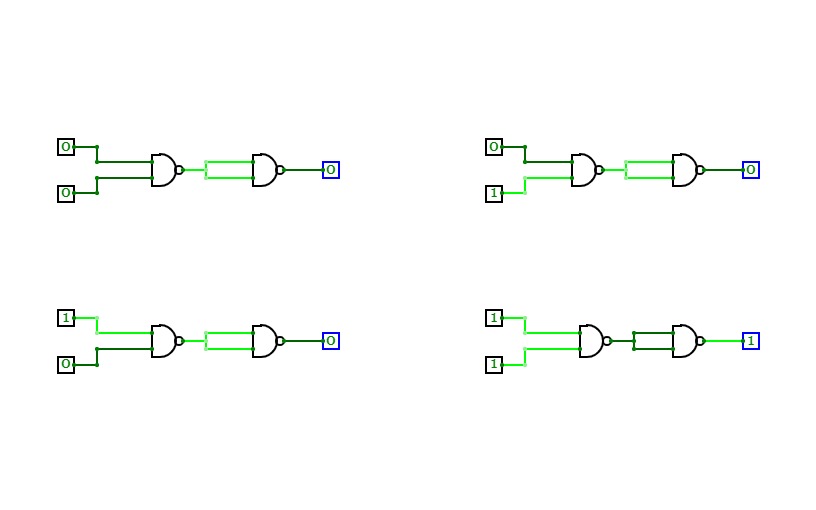

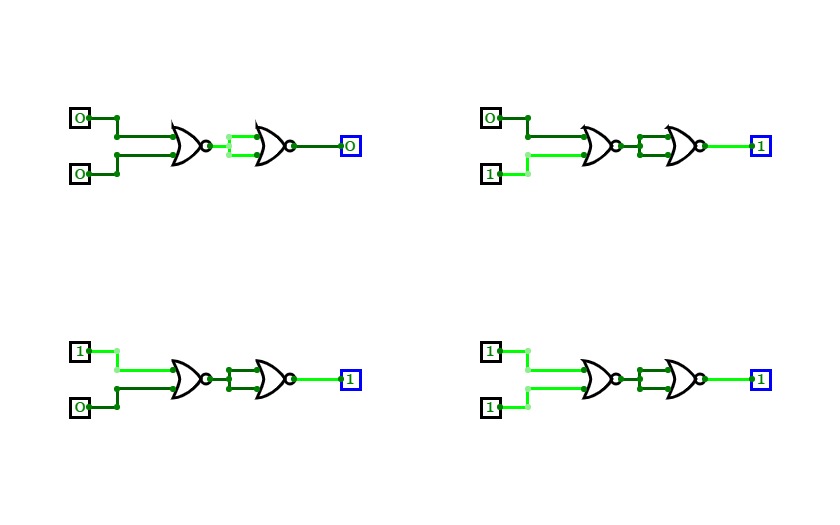

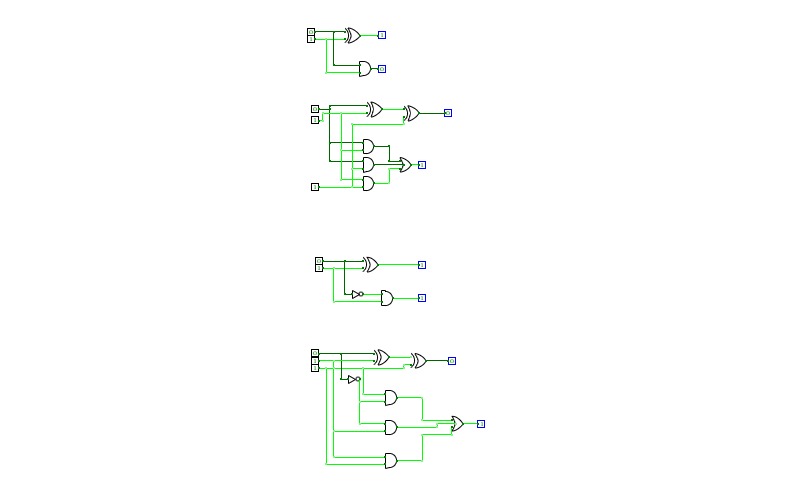

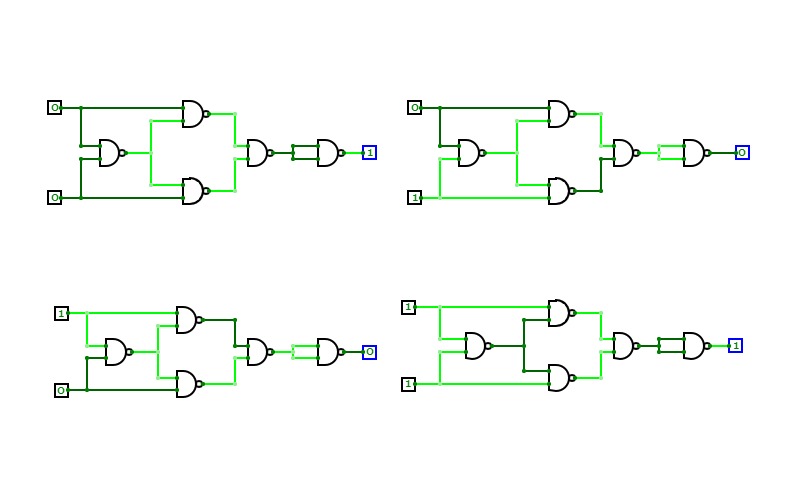

Half Adder

Half Adder

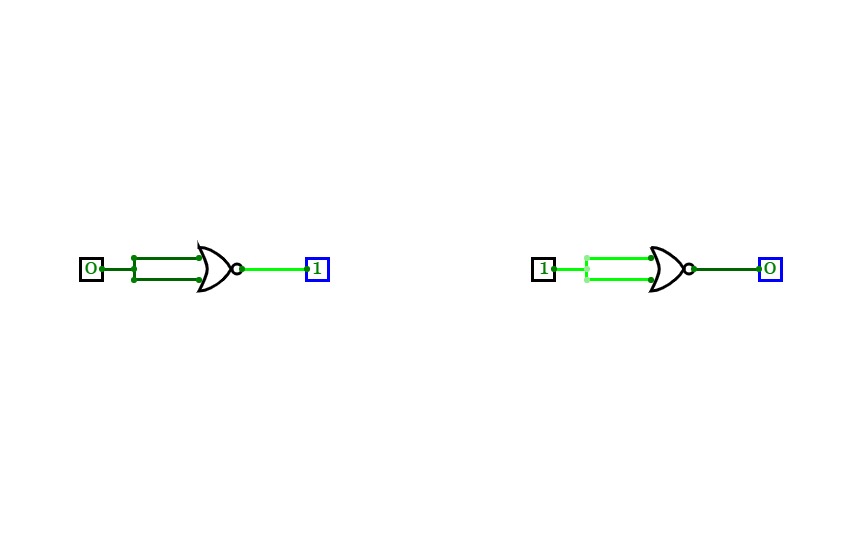

Untitled

Untitled

AND OR NOT Gate

AND OR NOT Gate

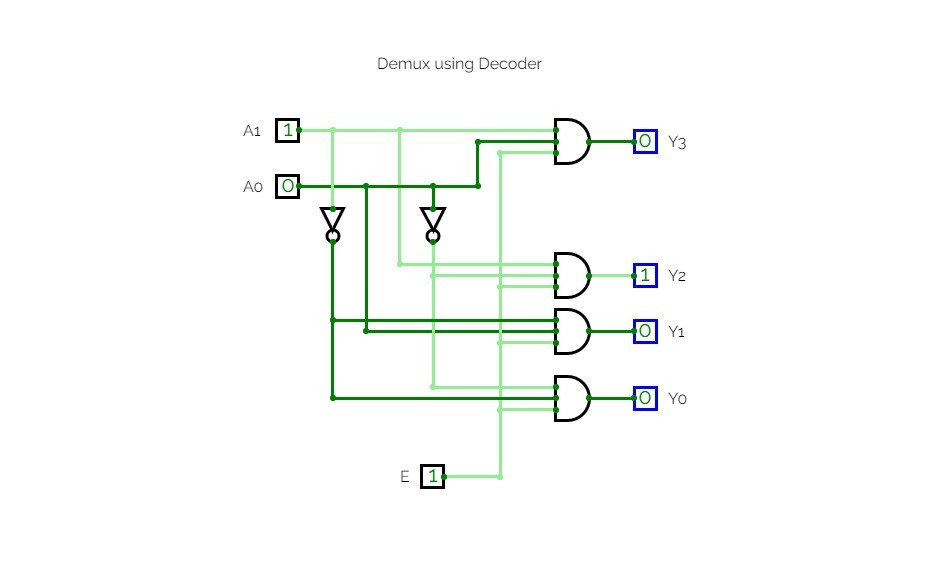

1x4 Demux using 2 to 4 Decoder

1x4 Demux using 2 to 4 Decoder

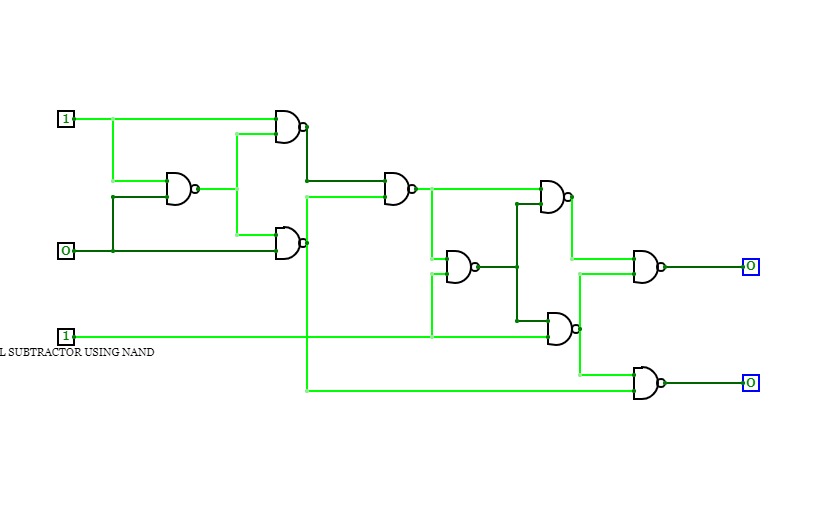

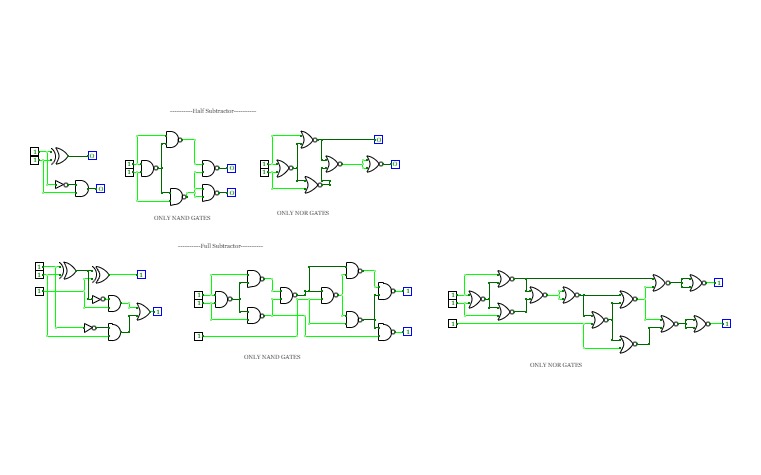

Q.16) Full Subtractor Implementation

Q.16) Full Subtractor Implementation

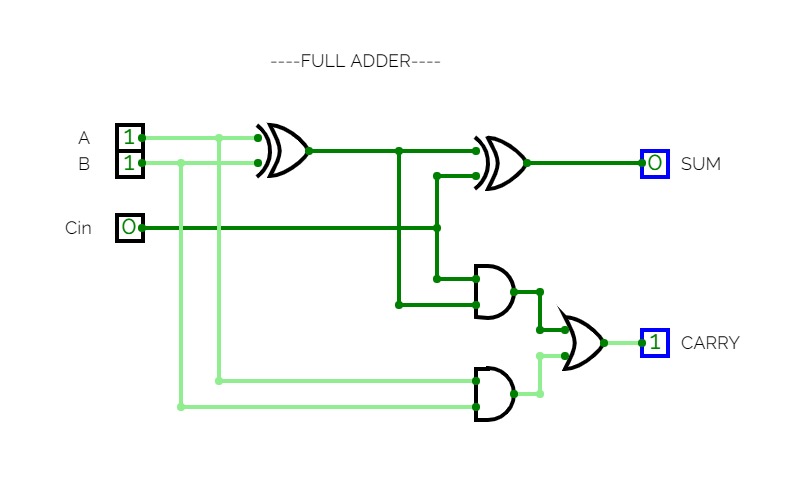

Q.15) Full adder Implementation

Q.15) Full adder Implementation

Half Adder ,Full adder , Half Subtractor and Full Subtractor

Half Adder ,Full adder , Half Subtractor and Full Subtractor

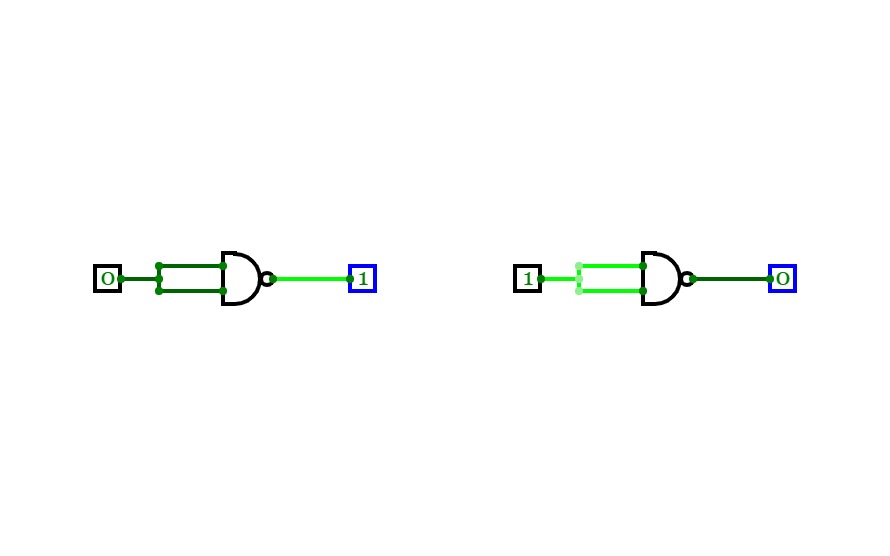

NOT using NOR

NOT using NOR

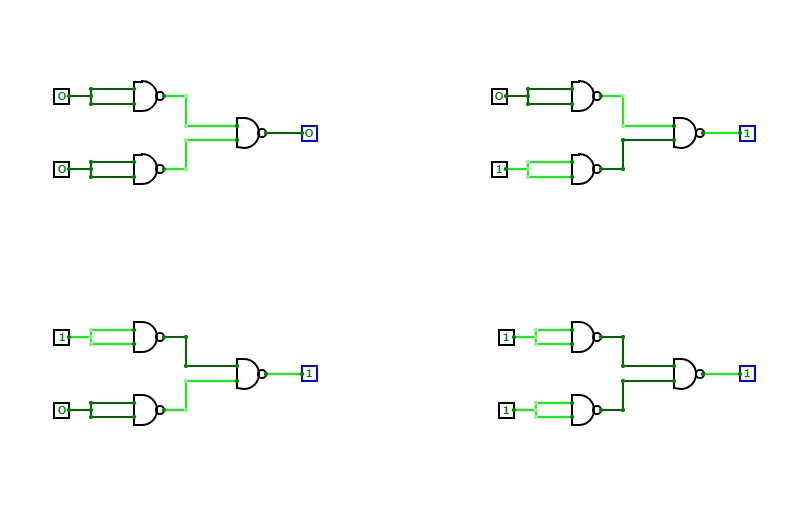

BASIC LOGIC GATES USING NOR GATE

BASIC LOGIC GATES USING NOR GATE

8bit Substractor

8bit Substractor

XNOR from NAND

XNOR from NAND

Full subtractor using NAND gate

Full subtractor using NAND gate

Full adder using NAND Gate

Full adder using NAND Gate

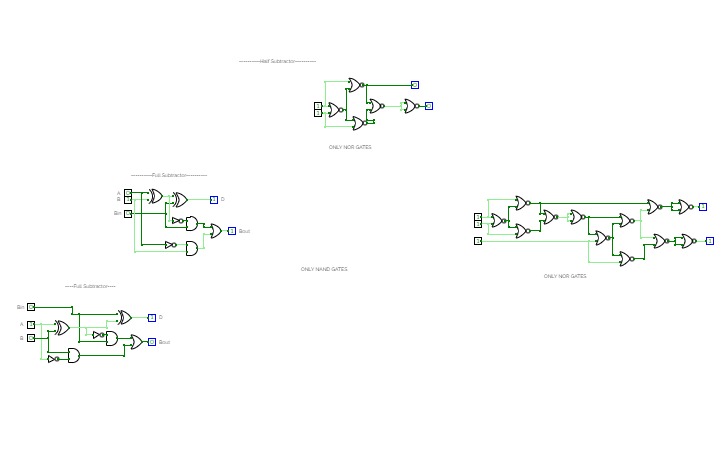

Half Subtractor and Full Subtractor

Half Subtractor and Full Subtractor

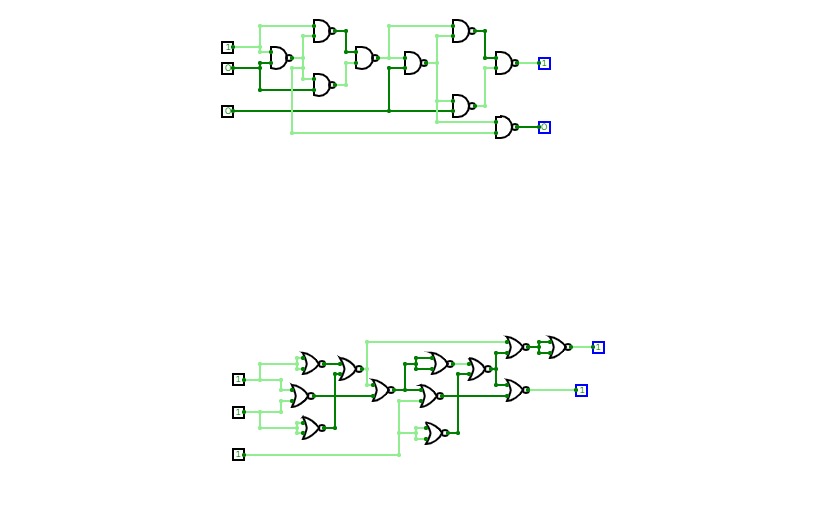

Experiment-2

Experiment-2

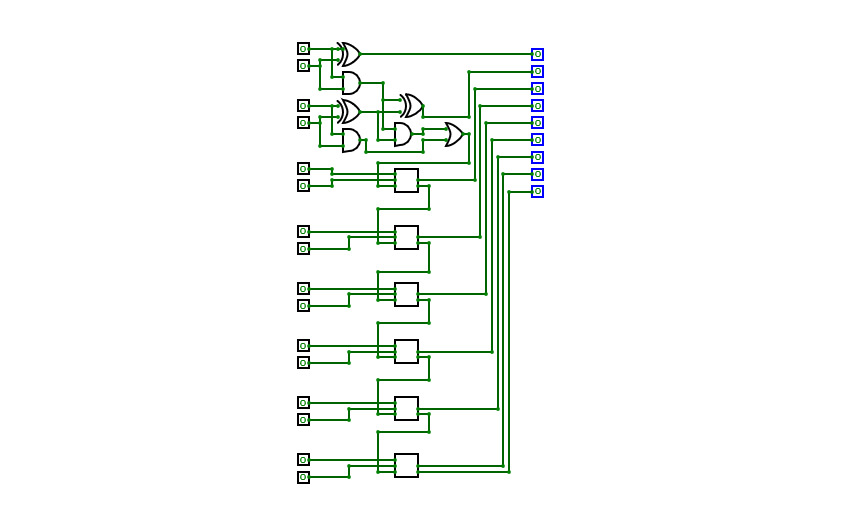

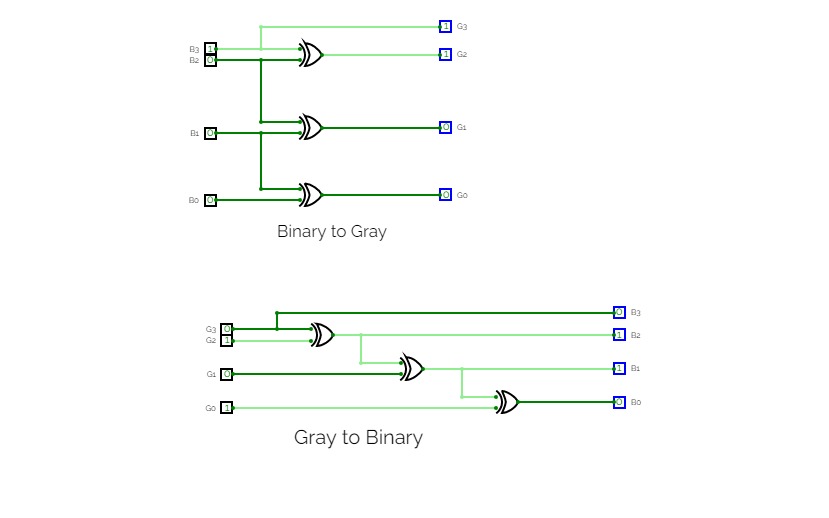

Binary -to -Gray, Gray -to -Binary code converte

Binary -to -Gray, Gray -to -Binary code converte

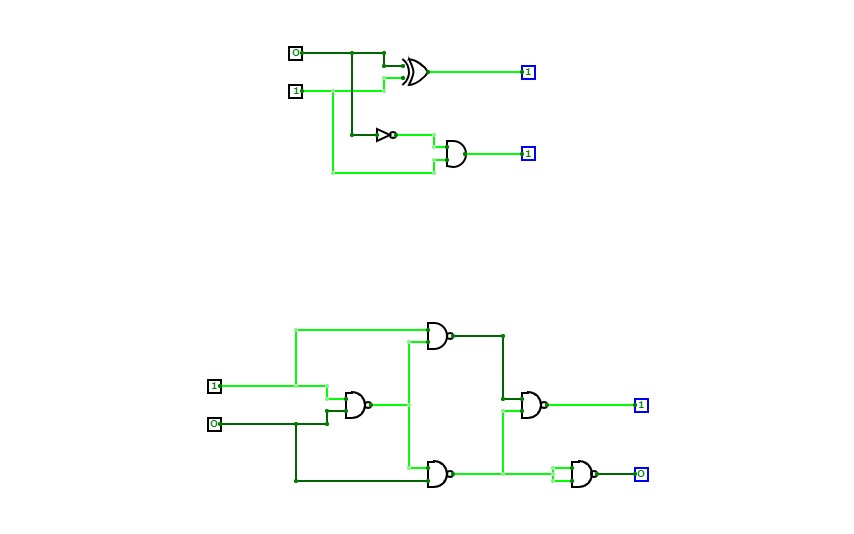

half subtractor

half subtractor

H.A. using nor gate and H.A. using XOR , AND gate

H.A. using nor gate and H.A. using XOR , AND gate

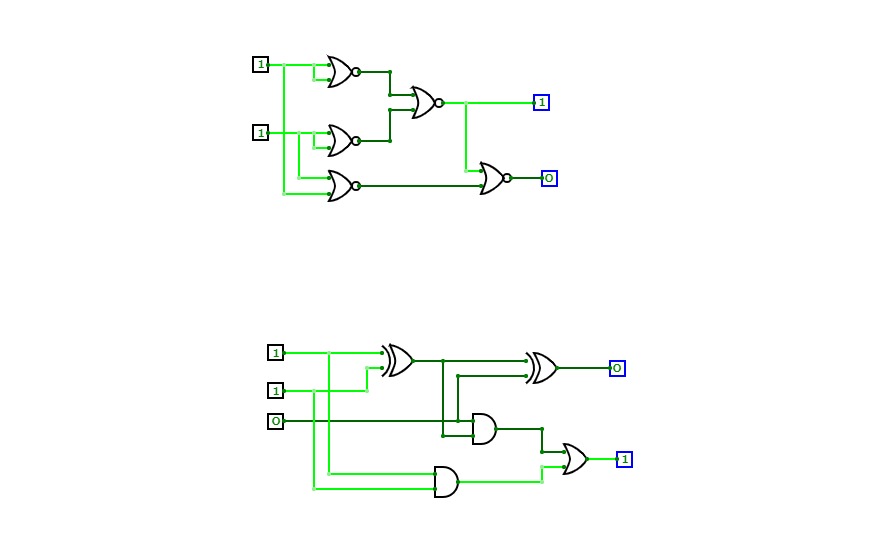

Full Adder using NAND and NOR gates

Full Adder using NAND and NOR gates

Experiment-2

Experiment-2