J.SHRUTHI RANJANI

Member since: 4 years

Educational Institution: Not Entered

Country: Not Entered

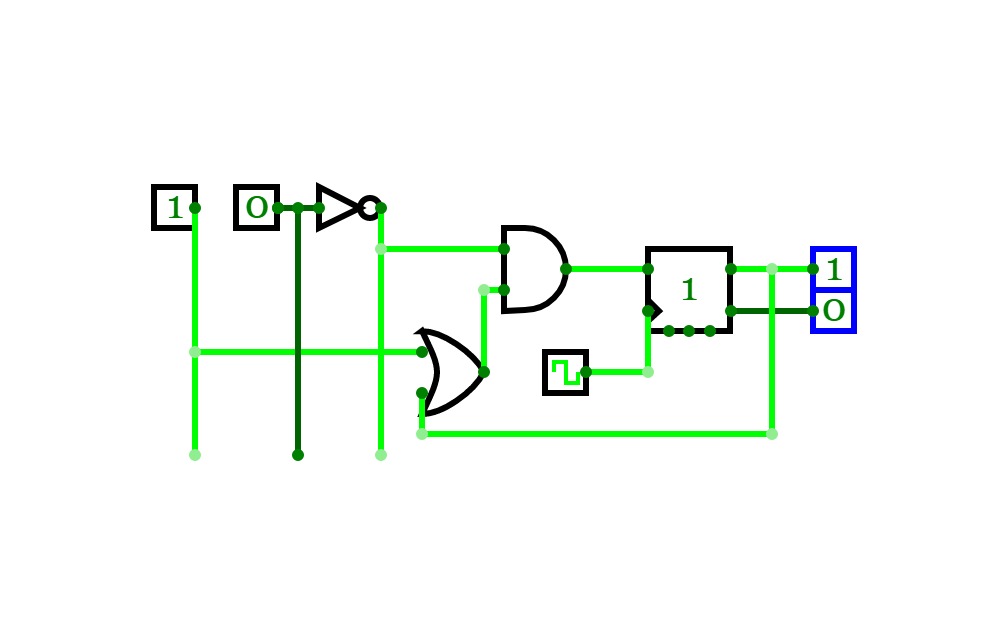

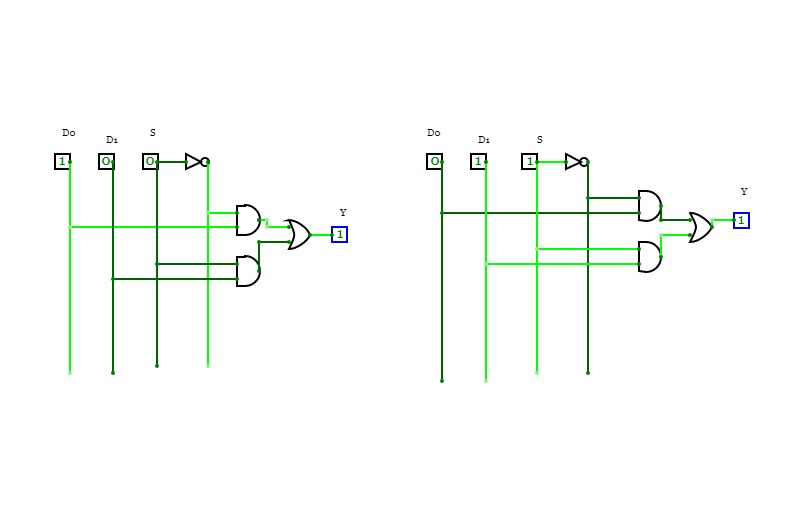

2 TO 1 MUX BY OR GATE

2 TO 1 MUX BY OR GATE

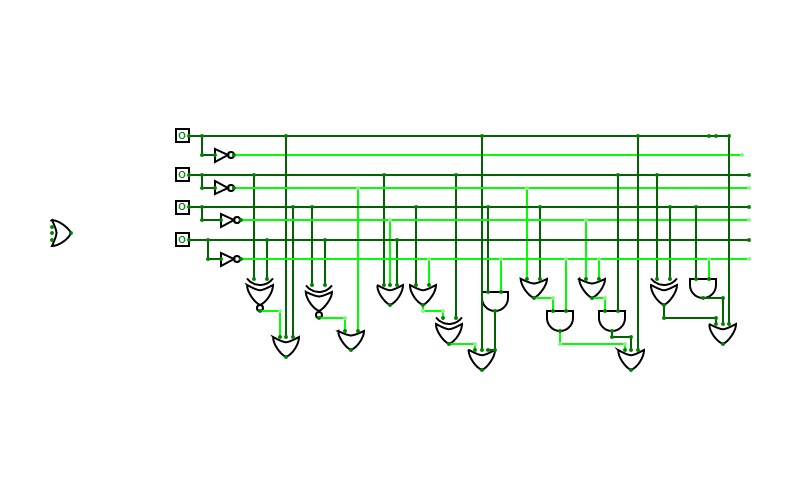

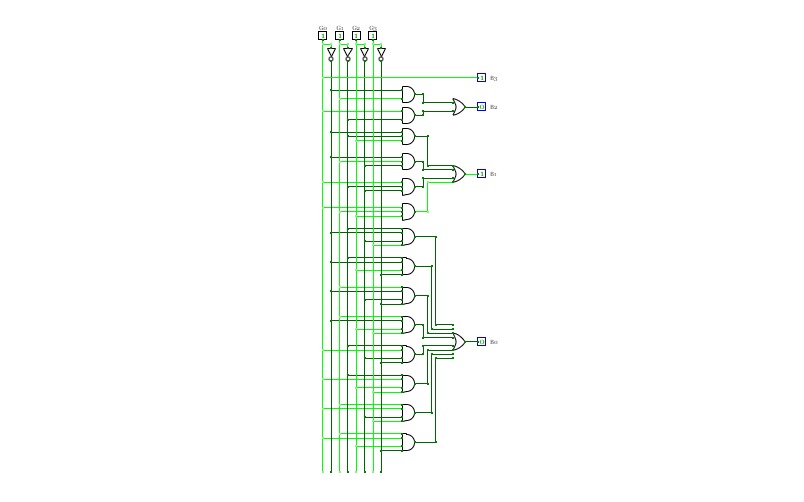

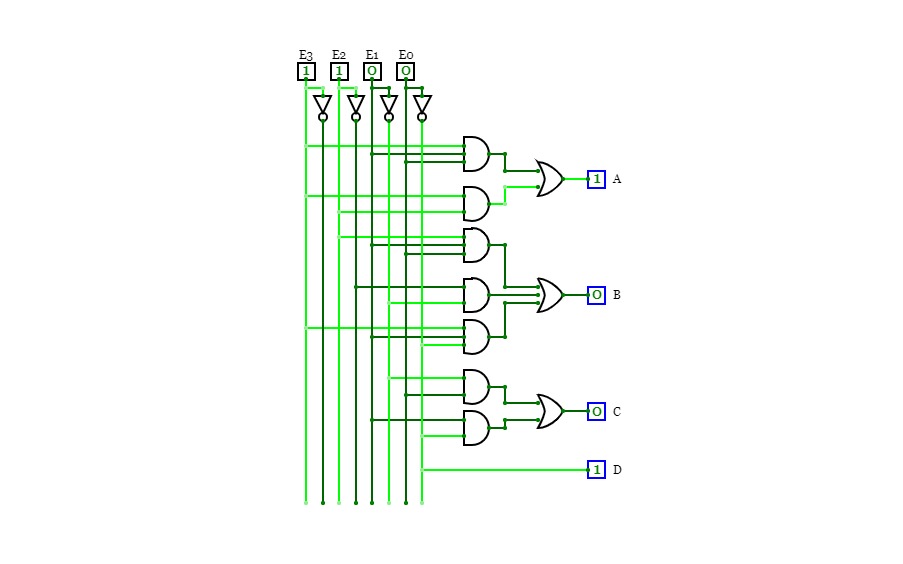

8 T0 3 PRIORITY ENCODER

8 T0 3 PRIORITY ENCODER

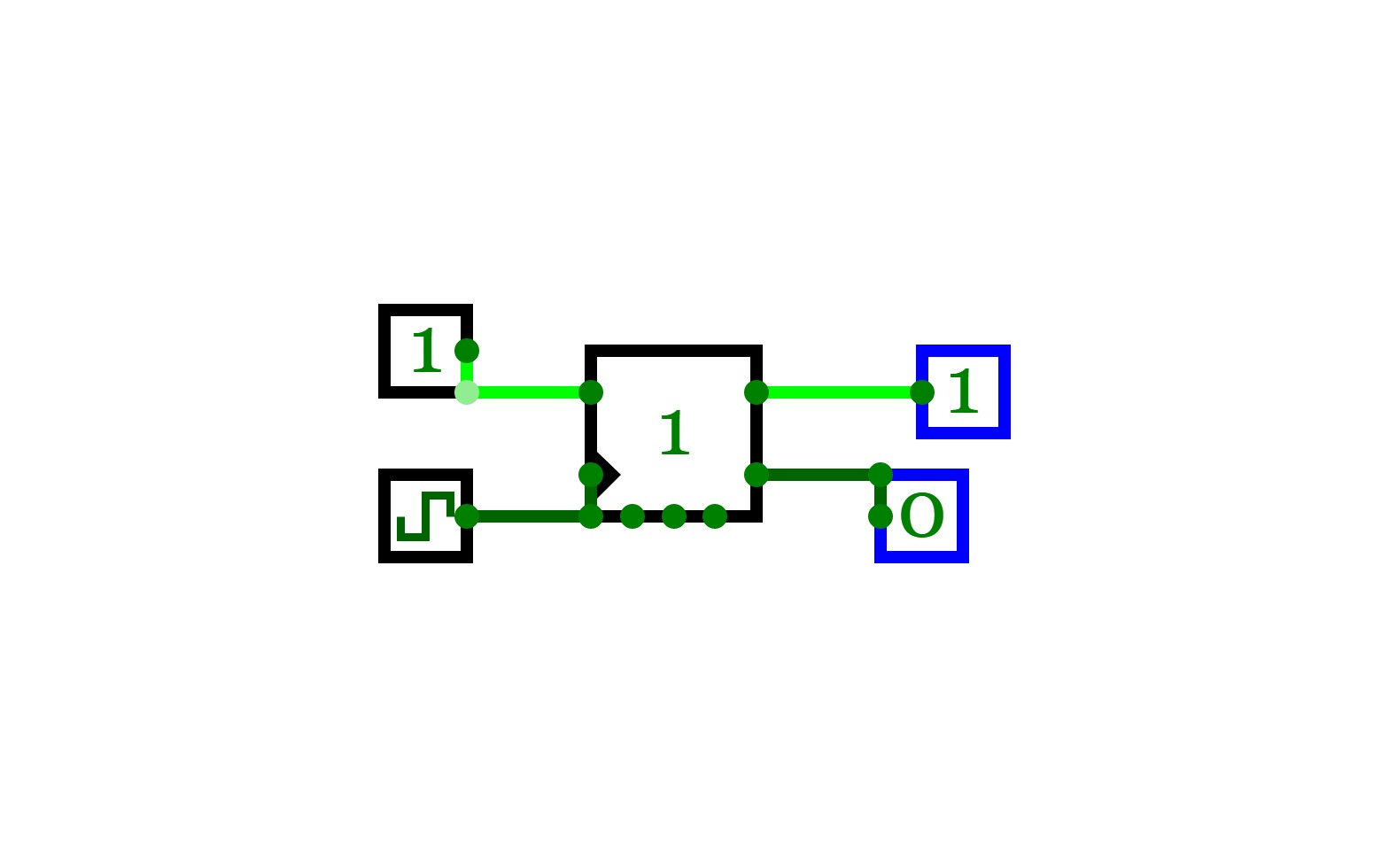

1 to 2 decoder

1 to 2 decoder

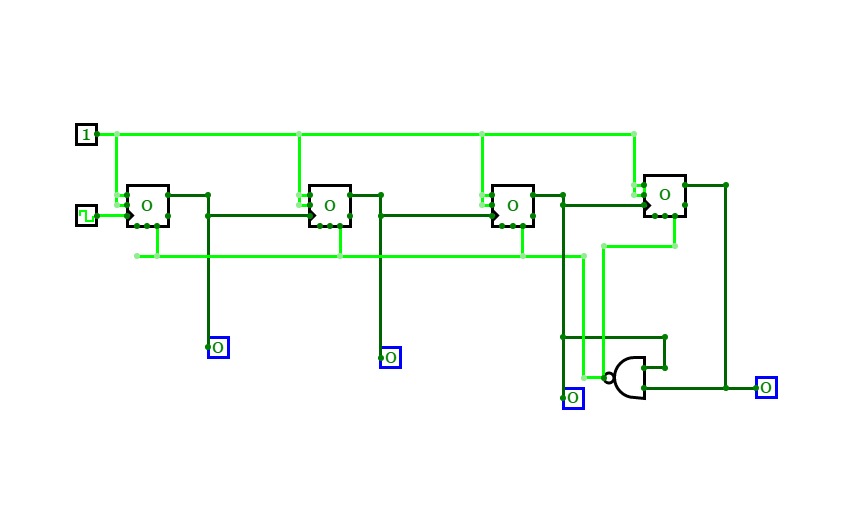

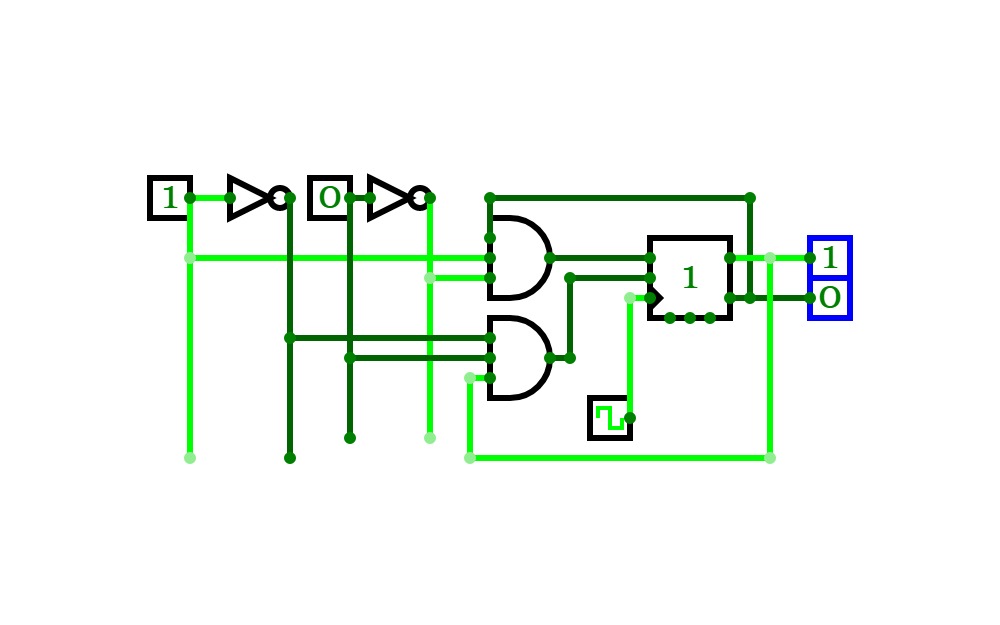

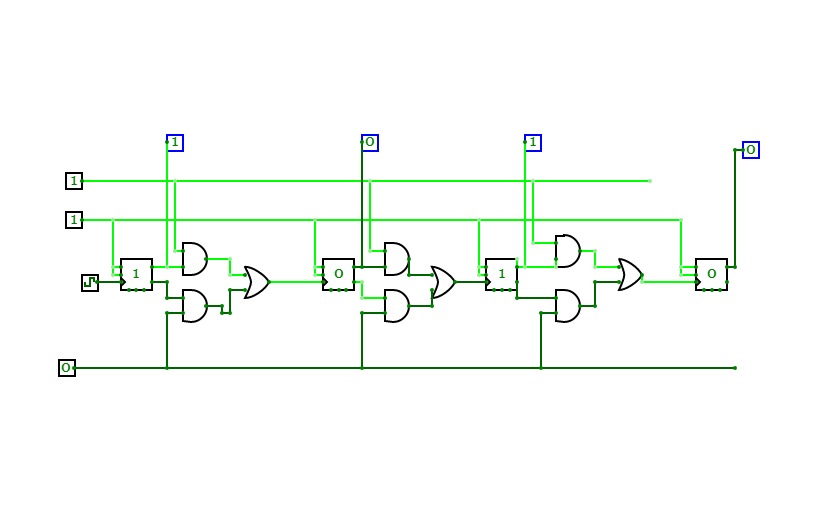

parallel in serial out

parallel in serial out

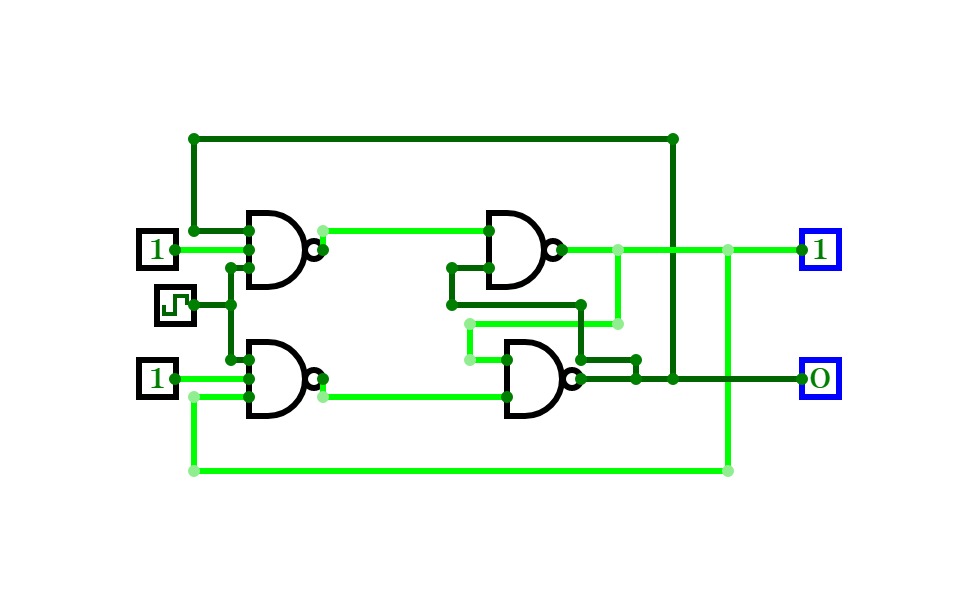

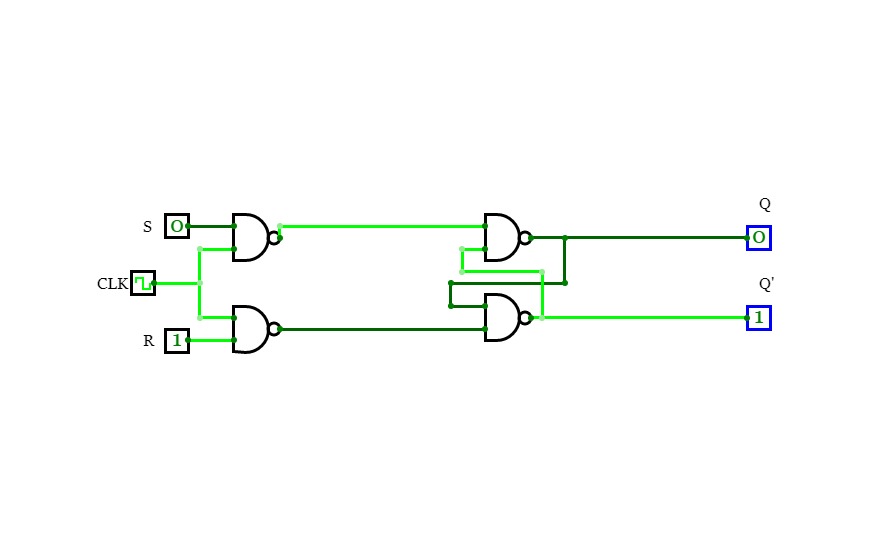

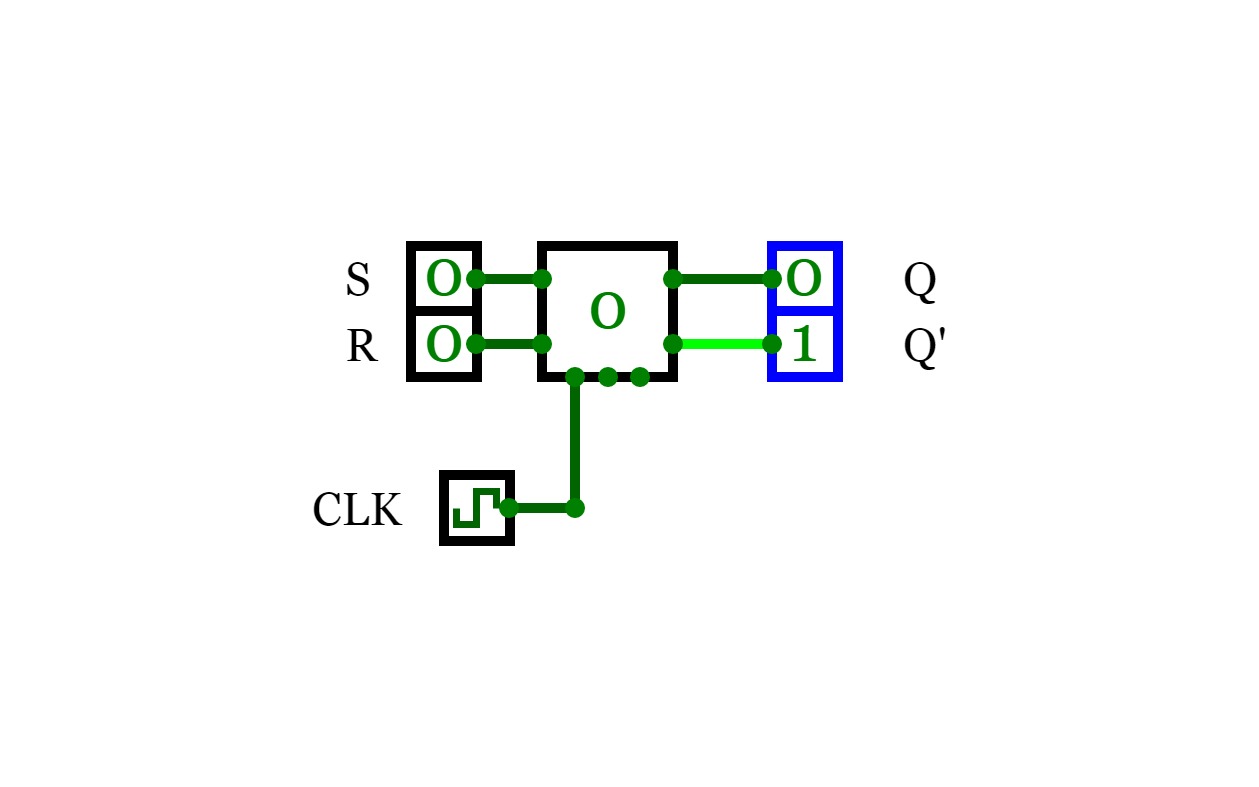

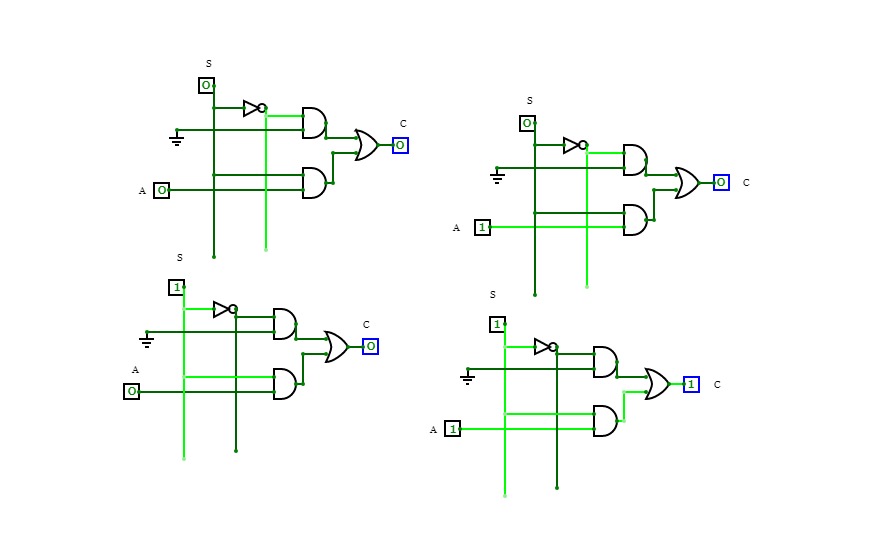

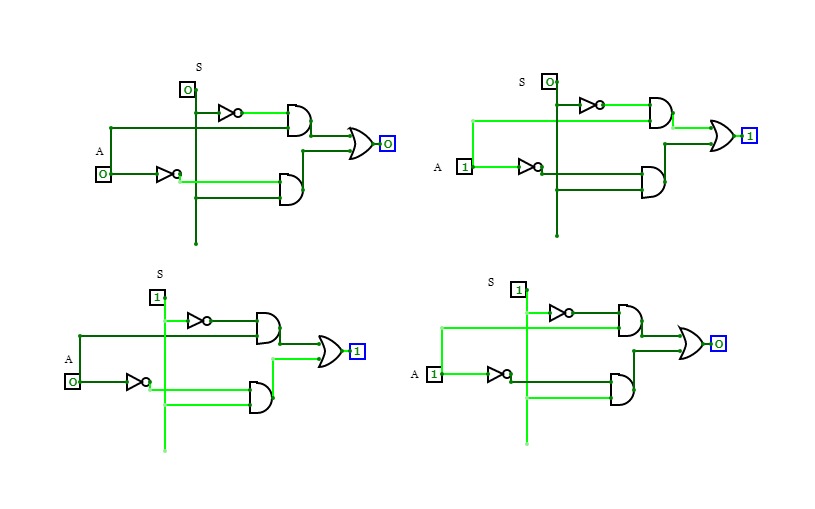

SR FLIPFLOP

SR FLIPFLOP

SR FLIPFLOP

SR FLIPFLOP

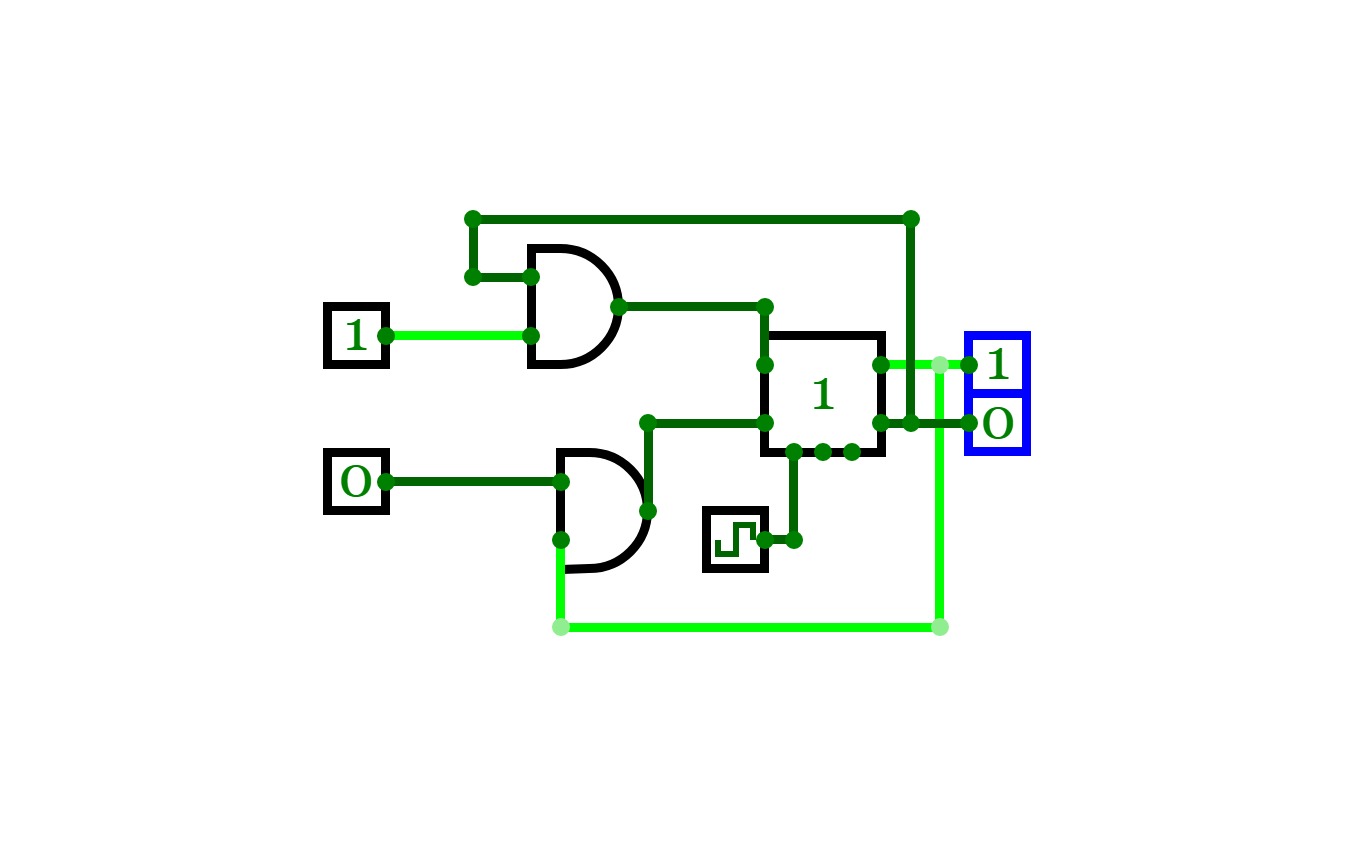

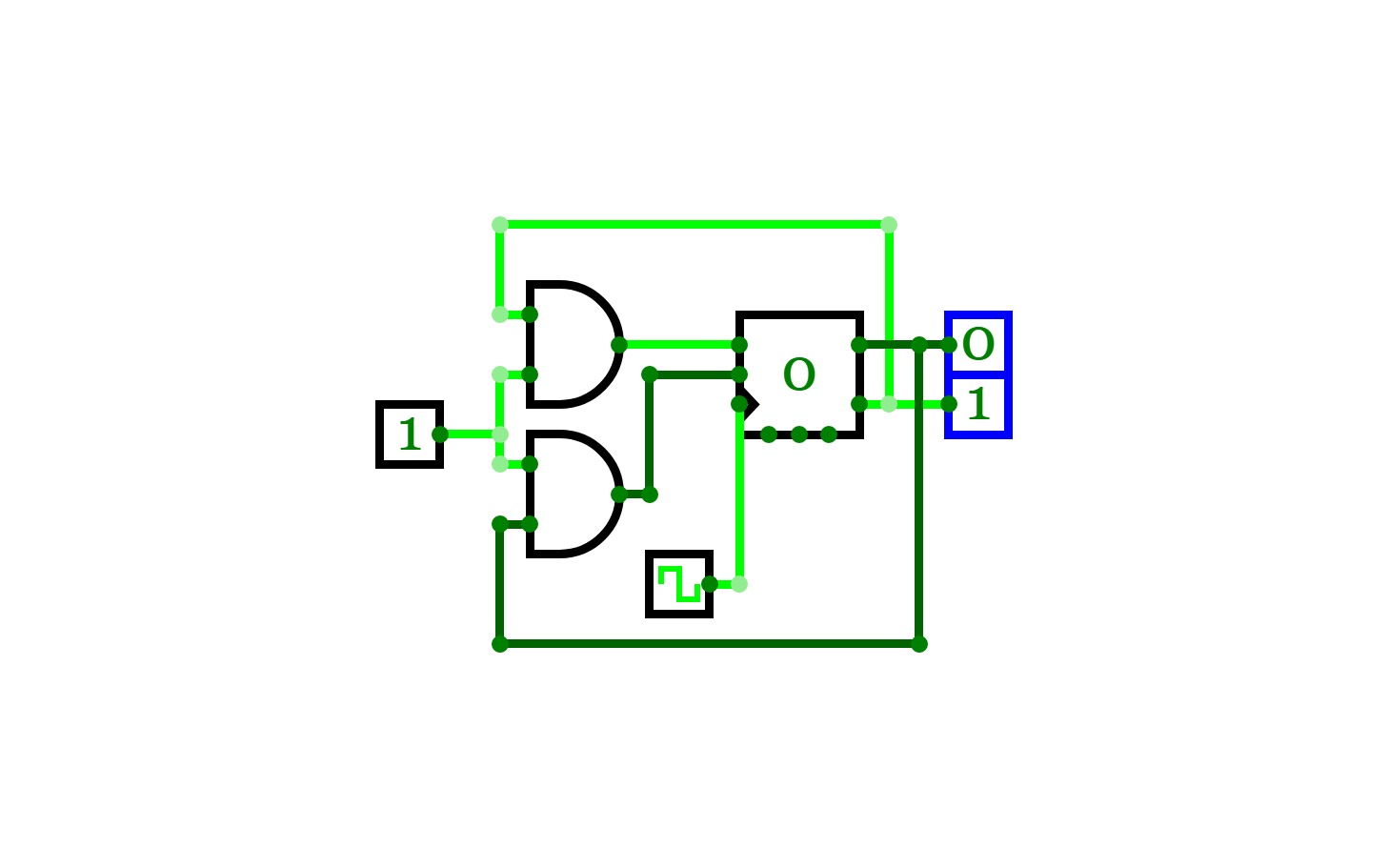

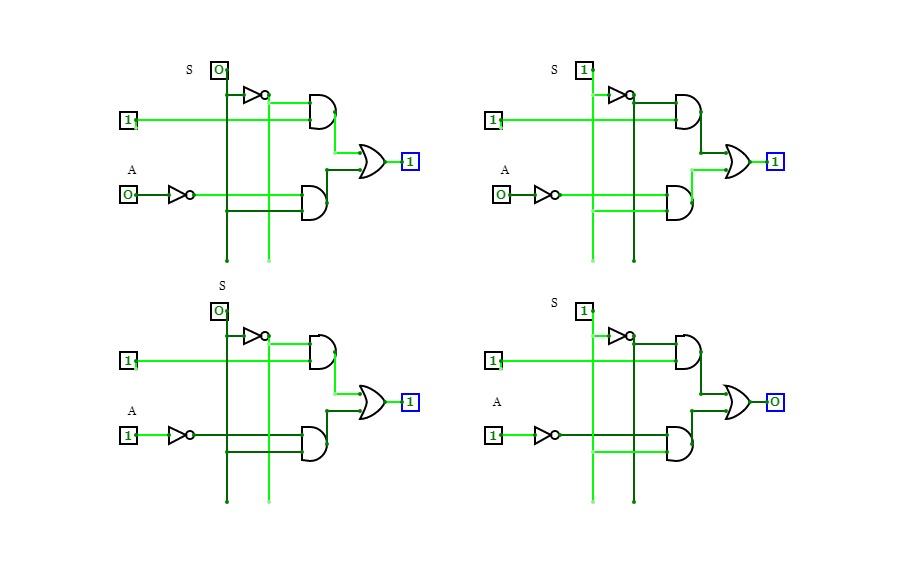

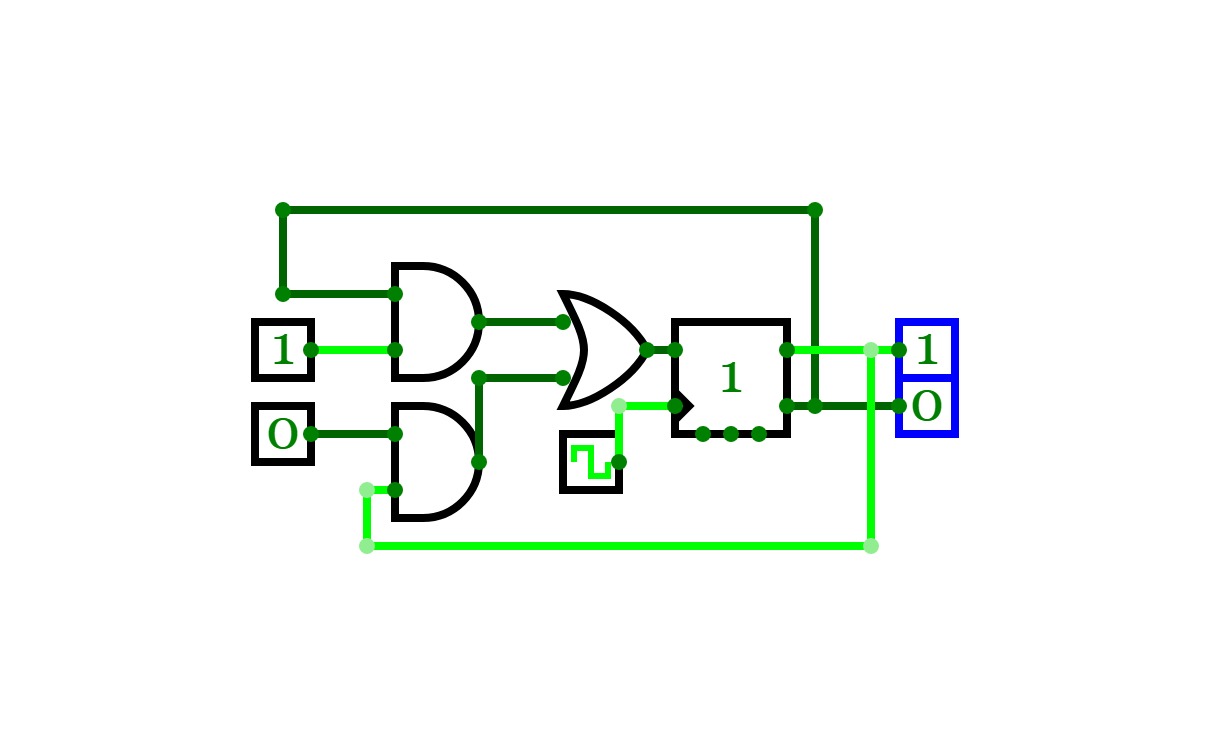

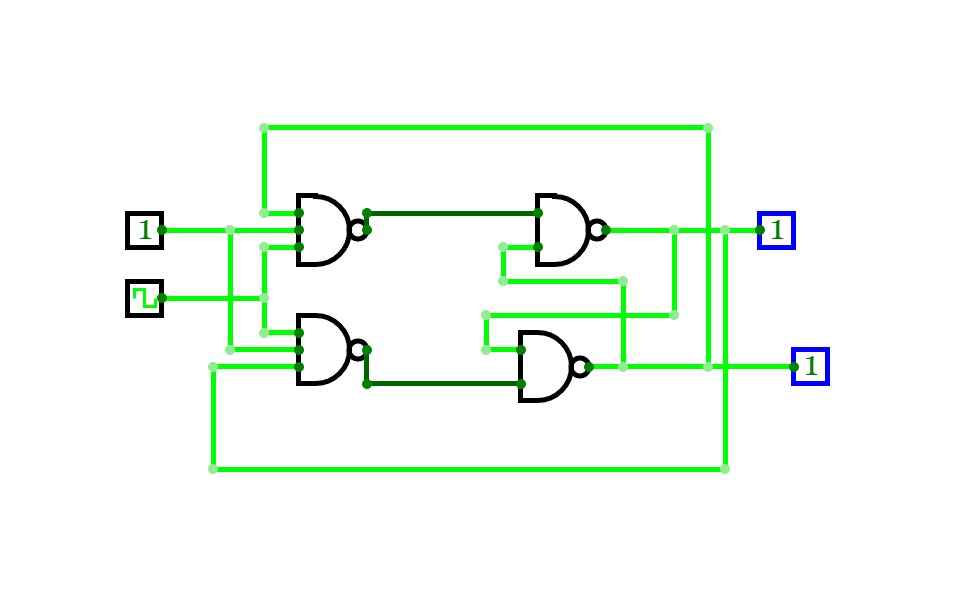

10.JKFF USING SRFF

10.JKFF USING SRFF

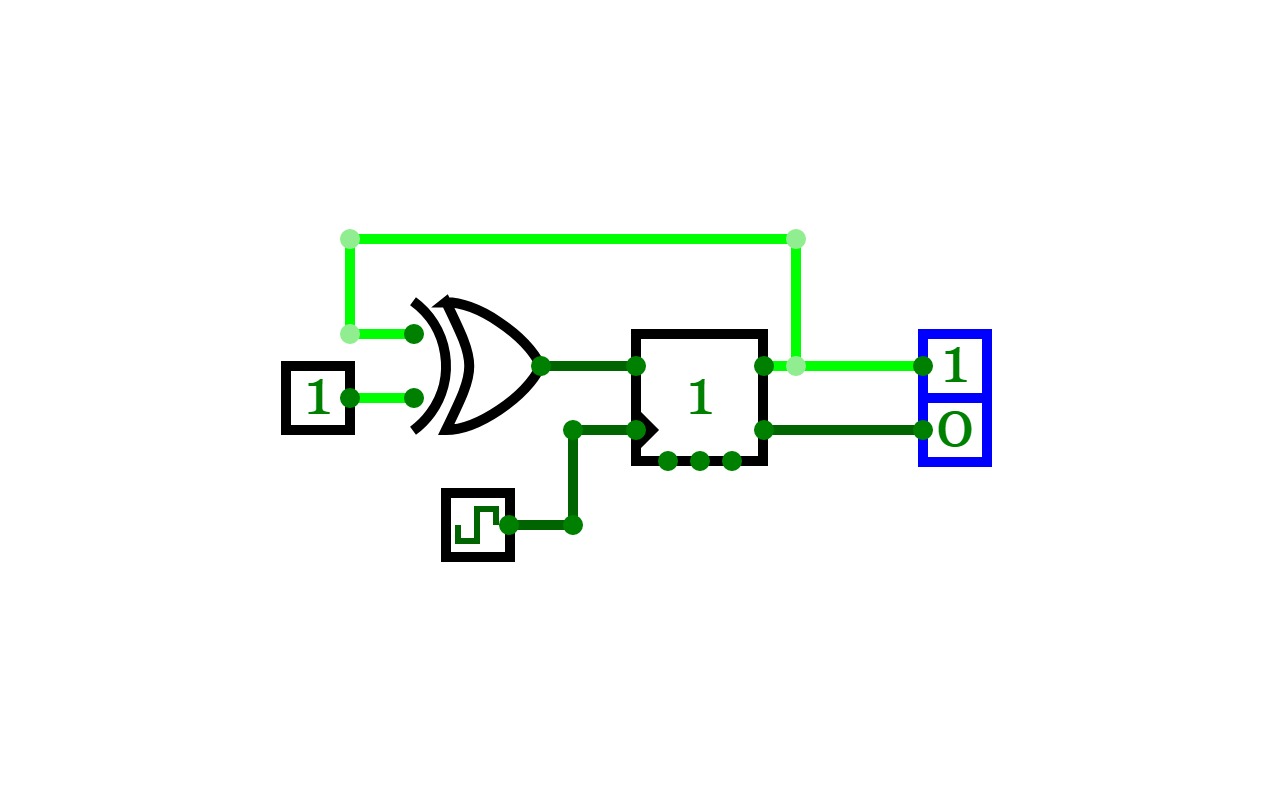

T FLIPFLOP USING INBULIT

T FLIPFLOP USING INBULIT

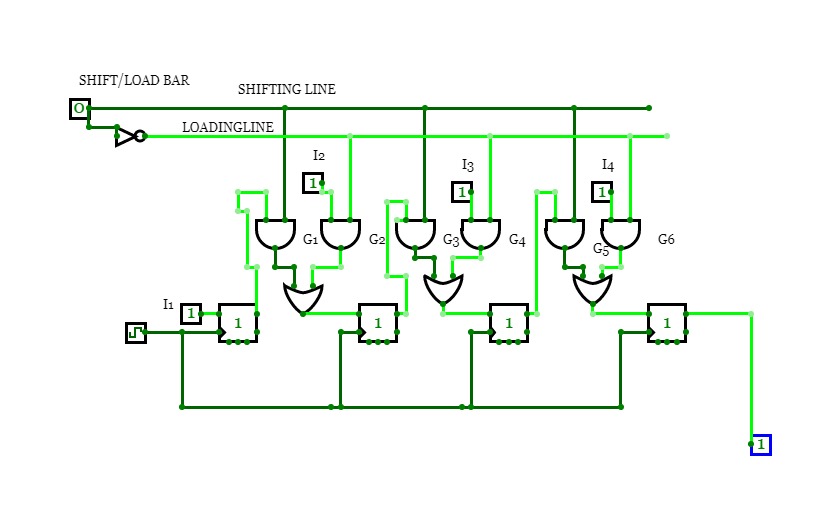

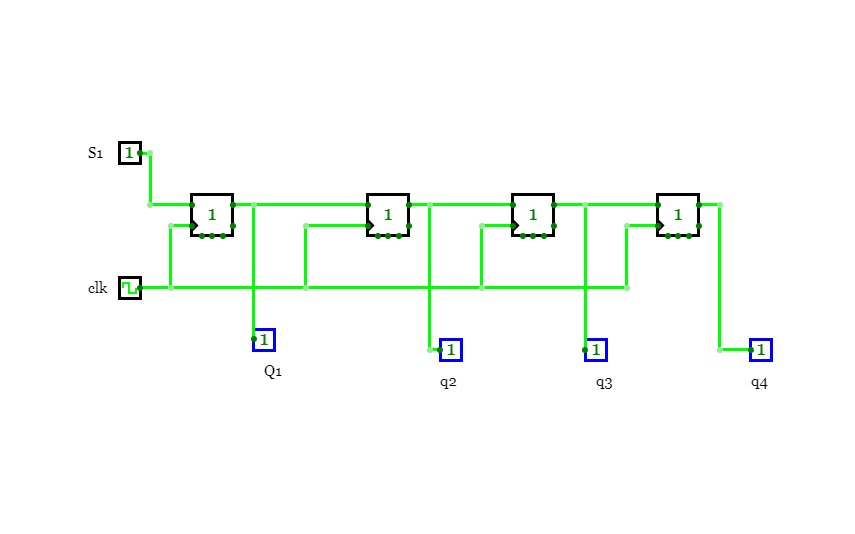

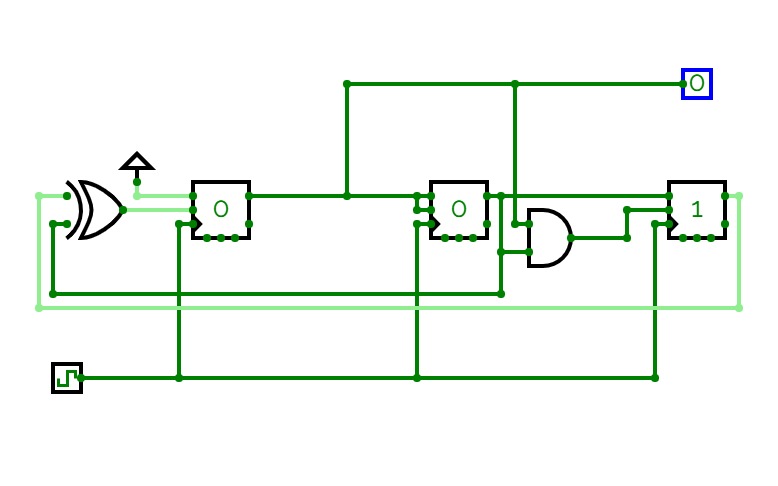

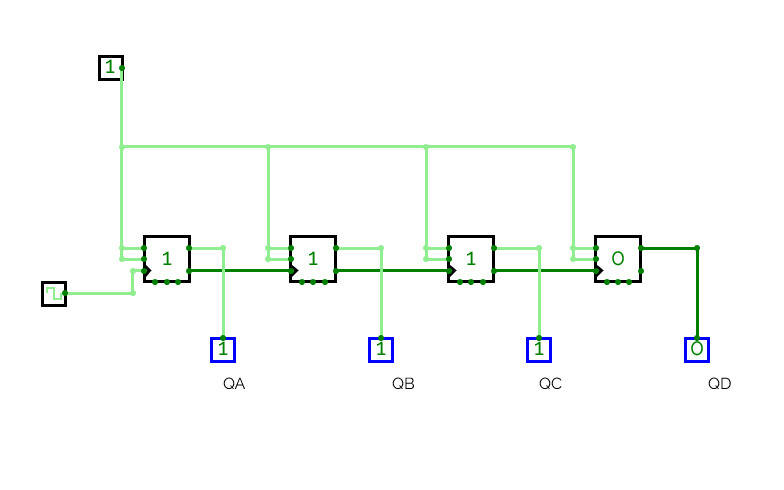

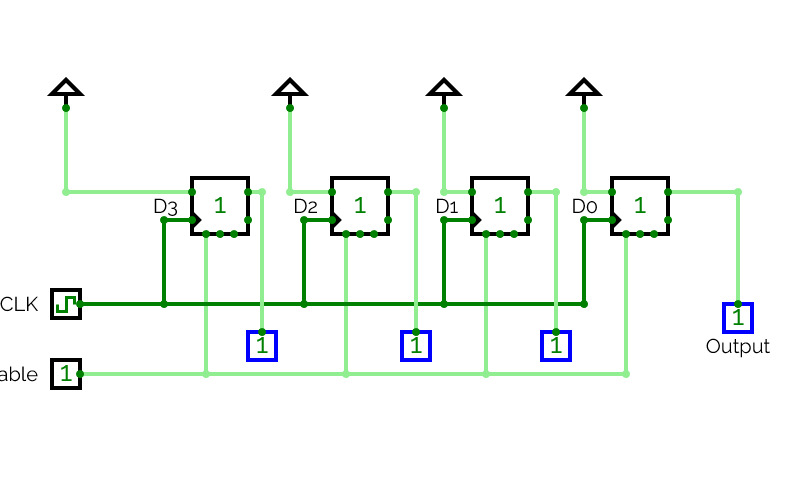

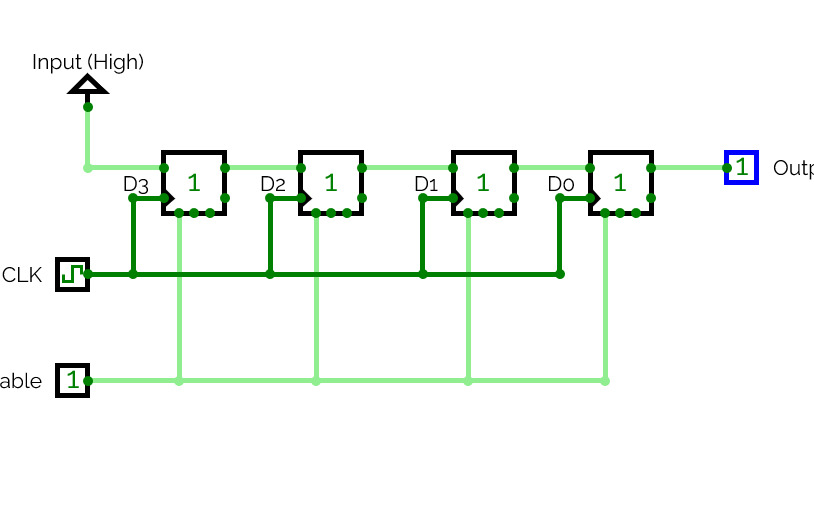

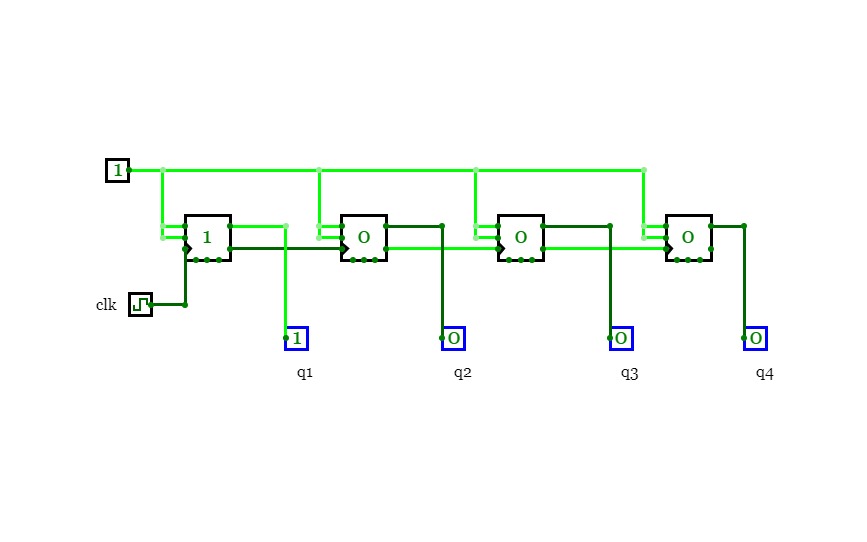

serial in parallel out

serial in parallel out

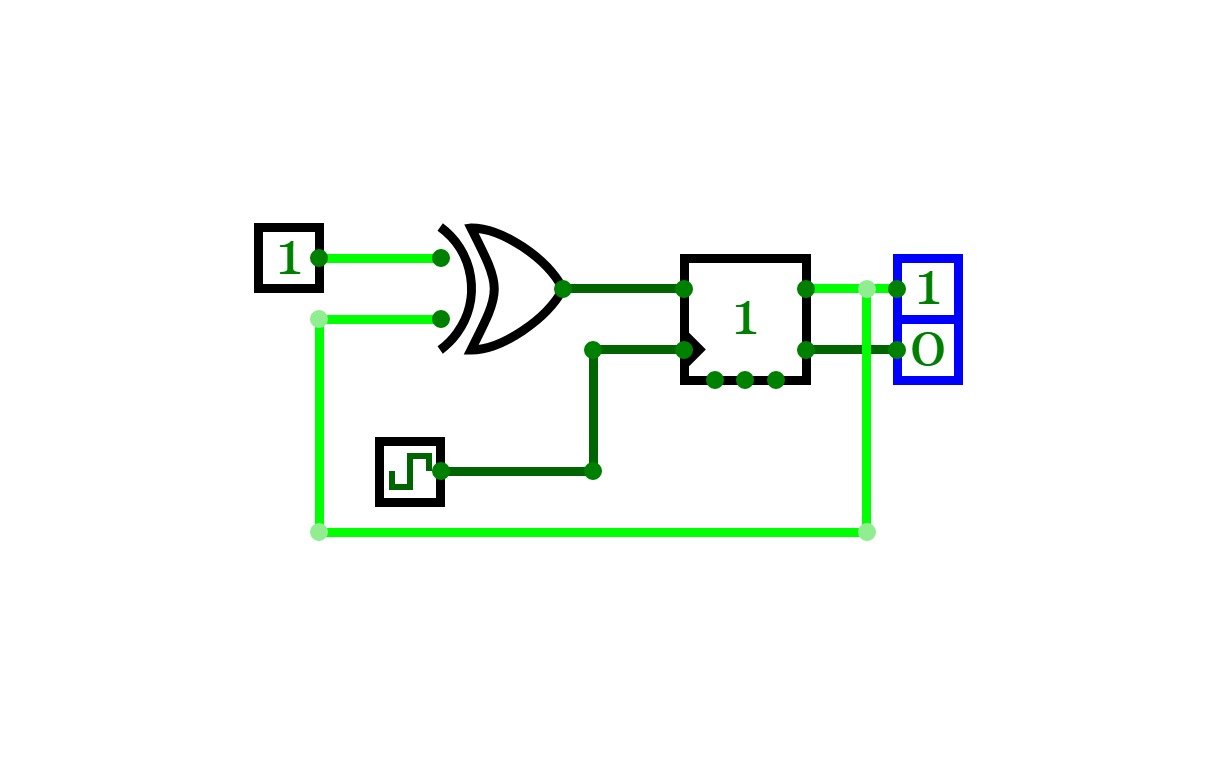

5.TFF USING JKFF

5.TFF USING JKFF

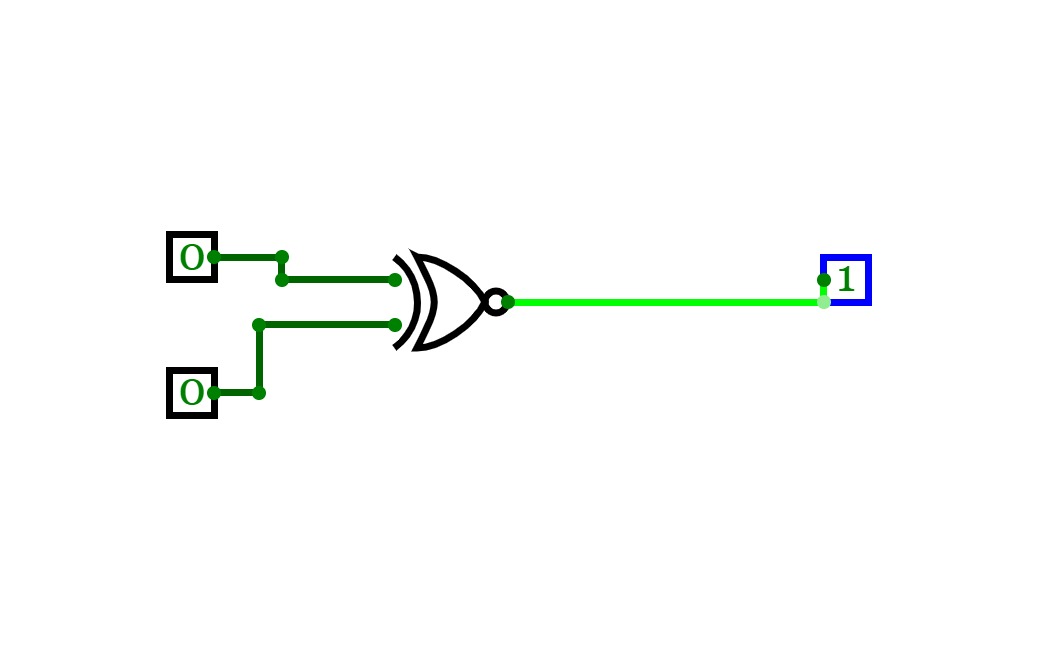

EXNOR

EXNOR

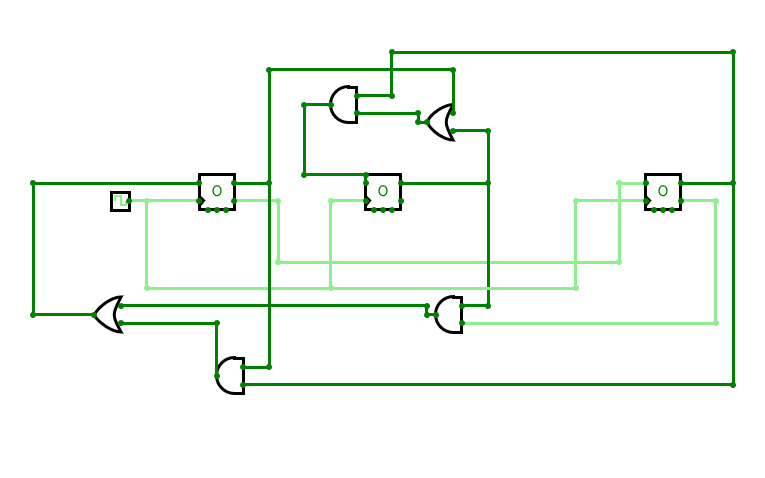

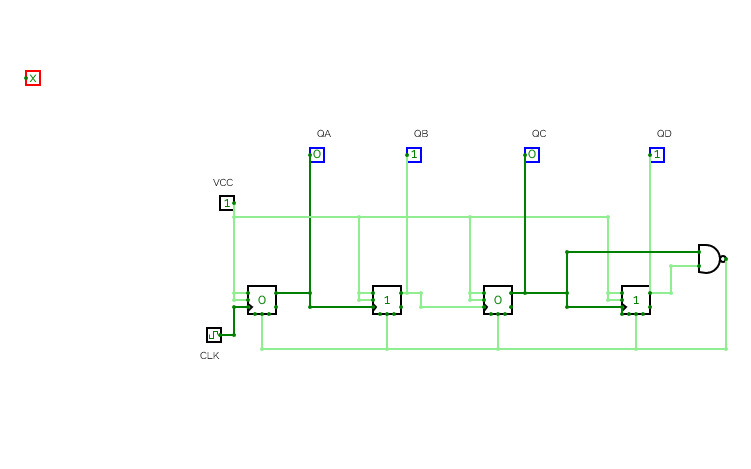

sequence generator using counter

sequence generator using counter

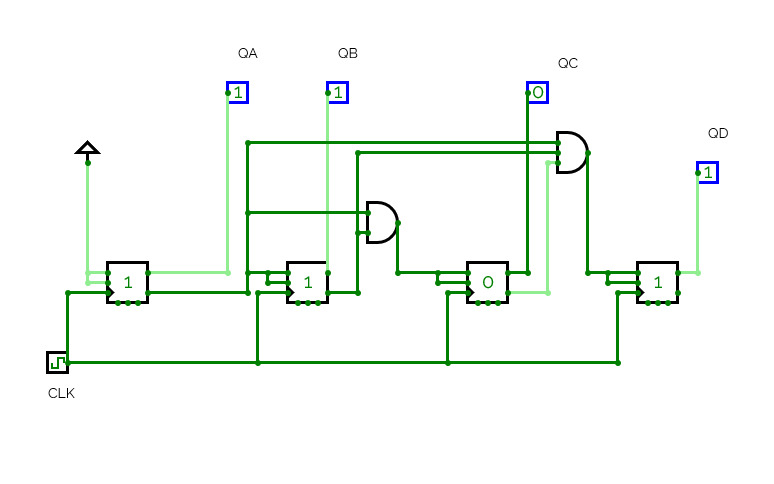

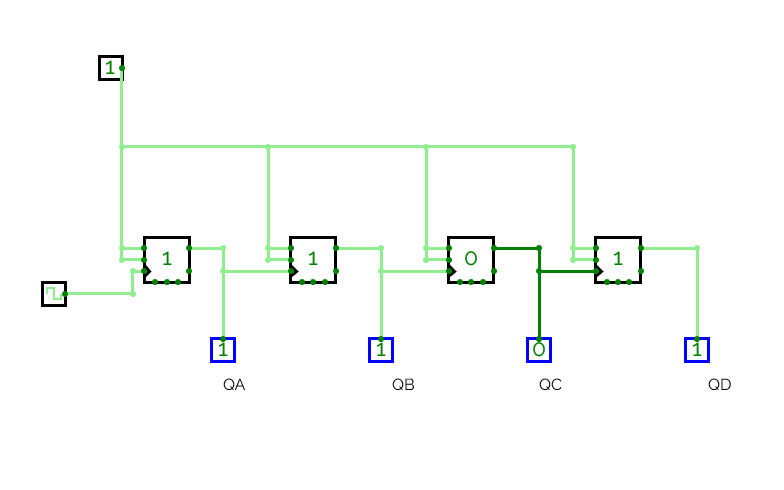

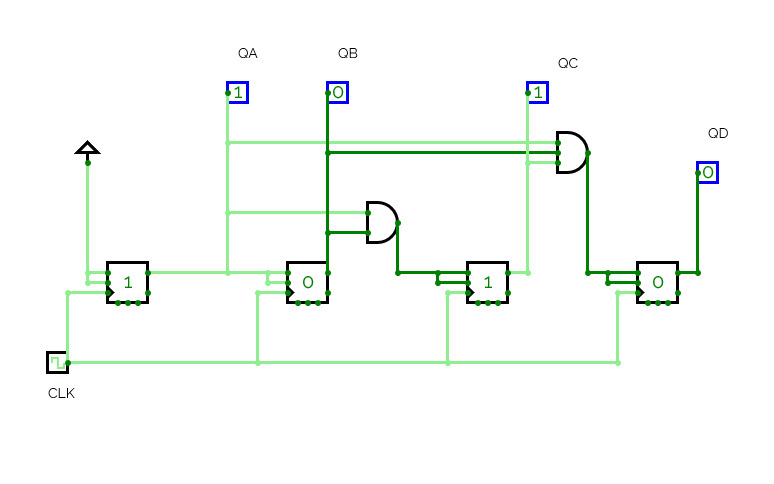

4 bit synchronous down counter

4 bit synchronous down counter

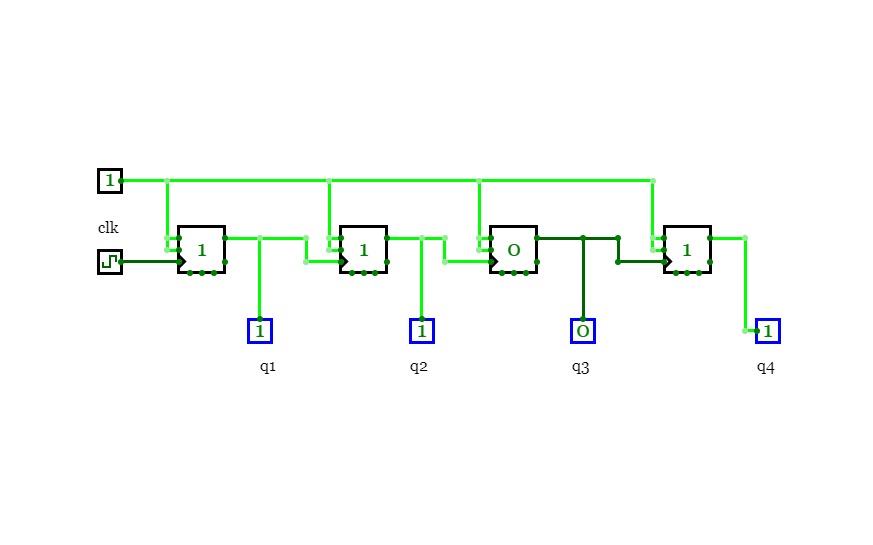

4 bit ripple up counter

4 bit ripple up counter

DFF USING SRFF

DFF USING SRFF

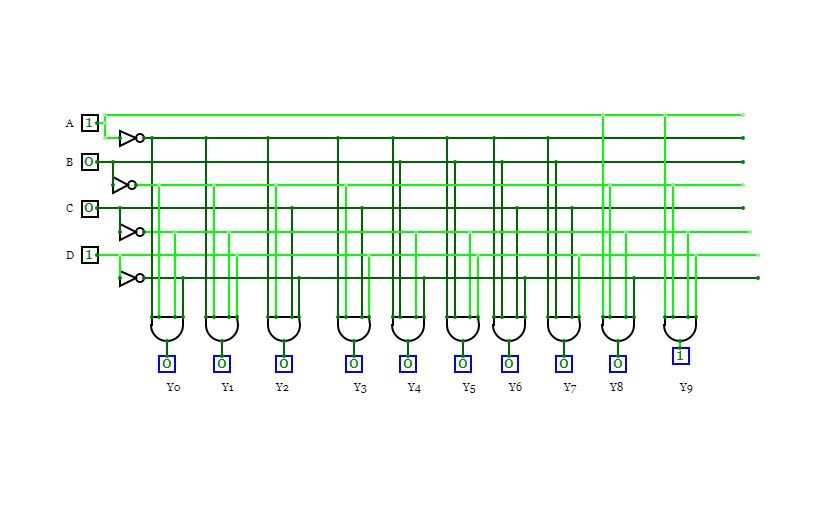

BCD TO DECIMAL DECODER

BCD TO DECIMAL DECODER

mod 12 counter

mod 12 counter

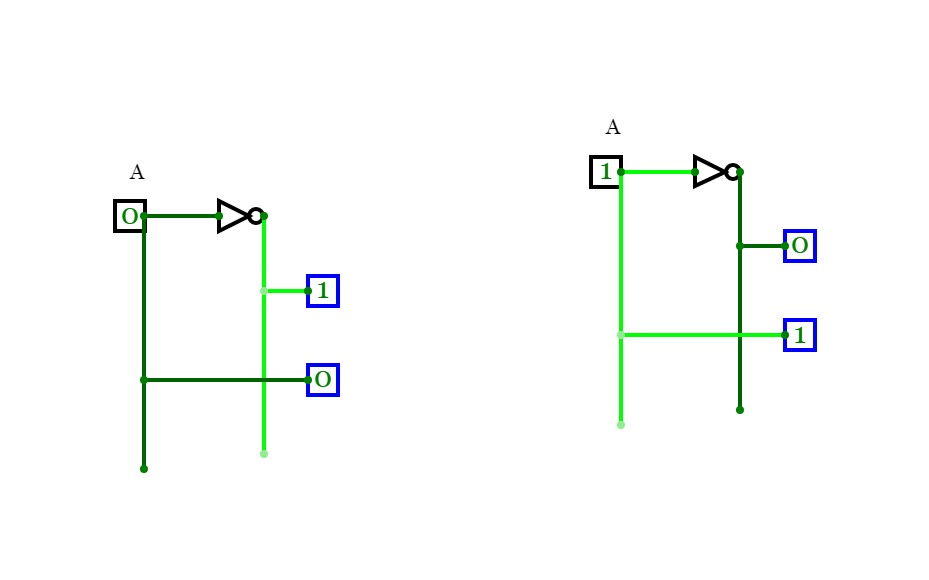

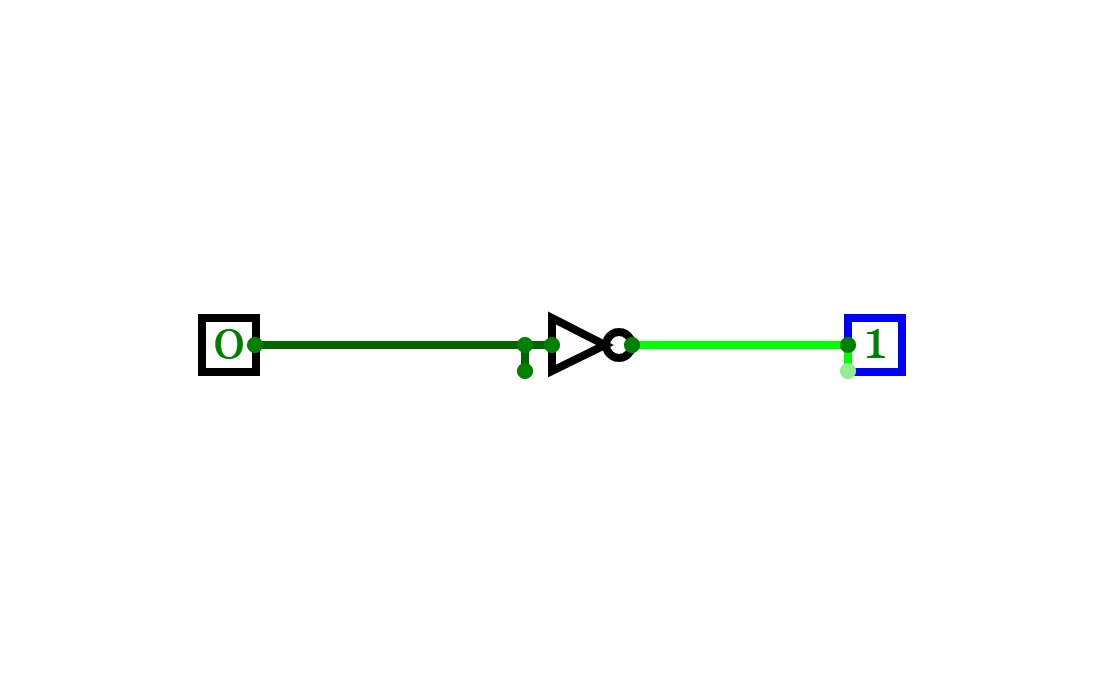

NOT GATE

NOT GATE

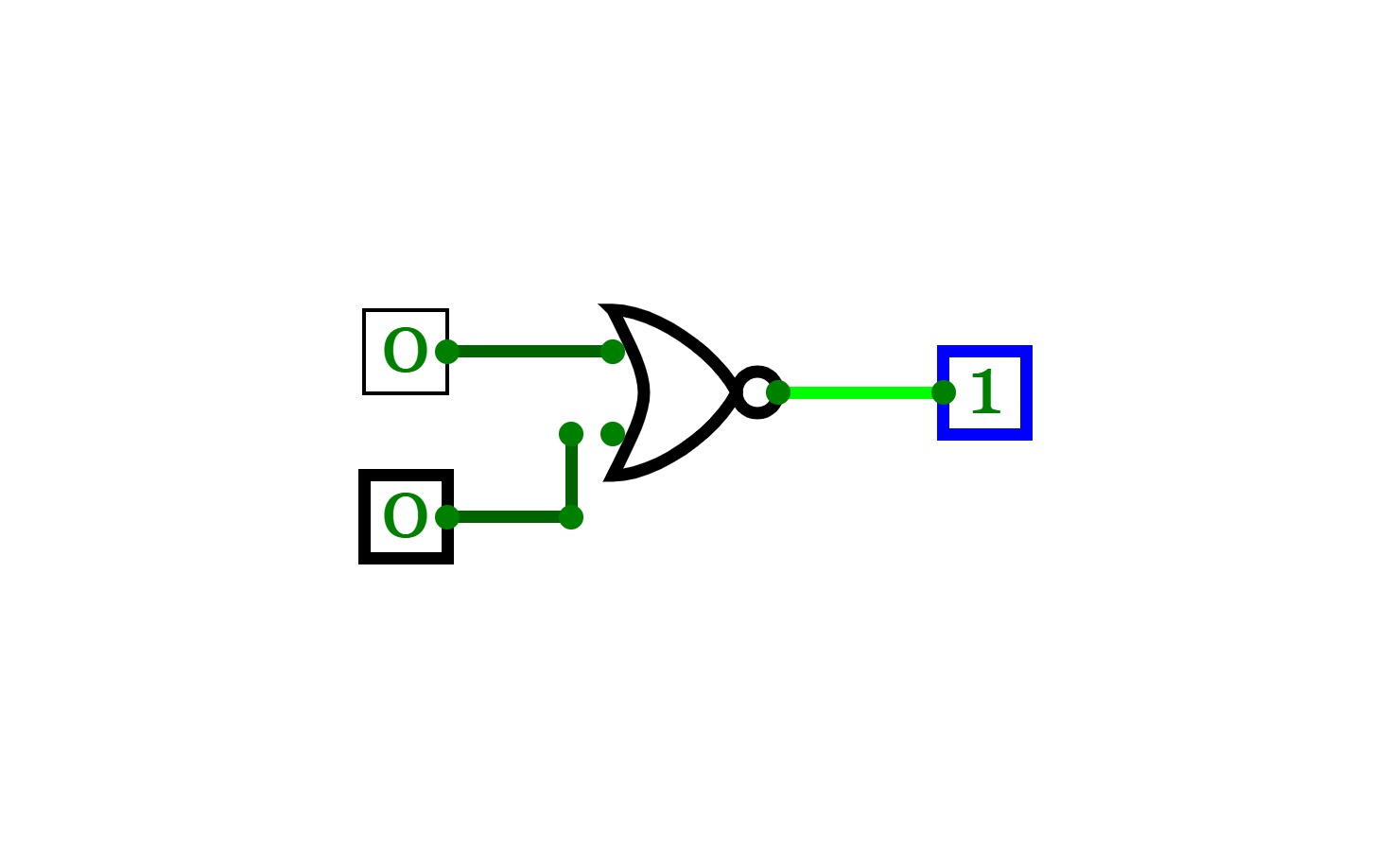

NOR GATE

NOR GATE

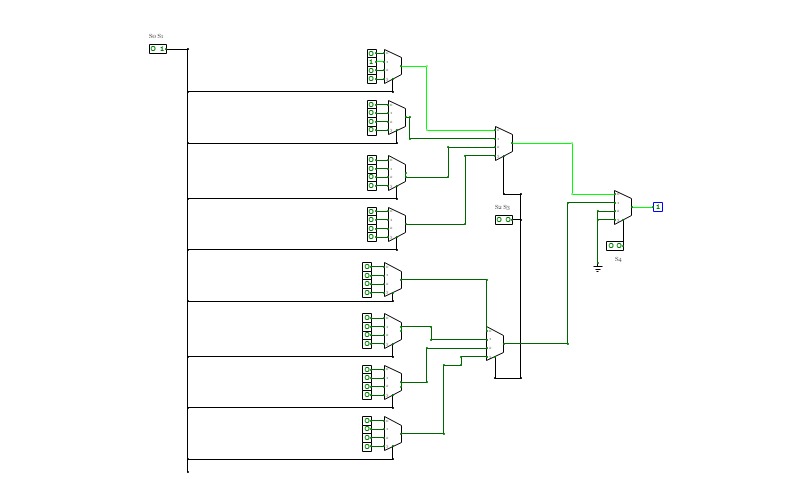

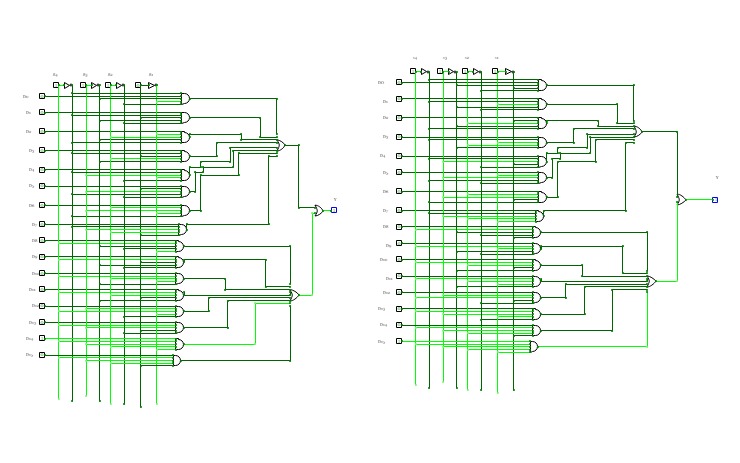

32 to 1 mux using 4 to 1 mux

32 to 1 mux using 4 to 1 mux

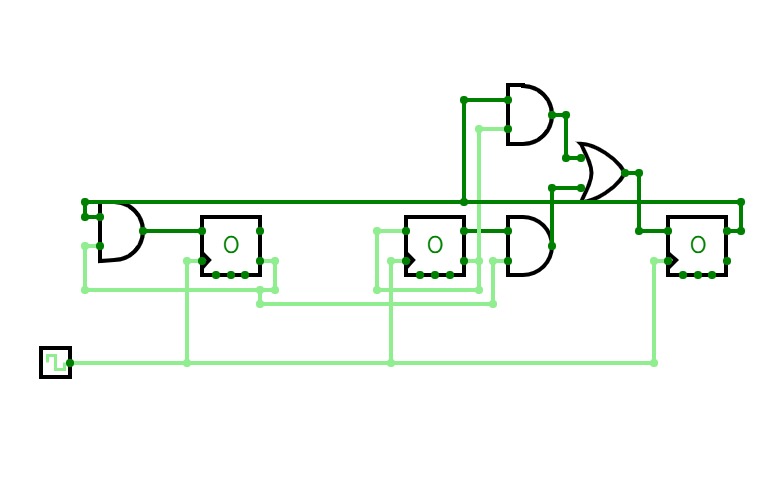

4 bit ripple down counter

4 bit ripple down counter

6.TFF USING DFF

6.TFF USING DFF

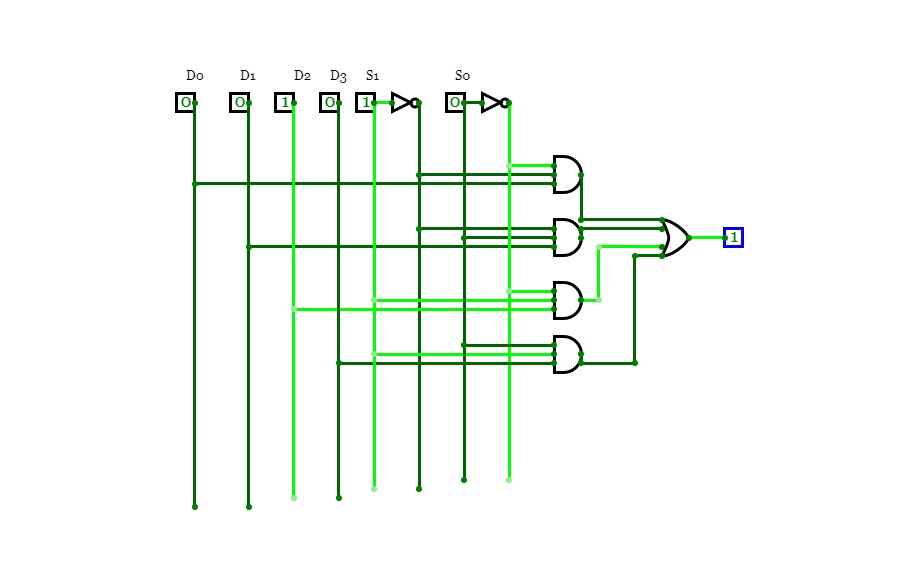

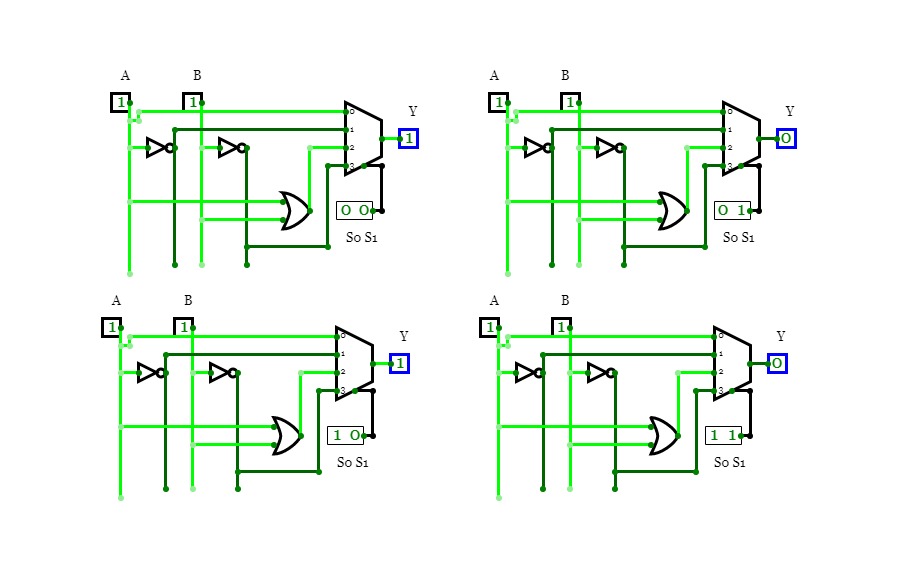

4 to 1 mux

4 to 1 mux

4 bit ripple counter

4 bit ripple counter

PIPO

PIPO

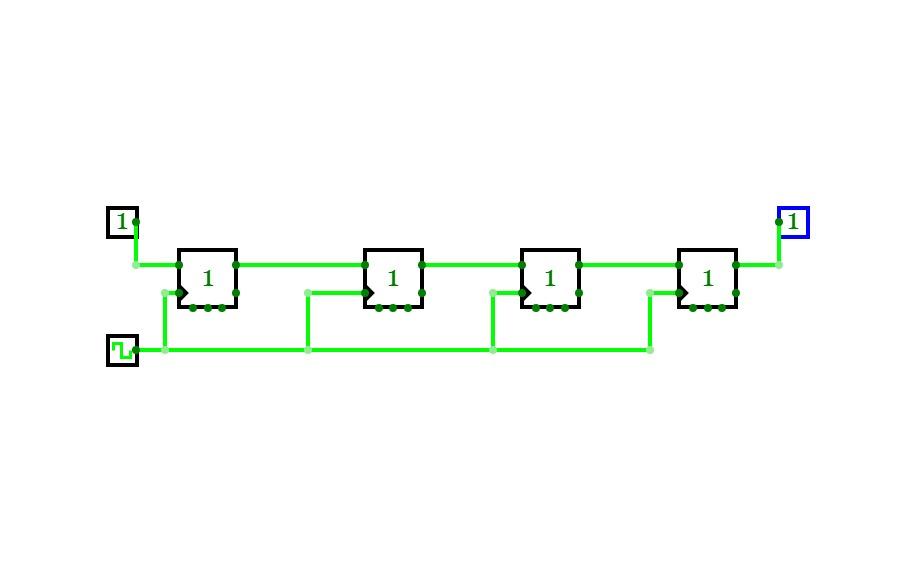

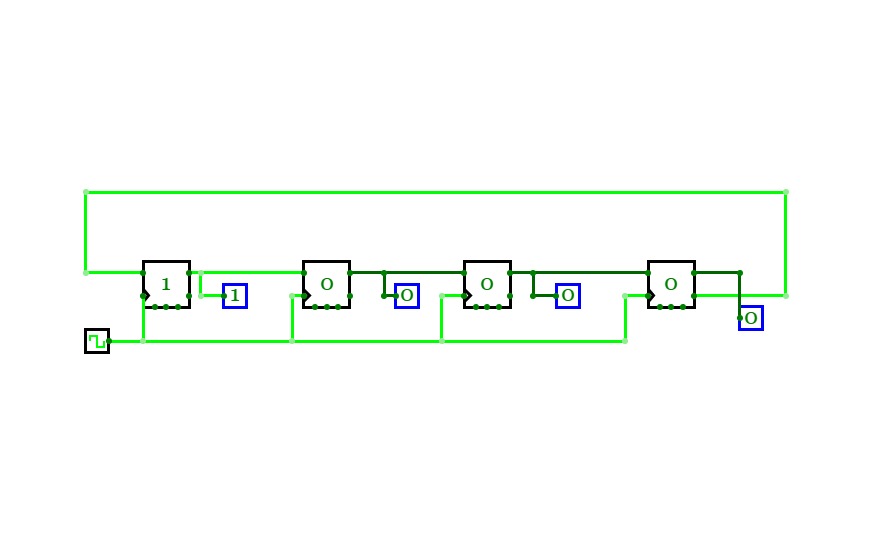

serial in serial out

serial in serial out

BCD TO EXCESS 3 COVERTOR

BCD TO EXCESS 3 COVERTOR

Untitled

Untitled

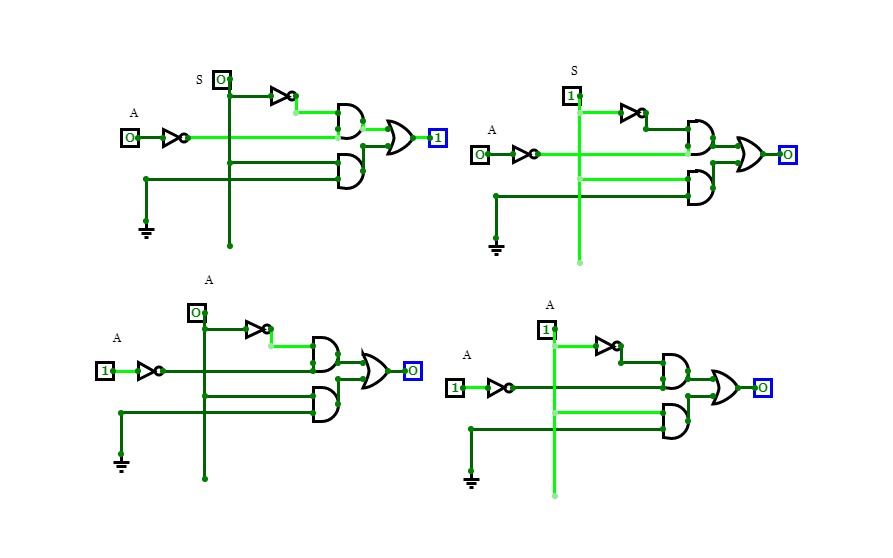

2 TO 1 MUX BY AND GATE

2 TO 1 MUX BY AND GATE

2 TO 1 MUX BY NAND GATE

2 TO 1 MUX BY NAND GATE

2 TO 1 MUX BY NOT GATE

2 TO 1 MUX BY NOT GATE

2 TO 1 MUX BY NOR GATE

2 TO 1 MUX BY NOR GATE

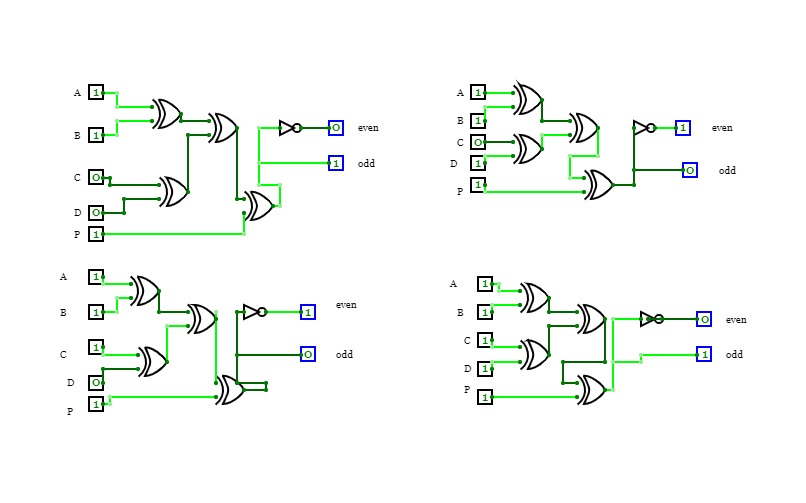

4 BIT PARITY CHECKER AND GENERATOR

4 BIT PARITY CHECKER AND GENERATOR

16 to 1 mux

16 to 1 mux

SISO

SISO

Untitled

Untitled

Untitled

Untitled

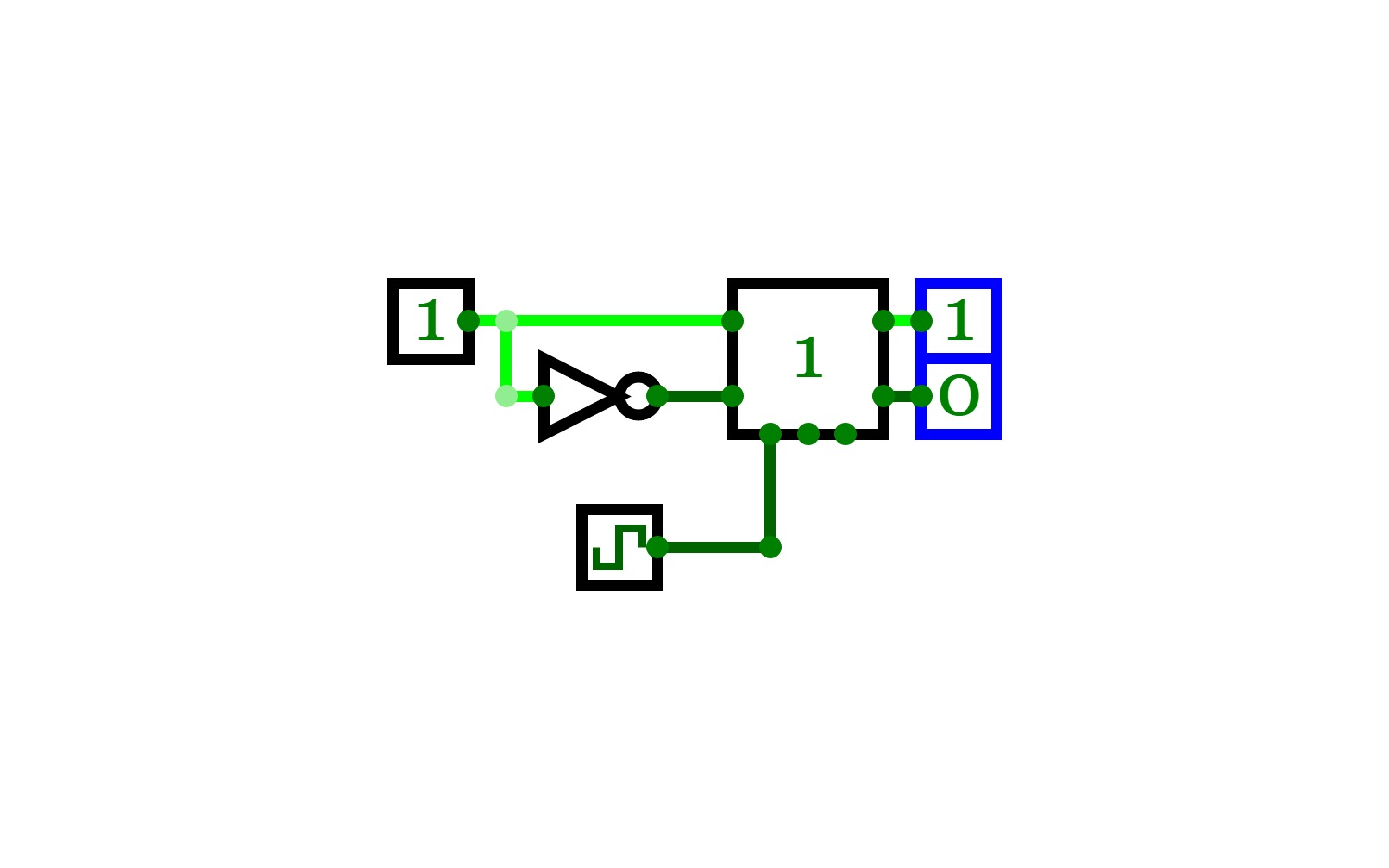

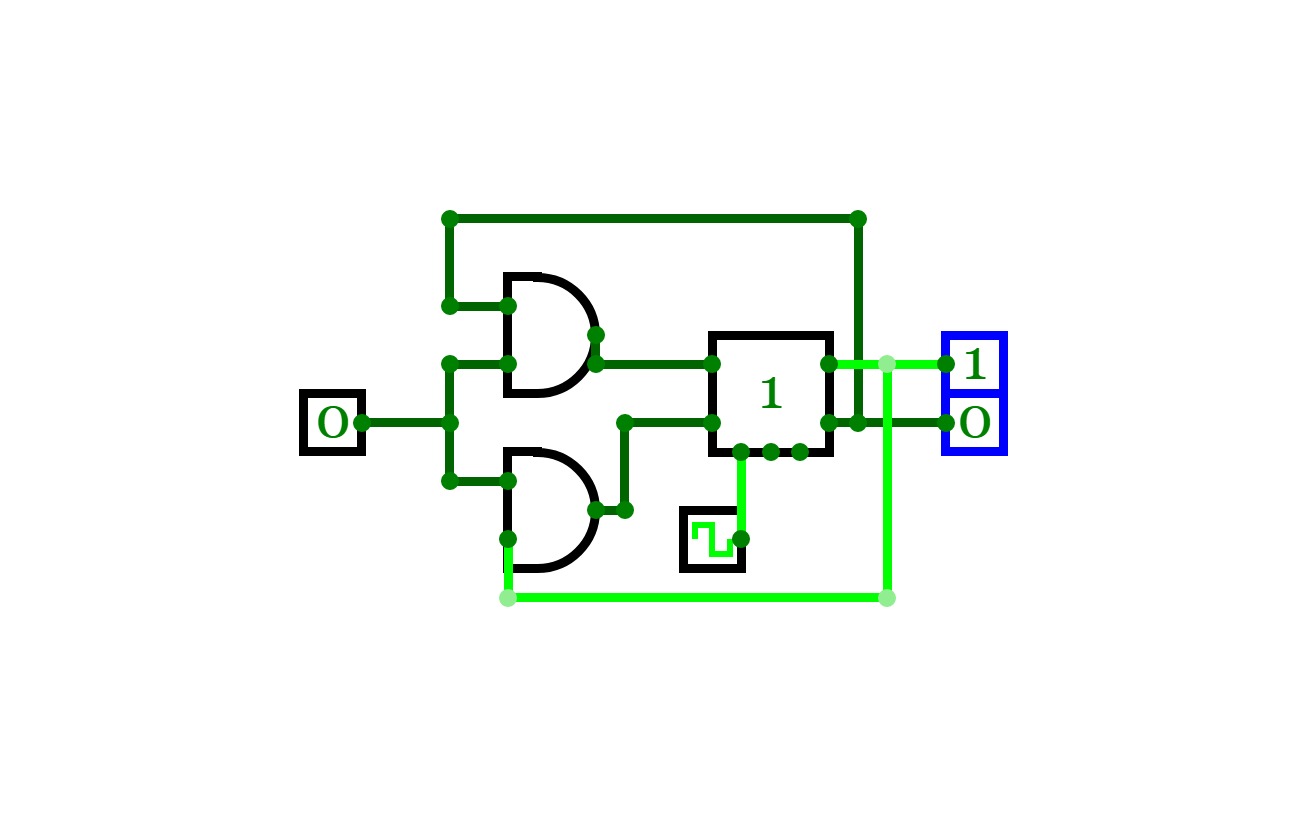

D FLIPFLOP

D FLIPFLOP

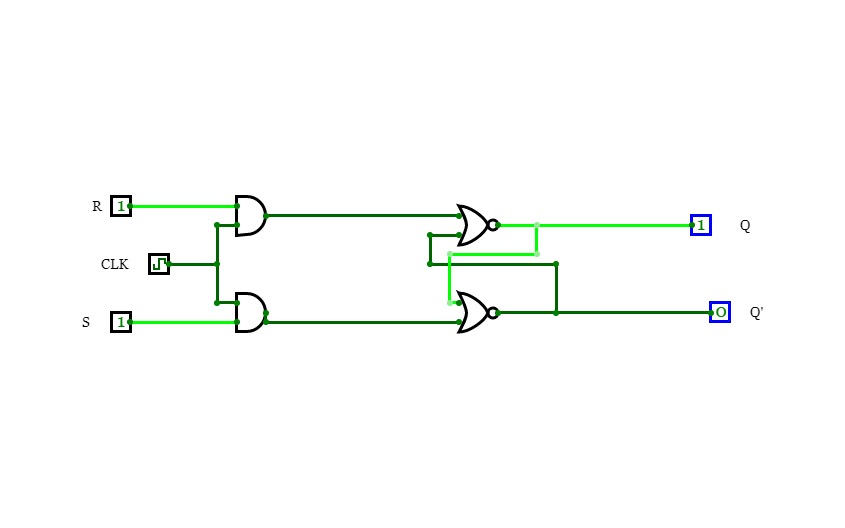

SR FILPFLOP

SR FILPFLOP

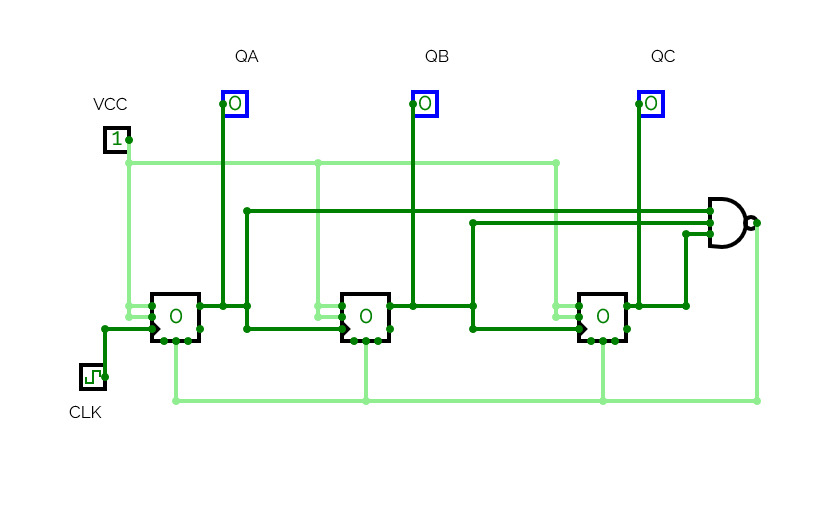

3 bit binary counter

3 bit binary counter

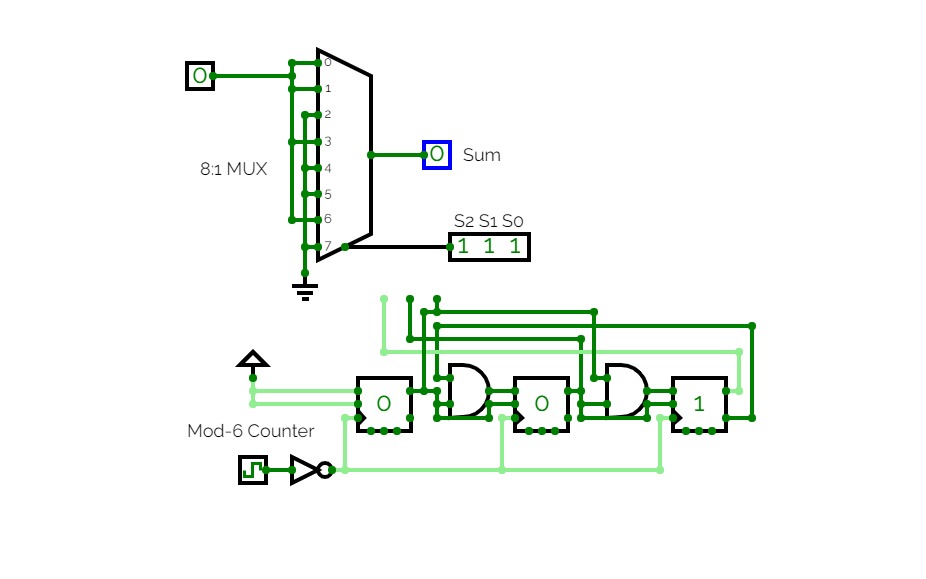

MUX with counter

MUX with counter

Untitled

Untitled

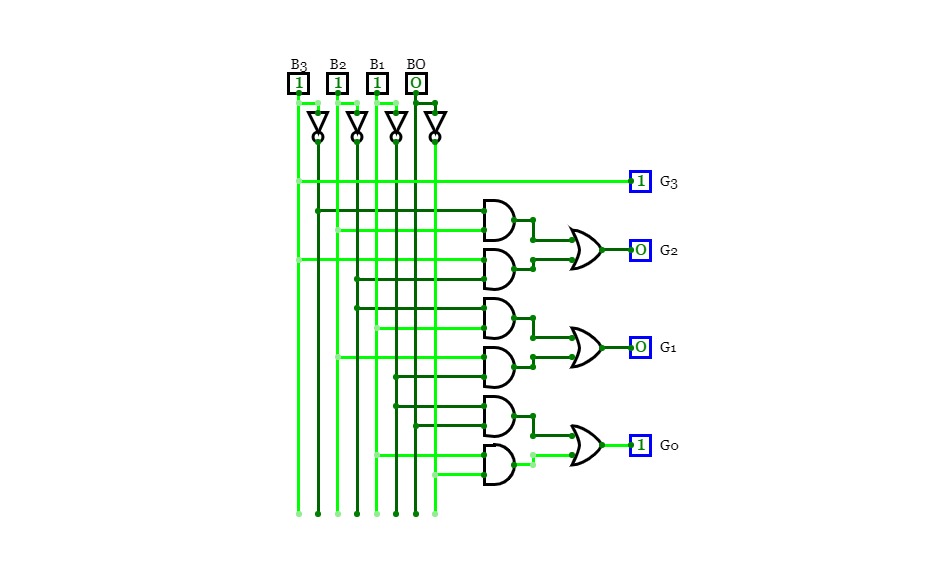

4 bit binary to grey

4 bit binary to grey

4 bit synchronous counter

4 bit synchronous counter

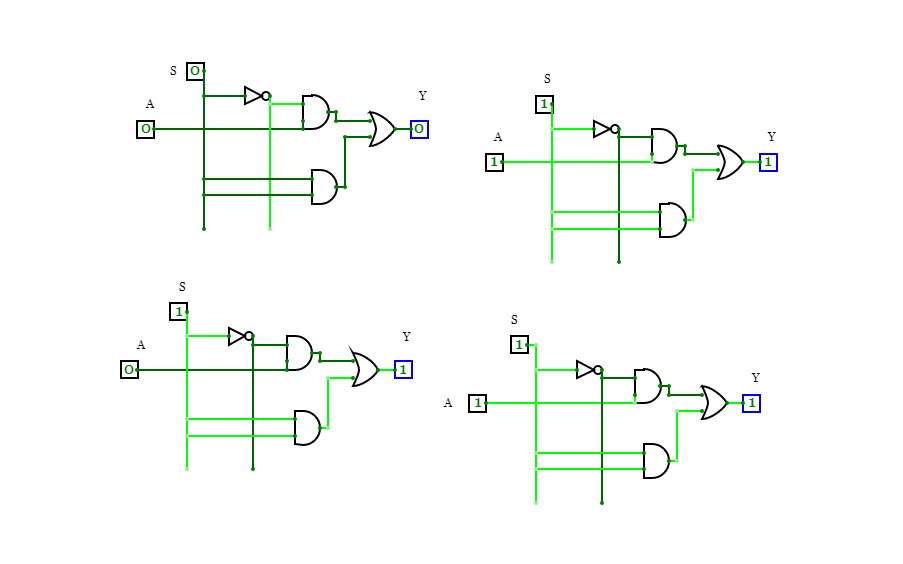

2to1mux by exor gate

2to1mux by exor gate

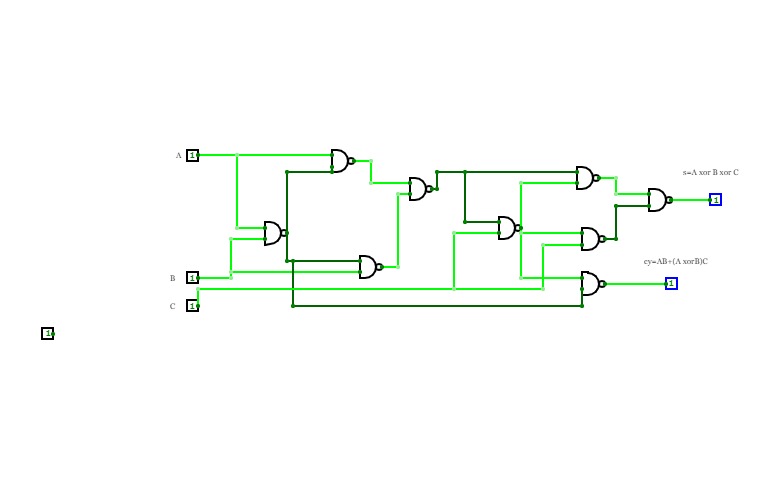

full adder using nand gate

full adder using nand gate

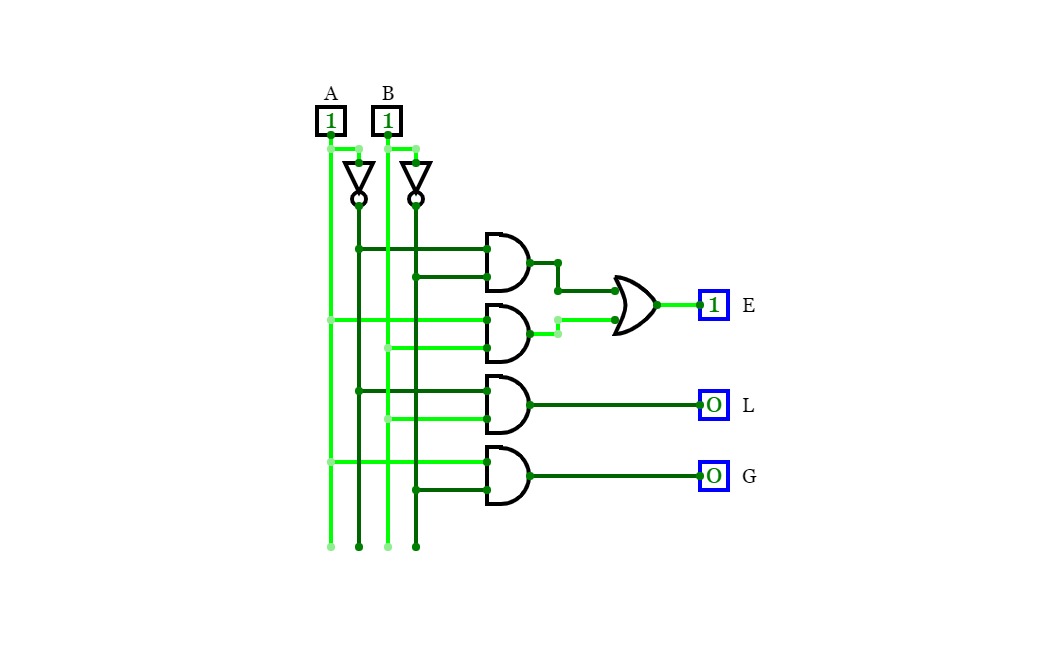

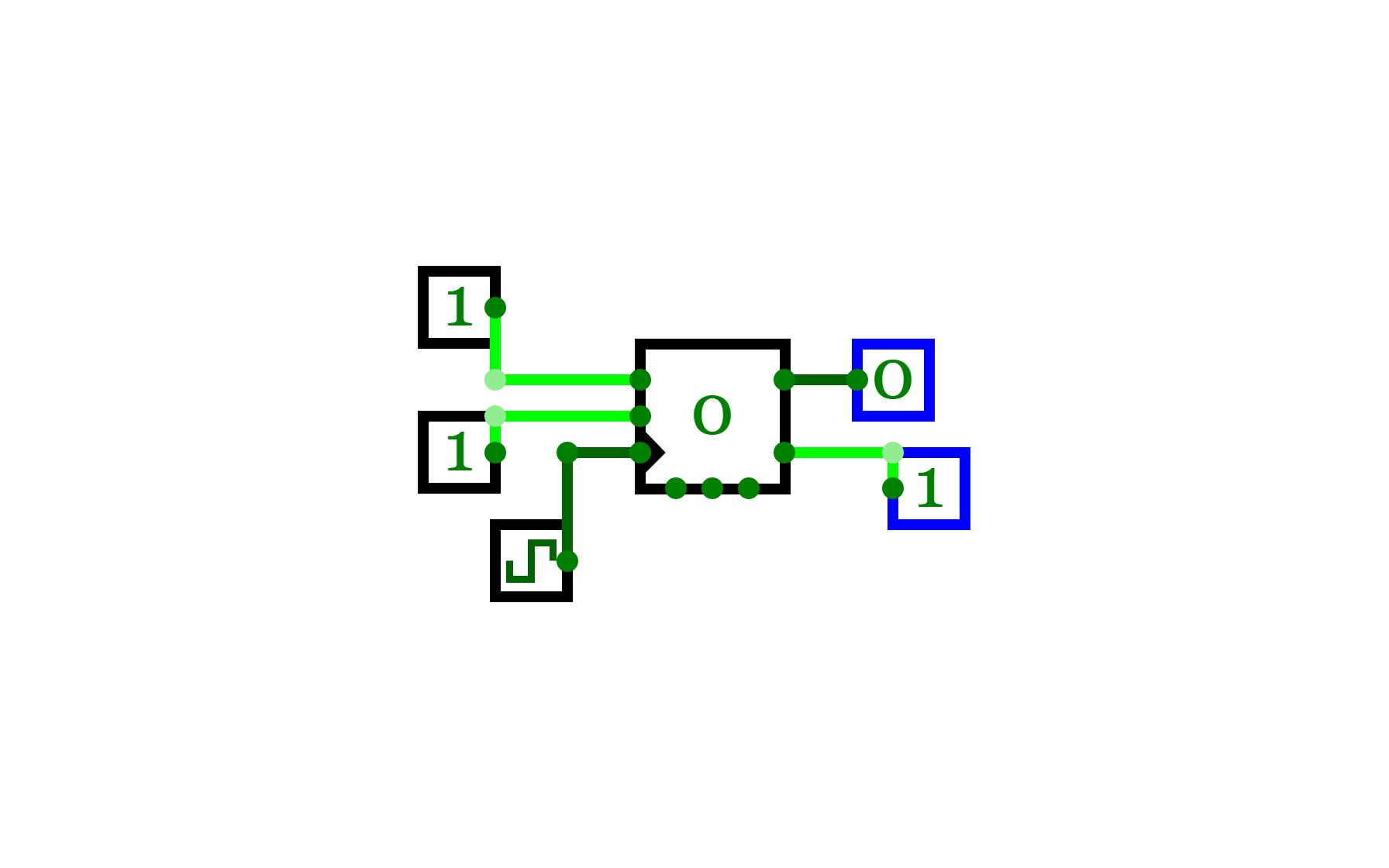

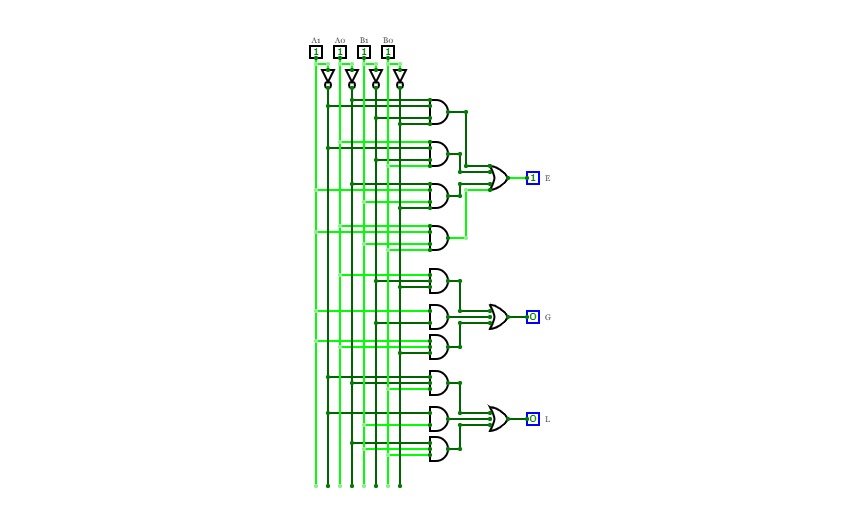

1 BIT MAGNITUDE COMPARATOR

1 BIT MAGNITUDE COMPARATOR

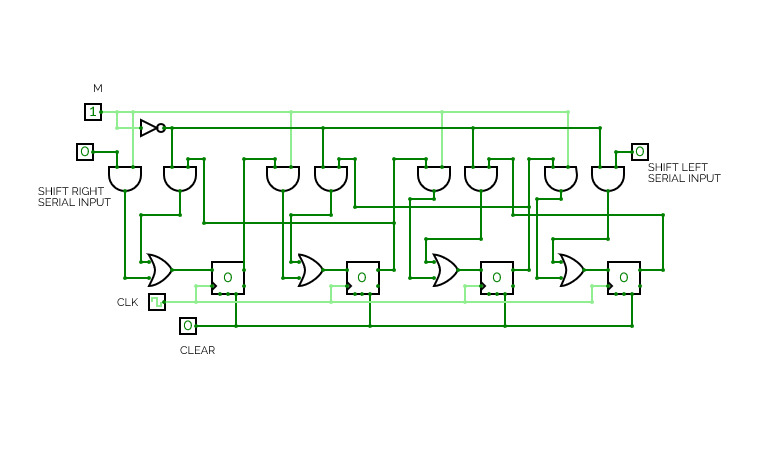

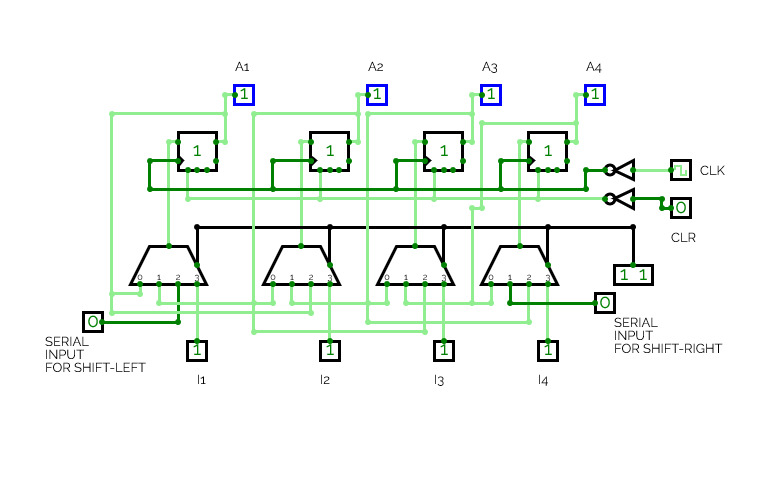

4 bit bidirectional shift register

4 bit bidirectional shift register

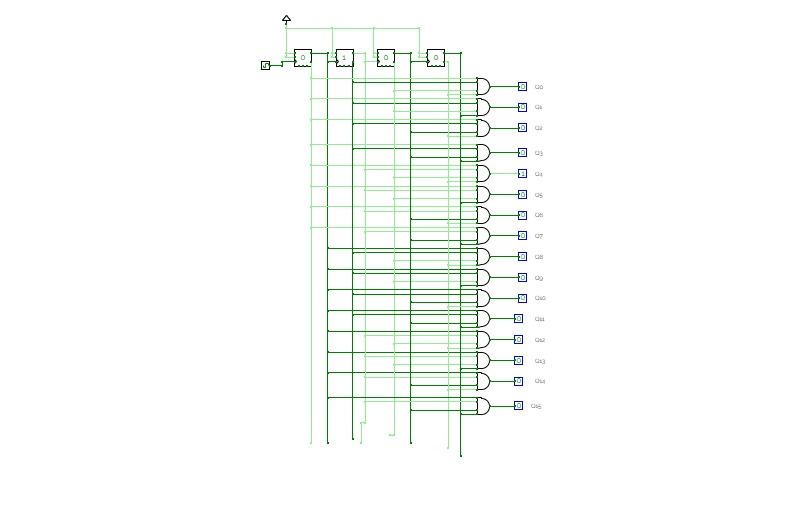

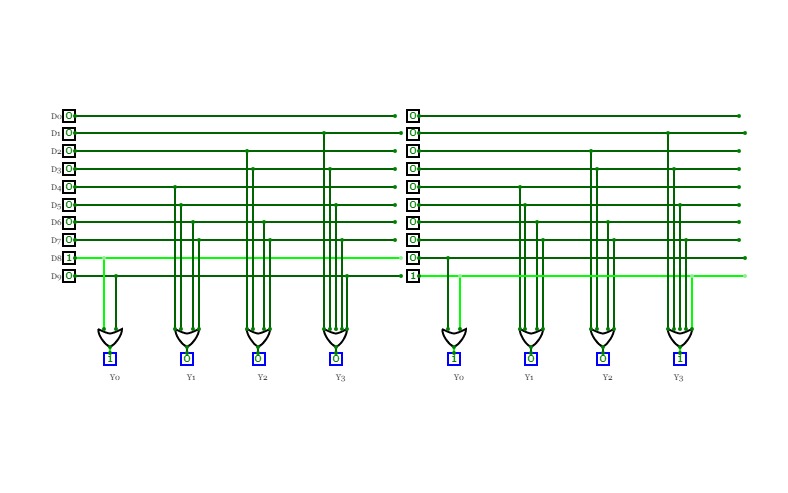

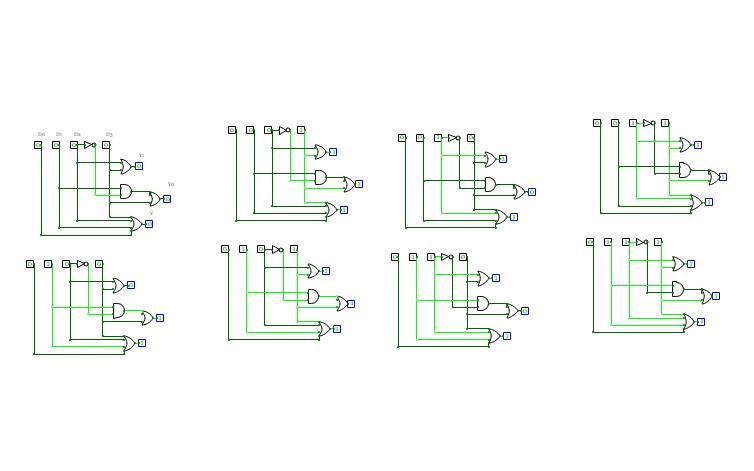

4 bit ripple counter with decoded outputs

4 bit ripple counter with decoded outputs

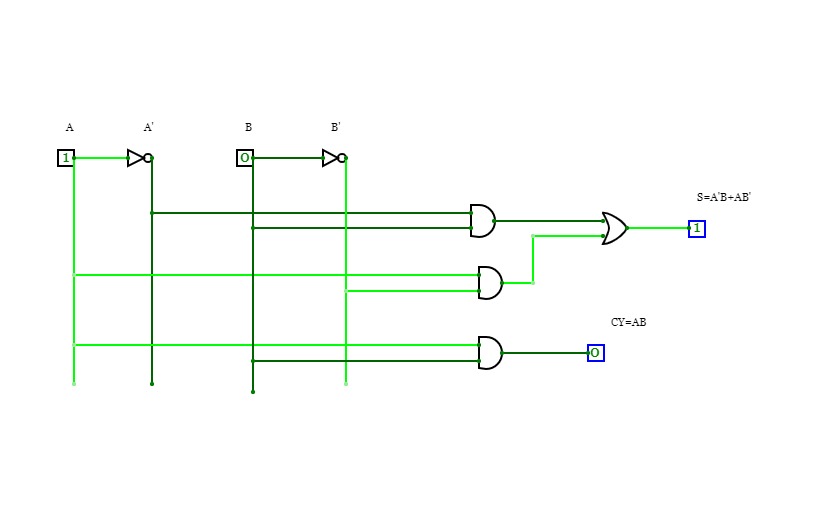

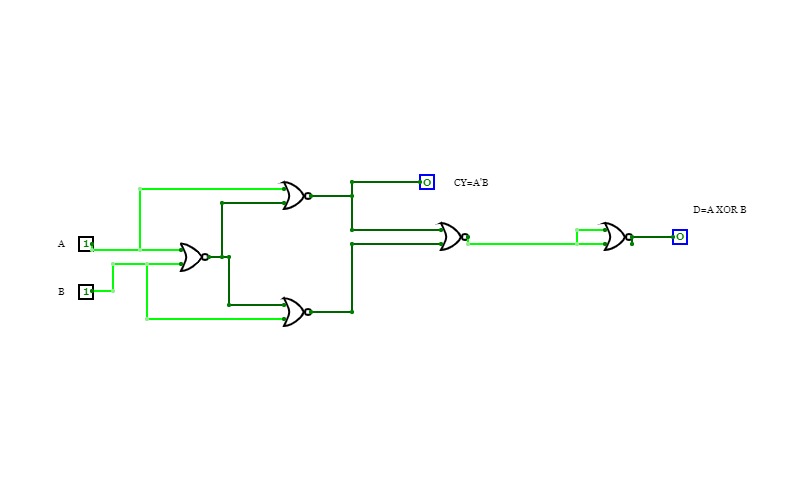

Half Adder using basic gates

Half Adder using basic gates

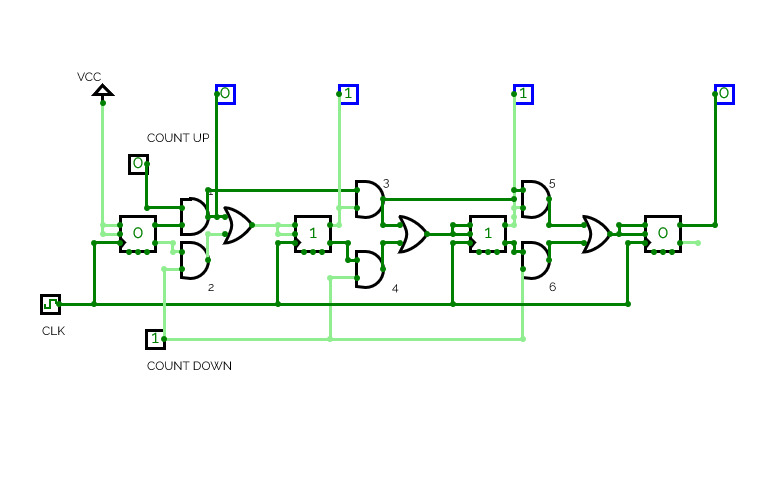

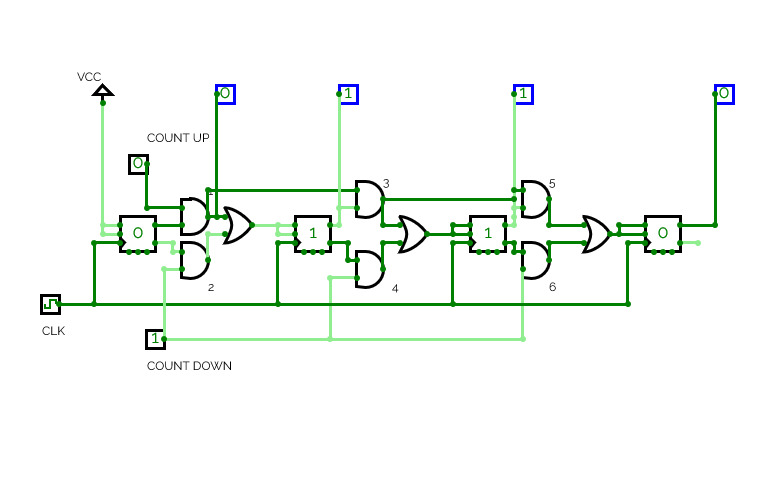

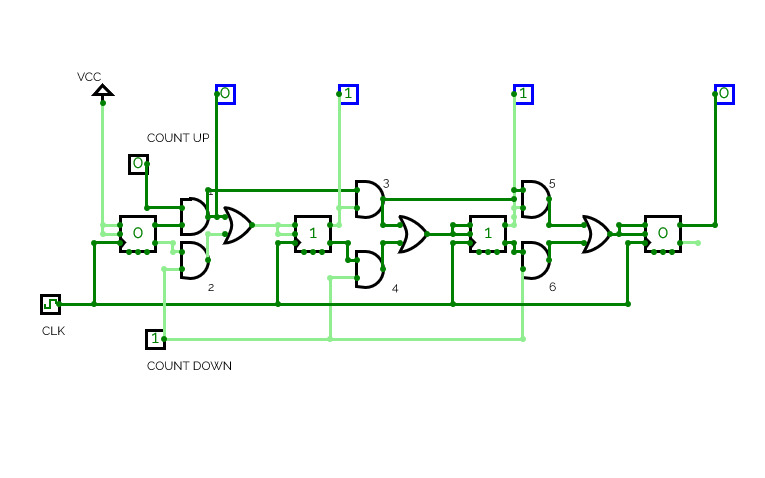

4 bit synchronous UP/DOWN counter

4 bit synchronous UP/DOWN counter

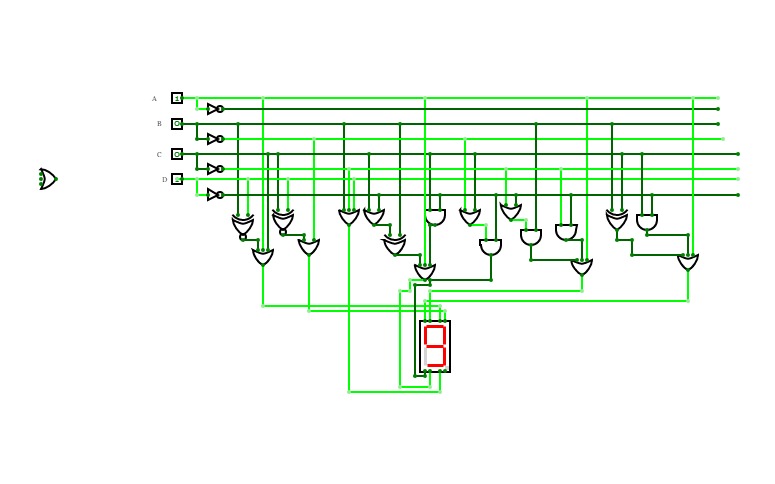

BCD TO 7 SEGMENT DECODER

BCD TO 7 SEGMENT DECODER

octal to binary encoder

octal to binary encoder

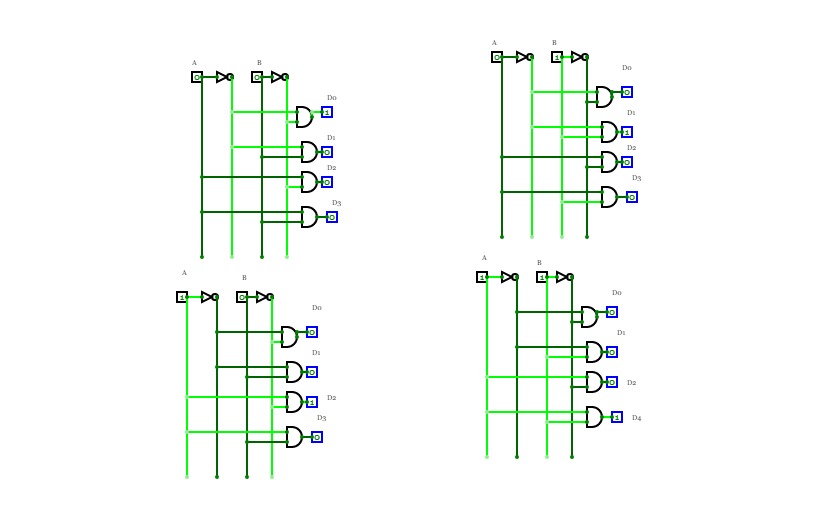

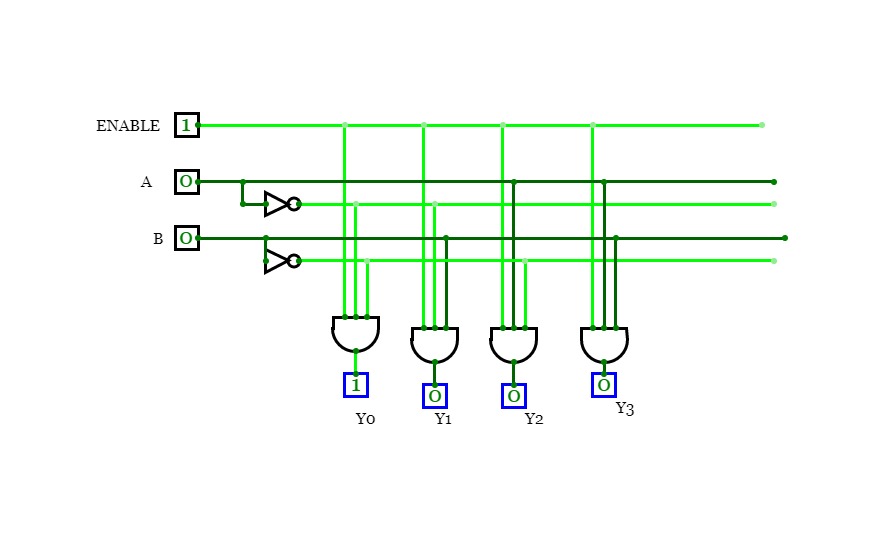

2 to 4 decoder

2 to 4 decoder

8.SRFF USING TFF

8.SRFF USING TFF

half subtractor using nor gate

half subtractor using nor gate

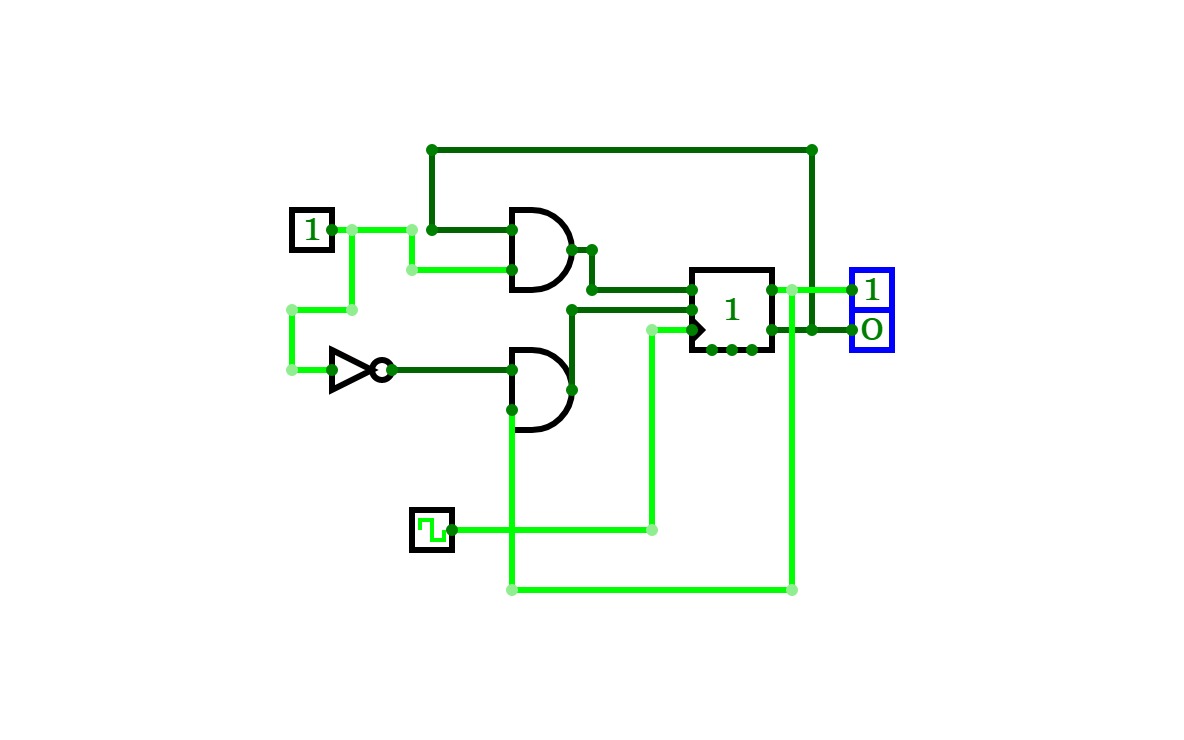

3.DFF USING TFF

3.DFF USING TFF

11.JKFF USING DFF

11.JKFF USING DFF

DFF USING JKFF

DFF USING JKFF

9.SRFF USING DFF

9.SRFF USING DFF

7.SRFF USING JKFF

7.SRFF USING JKFF

16 t0 1 mux

16 t0 1 mux

JK FIPFLOP USING INBUILT

JK FIPFLOP USING INBUILT

4 bit ripple up/down counter

4 bit ripple up/down counter

12.JKFF USING TFF

12.JKFF USING TFF

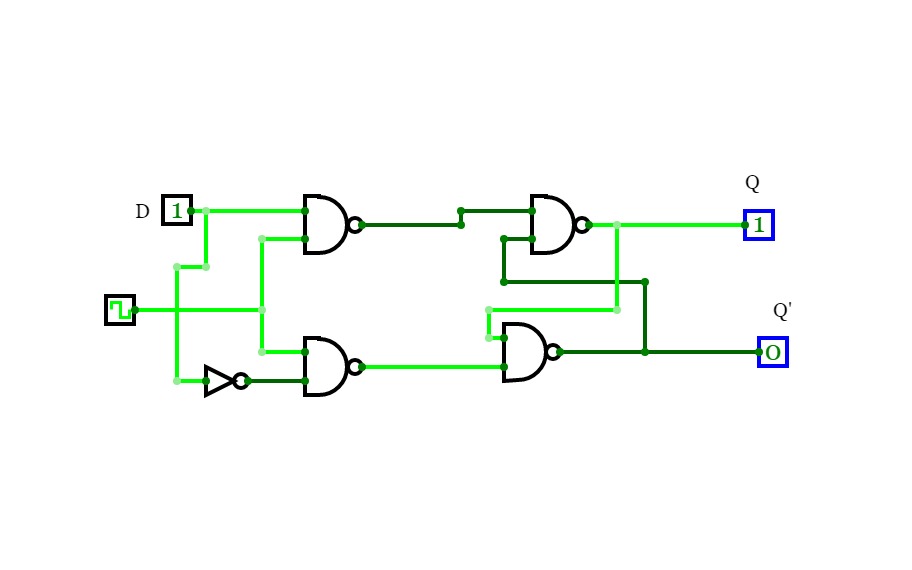

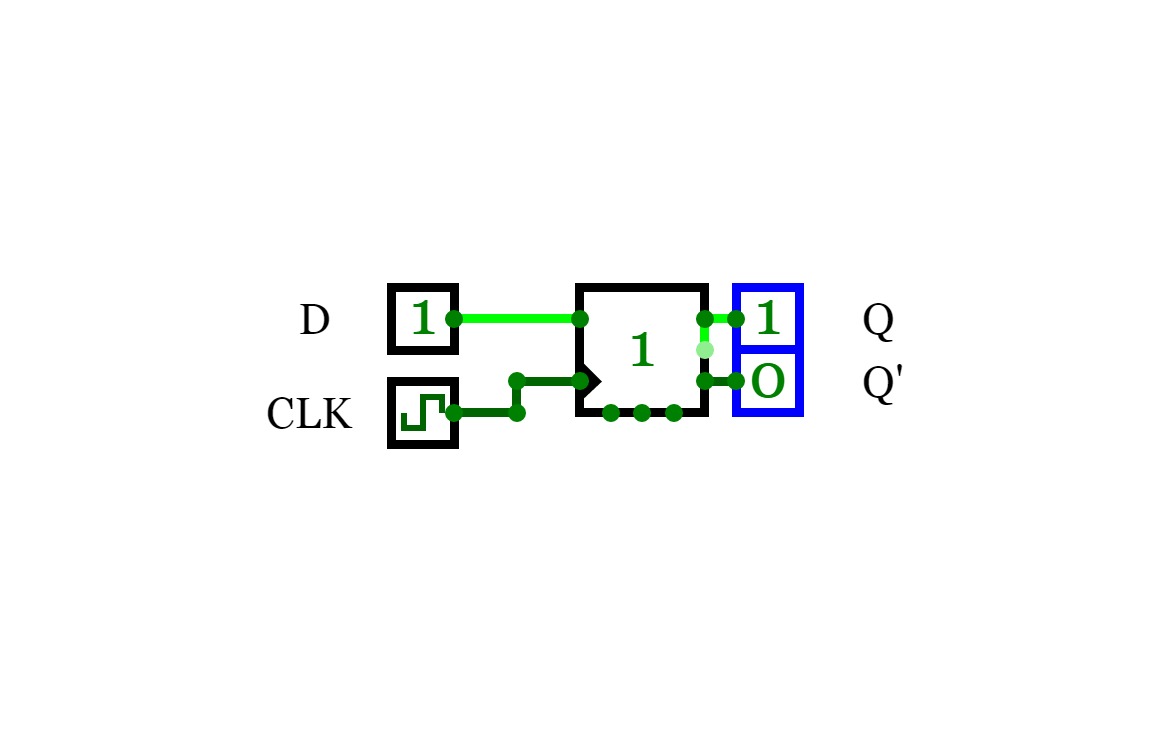

DELAY FLIPFLOP USNG INBUILT

DELAY FLIPFLOP USNG INBUILT

MOD 12 COUNTER

MOD 12 COUNTER

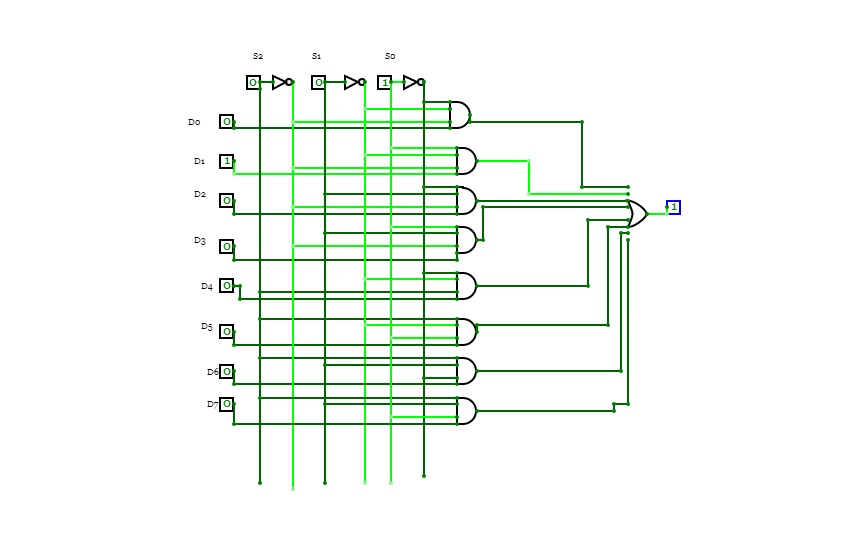

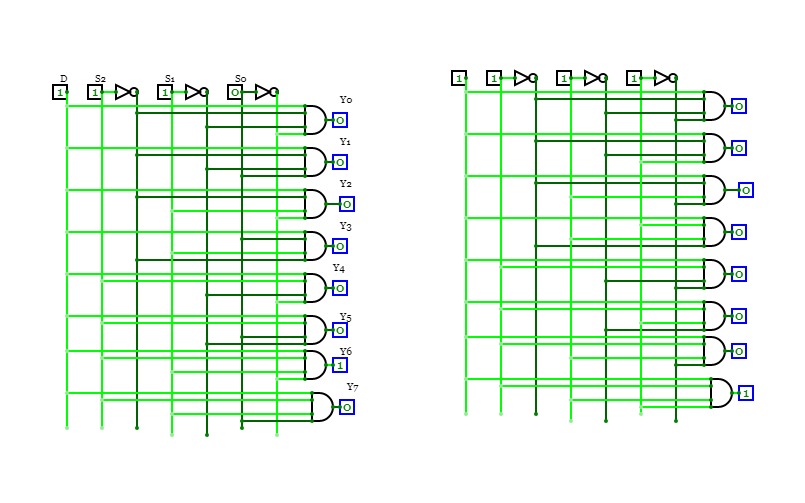

8 TO 1 MUX

8 TO 1 MUX

mod-6 unit distance counter

mod-6 unit distance counter

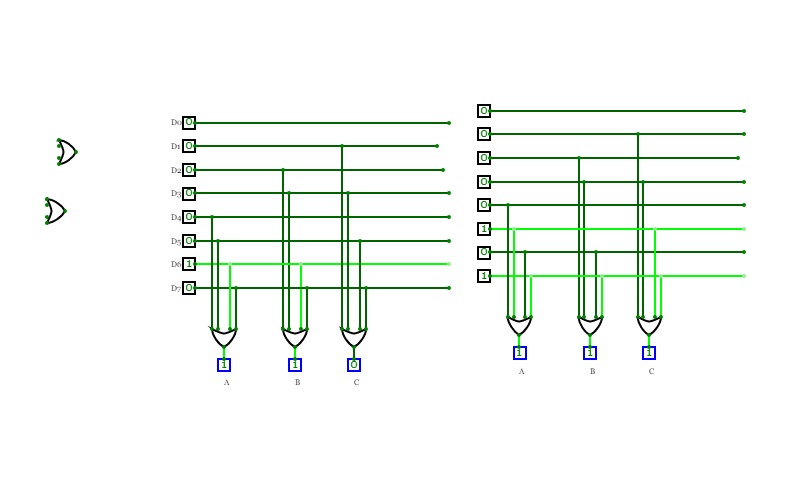

DECIMAL TO BCD ENCODER

DECIMAL TO BCD ENCODER

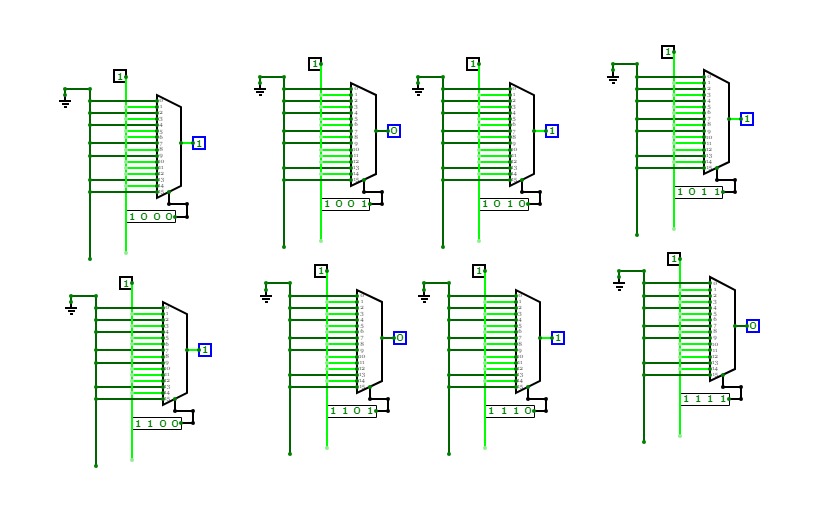

circuit that counts (0,2,4...14)when input is 1 and counts (1,3...15)when input is 0

circuit that counts (0,2,4...14)when input is 1 and counts (1,3...15)when input is 0

MOD 7 COUNTER

MOD 7 COUNTER

2 to 1 mux

2 to 1 mux

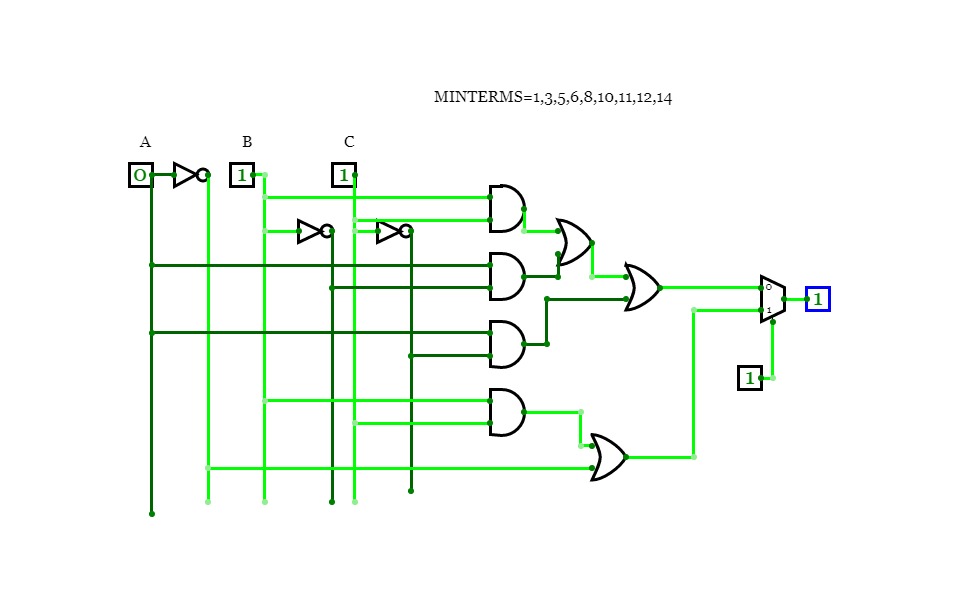

IMPLEMENTATION OF MINTERMS BY 4 TO 1 MUX

IMPLEMENTATION OF MINTERMS BY 4 TO 1 MUX

4 bit grey to binary code convertor

4 bit grey to binary code convertor

4 bit ripple down counter

4 bit ripple down counter

4 BIT EXCESS 3 TO BCD

4 BIT EXCESS 3 TO BCD

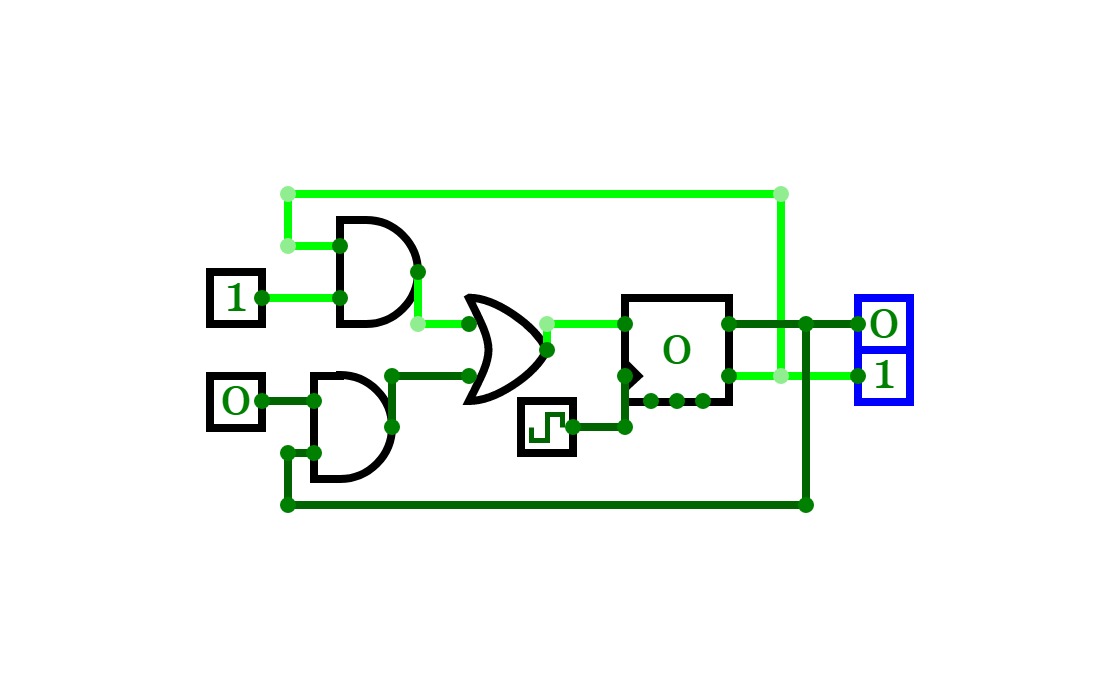

4.TFF USING SRFF

4.TFF USING SRFF

counter that counts 0,2,4,7,0

counter that counts 0,2,4,7,0

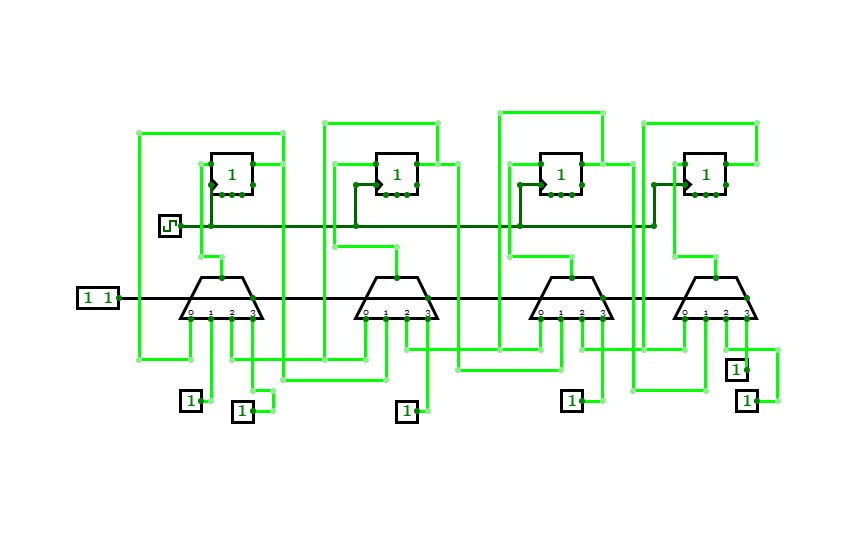

4 BIT UNIVERSAL SHIFT REGISTER

4 BIT UNIVERSAL SHIFT REGISTER

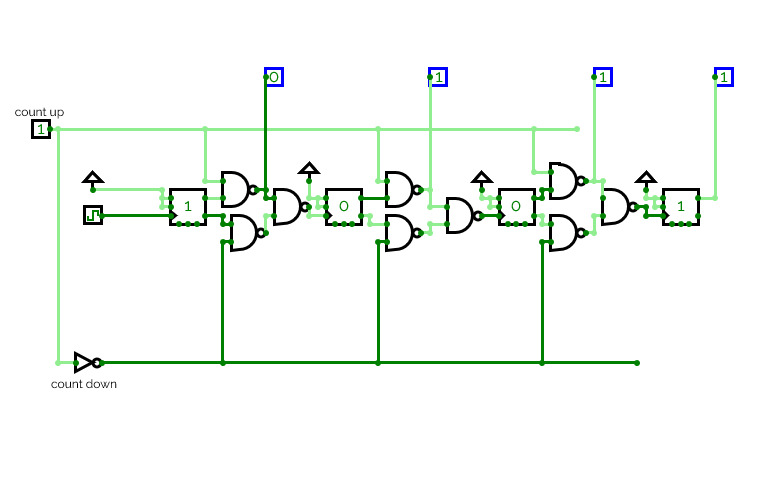

4 bit synchronous UP/DOWN counter

4 bit synchronous UP/DOWN counter

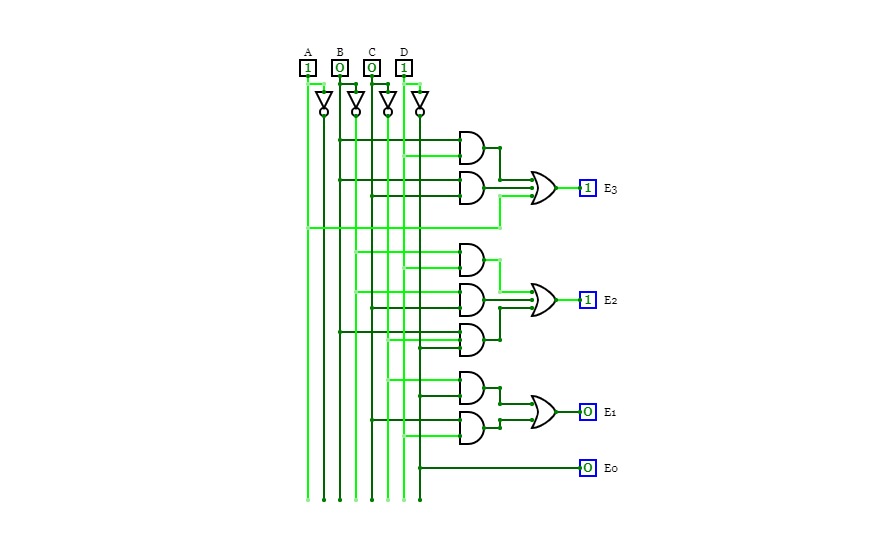

4 TO 2 PRIORITY ENCODER

4 TO 2 PRIORITY ENCODER

Untitled

Untitled

2 BIT MAGNITUDE COMPARATOR

2 BIT MAGNITUDE COMPARATOR

1 TO 8 DEMUX

1 TO 8 DEMUX

RING COUNTER

RING COUNTER

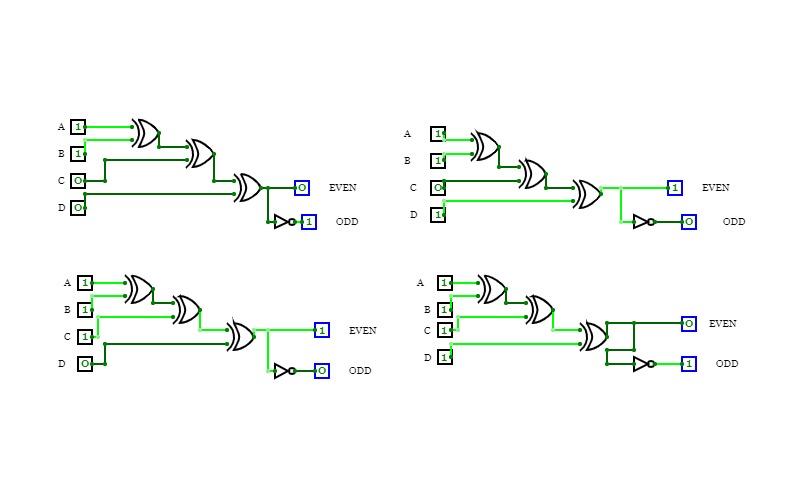

4 BIT PARITY GENERATOR AND CHECKER

4 BIT PARITY GENERATOR AND CHECKER

BCD TO 7 SEGMENT DECODER

BCD TO 7 SEGMENT DECODER

UNIVERSAL SHIFT REGISTER

UNIVERSAL SHIFT REGISTER

T FLIPFLOP USING LOGIC GATES

T FLIPFLOP USING LOGIC GATES

2 TO 4 DECODER

2 TO 4 DECODER

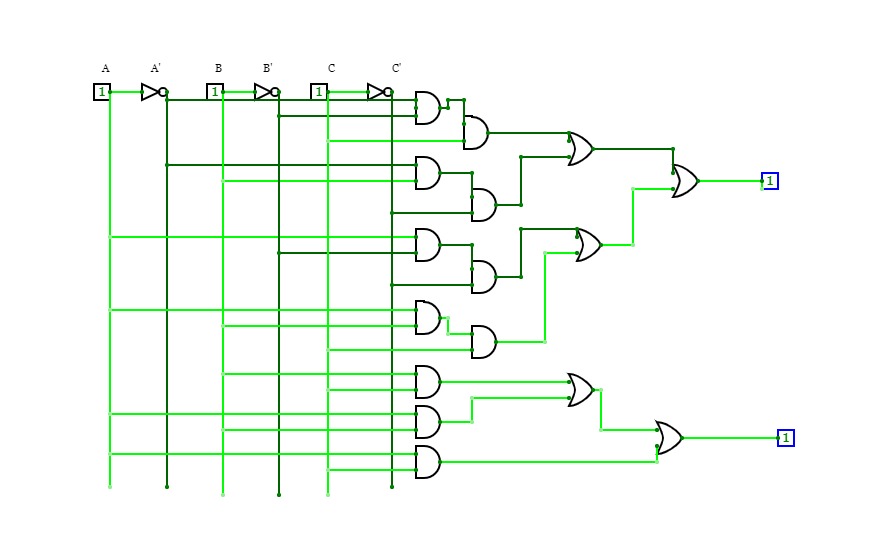

implementation using minterms with2:1 mux

implementation using minterms with2:1 mux

FULL ADDER USING BASIC GATES

FULL ADDER USING BASIC GATES

24 to 1 mux using 8 to 1 mux

24 to 1 mux using 8 to 1 mux

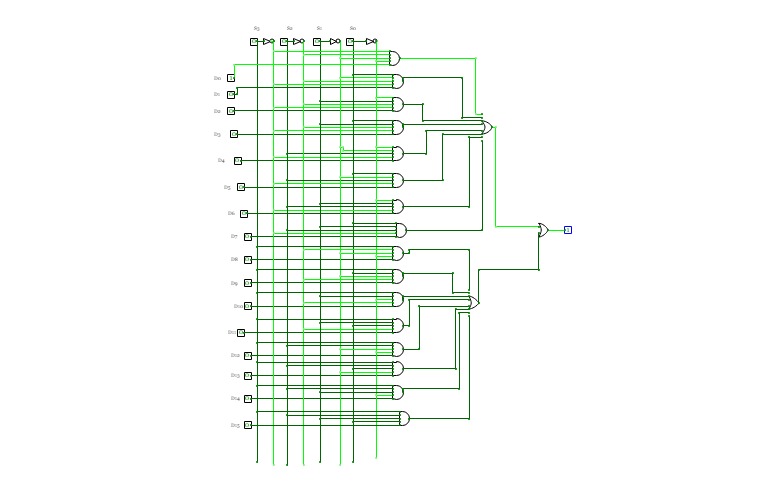

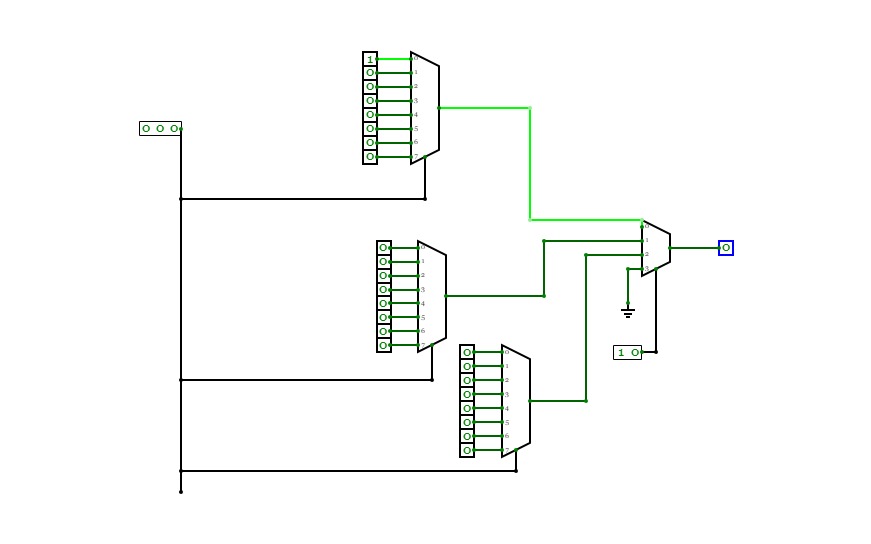

implementation using minterms with 16:1 mux

implementation using minterms with 16:1 mux

4 bit synchronous UP/DOWN counter

4 bit synchronous UP/DOWN counter

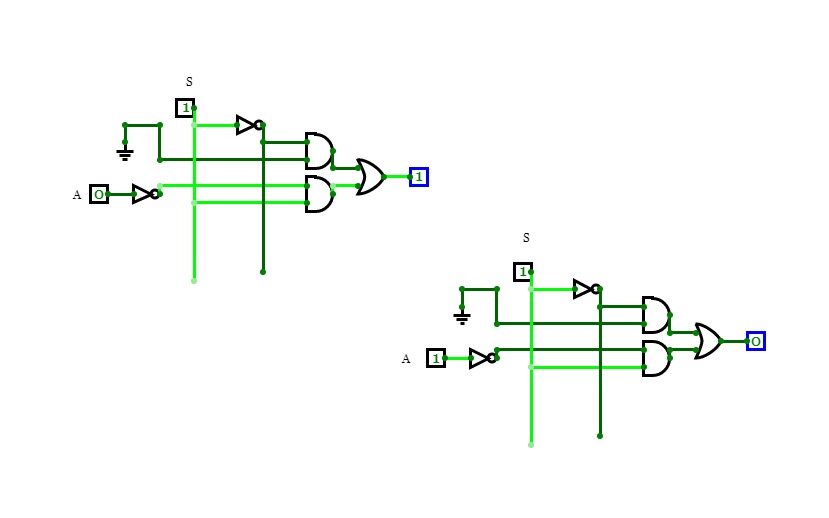

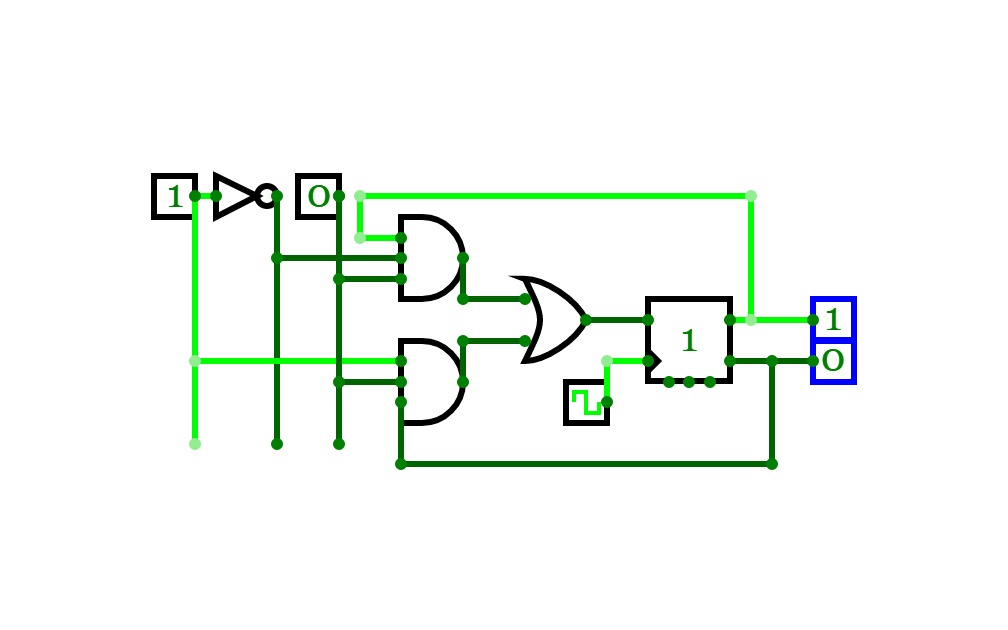

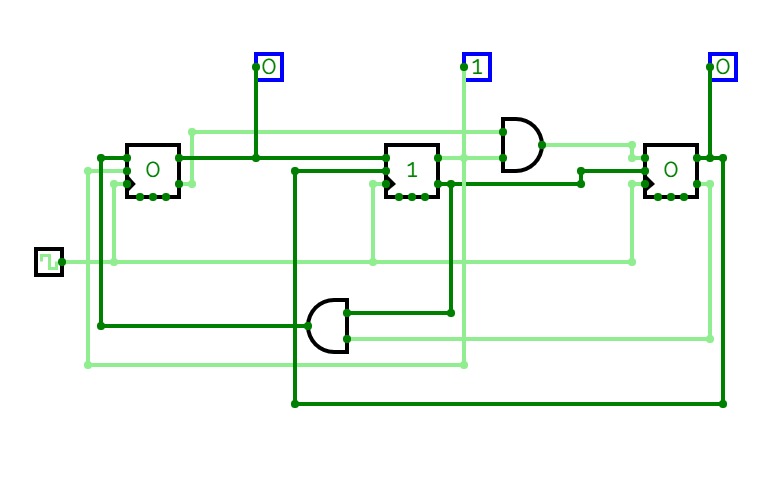

JACK KILBY FLIPFLOP USING LOGICGATES

JACK KILBY FLIPFLOP USING LOGICGATES