UBIKAA SREE K

Member since: 3 years

Educational Institution: MEPCO SCHLENK ENGINNERING COLLEGE,SIVAKASI

Country: India

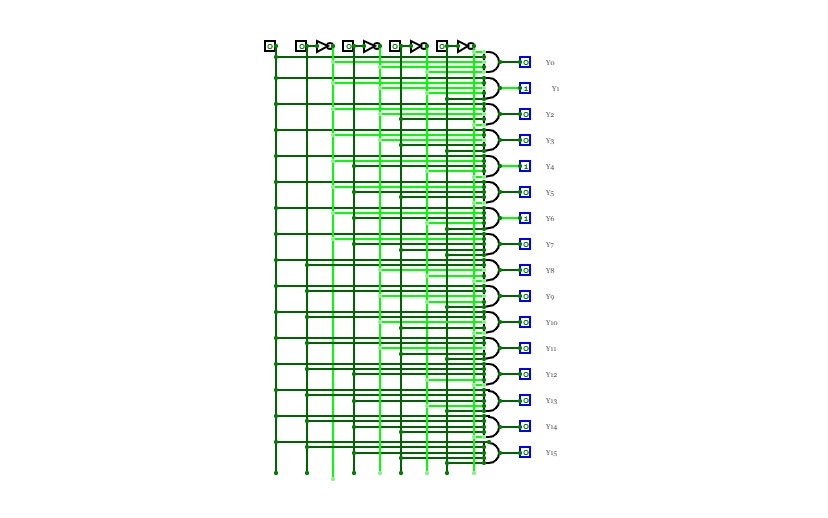

16:1 MUX

16:1 MUX

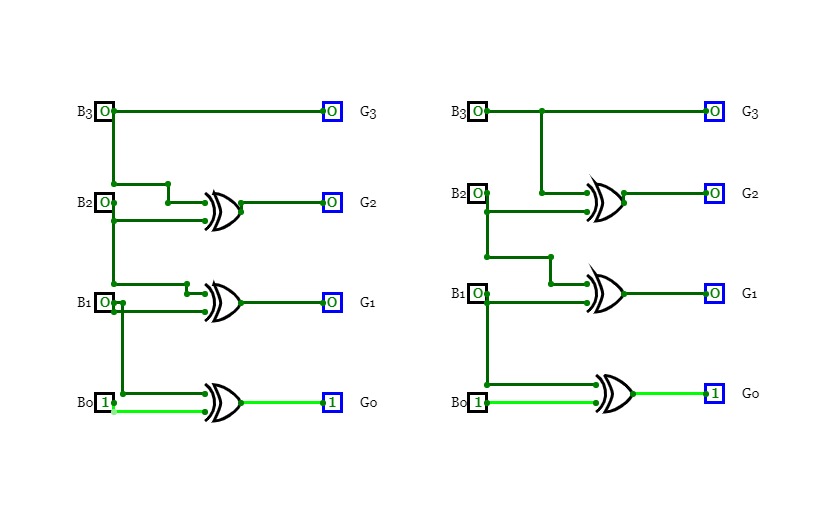

BINARY TO GRAY CODE

BINARY TO GRAY CODE

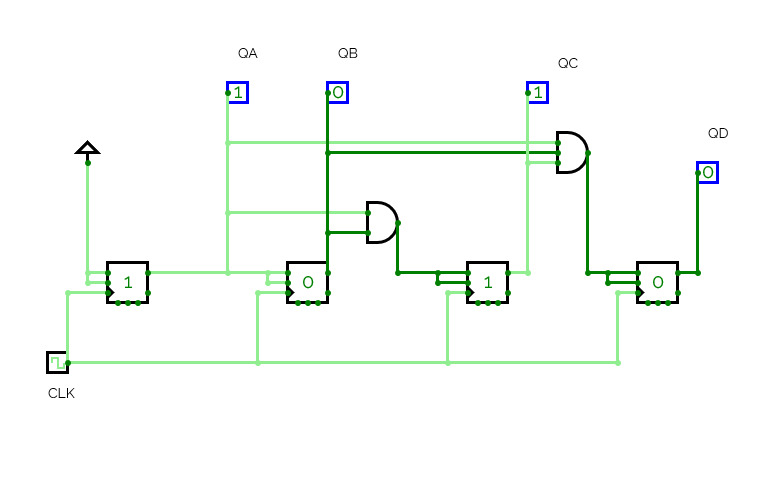

4 bit synchronous counter

4 bit synchronous counter

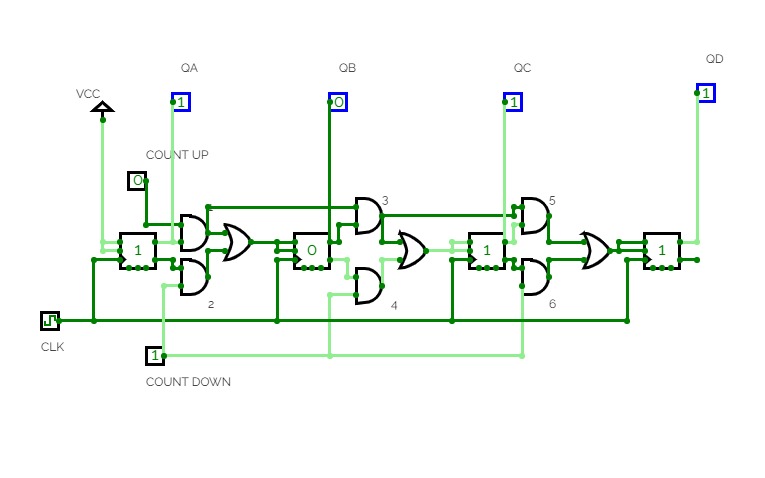

4 bit synchronous UP/DOWN counter

4 bit synchronous UP/DOWN counter

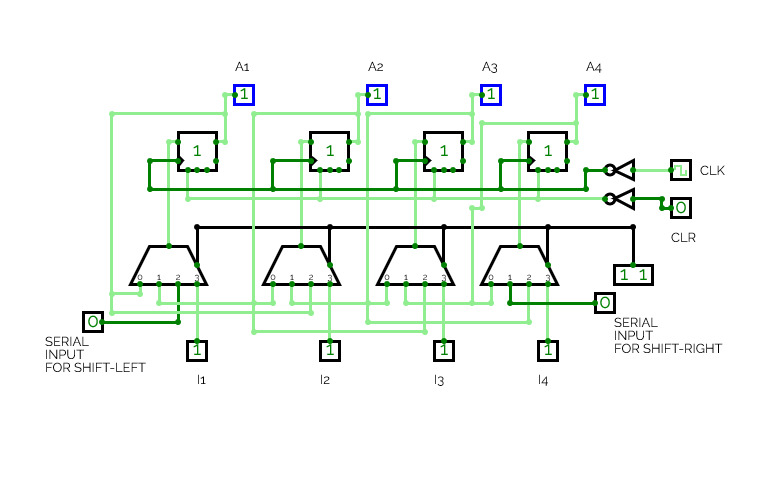

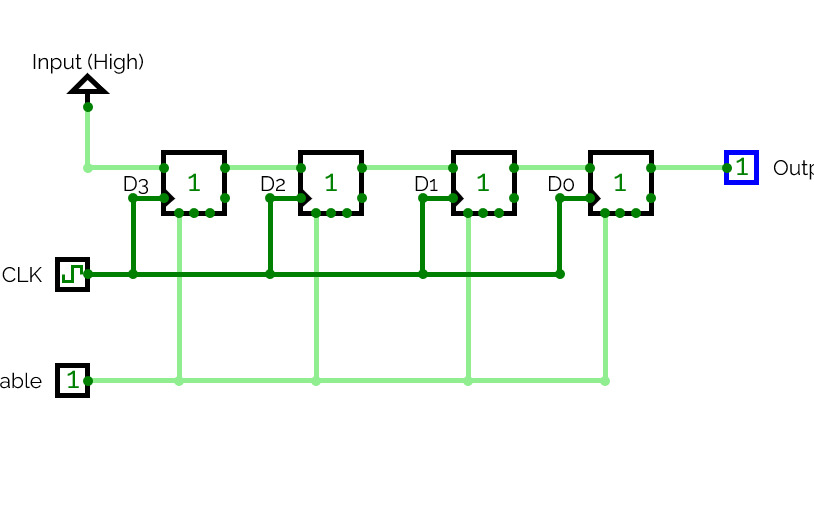

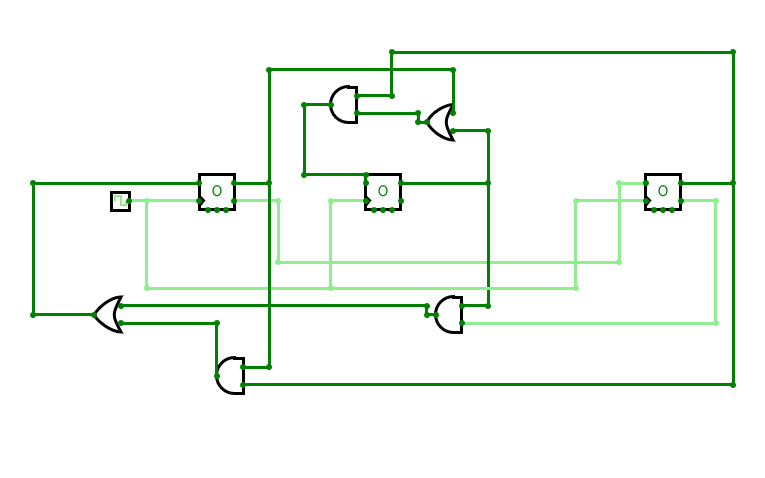

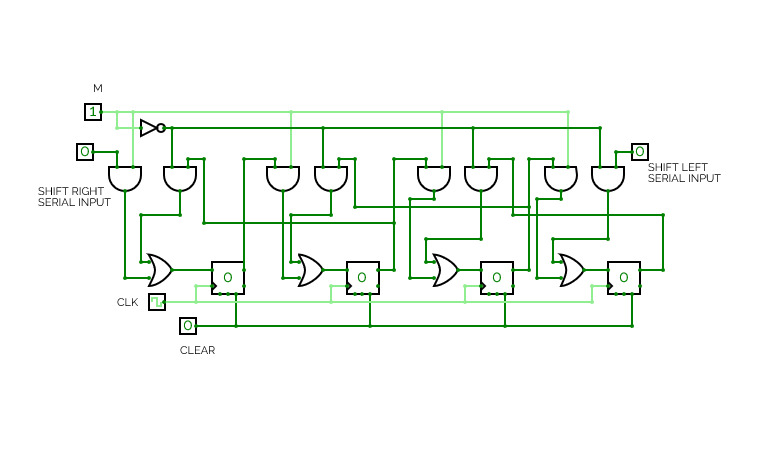

4 BIT UNIVERSAL SHIFT REGISTER

4 BIT UNIVERSAL SHIFT REGISTER

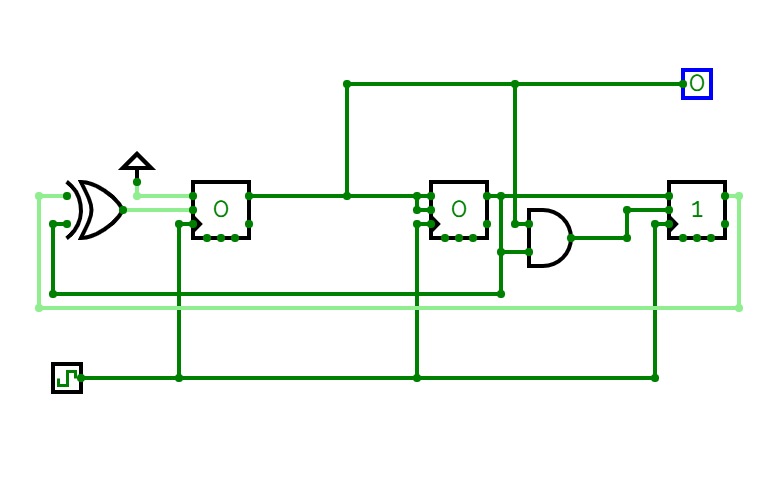

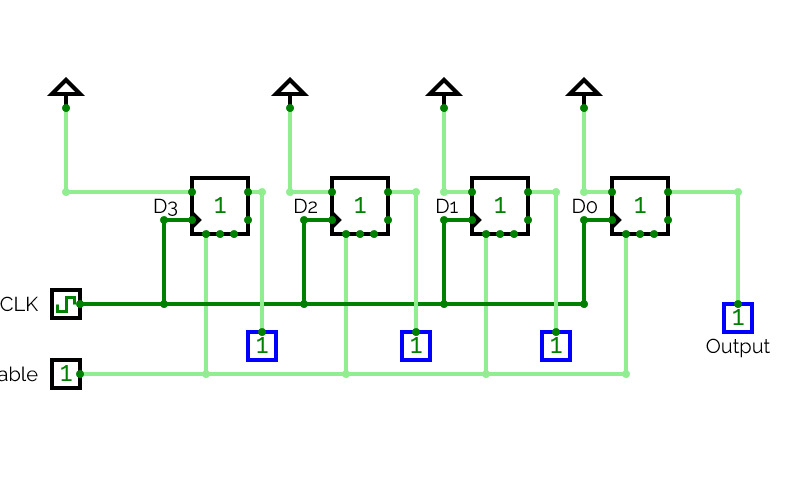

SIPO

SIPO

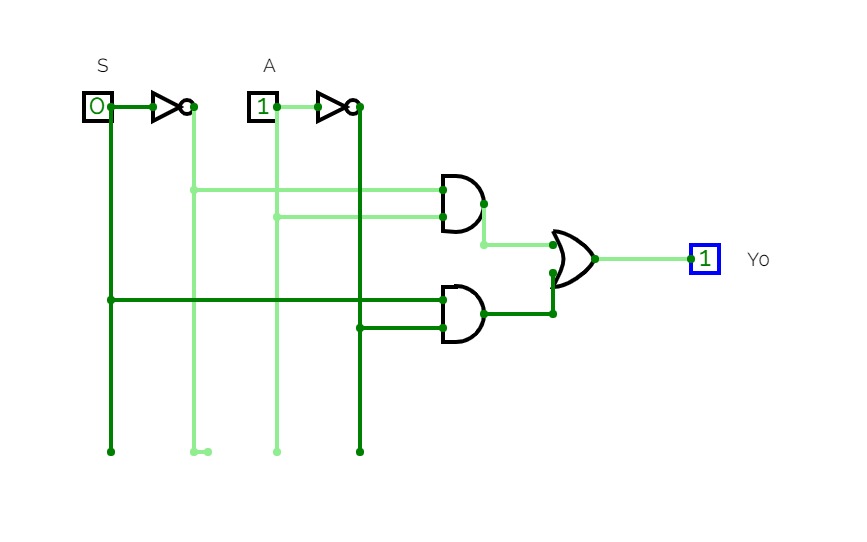

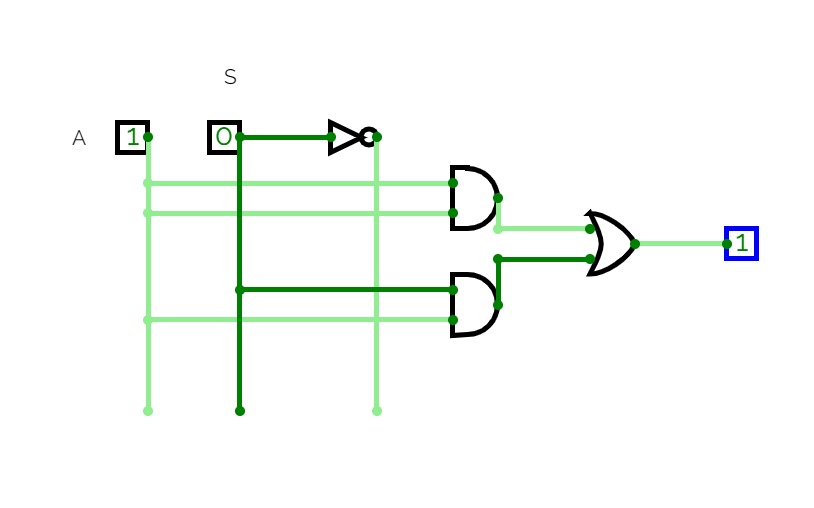

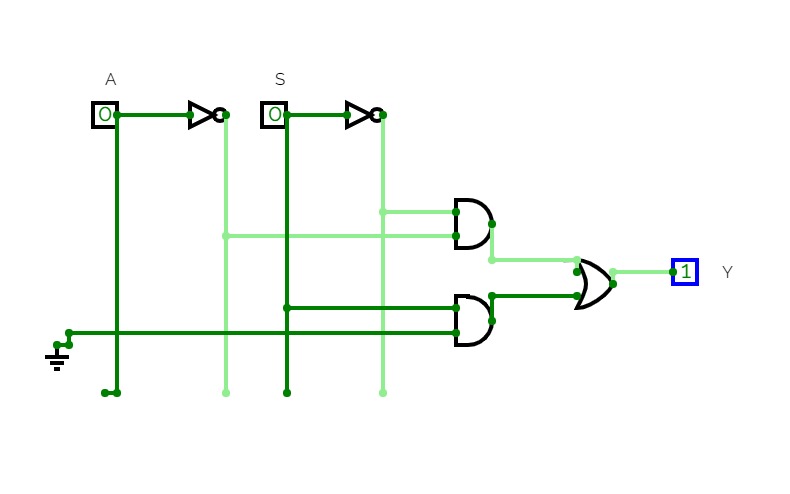

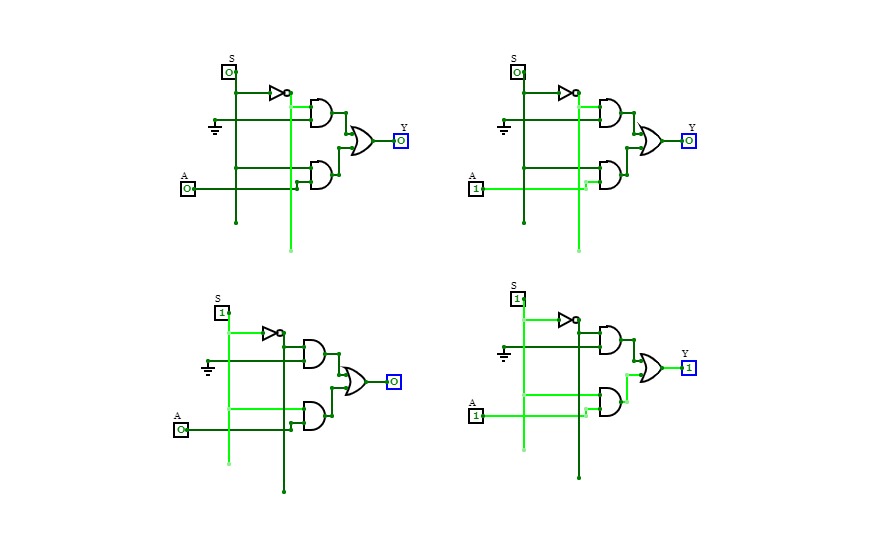

EX OR USING 2 TO 1 MUX

EX OR USING 2 TO 1 MUX

EXP 8.1

EXP 8.1

Untitled

Untitled

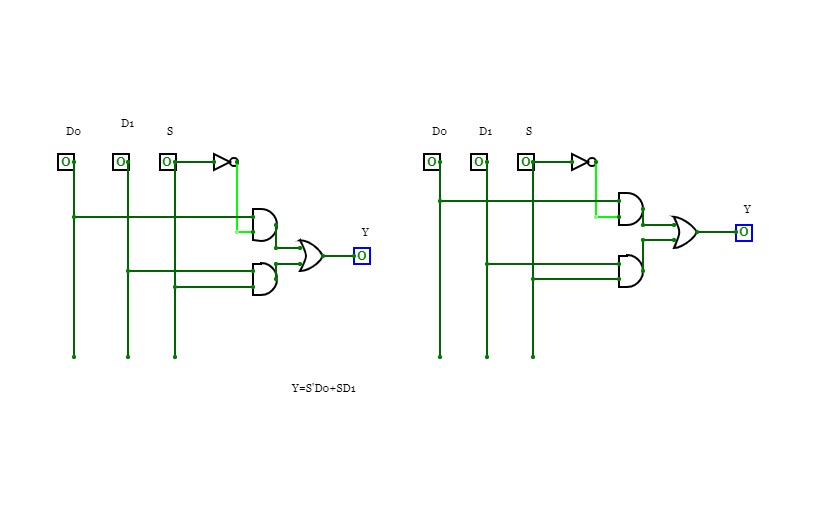

2X1 MUX

2X1 MUX

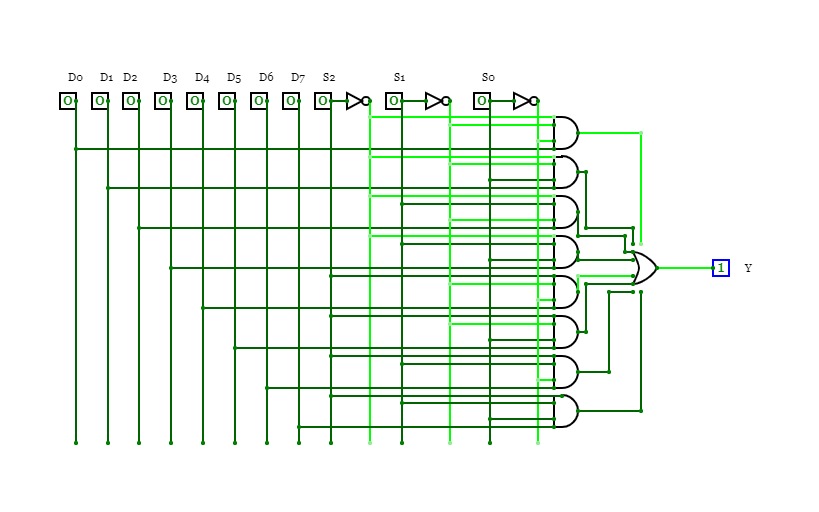

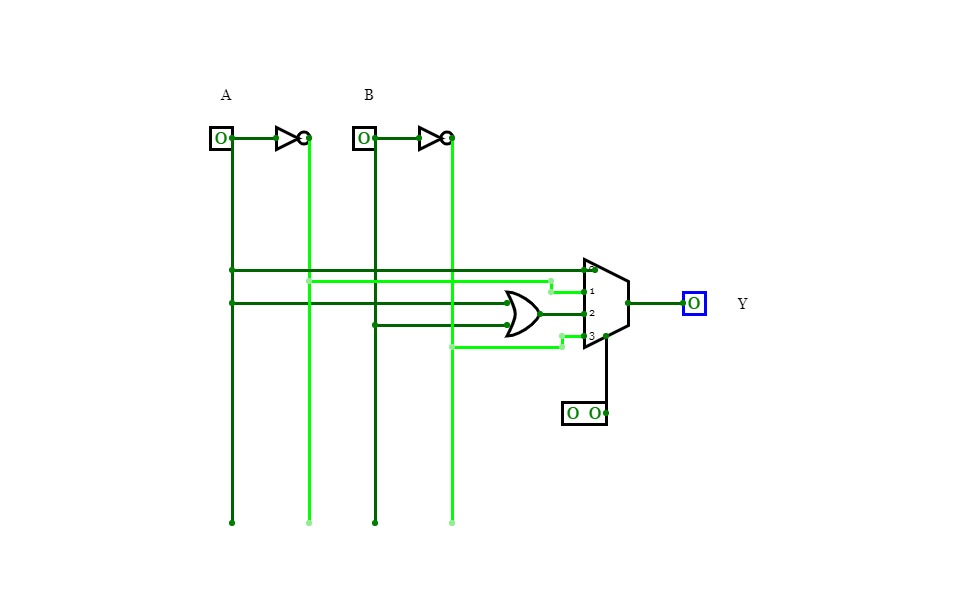

8:1 MUX

8:1 MUX

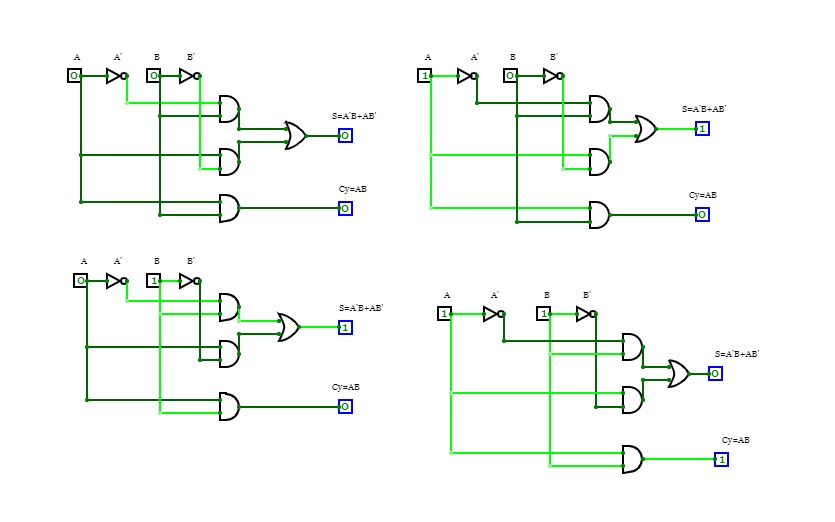

HALF ADDER USING BASIC GATES

HALF ADDER USING BASIC GATES

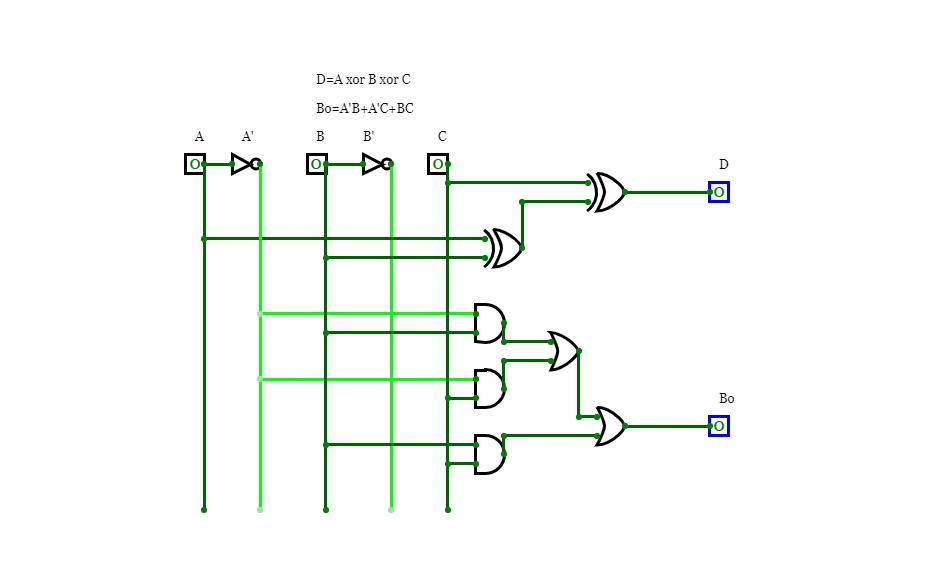

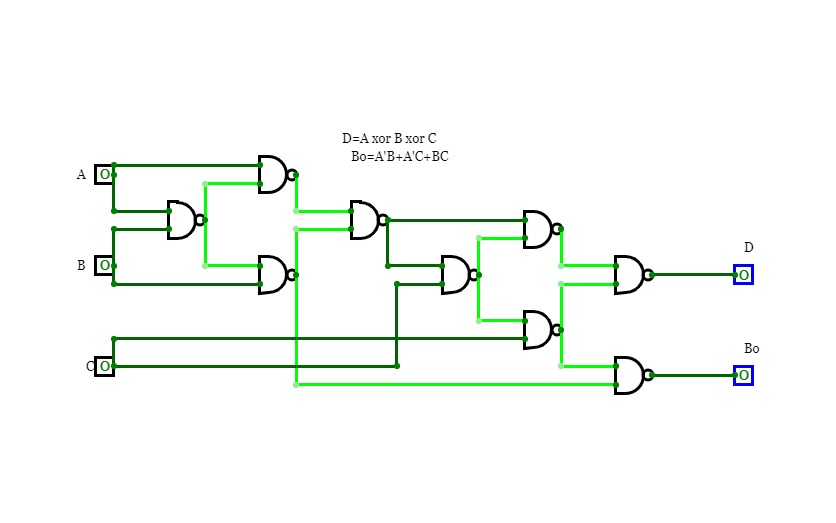

FULL SUBTRACTOR USING XOR GATE

FULL SUBTRACTOR USING XOR GATE

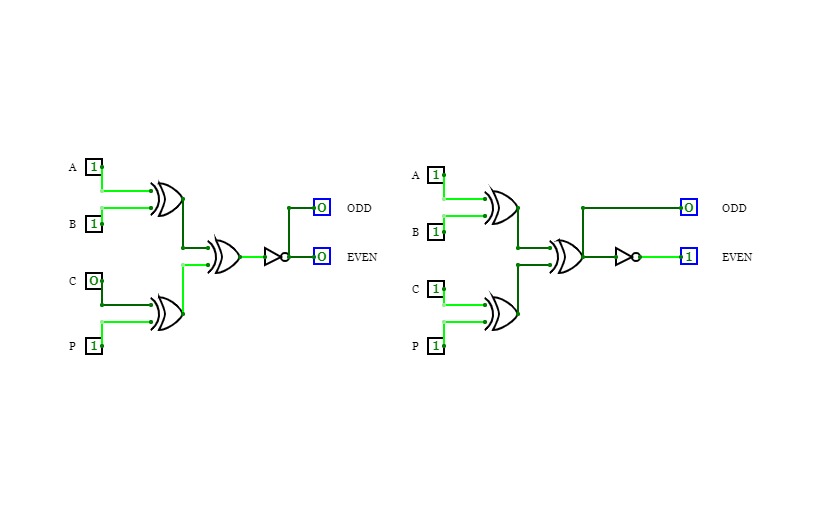

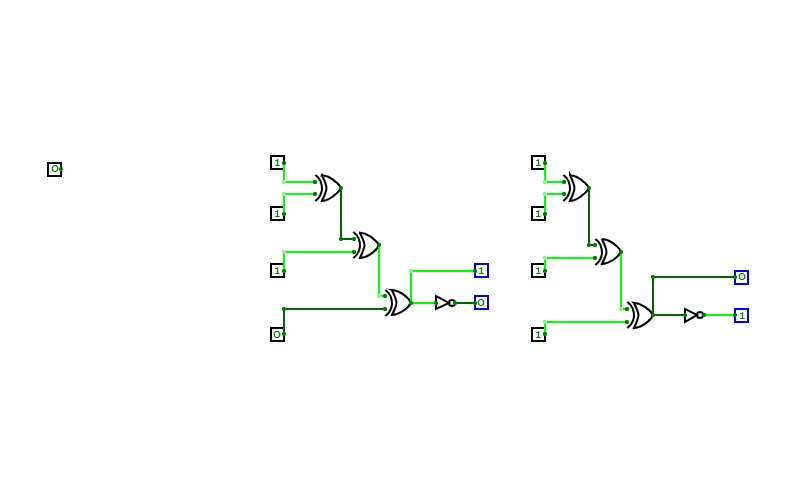

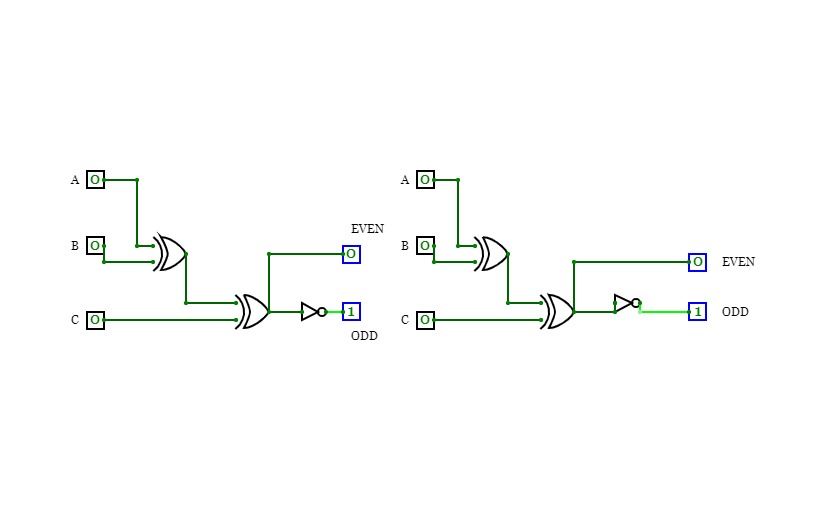

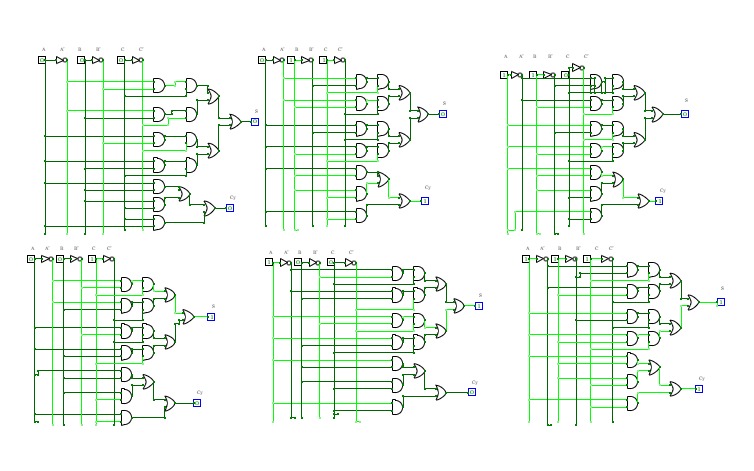

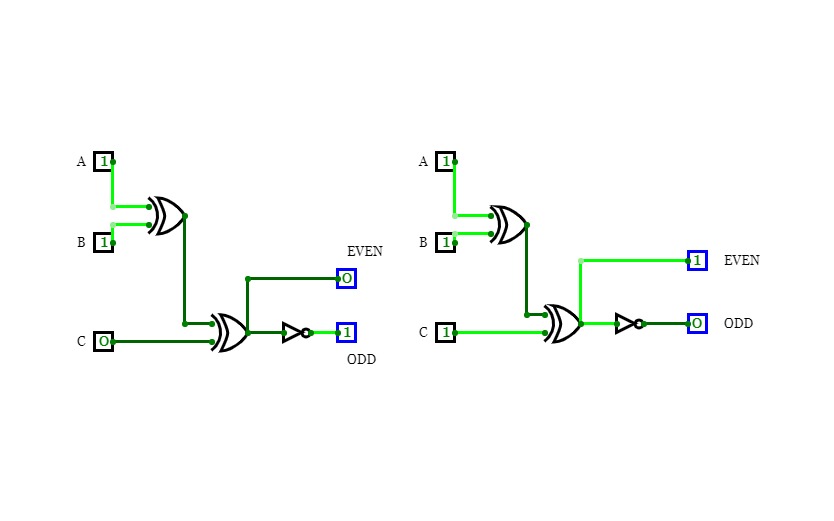

3 BIT PARITY CHECKER

3 BIT PARITY CHECKER

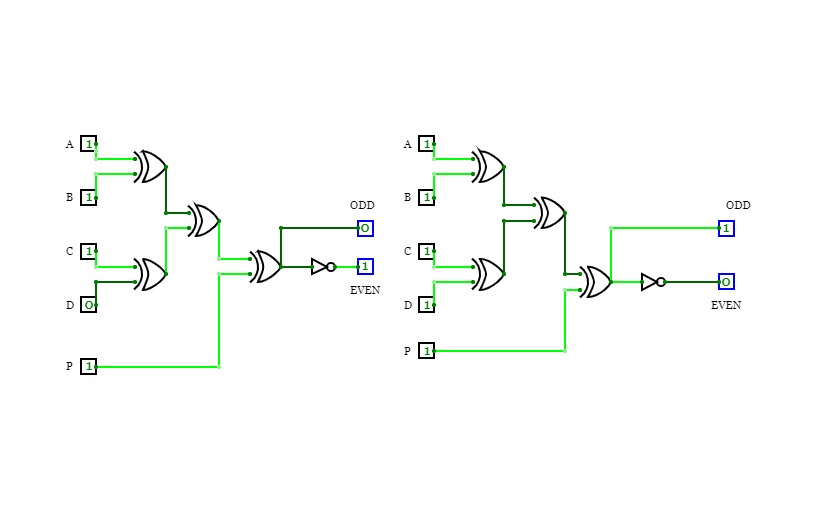

4 BIT PARITY CHECKER

4 BIT PARITY CHECKER

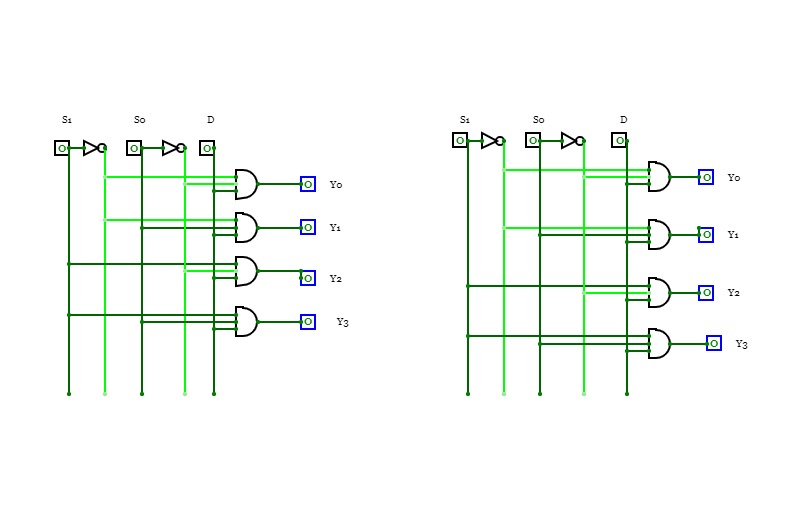

1:4 DEMUX

1:4 DEMUX

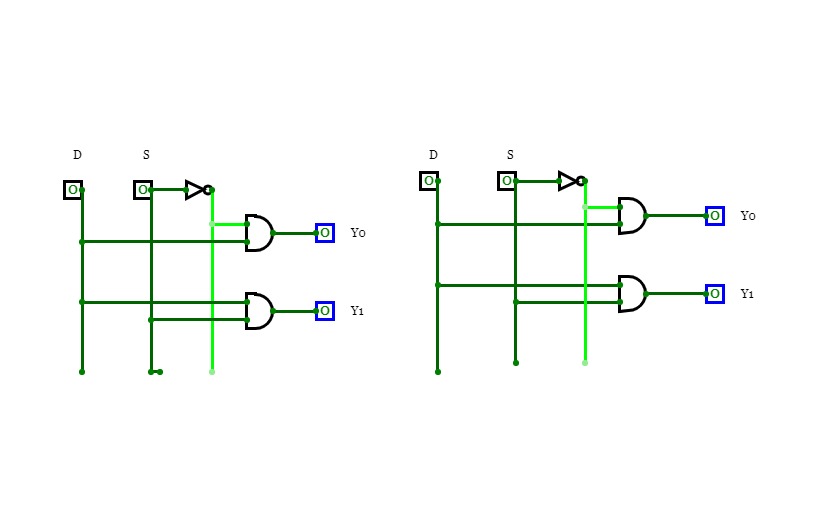

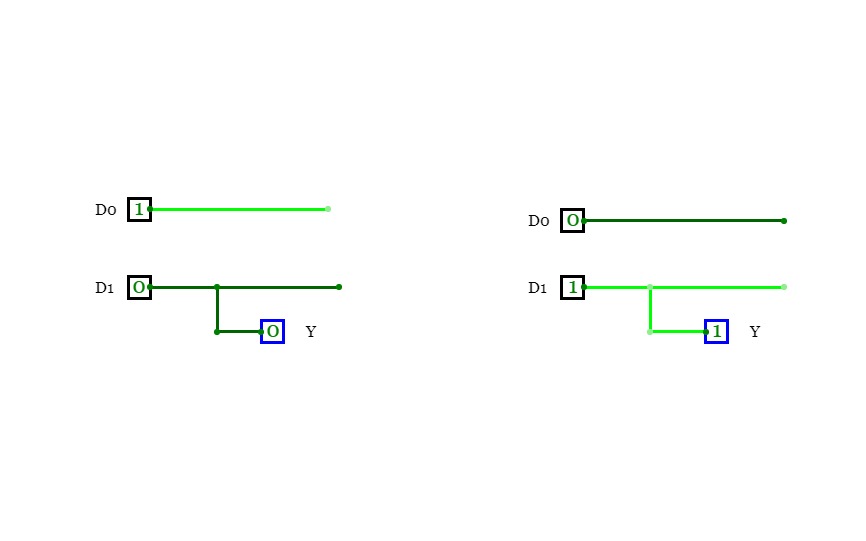

1:2 DEMUX

1:2 DEMUX

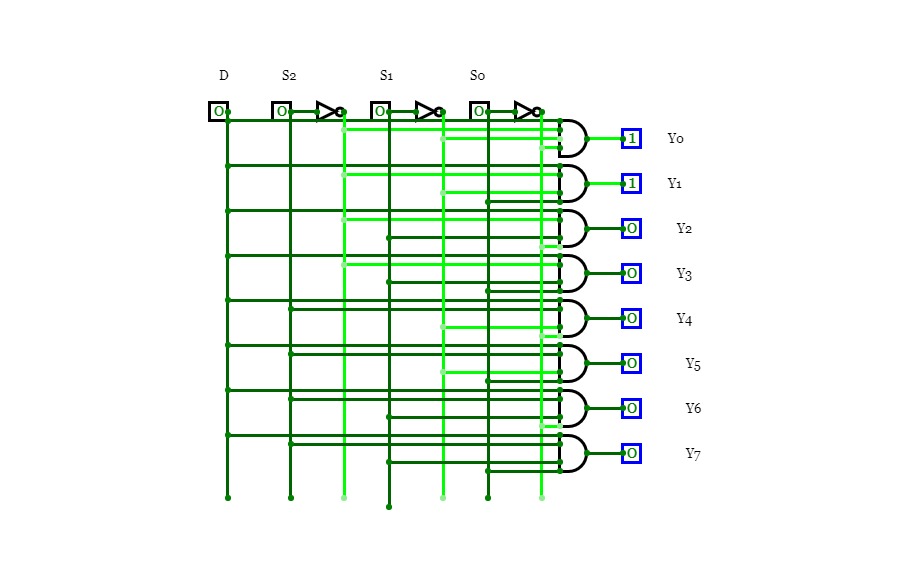

1:8 DEMUX

1:8 DEMUX

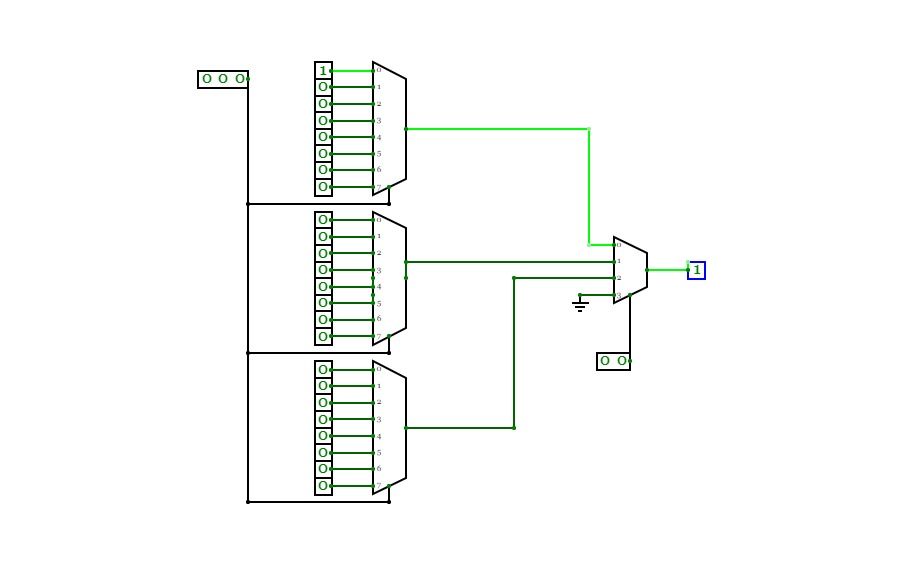

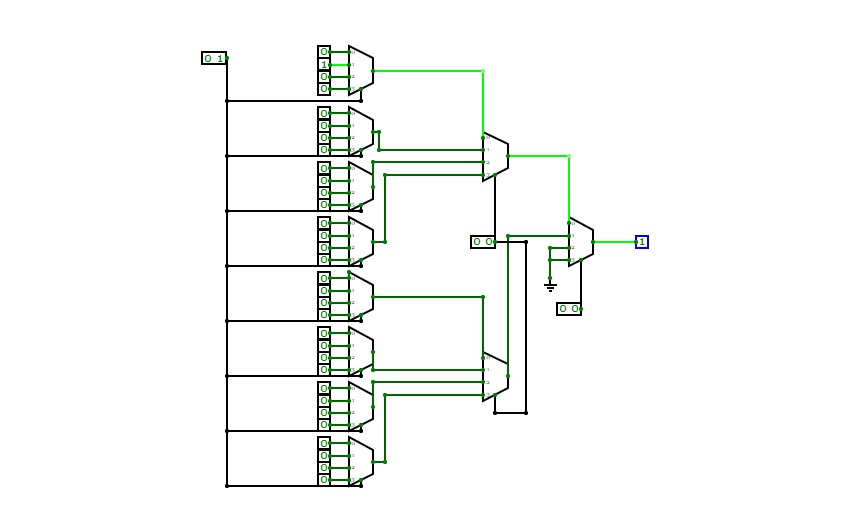

24:1 MUX USING 8:1 MUX

24:1 MUX USING 8:1 MUX

4:1 IMPLEMENTATION

4:1 IMPLEMENTATION

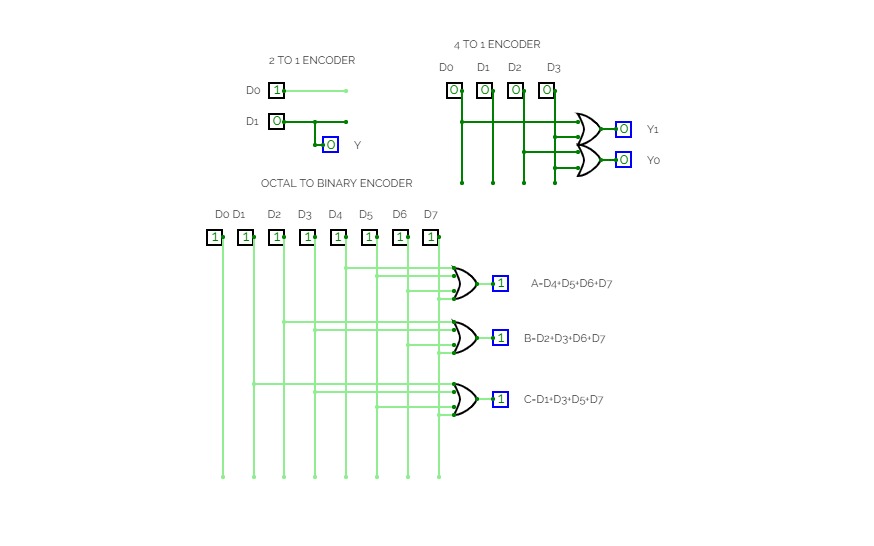

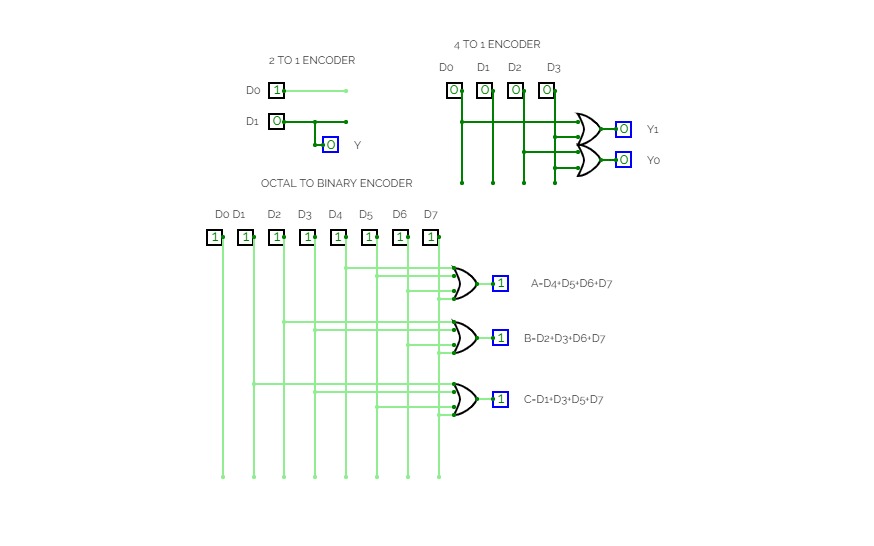

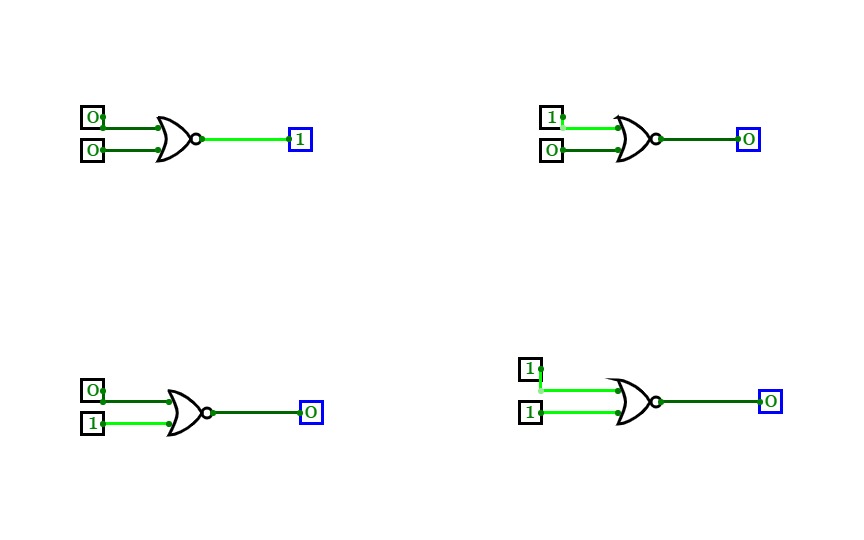

2:1 ENCODER

2:1 ENCODER

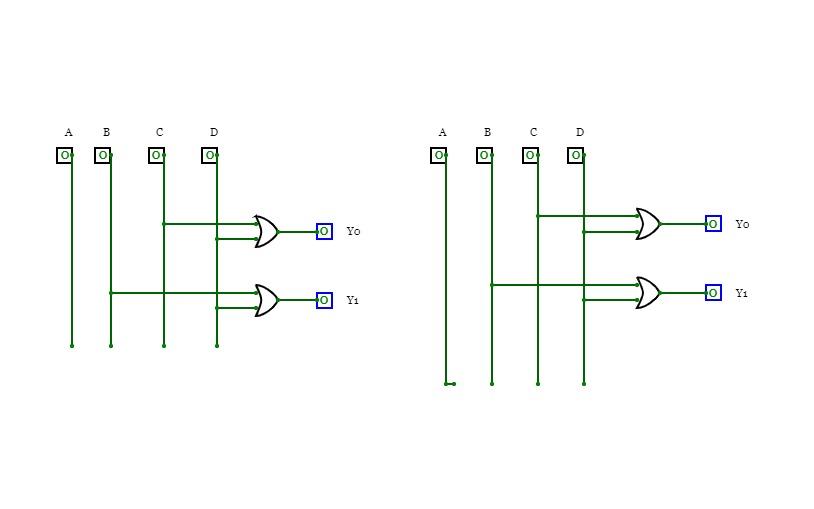

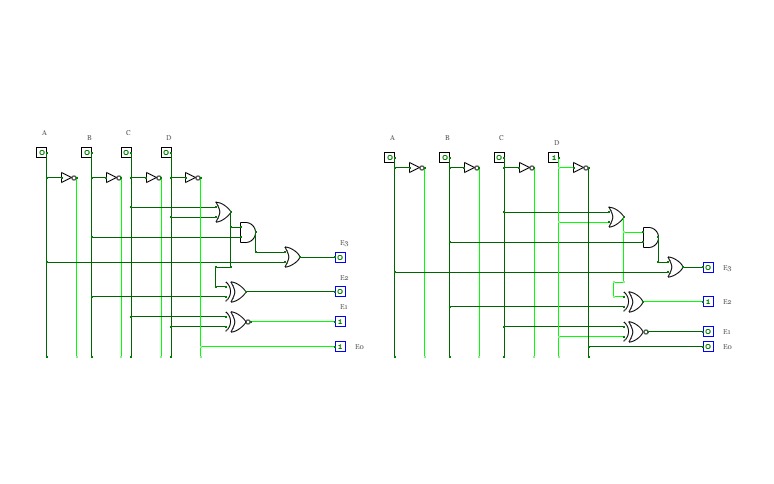

4:2 ENCODER

4:2 ENCODER

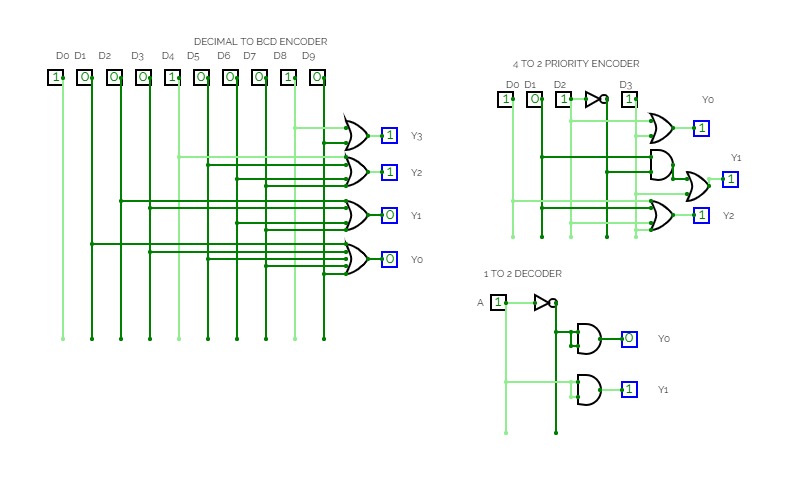

4:2 PRIORITY ENCODER

4:2 PRIORITY ENCODER

16:1 MUX IMPLEMENTATION

16:1 MUX IMPLEMENTATION

HALF SUBTRACTOR USING NOR GATE

HALF SUBTRACTOR USING NOR GATE

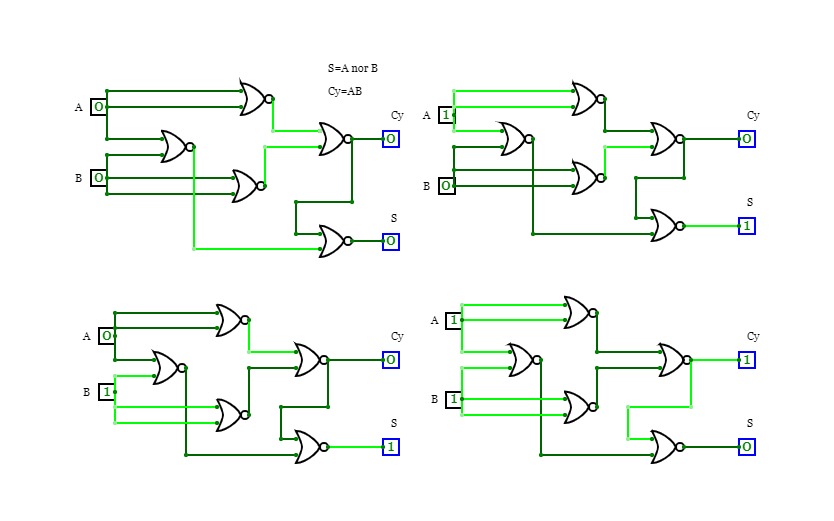

HALF ADDER USING NOR GATE

HALF ADDER USING NOR GATE

4 BIT PARITY GENERATOR

4 BIT PARITY GENERATOR

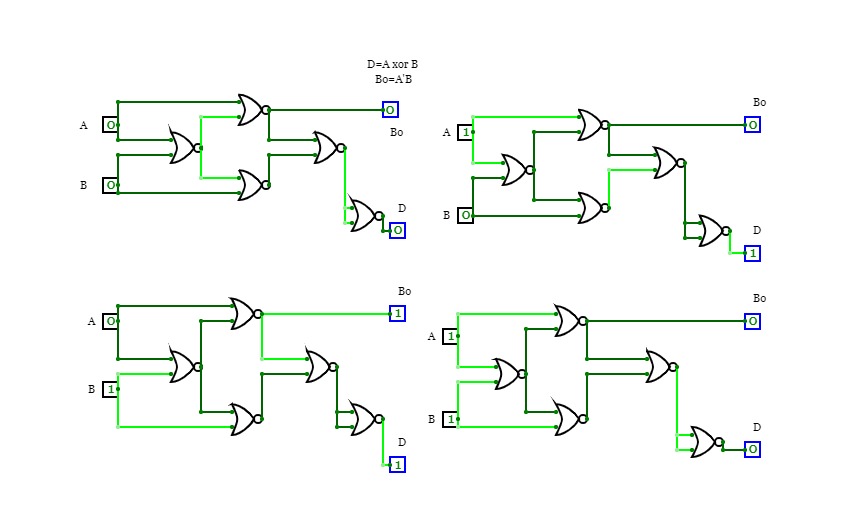

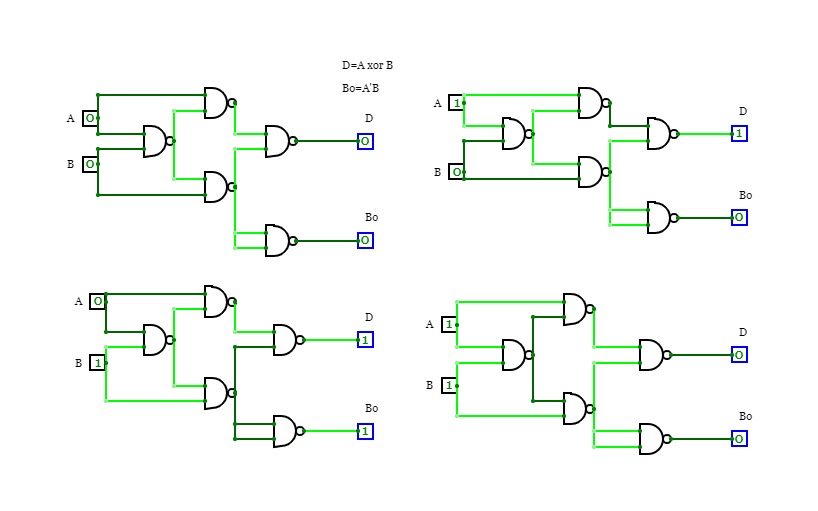

HALF SUBTRACTOR USING XOR GATE

HALF SUBTRACTOR USING XOR GATE

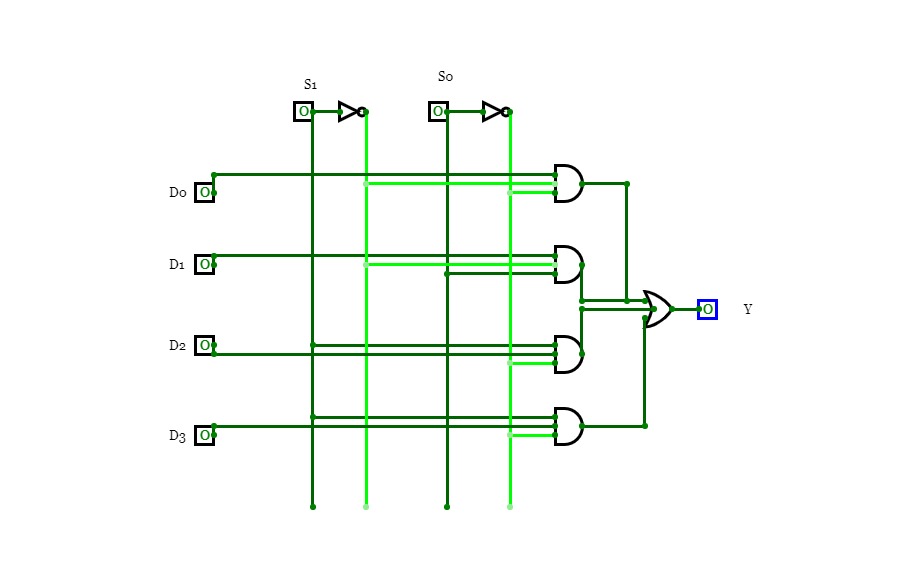

4:1 MUX

4:1 MUX

FULL ADDER USING NOR GATES

FULL ADDER USING NOR GATES

HALF SUBTRACTOR USING NAND GATE

HALF SUBTRACTOR USING NAND GATE

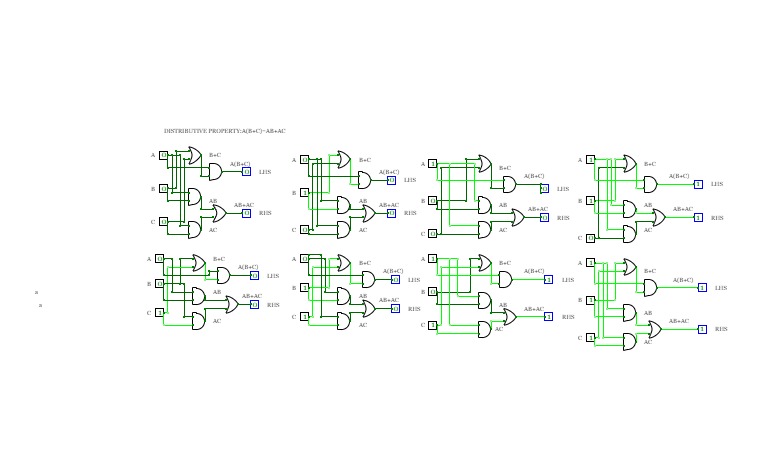

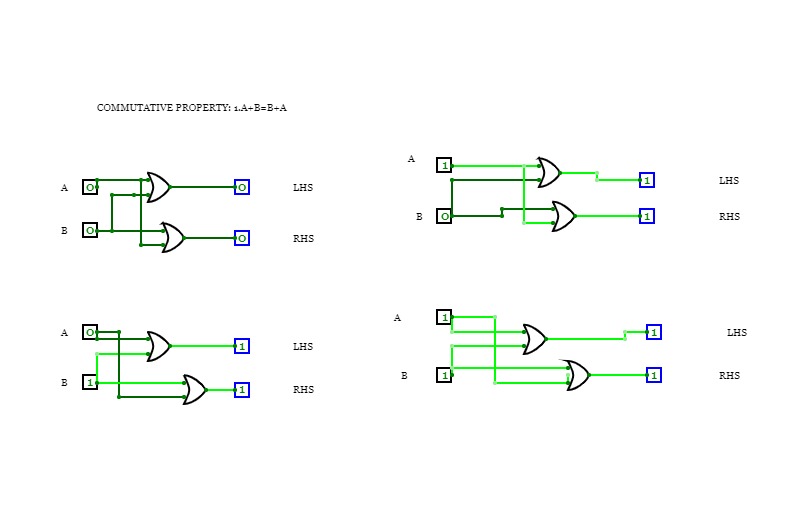

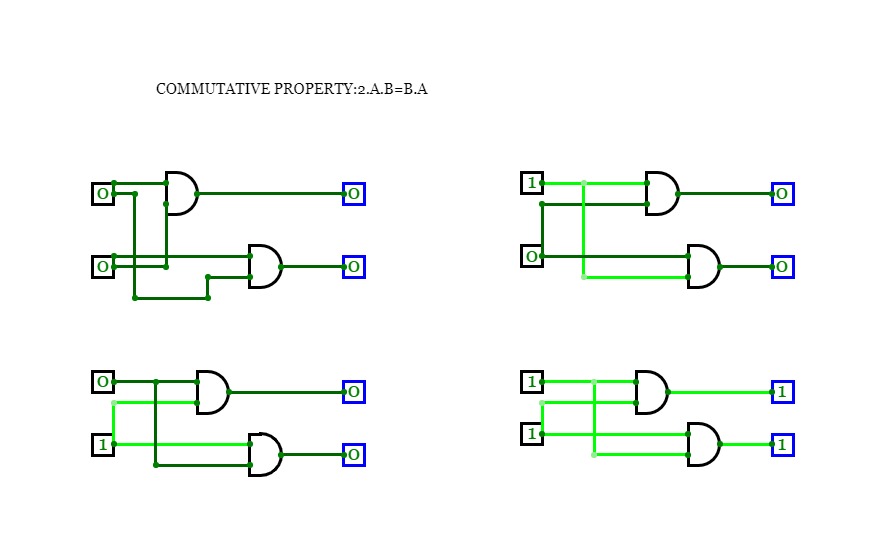

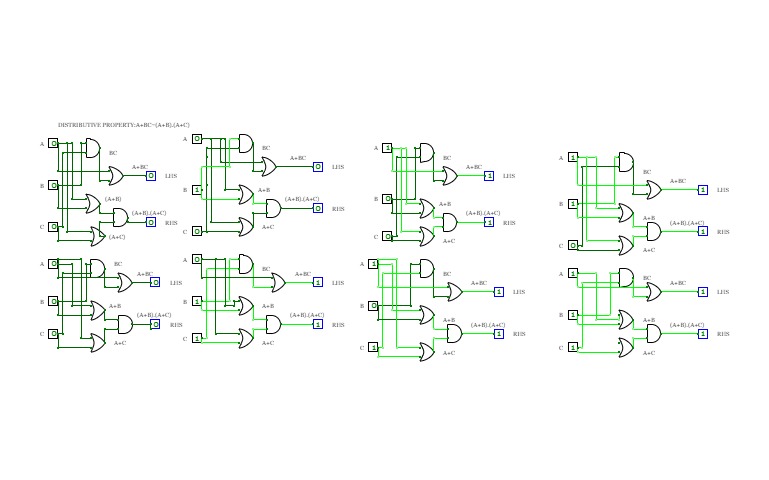

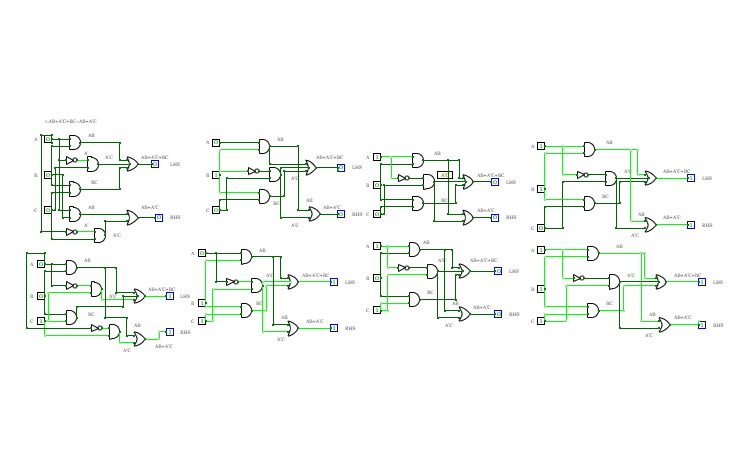

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

3 BIT PARITY GENERATOR

3 BIT PARITY GENERATOR

HALF SUBTRACTOR USING BASIC GATES

HALF SUBTRACTOR USING BASIC GATES

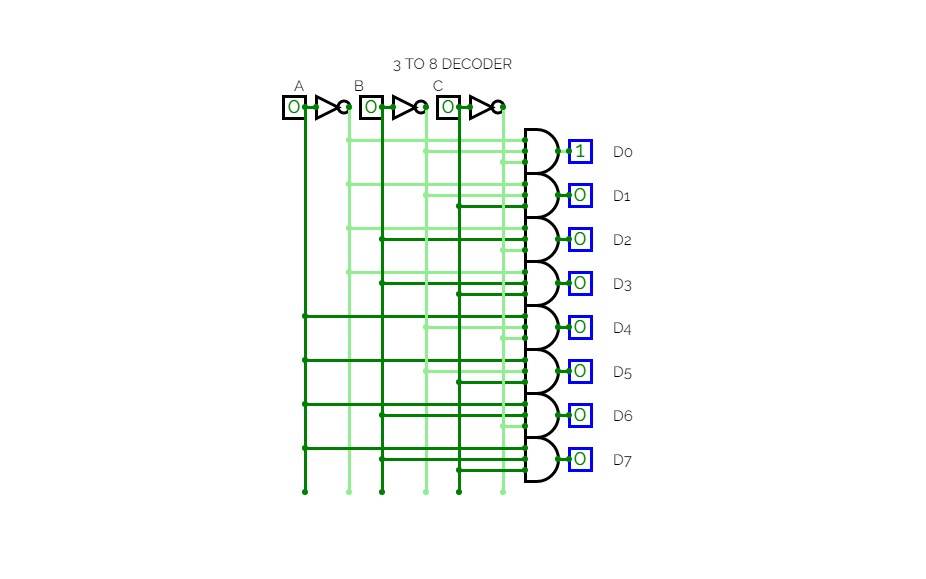

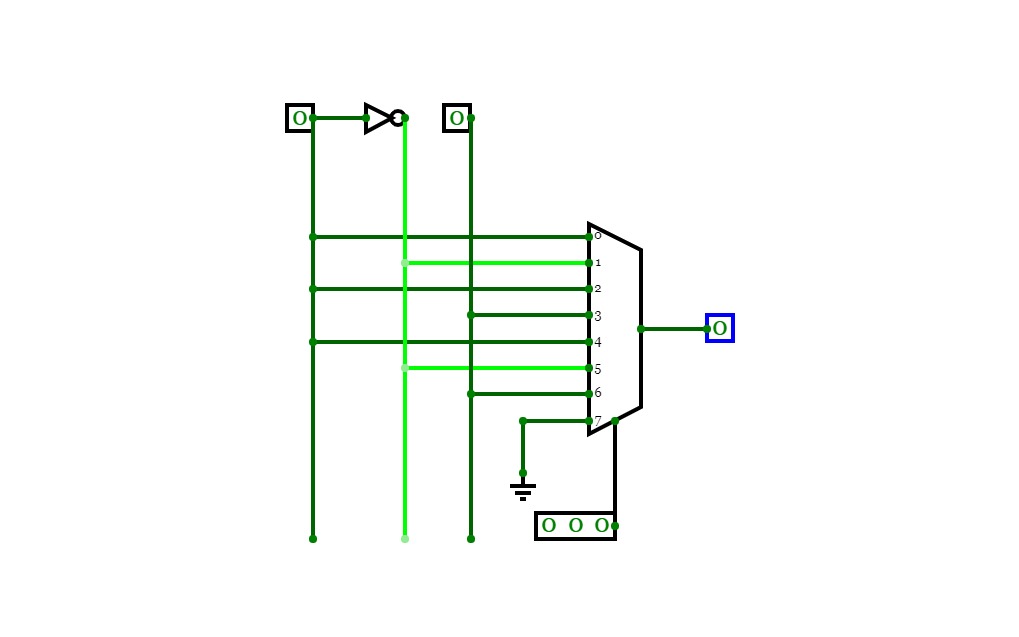

3 TO 8 DECODER

3 TO 8 DECODER

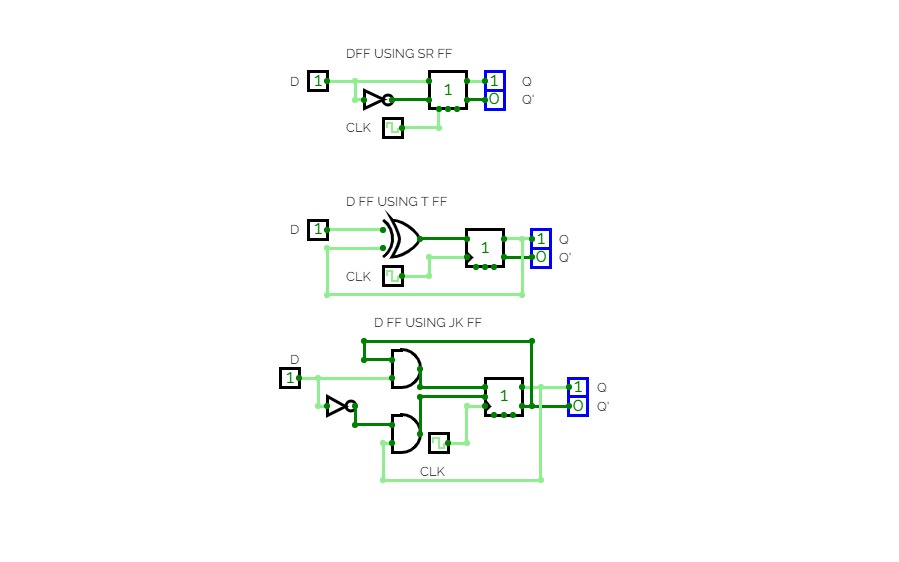

D FF USING OTHER FF

D FF USING OTHER FF

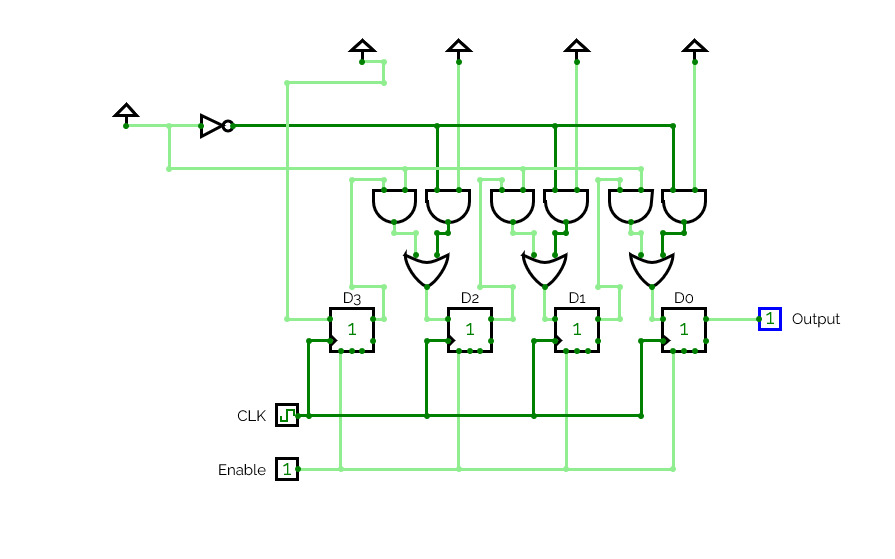

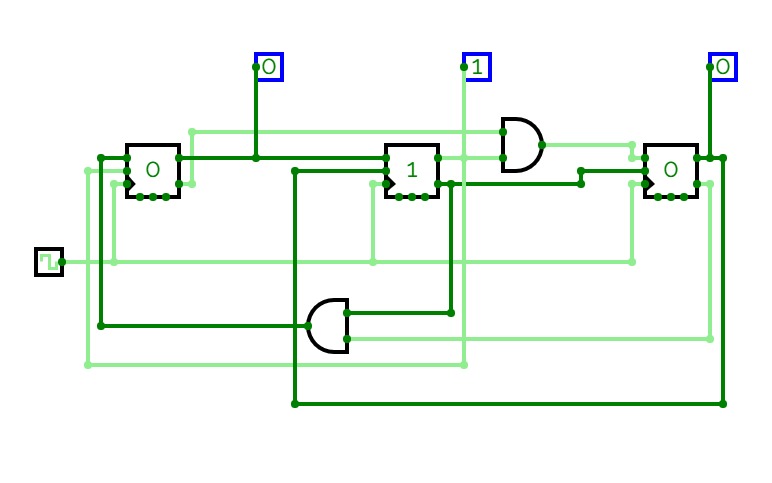

PISO

PISO

Untitled

Untitled

4 bit synchronous down counter

4 bit synchronous down counter

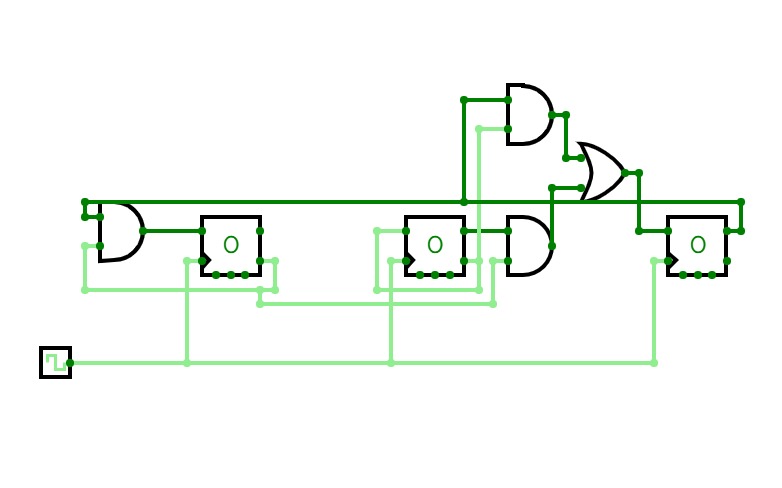

SISO

SISO

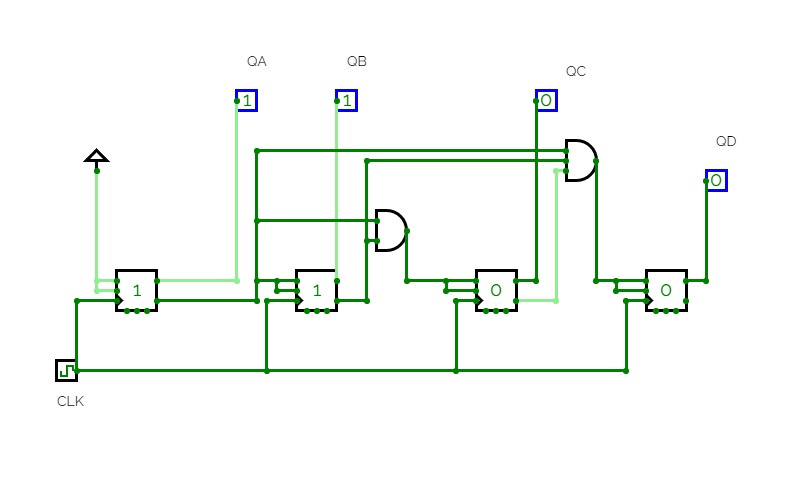

sequence generator using counter

sequence generator using counter

mod-6 unit distance counter

mod-6 unit distance counter

counter that counts 0,2,4,7,0

counter that counts 0,2,4,7,0

3 bit binary counter

3 bit binary counter

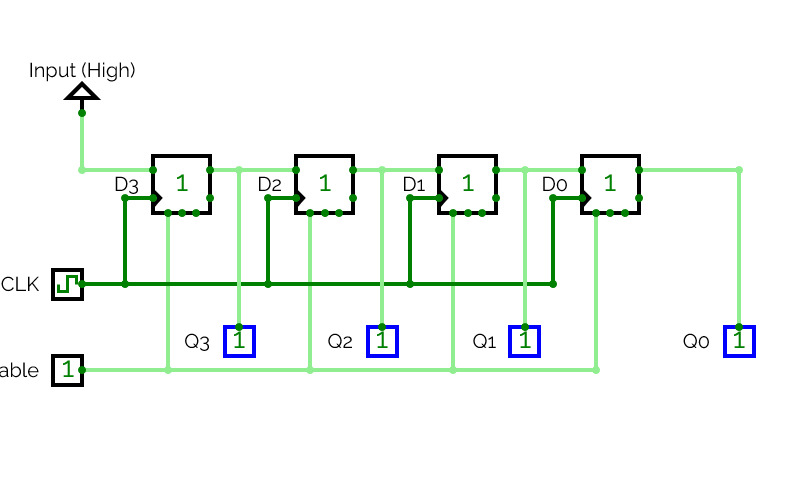

PIPO

PIPO

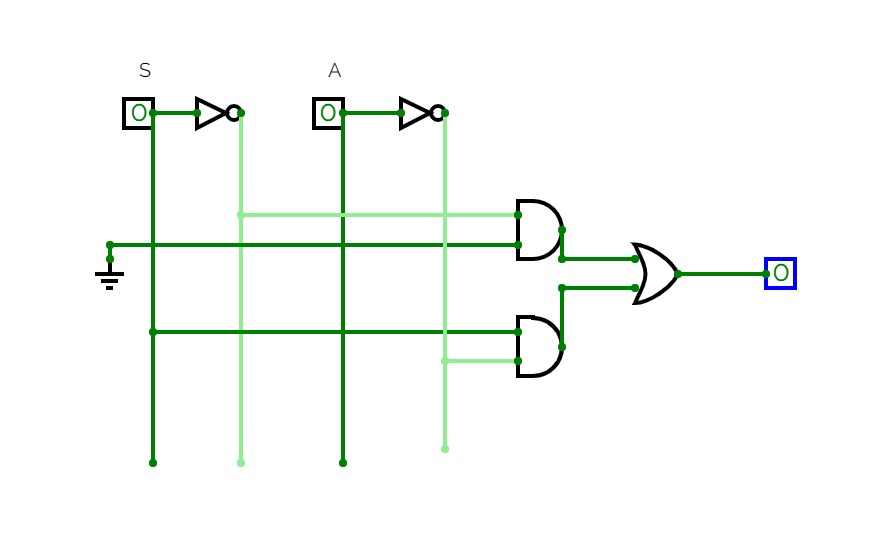

OR USING 2 TO 1 MUX

OR USING 2 TO 1 MUX

Untitled

Untitled

NOR USING 2 TO 1 MUX

NOR USING 2 TO 1 MUX

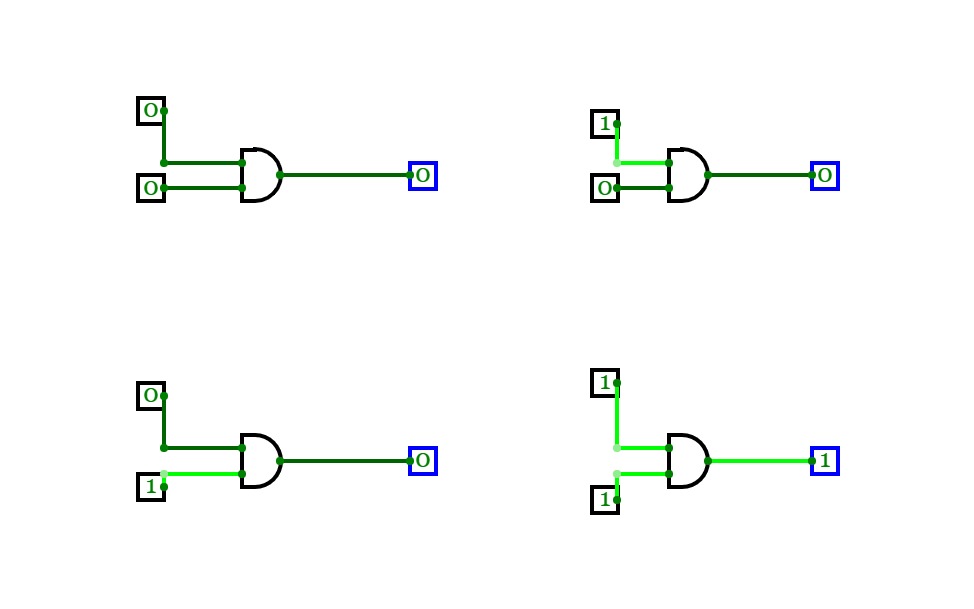

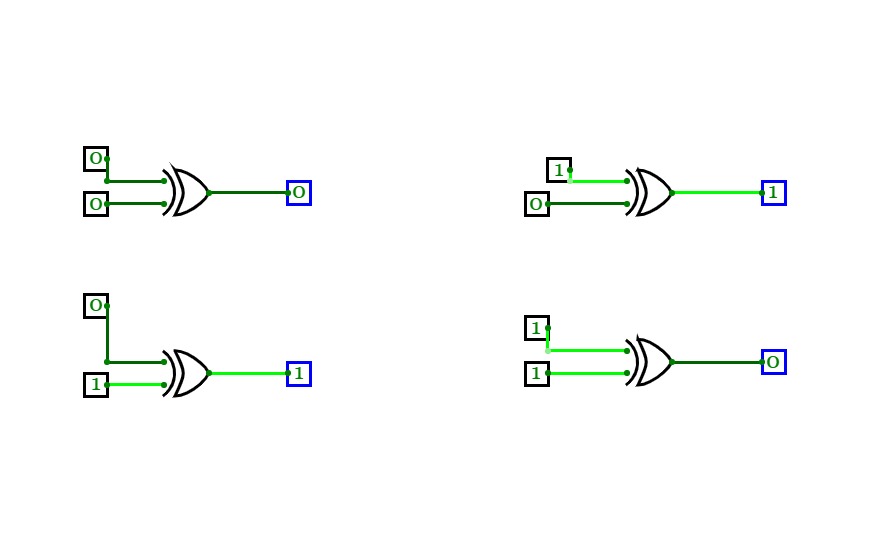

AND GATE

AND GATE

NOT USING 2 TO 1 MUX

NOT USING 2 TO 1 MUX

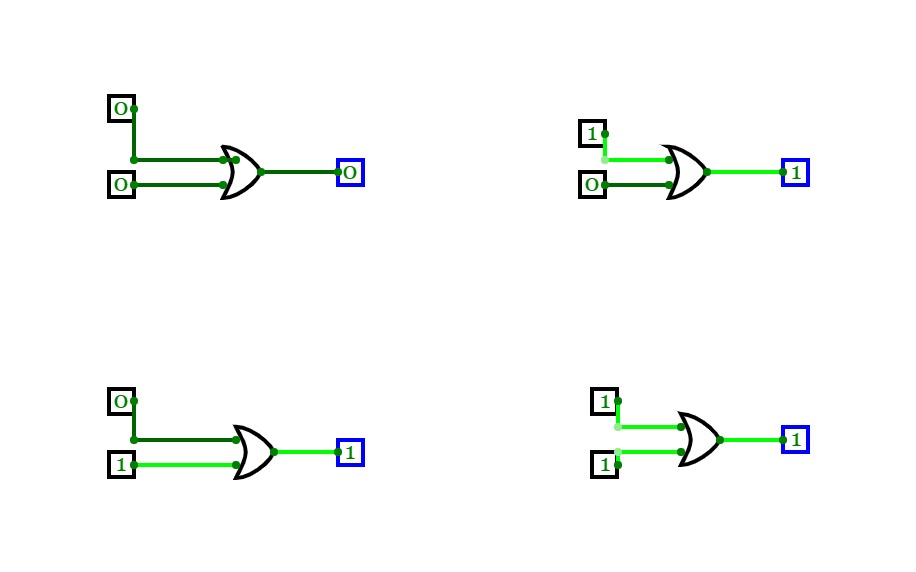

OR GATE

OR GATE

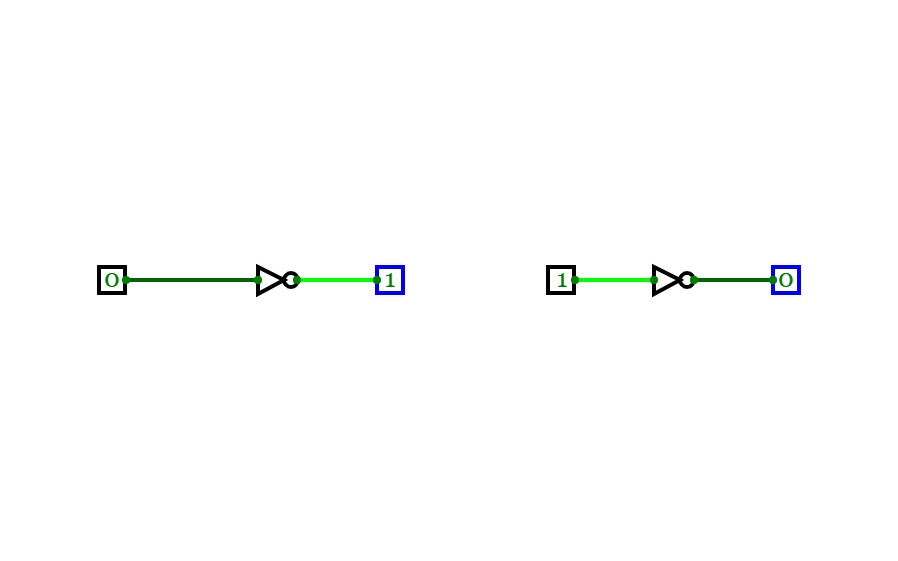

NOT GATE

NOT GATE

EXP 8.2

EXP 8.2

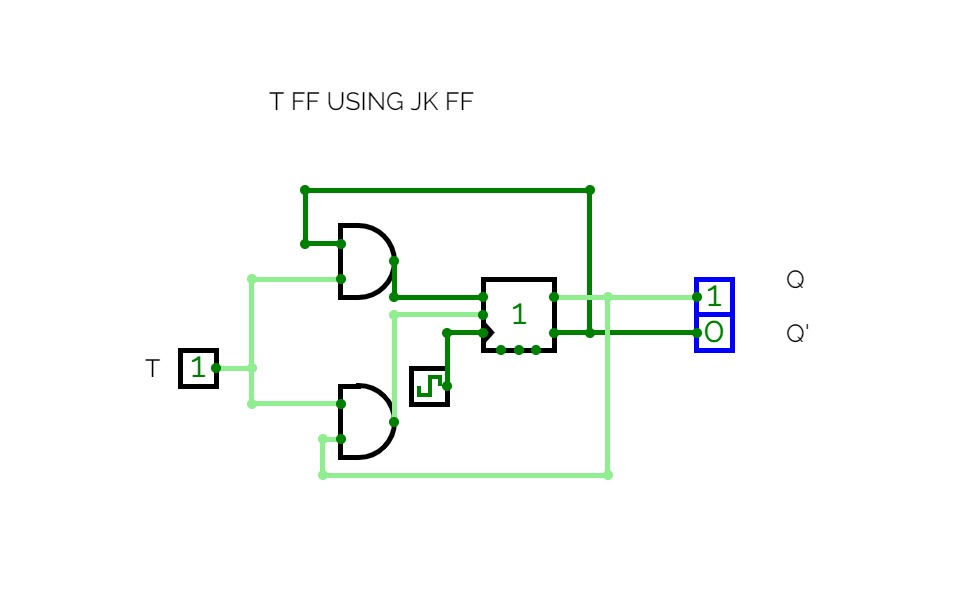

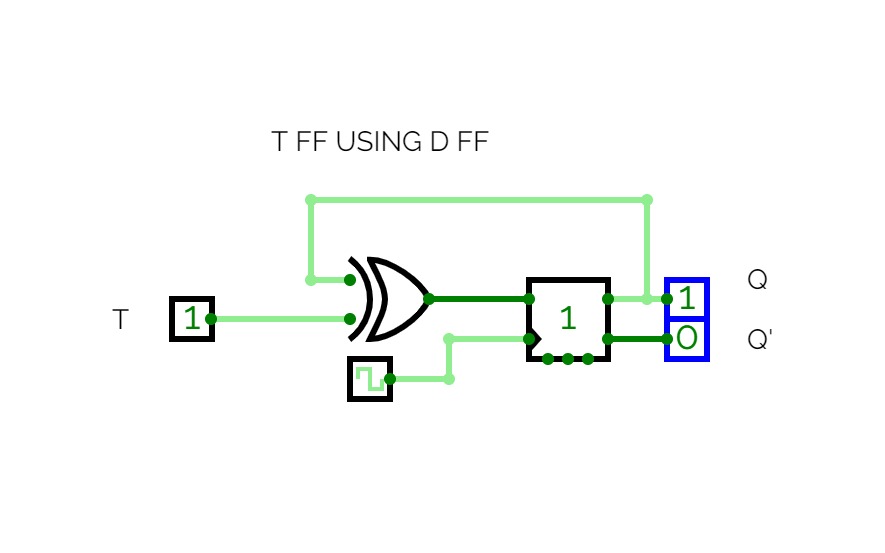

T FF USING D FF

T FF USING D FF

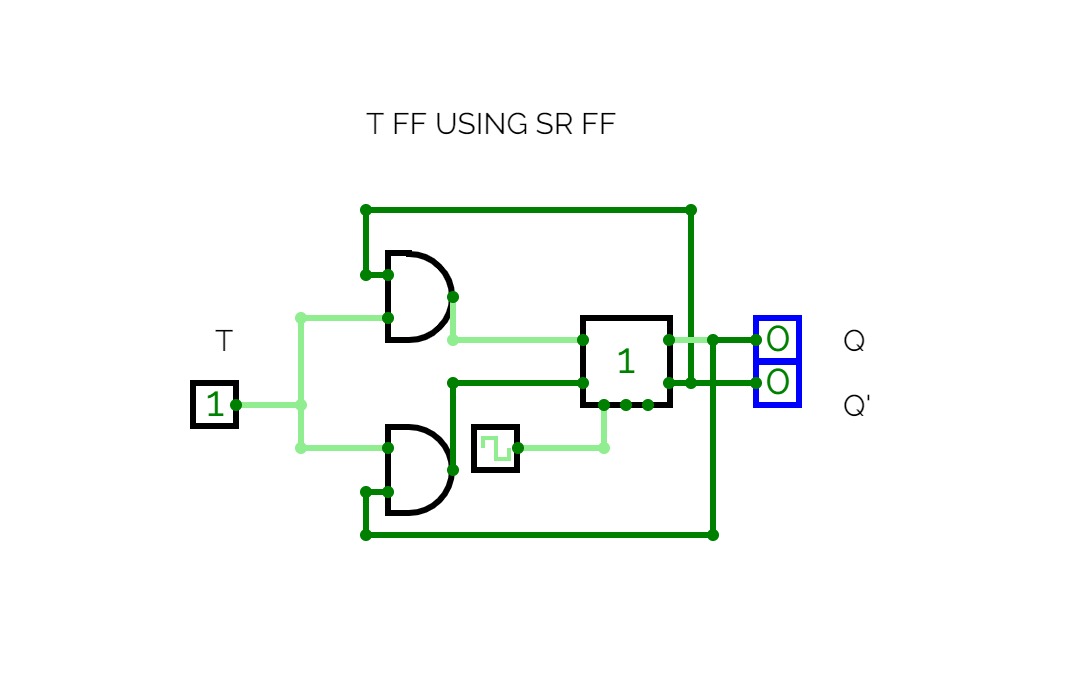

T FF USING SR FF

T FF USING SR FF

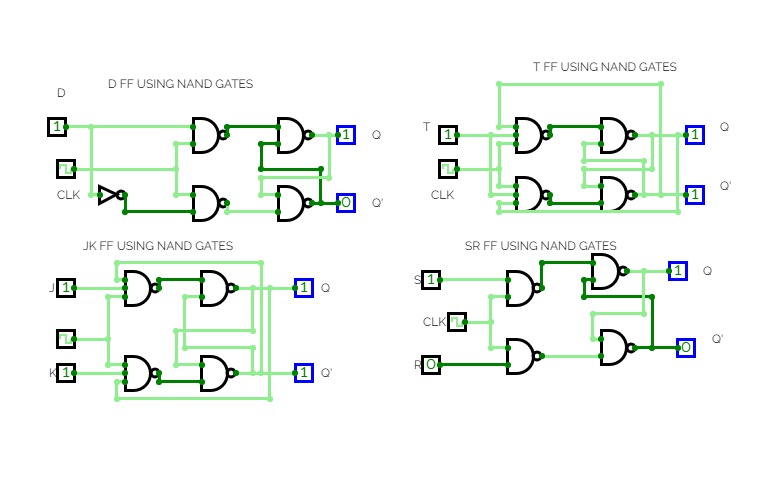

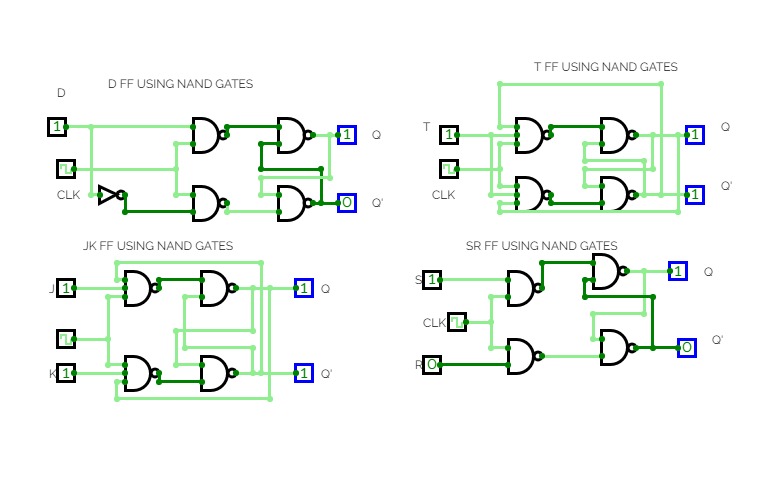

SR JK D T FF

SR JK D T FF

SR JK D T FF

SR JK D T FF

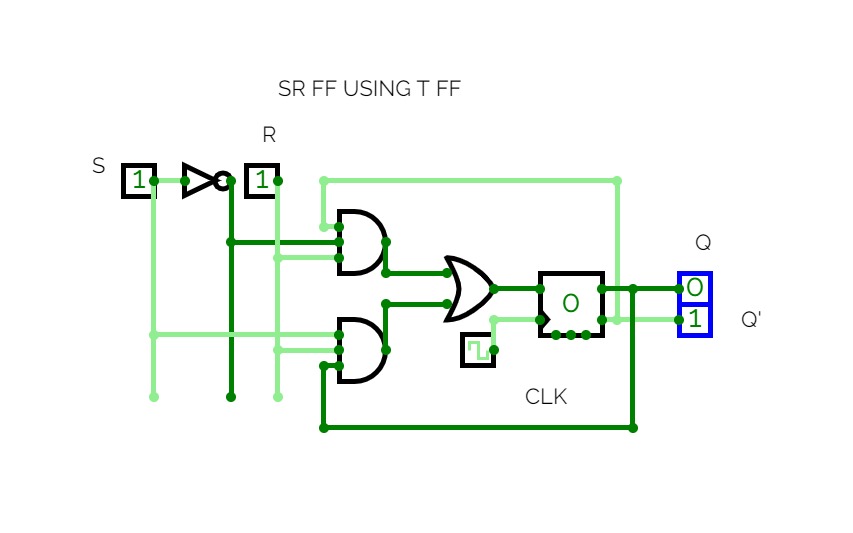

SR FF USING T FF

SR FF USING T FF

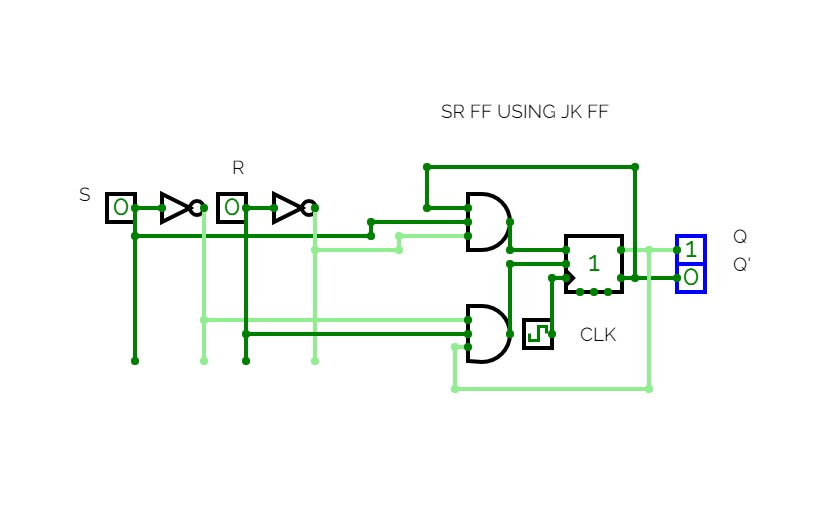

SR FF USING JK FF

SR FF USING JK FF

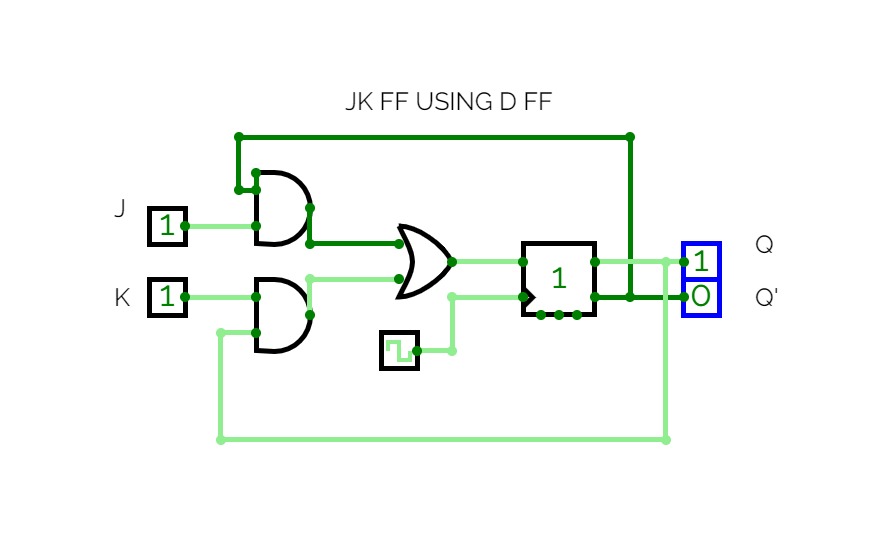

JK FF USING D FF

JK FF USING D FF

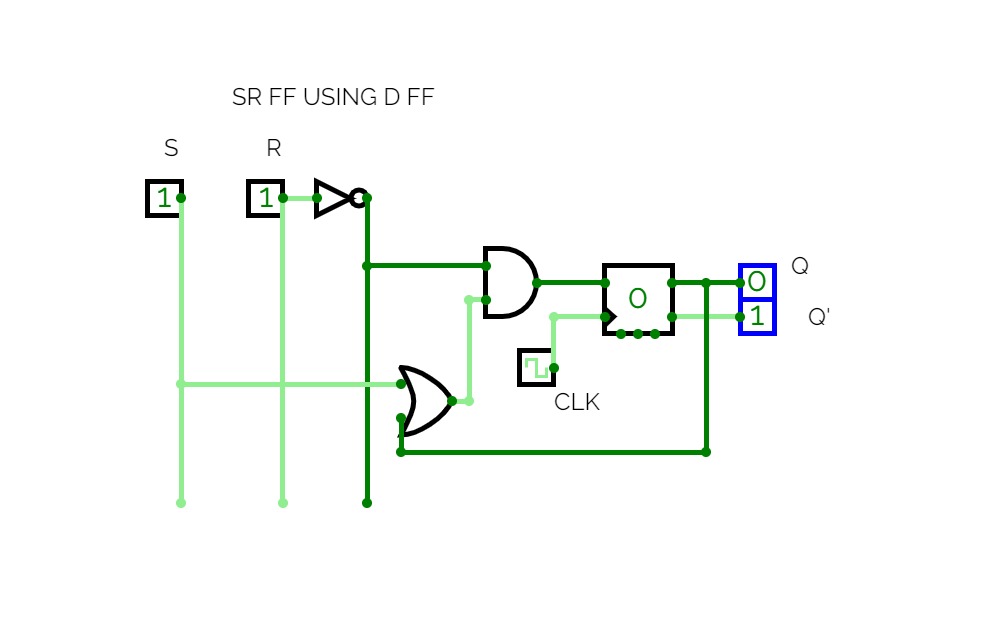

SR FF USING DFF

SR FF USING DFF

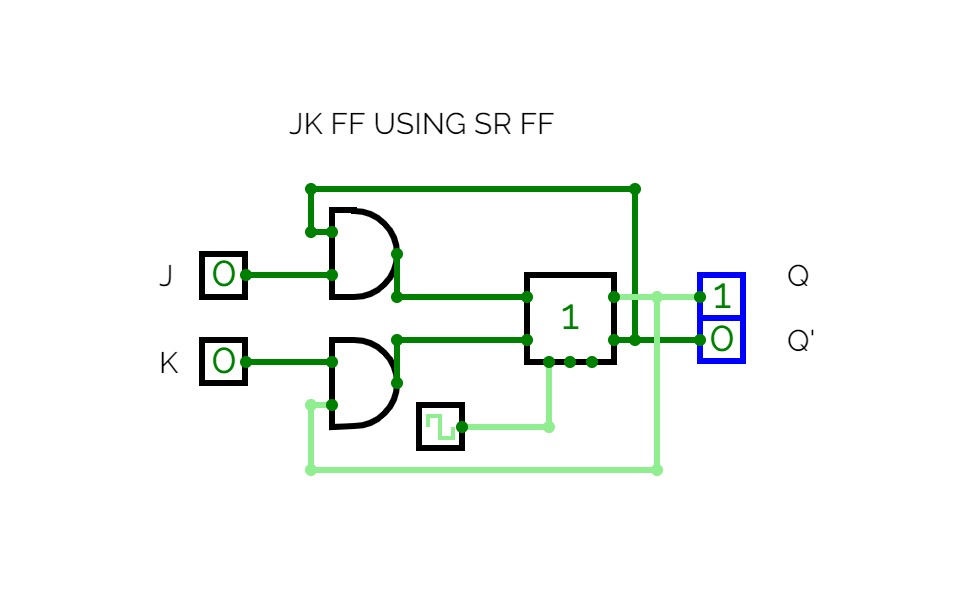

JK FF USING SR FF

JK FF USING SR FF

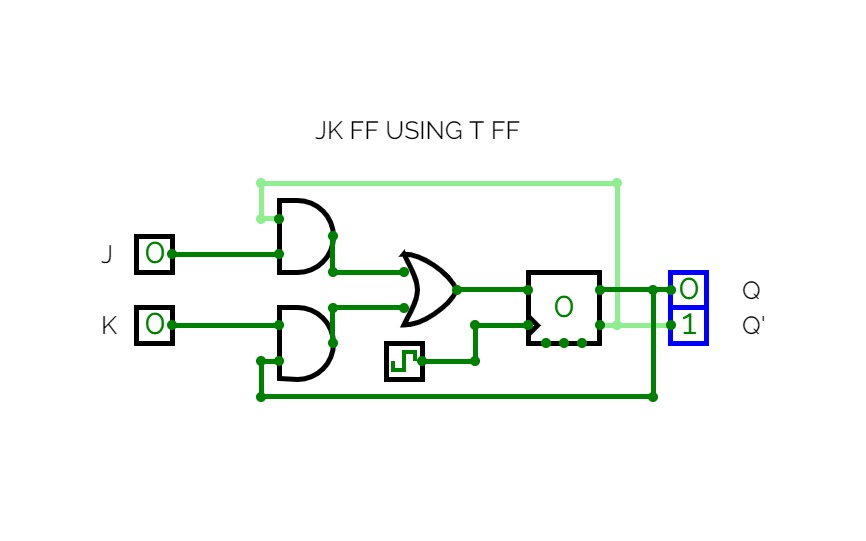

JK FF USING T FF

JK FF USING T FF

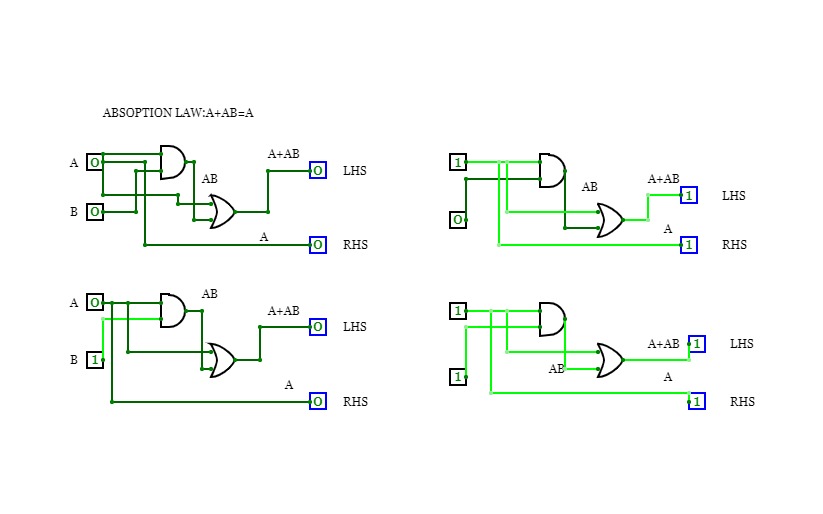

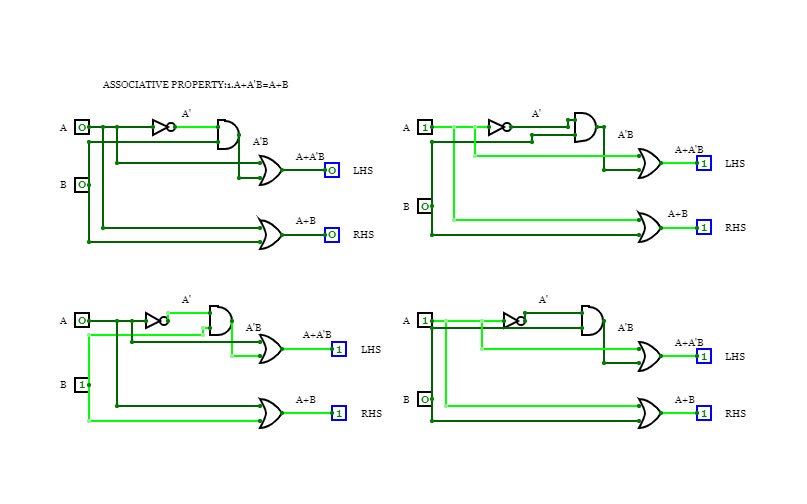

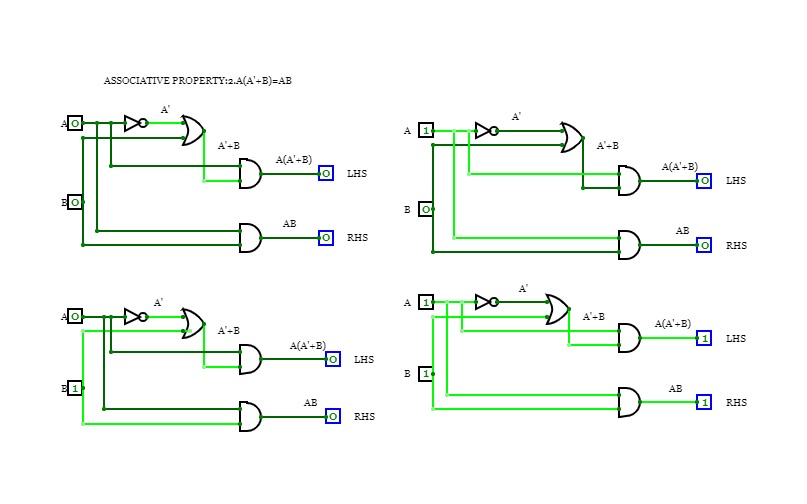

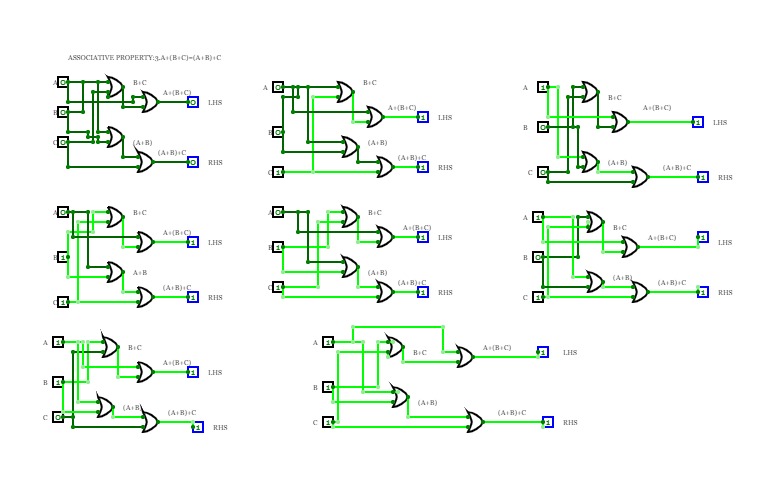

VERIFICATION OF BOOLEAN PROPERTY AND LAWS

VERIFICATION OF BOOLEAN PROPERTY AND LAWS

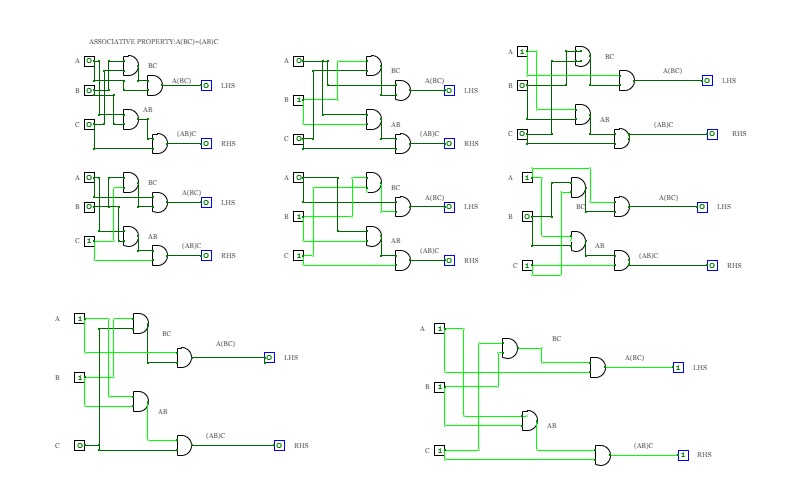

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

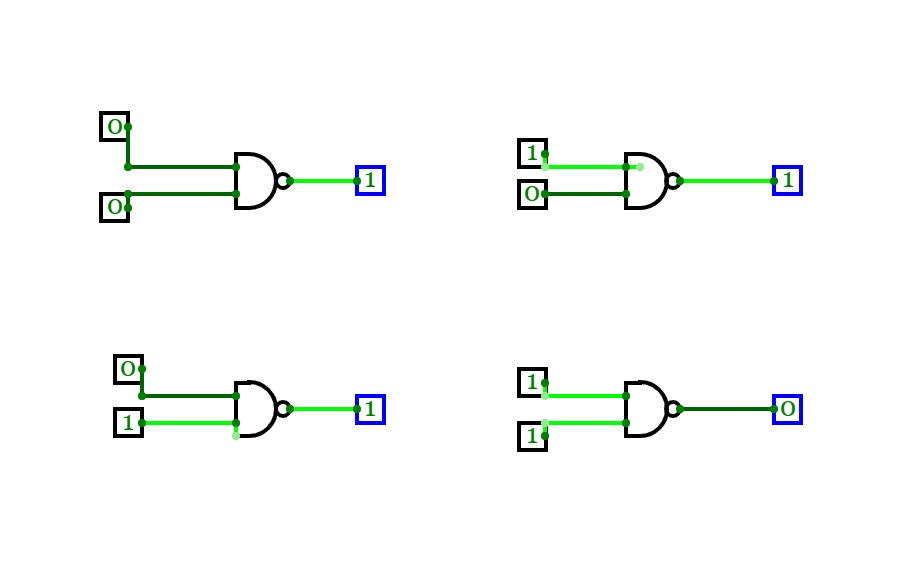

NAND GATE

NAND GATE

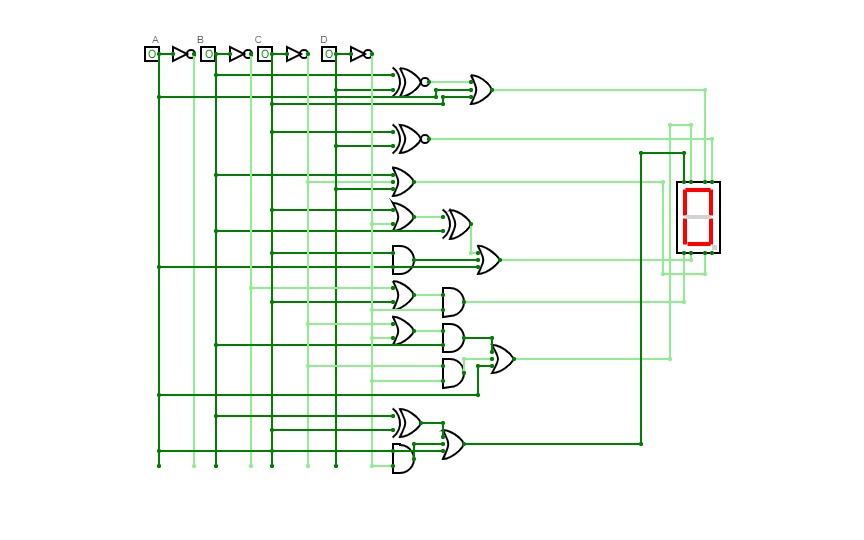

BCD TO SEVEN SEGMENT DECODER

BCD TO SEVEN SEGMENT DECODER

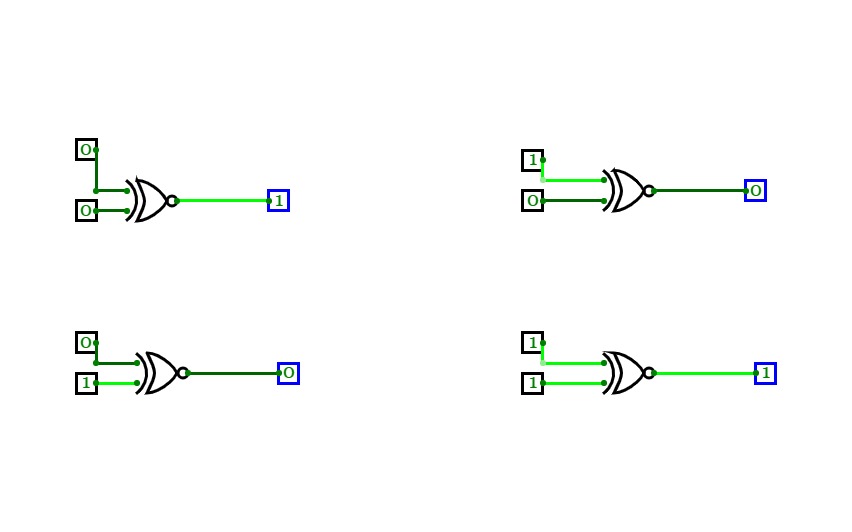

NOR GATE

NOR GATE

Xnor GATE

Xnor GATE

BCD TO EXCESS-3 CONVERTER I

BCD TO EXCESS-3 CONVERTER I

HALF ADDER USING NAND GATE

HALF ADDER USING NAND GATE

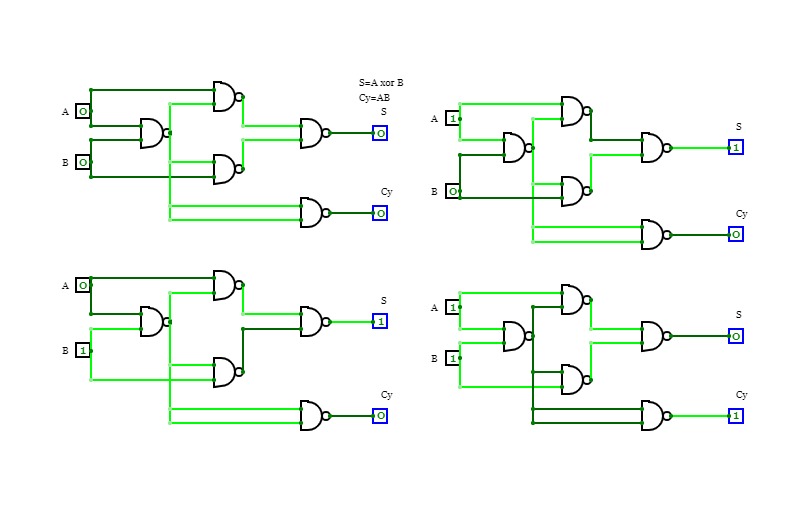

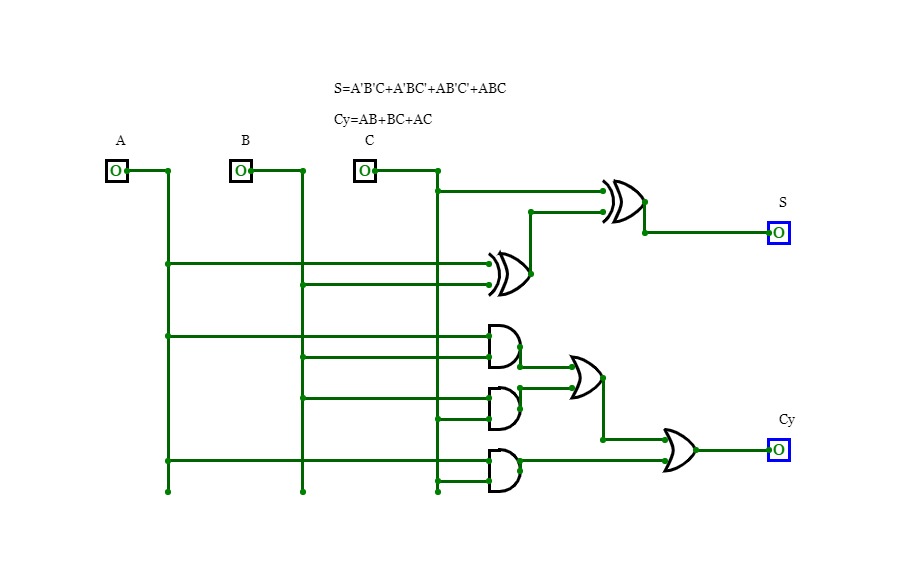

FULL ADDER USING BASIC GATES

FULL ADDER USING BASIC GATES

Xor GATE

Xor GATE

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

VERIFICATION OF BOOLEAN POSTULATES AND LAWS

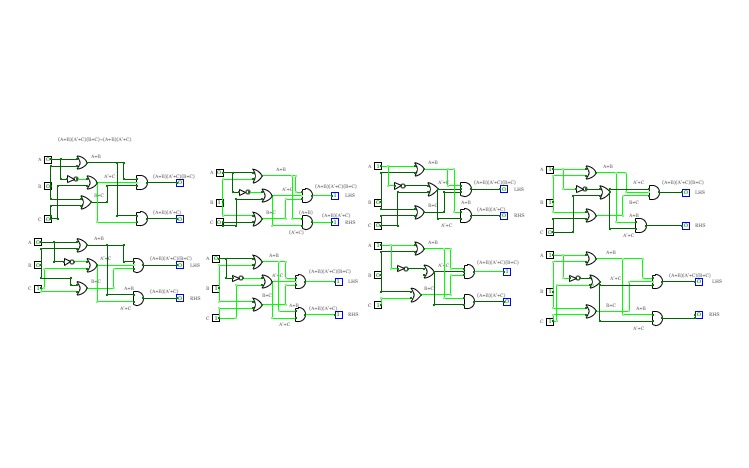

CONSENSUS THEOREM

CONSENSUS THEOREM

CONSENSUS THEOREM

CONSENSUS THEOREM

4 bit bidirectional shift register

4 bit bidirectional shift register

8:1 MUX IMPLEMENTATION

8:1 MUX IMPLEMENTATION

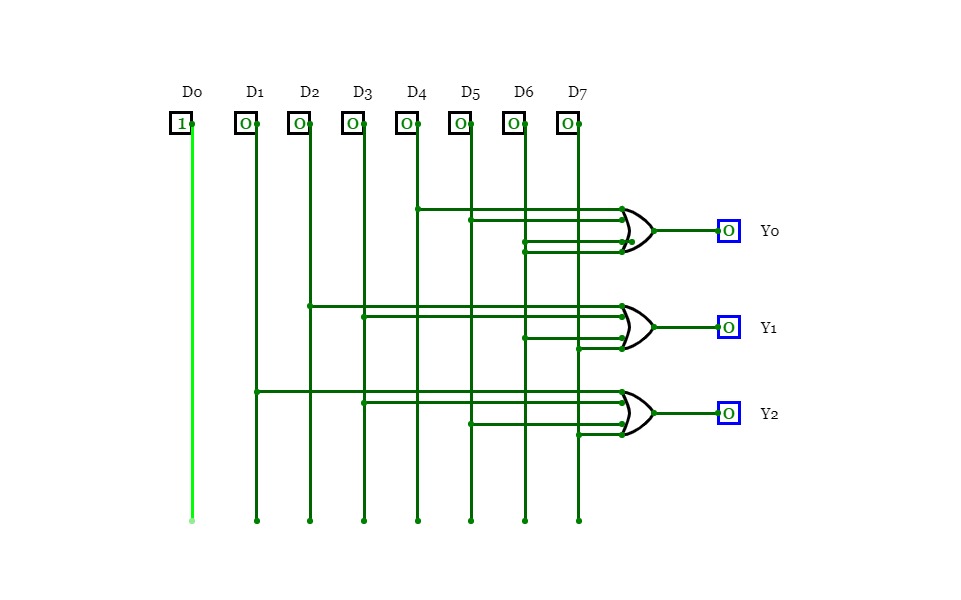

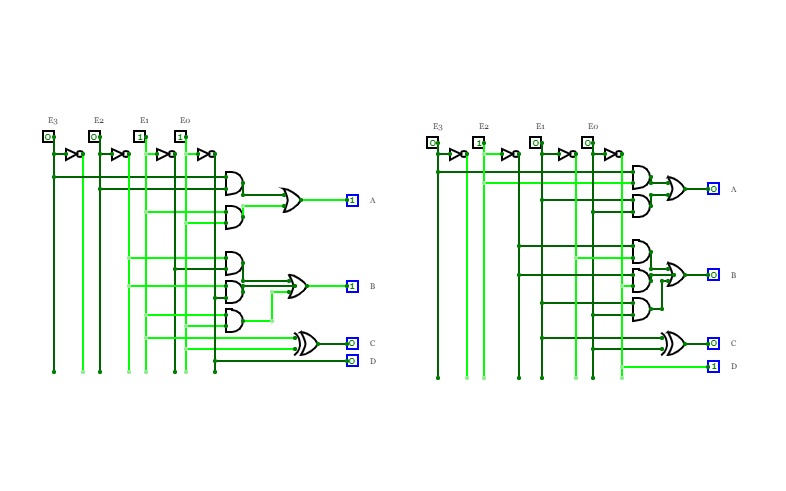

8:3 ENCODER

8:3 ENCODER

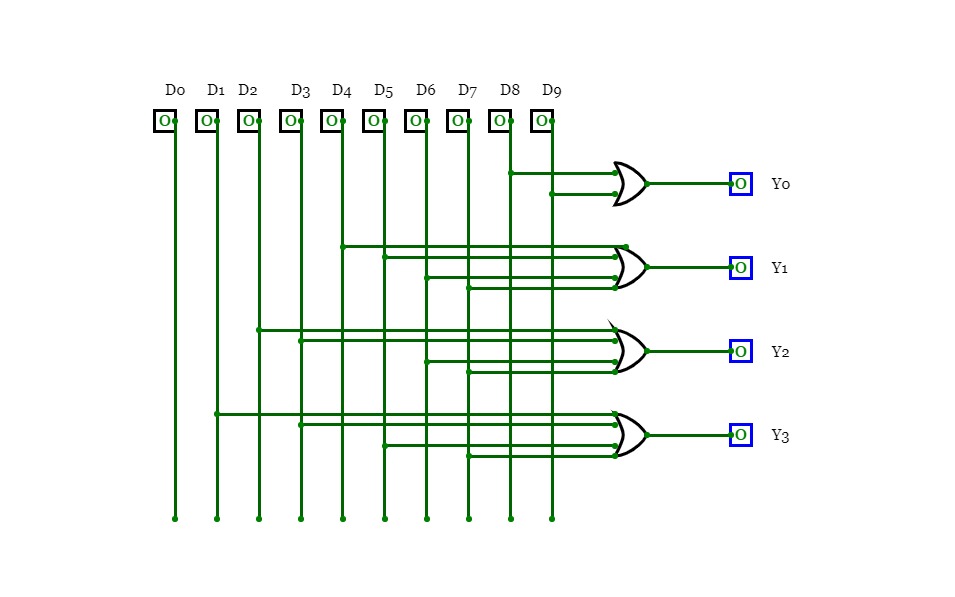

10:4 ENCODER

10:4 ENCODER

EXCESS - 3 TO BCD CONVERTER I

EXCESS - 3 TO BCD CONVERTER I

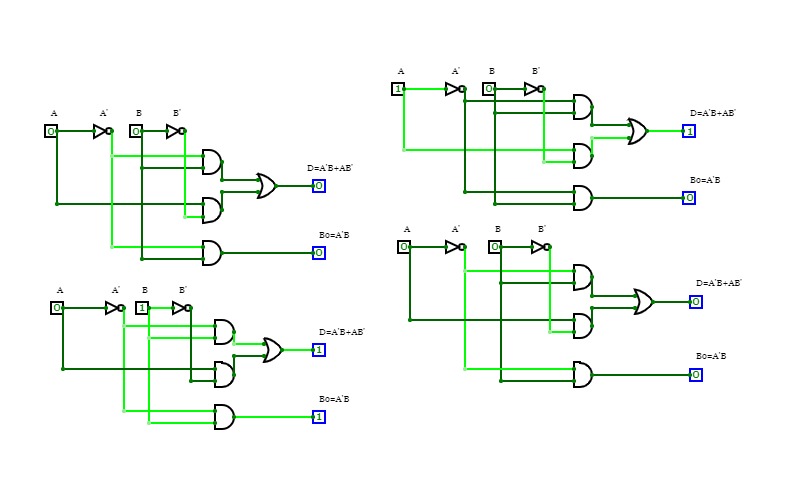

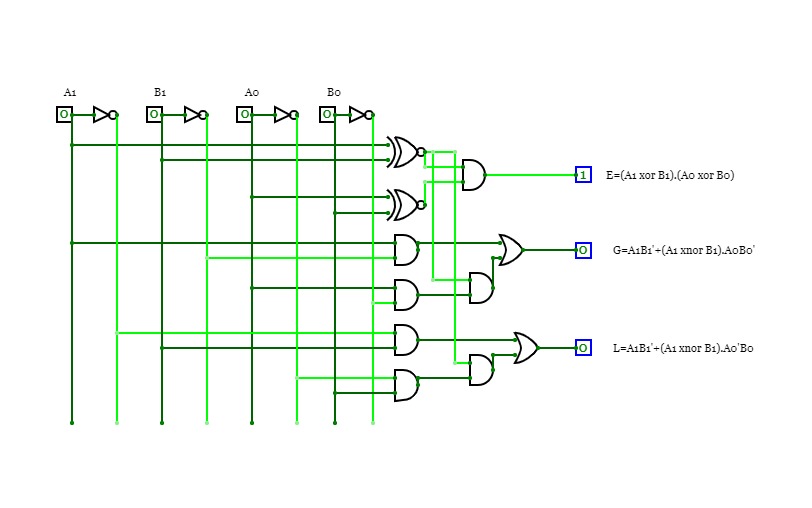

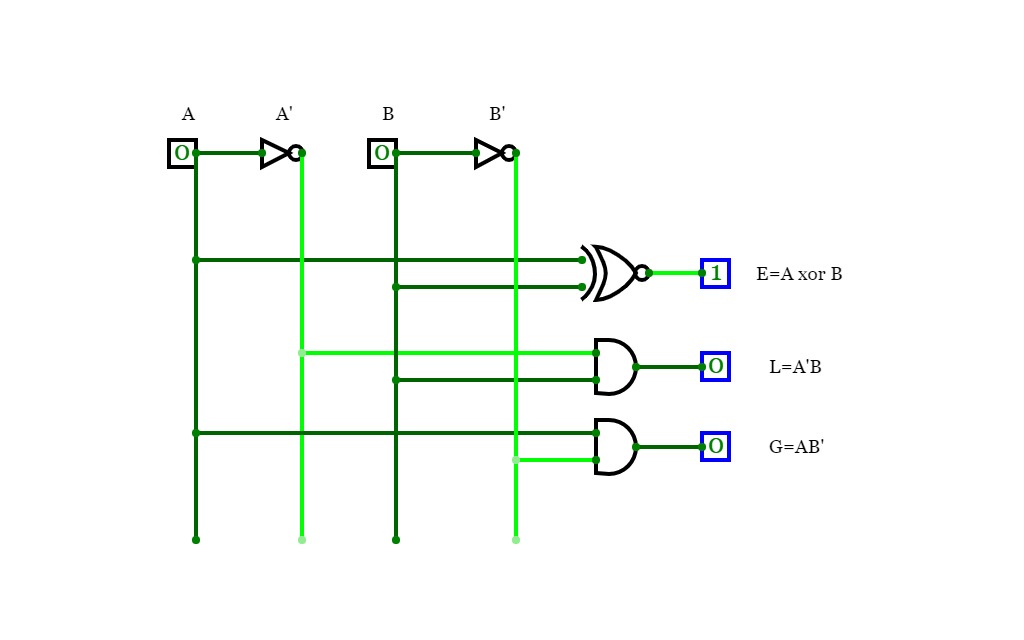

2 BIT MAGNITUDE COMPARATOR

2 BIT MAGNITUDE COMPARATOR

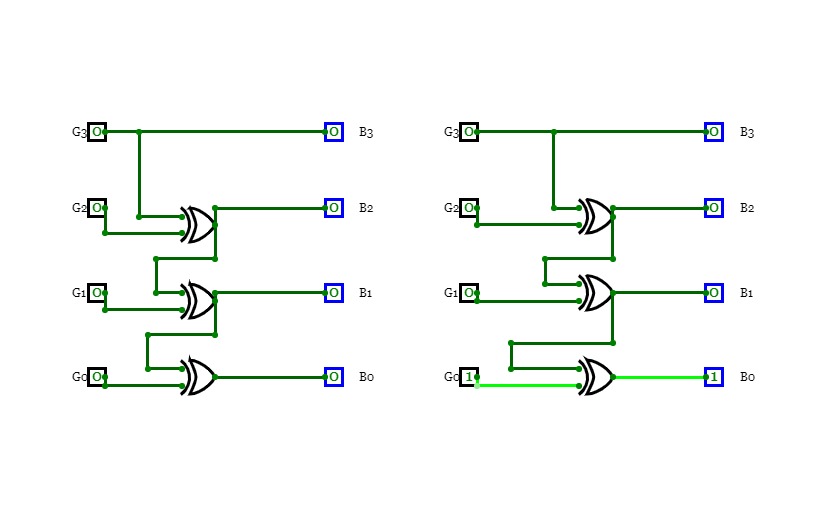

GRAY TO BINARY CODE I

GRAY TO BINARY CODE I

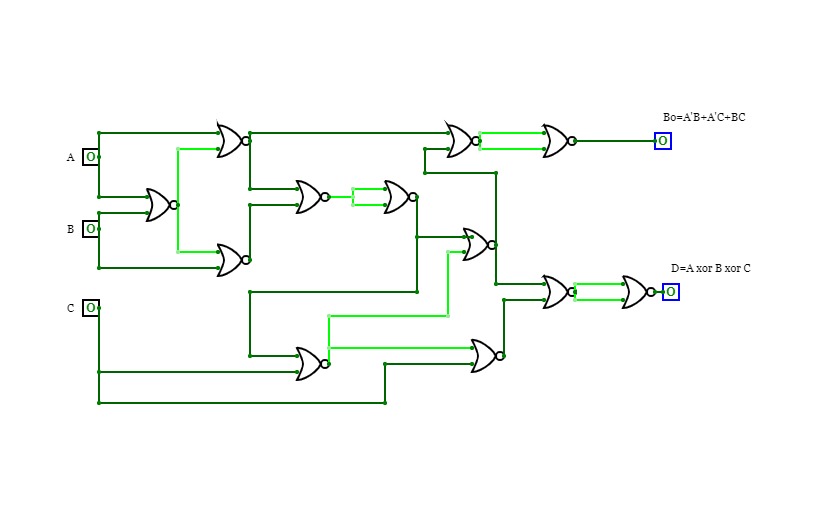

FULL SUBTRACTOR USING BASIC GATES

FULL SUBTRACTOR USING BASIC GATES

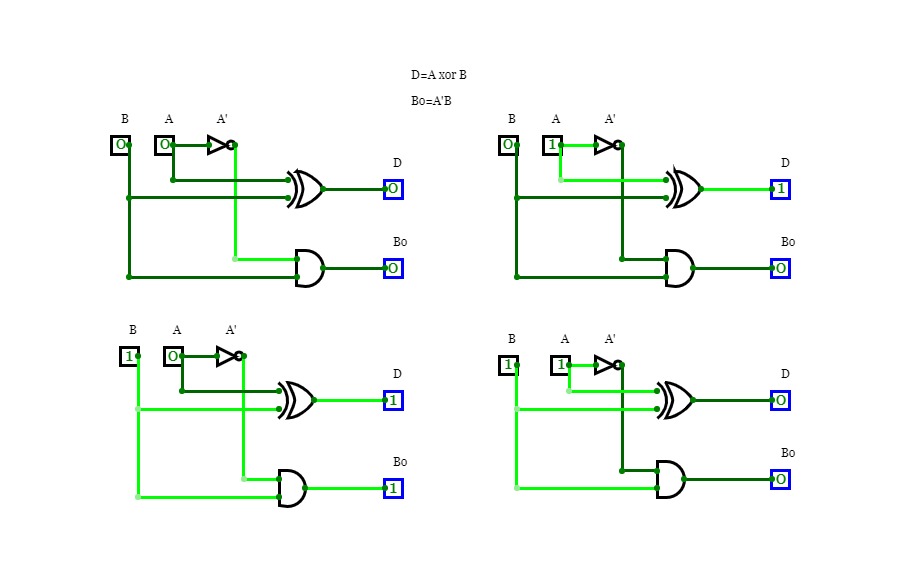

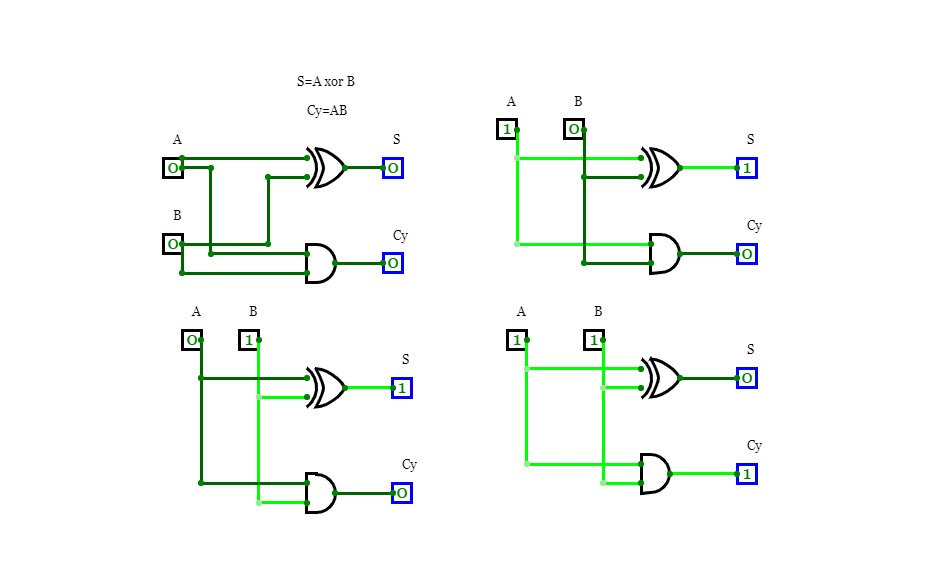

HALF ADDER USING XOR GATE

HALF ADDER USING XOR GATE

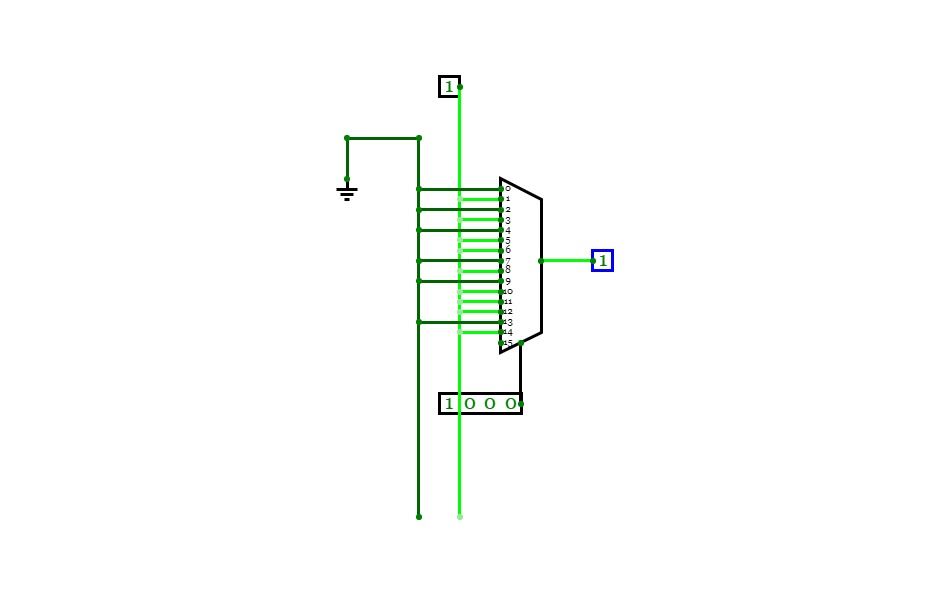

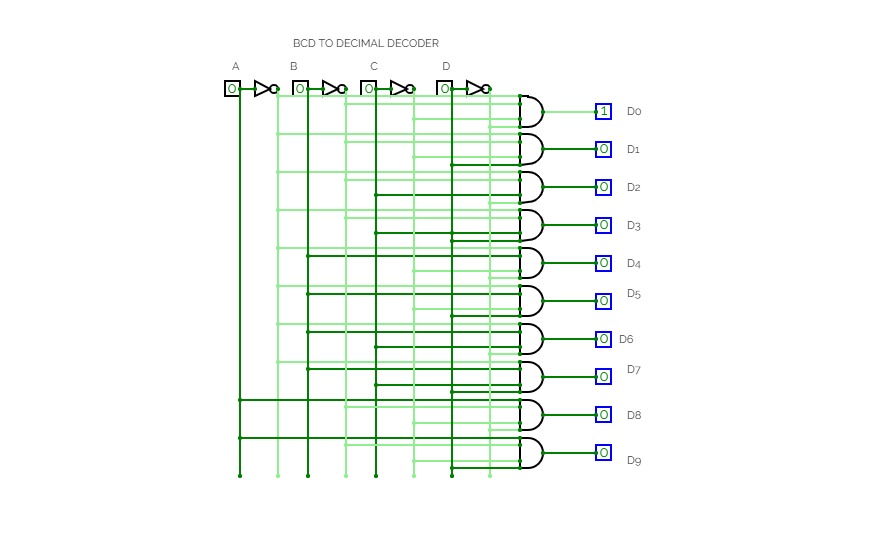

BCD TO DECIMAL DECODER

BCD TO DECIMAL DECODER

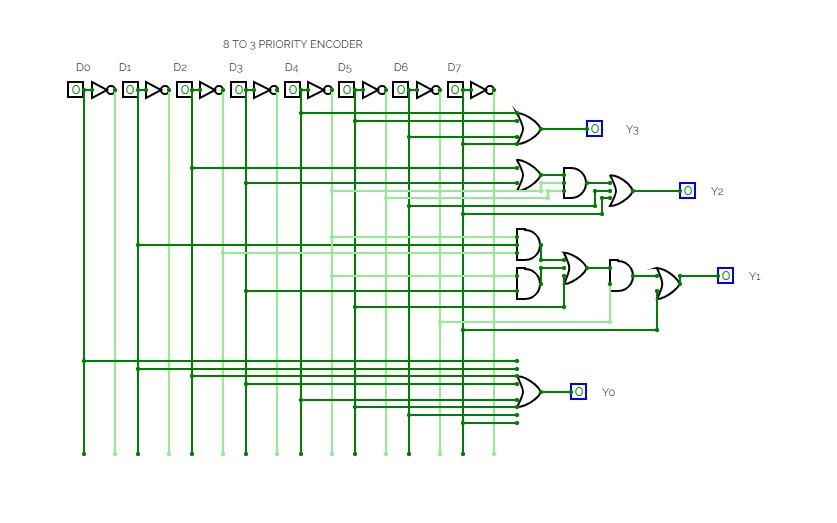

8 TO 3 PRIORITY ENCODER

8 TO 3 PRIORITY ENCODER

FULL ADDER USING NAND GATES

FULL ADDER USING NAND GATES

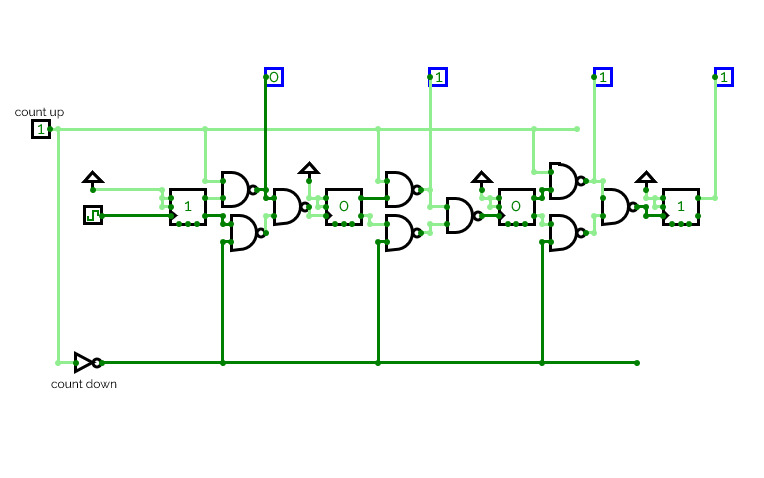

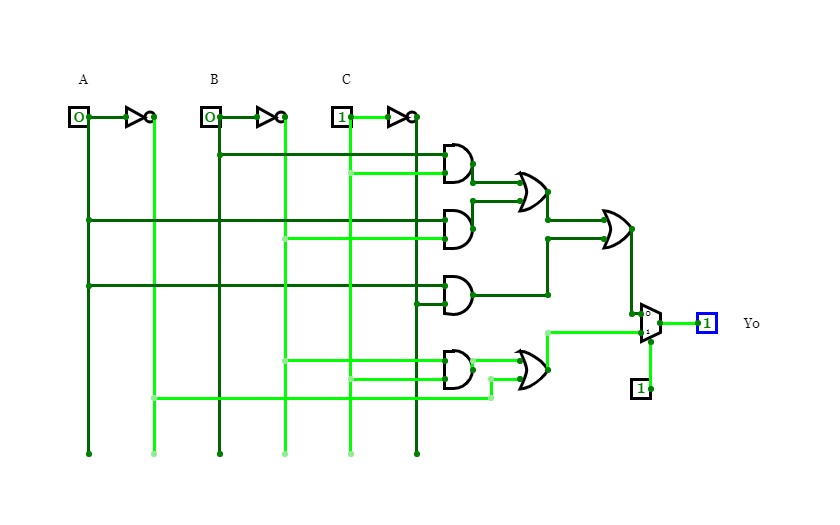

circuit that counts (0,2,4...14)when input is 1 and counts (1,3...15)when input is 0

circuit that counts (0,2,4...14)when input is 1 and counts (1,3...15)when input is 0

3 BIT PARITY GENERATOR

3 BIT PARITY GENERATOR

FULL SUBTRACTOR USING NAND GATES

FULL SUBTRACTOR USING NAND GATES

32:1 MUX USING 4:1 MUX

32:1 MUX USING 4:1 MUX

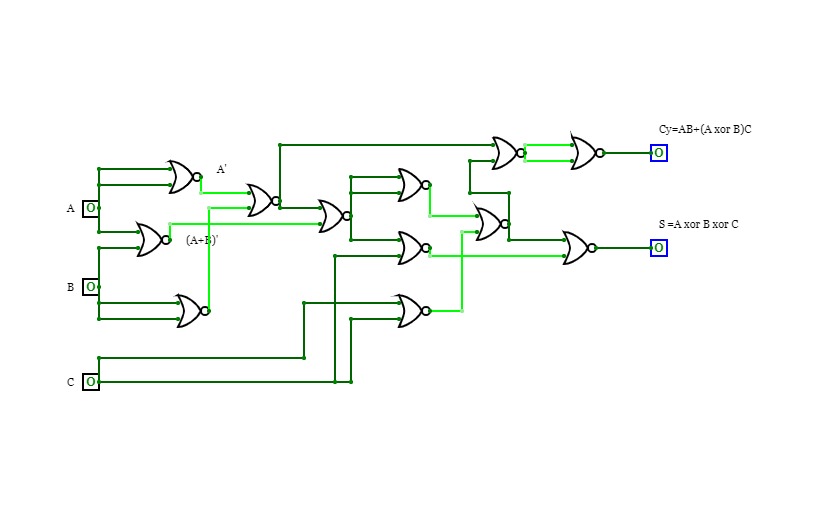

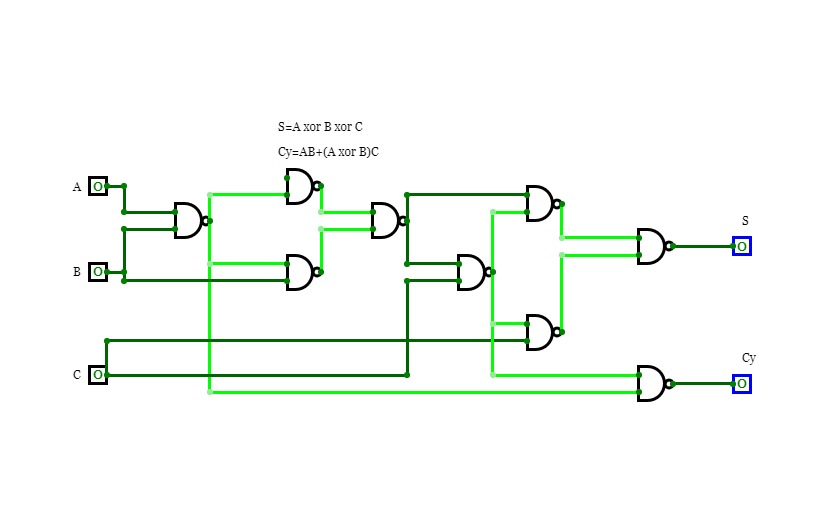

FULL ADDER USING XOR GATES

FULL ADDER USING XOR GATES

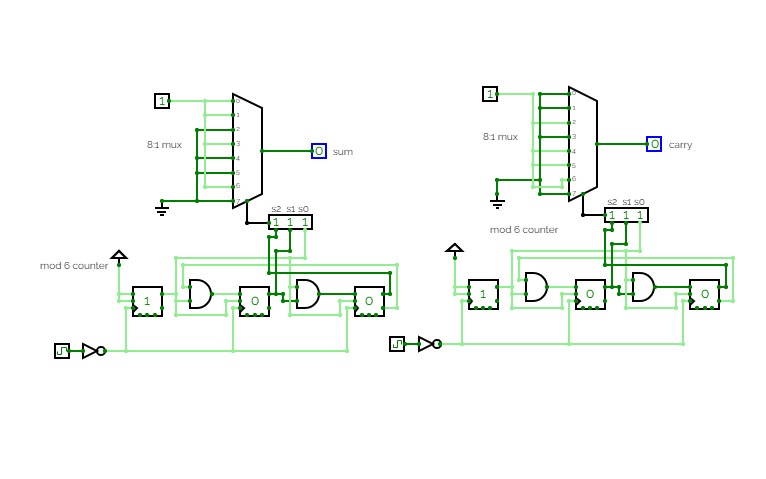

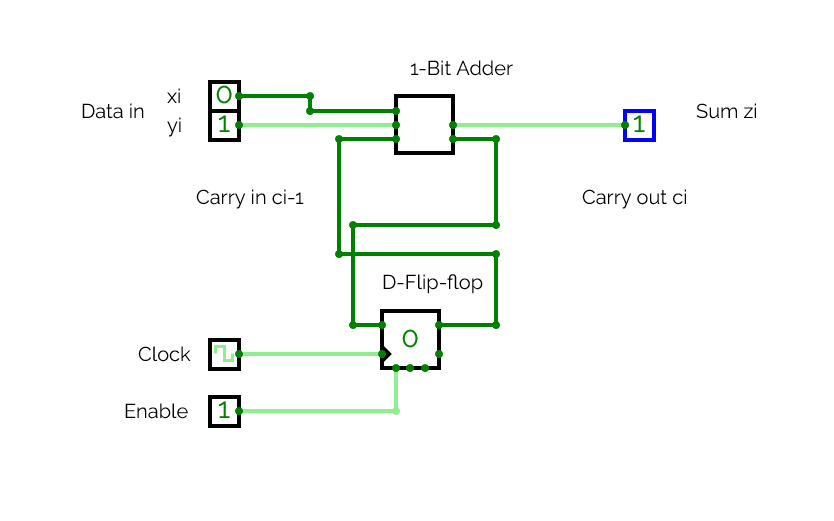

implementation of full adder with mux and counter

implementation of full adder with mux and counter

FULL SUBTRACTOR USING NOR GATES

FULL SUBTRACTOR USING NOR GATES

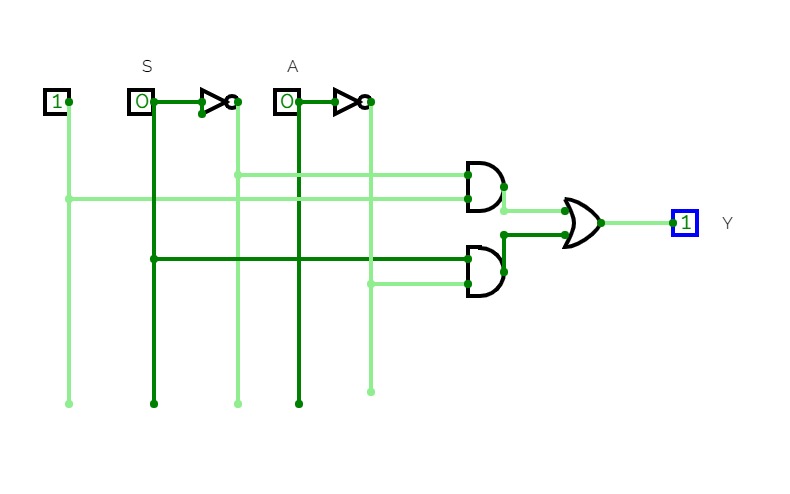

AND USING 2 TO 1 MUX

AND USING 2 TO 1 MUX

implementation of full adder using counter

implementation of full adder using counter

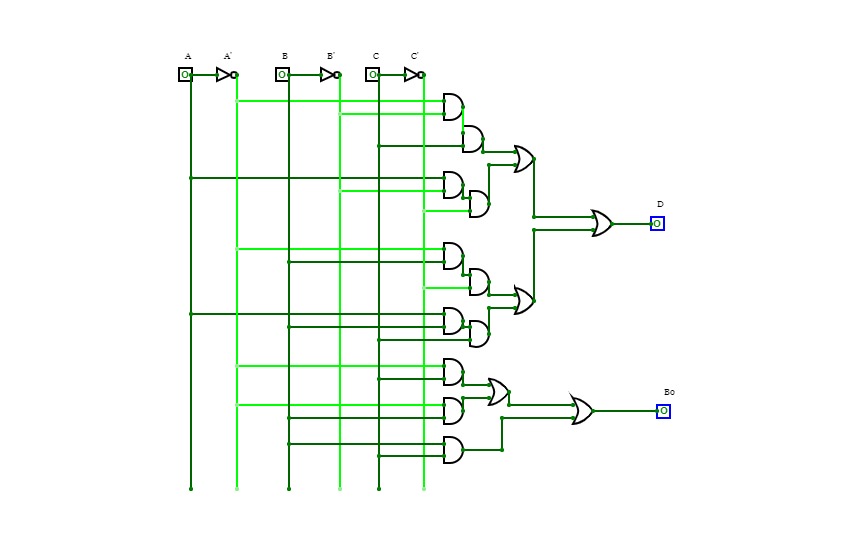

I BIT MAGNITUDE COMPARATOR

I BIT MAGNITUDE COMPARATOR

2:1 IMPLEMENTATION

2:1 IMPLEMENTATION

EXP 8.1

EXP 8.1