Bhavadharani.P

Member since: 4 years

Educational Institution: Not Entered

Country: Not Entered

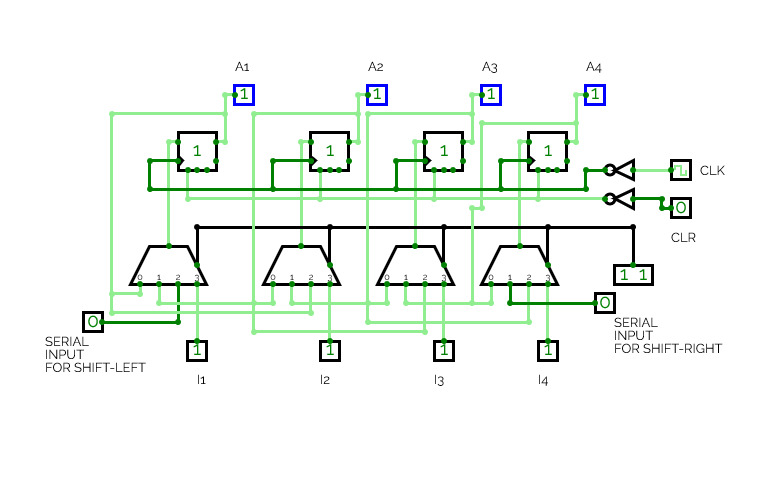

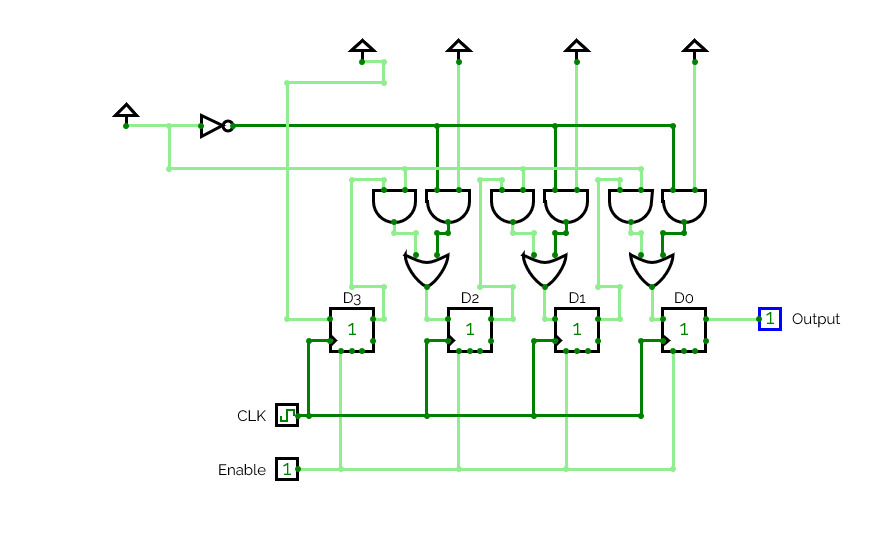

4 BIT UNIVERSAL SHIFT REGISTER

4 BIT UNIVERSAL SHIFT REGISTER

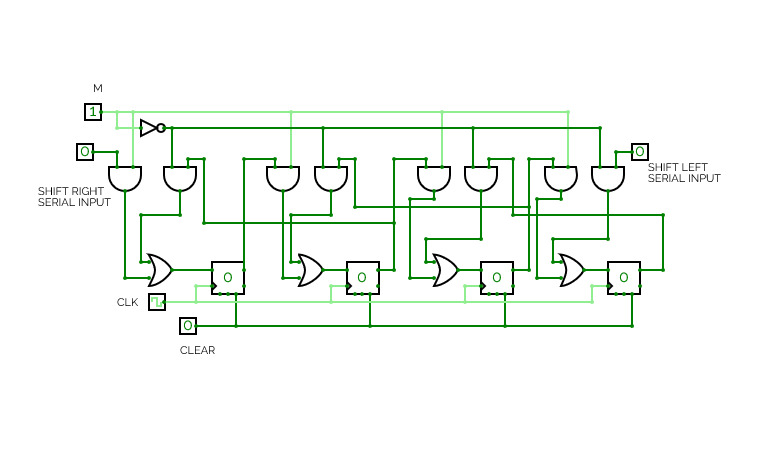

4 bit bidirectional shift register

4 bit bidirectional shift register

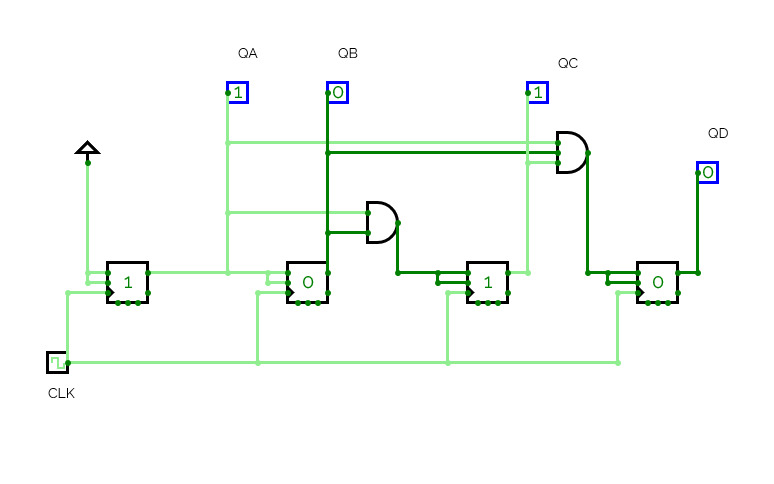

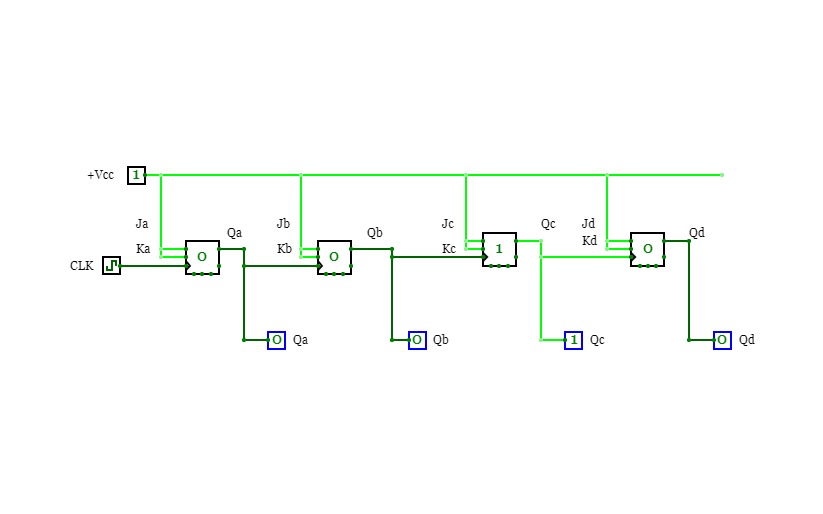

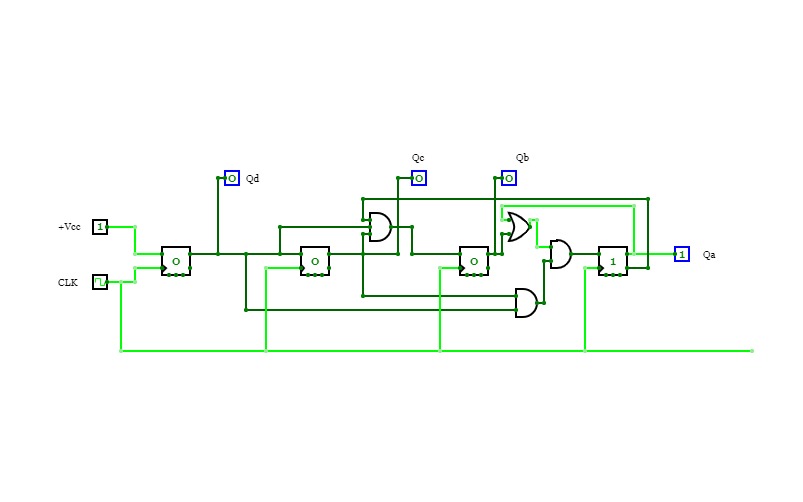

4 bit synchronous counter

4 bit synchronous counter

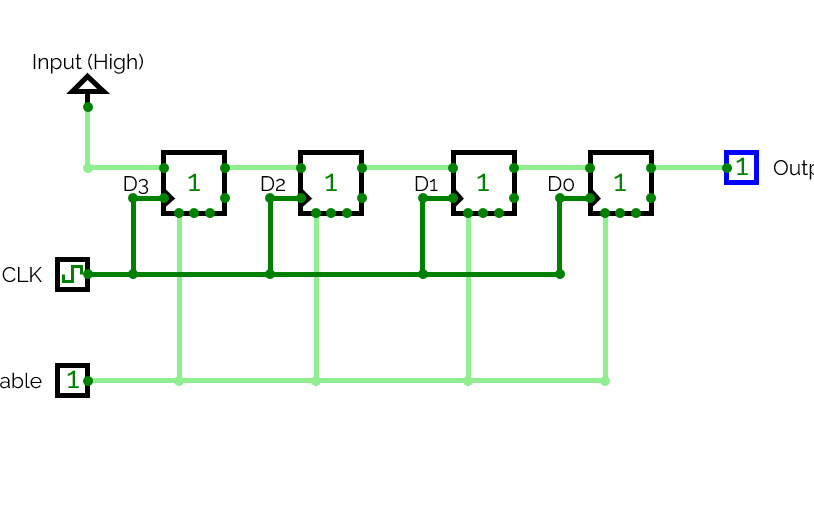

PISO

PISO

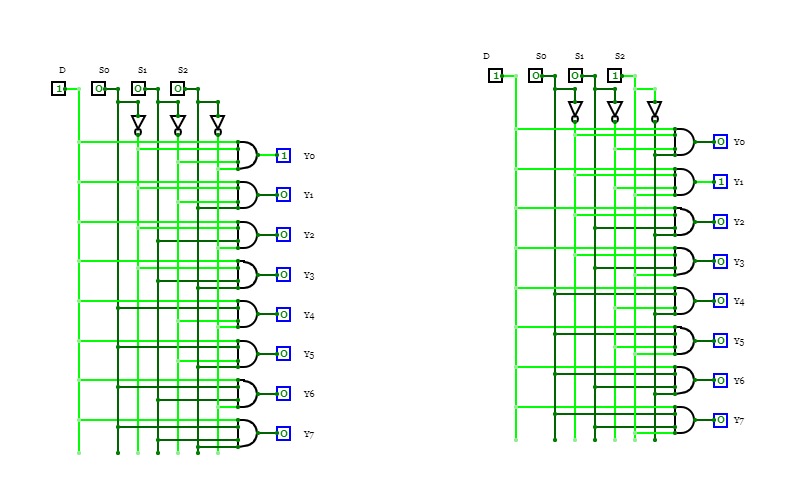

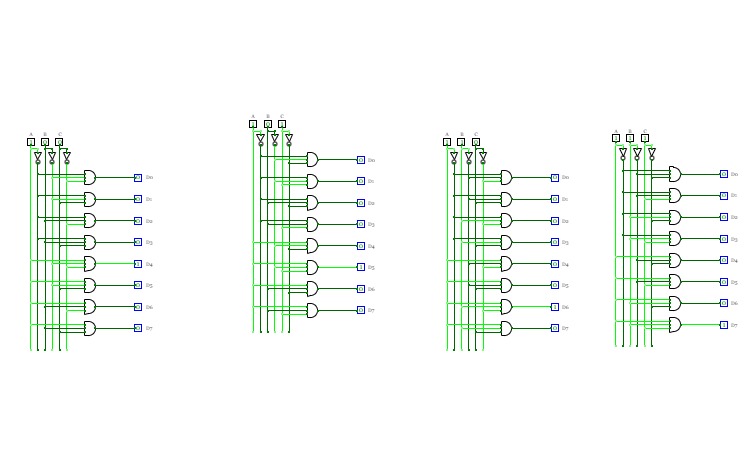

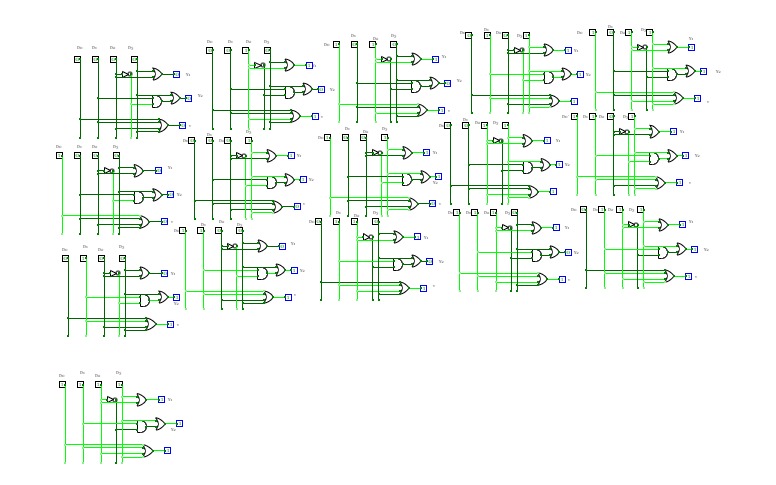

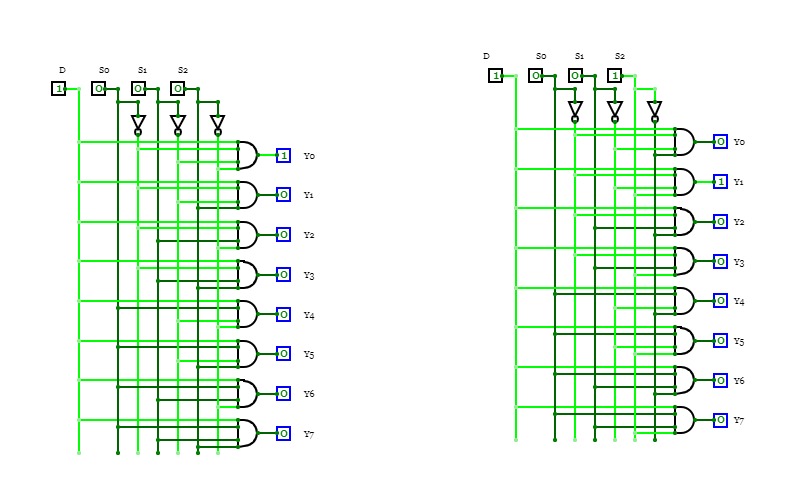

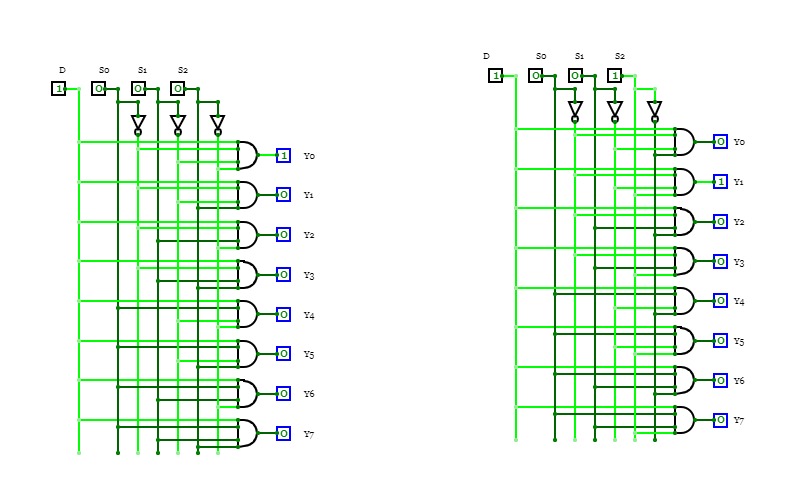

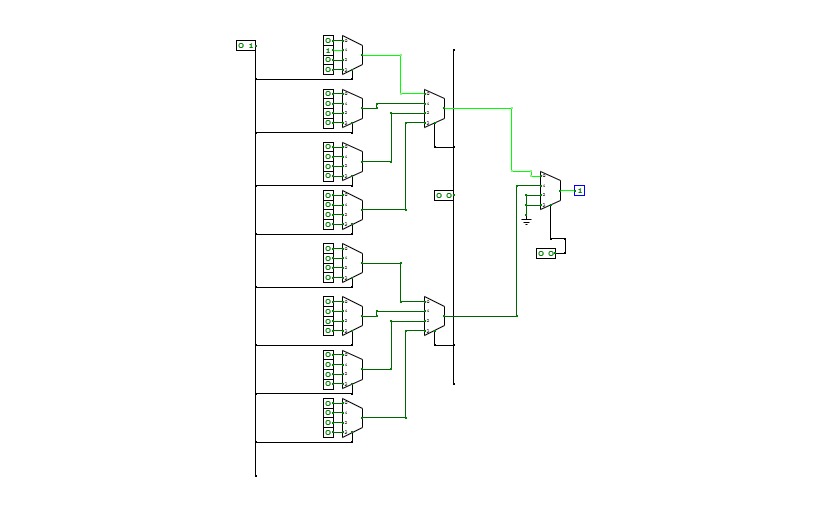

1 to 8 DEMUX

1 to 8 DEMUX

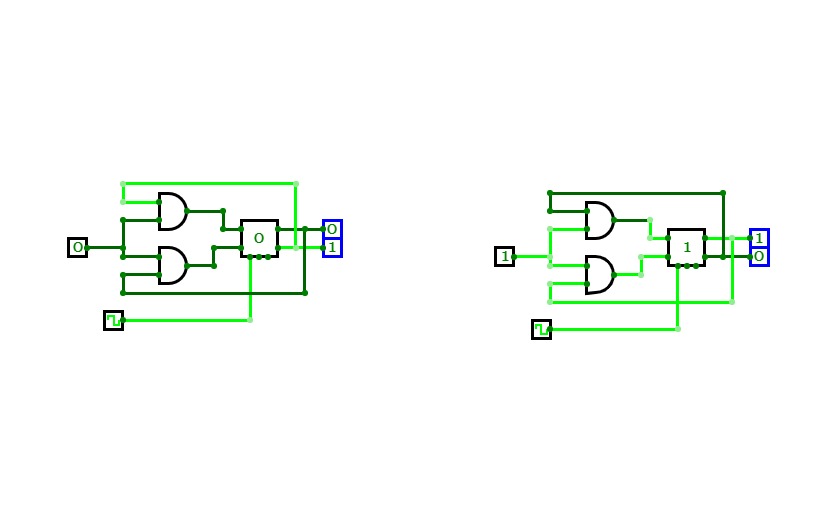

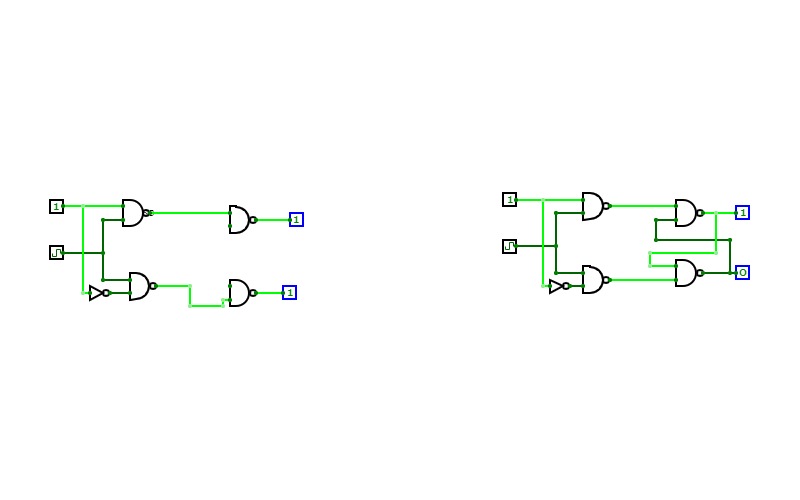

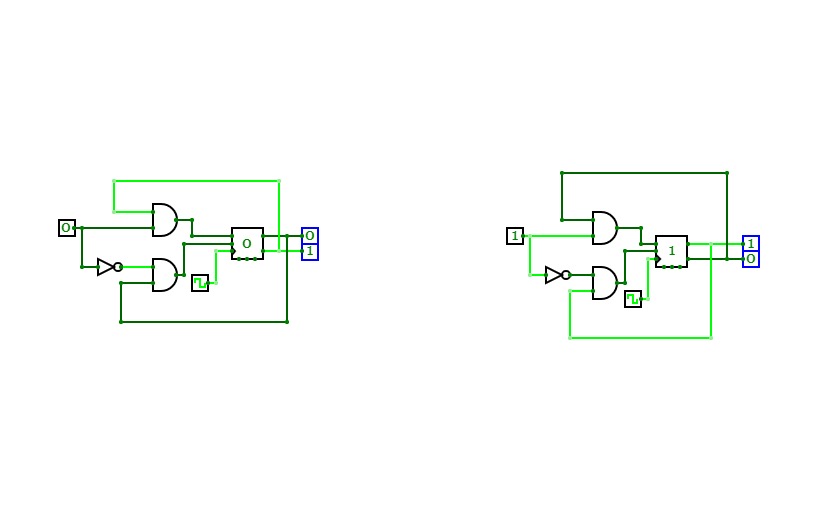

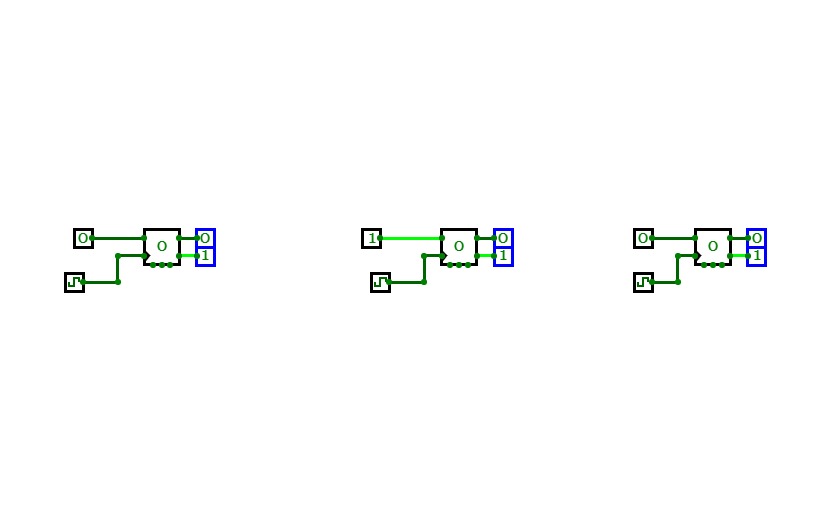

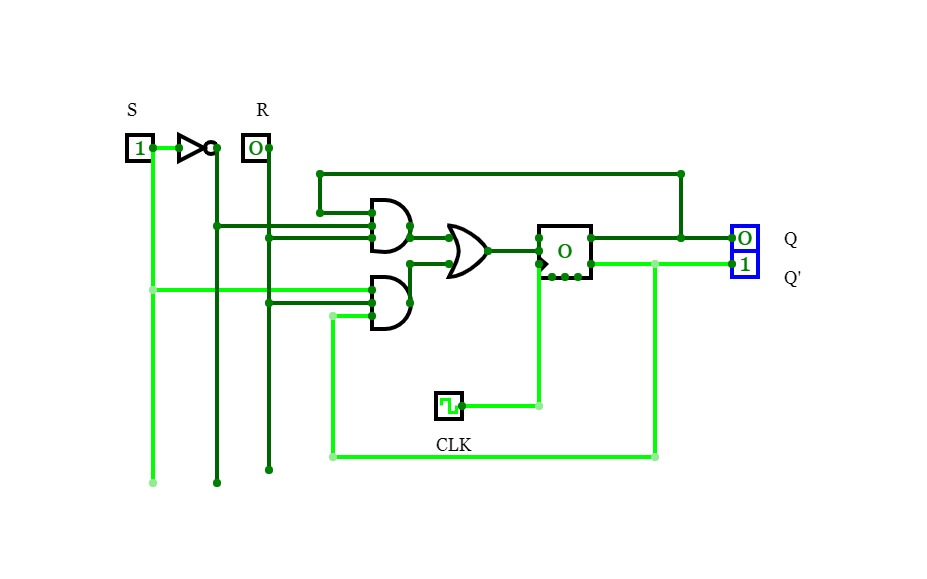

TFF USING SRFF

TFF USING SRFF

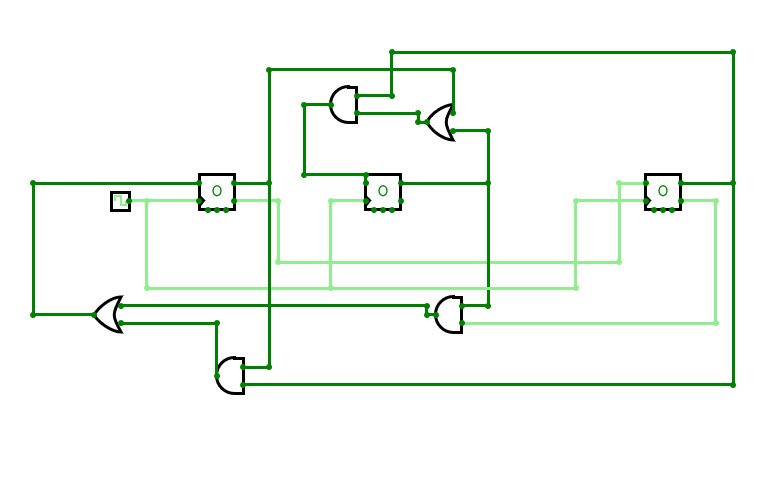

GRAY TO BINARY CODE

GRAY TO BINARY CODE

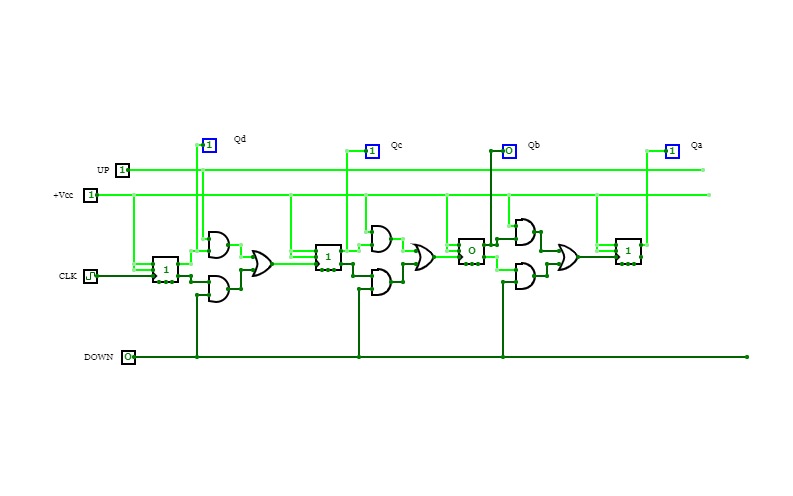

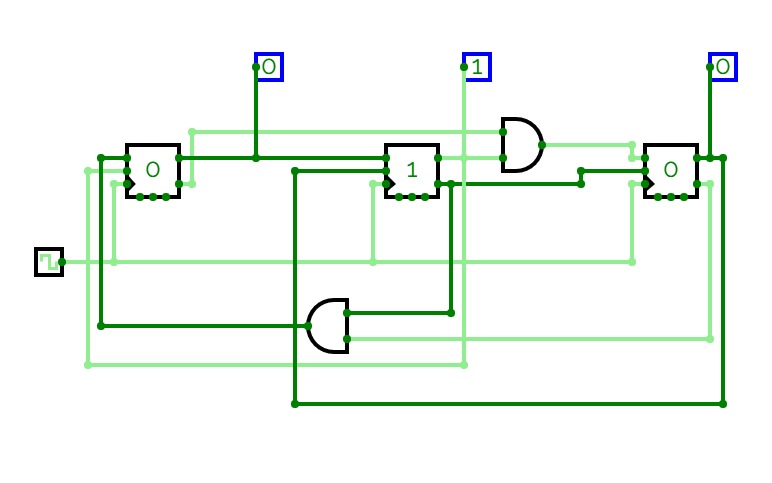

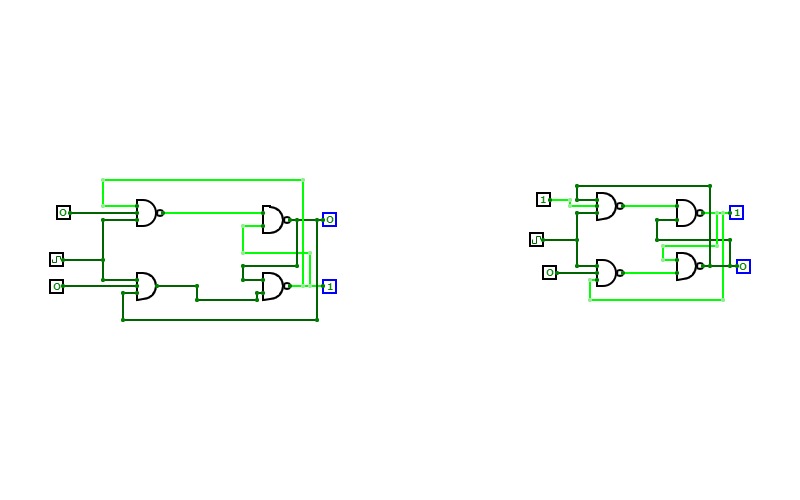

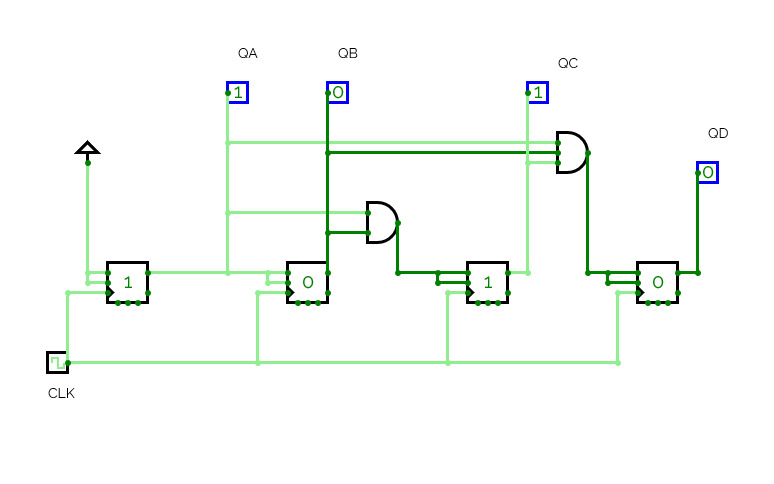

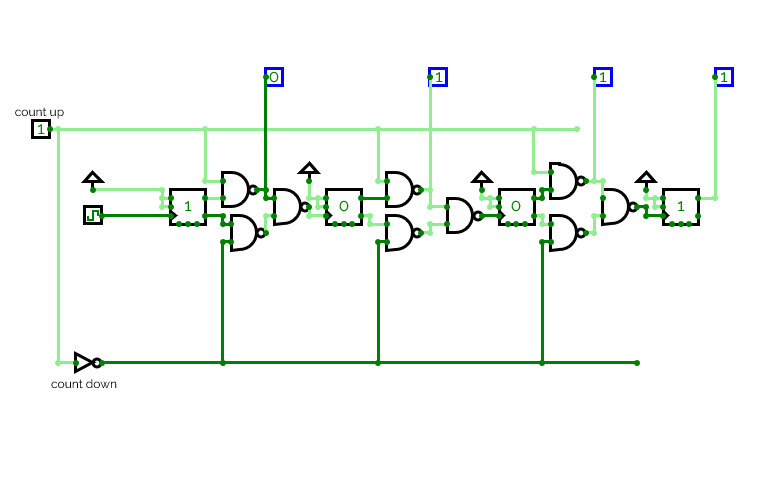

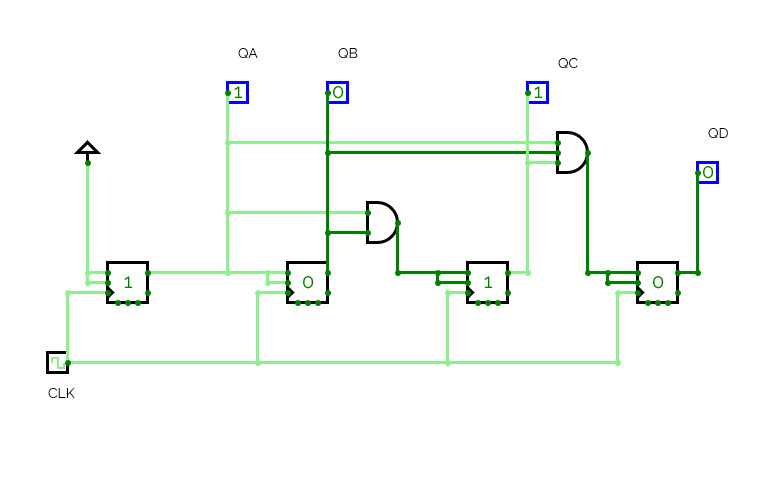

4 BIT RIPPLE UP\DOWN COUNTER

4 BIT RIPPLE UP\DOWN COUNTER

TFF USING JKFF

TFF USING JKFF

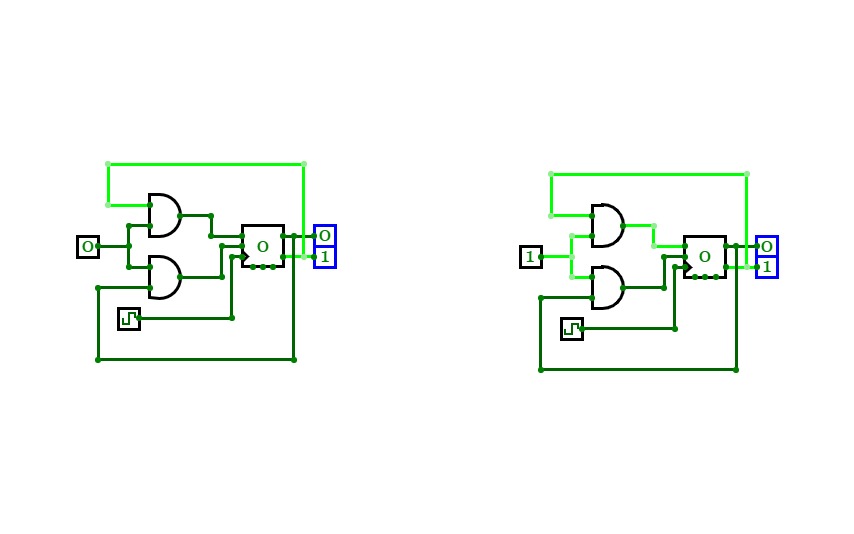

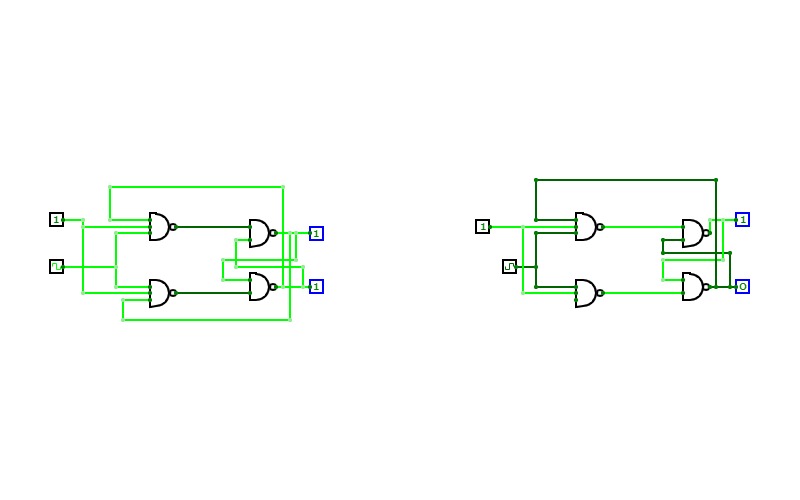

JKFF Using TFF

JKFF Using TFF

JKFF USING DFF

JKFF USING DFF

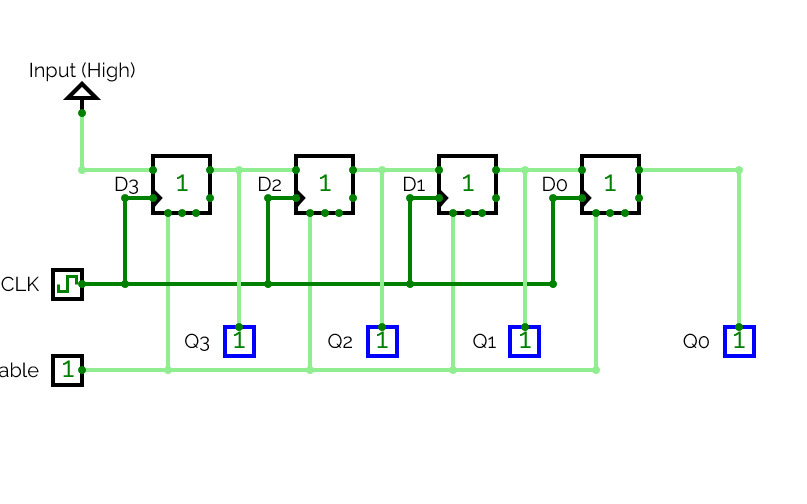

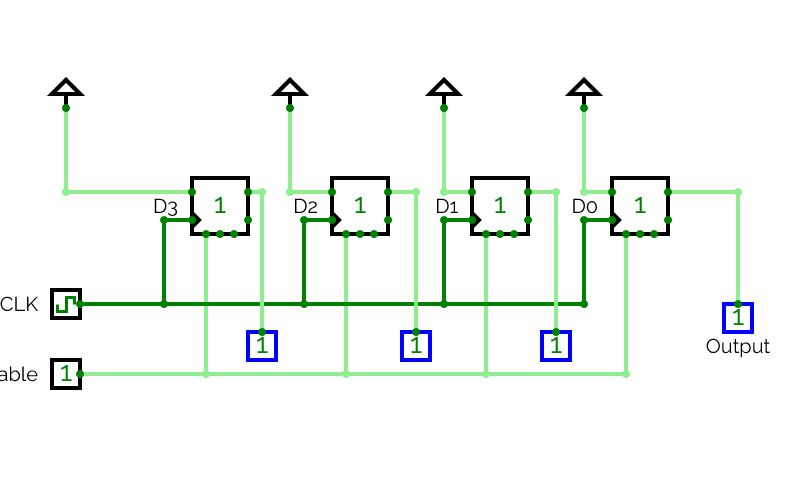

SIPO

SIPO

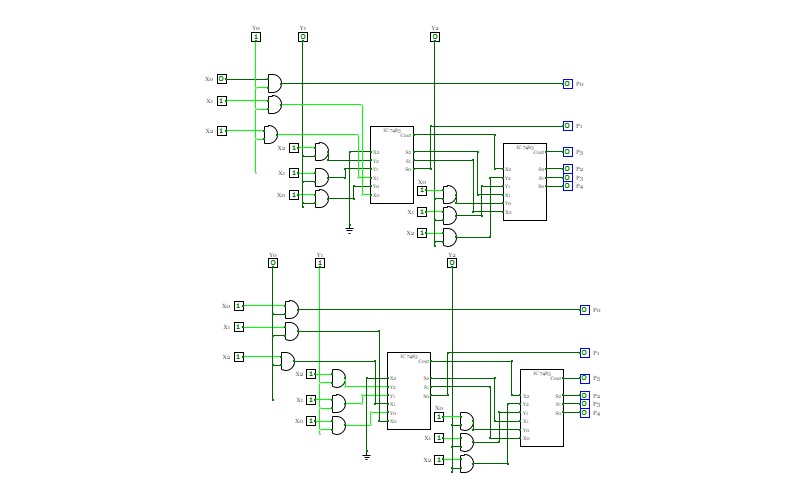

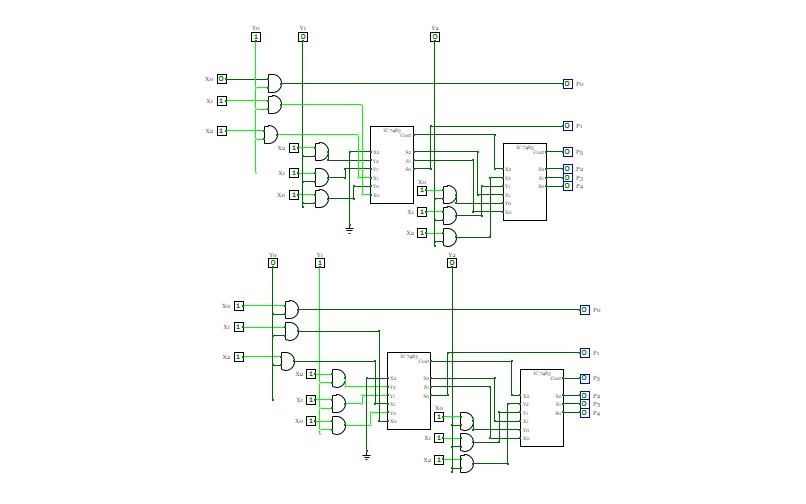

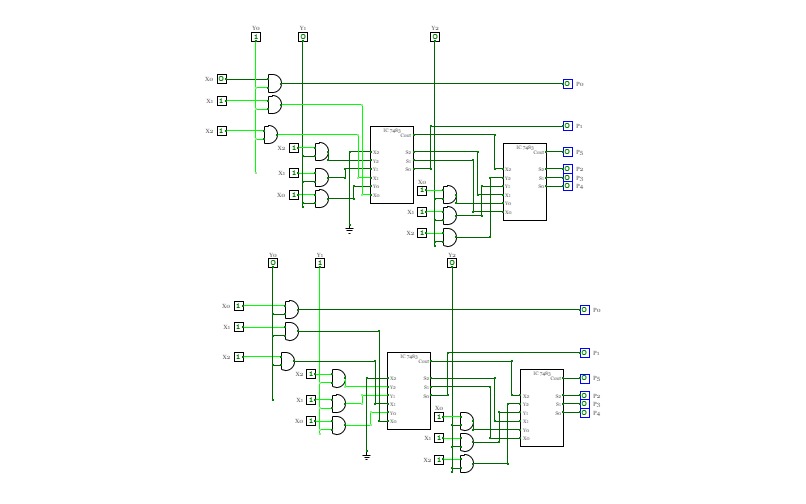

3 BIT PARALLEL MULTIPLIER

3 BIT PARALLEL MULTIPLIER

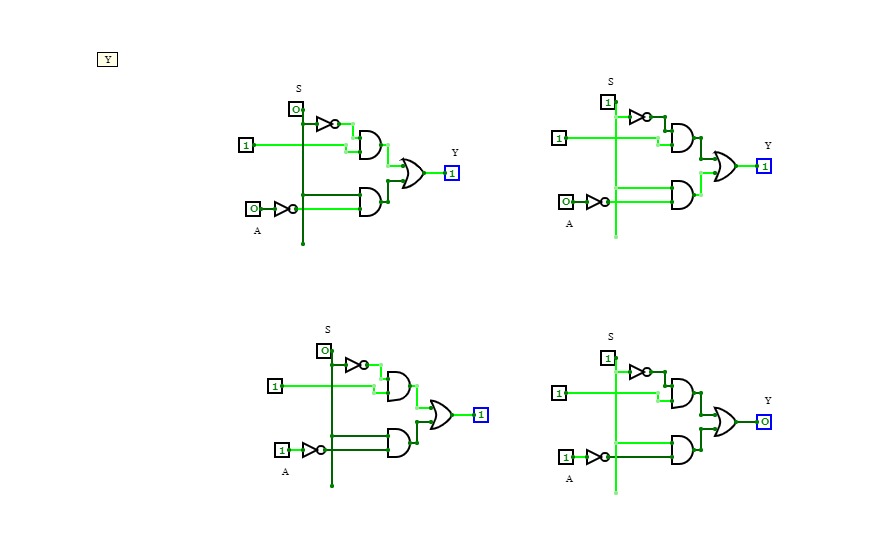

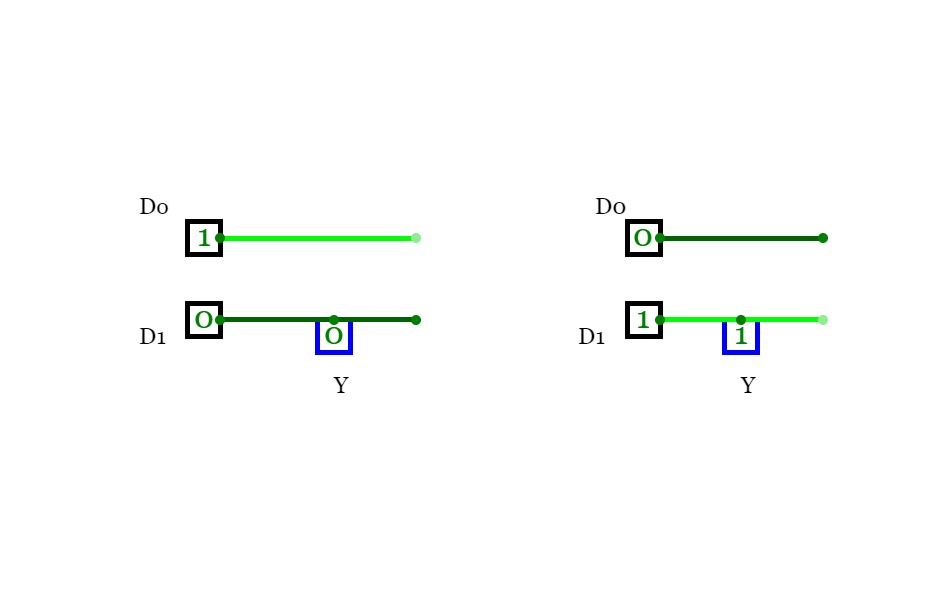

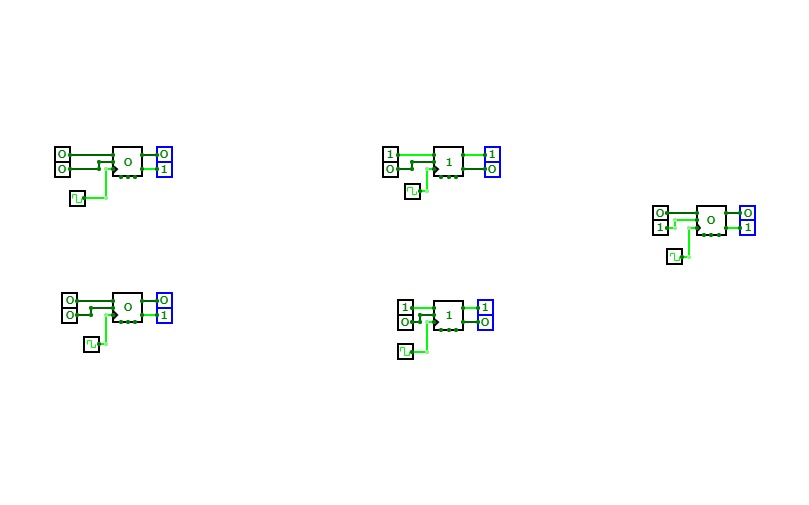

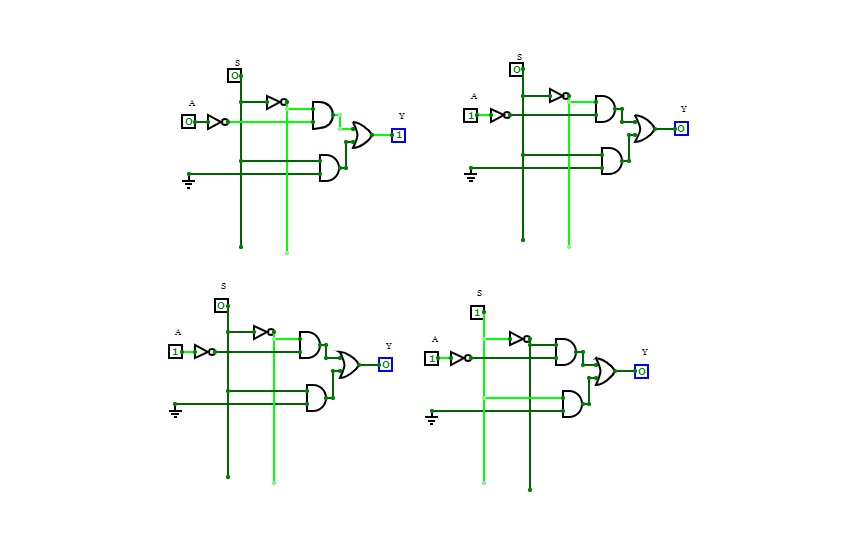

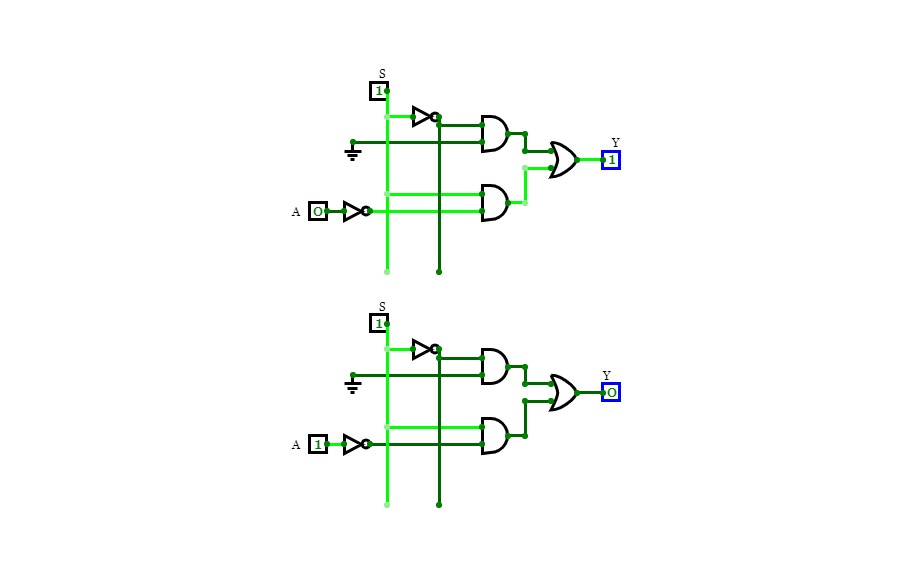

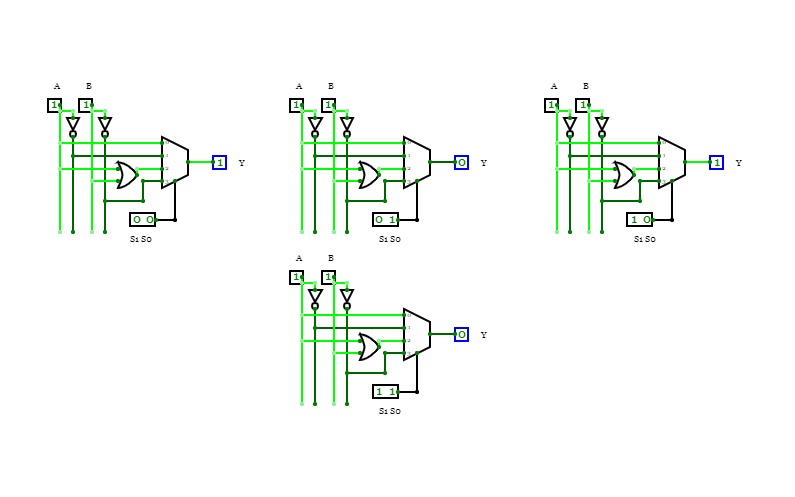

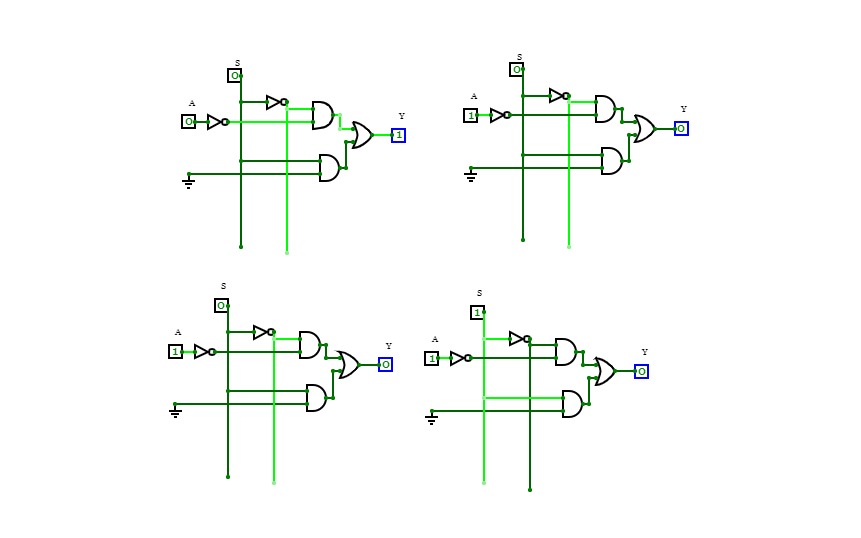

NAND USING 2 TO 1 MUX

NAND USING 2 TO 1 MUX

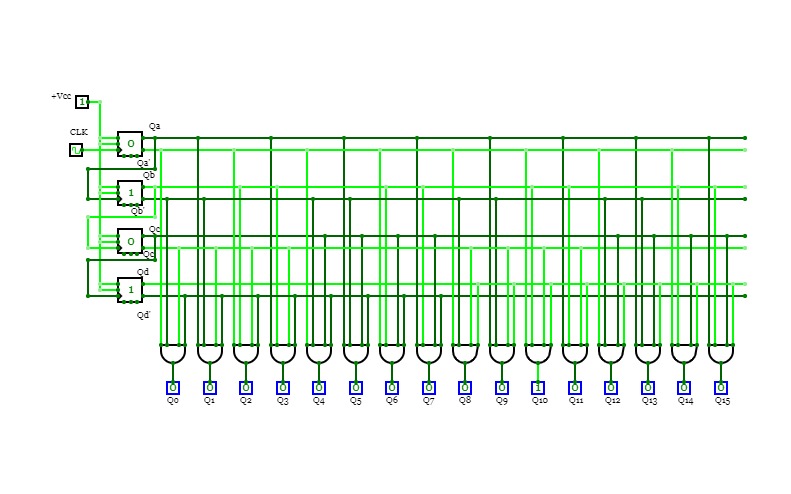

4-BIT RIPPLE COUNTER WITH DECODED OUTPUTS

4-BIT RIPPLE COUNTER WITH DECODED OUTPUTS

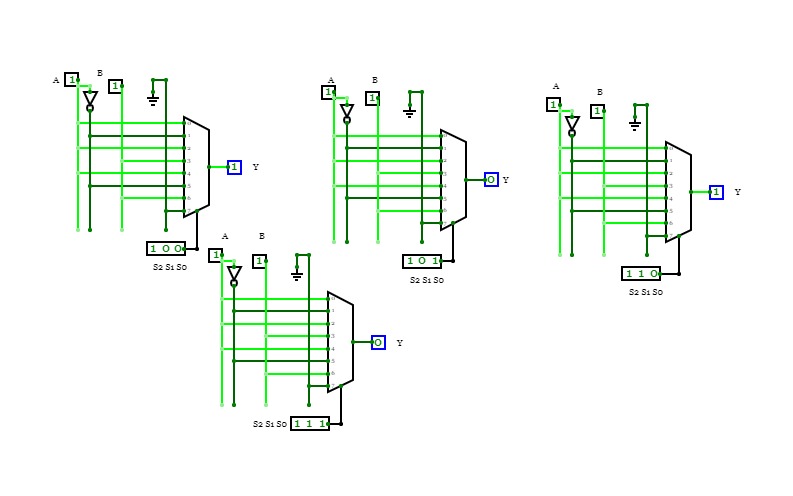

3 to 8 DECODER

3 to 8 DECODER

TFF USING DFF

TFF USING DFF

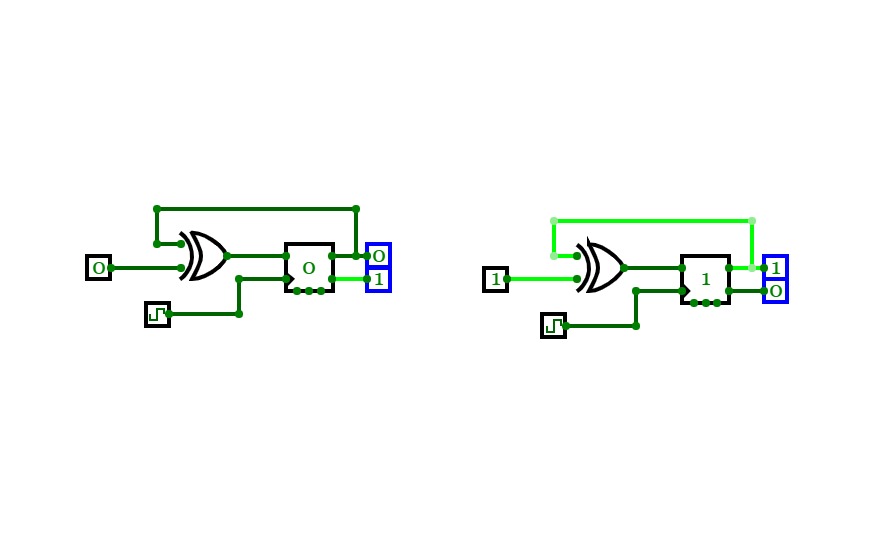

D FLIPFLOP

D FLIPFLOP

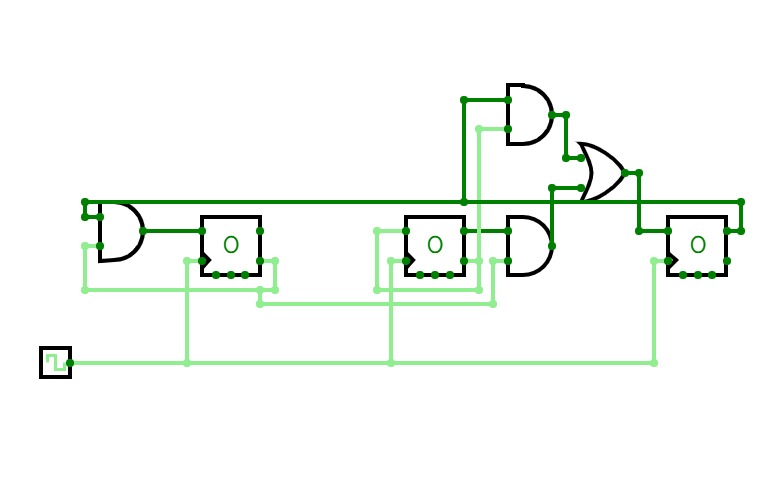

SEQUENCE GENERATOR USING COUNTER

SEQUENCE GENERATOR USING COUNTER

counter that counts 0,2,4,7,0

counter that counts 0,2,4,7,0

mod-6 unit distance counter

mod-6 unit distance counter

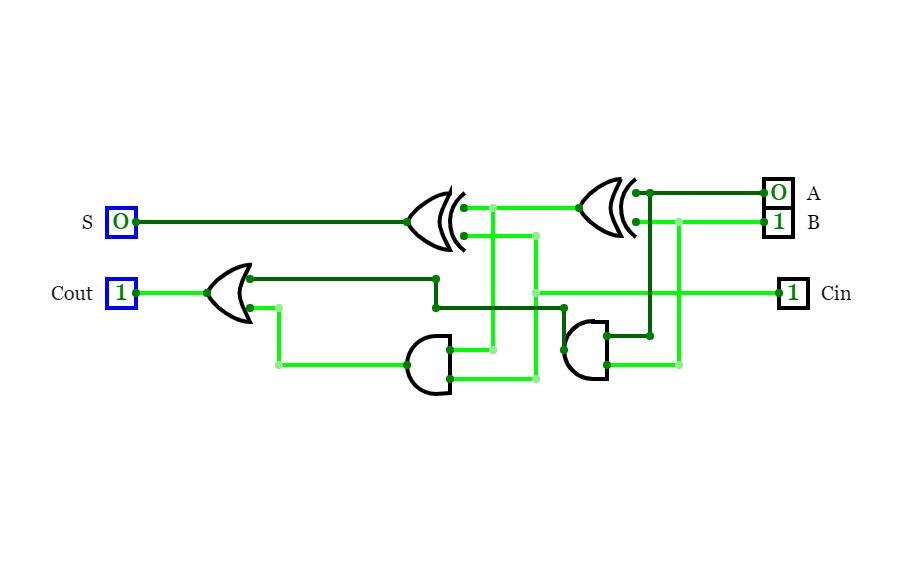

implementation of full adder using counter

implementation of full adder using counter

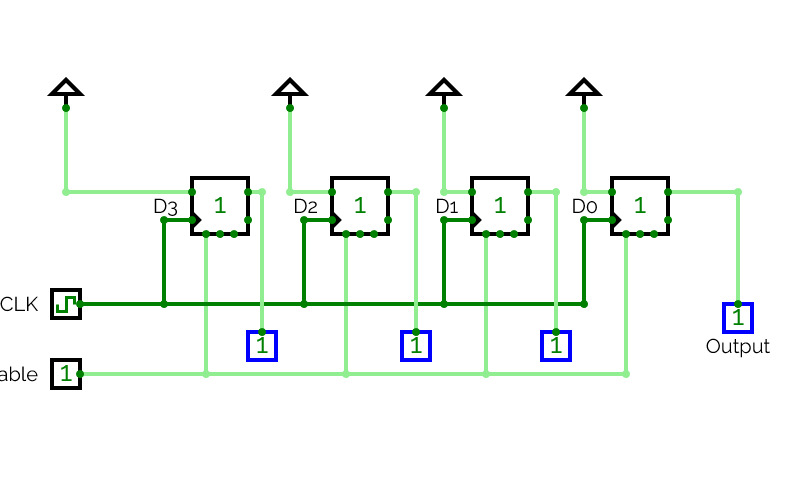

PIPO

PIPO

PIPO

PIPO

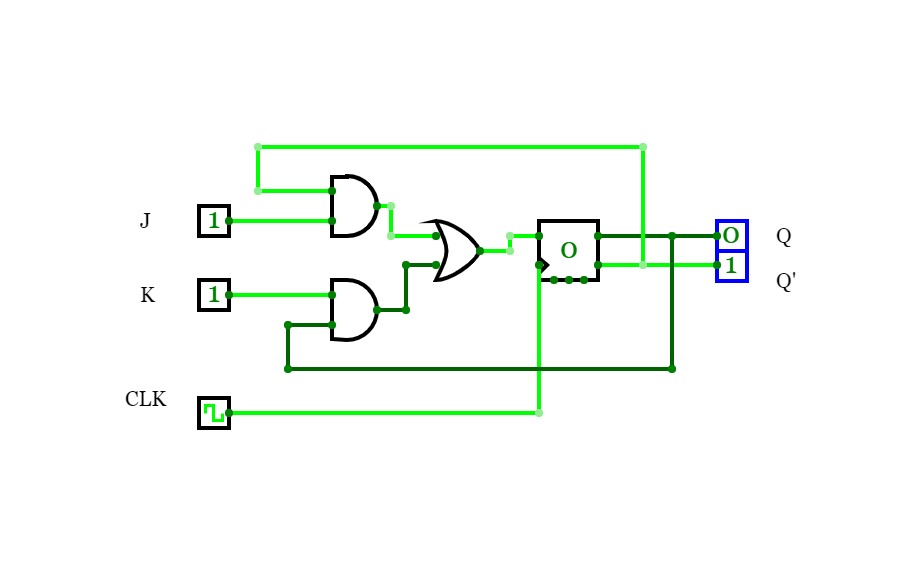

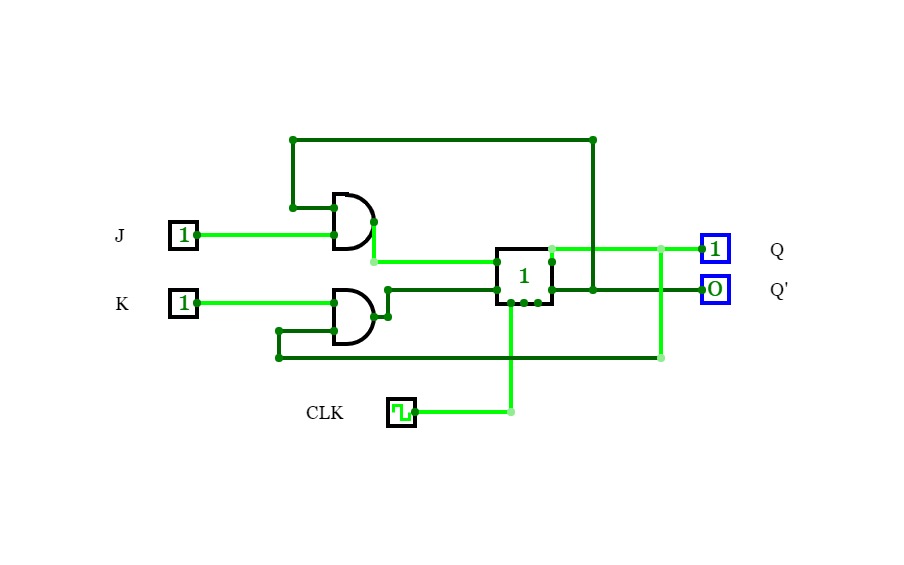

JK FLIPFLOP

JK FLIPFLOP

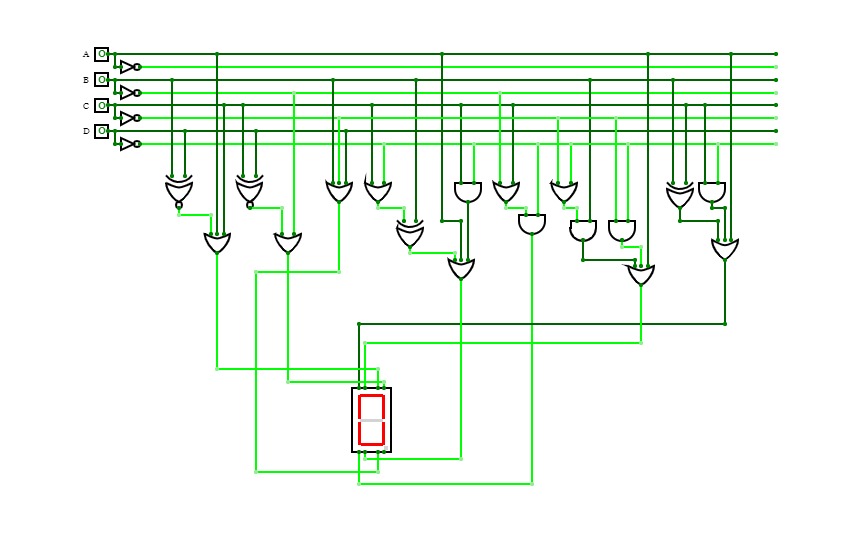

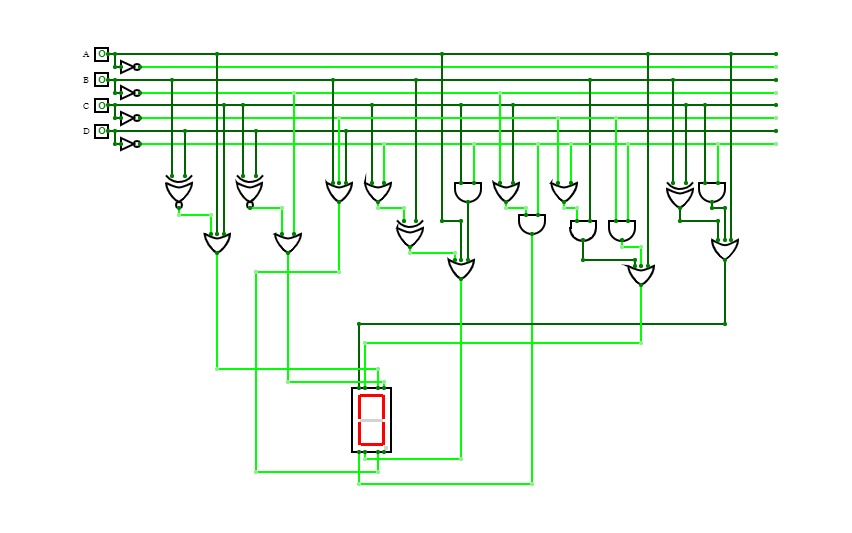

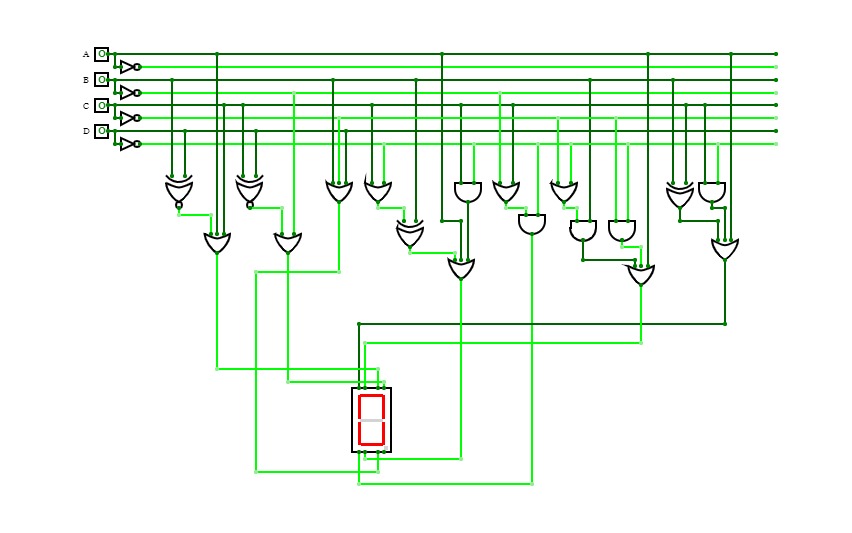

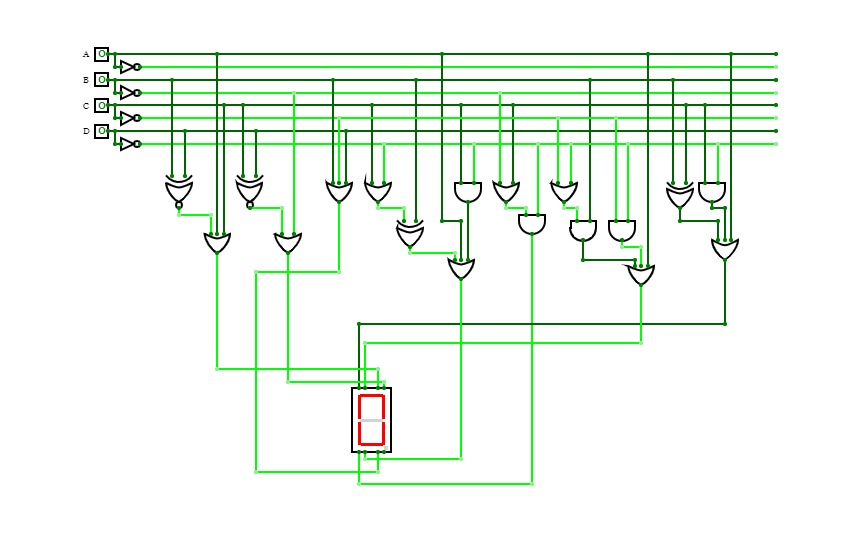

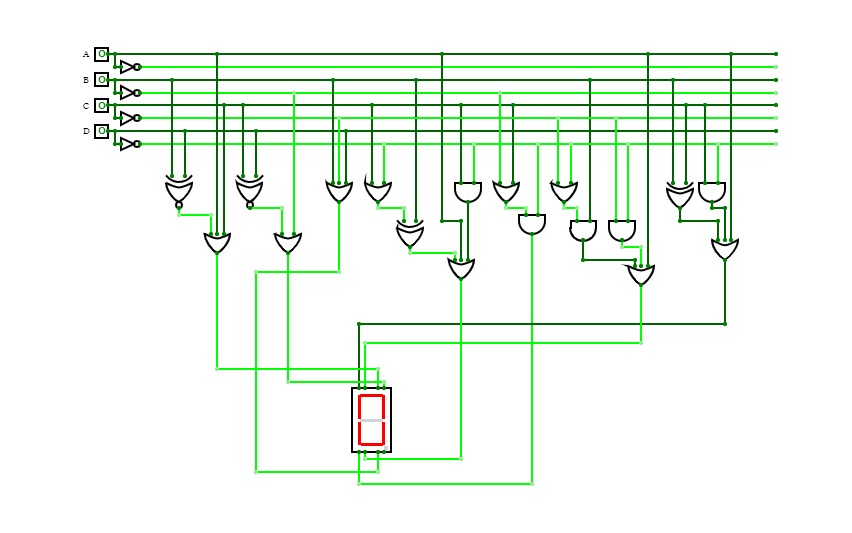

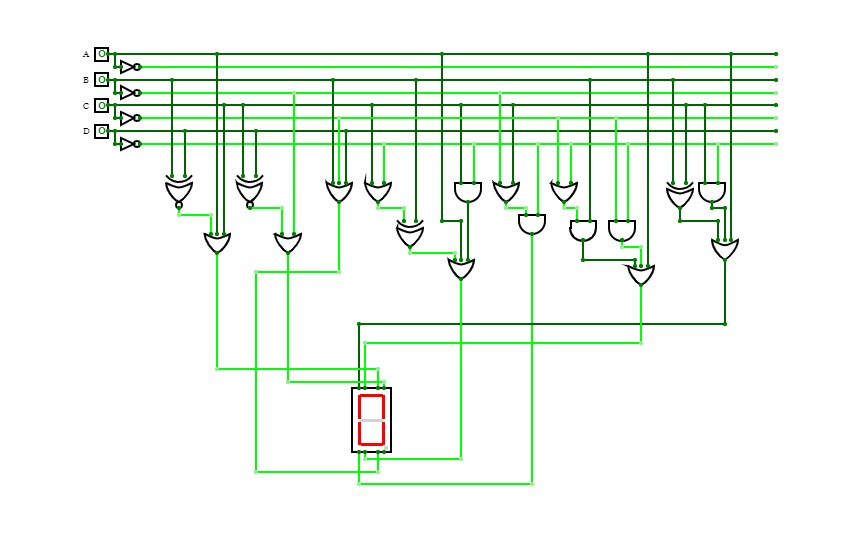

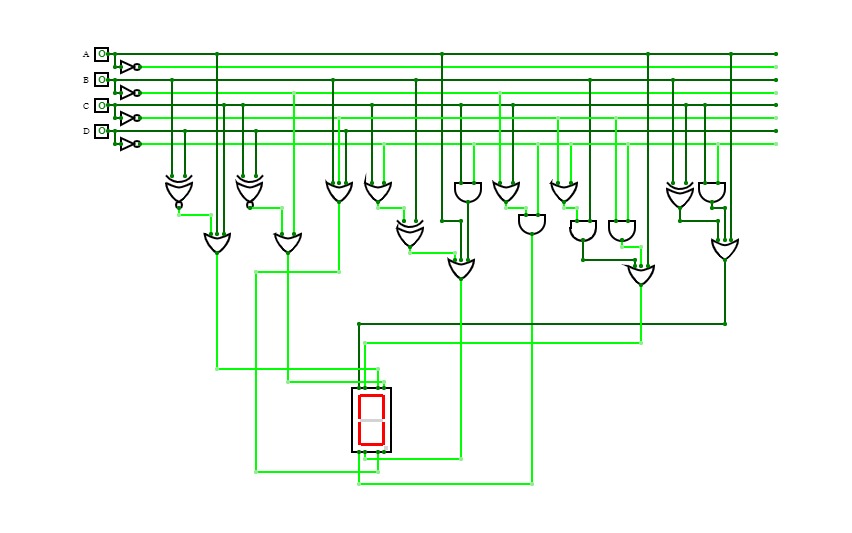

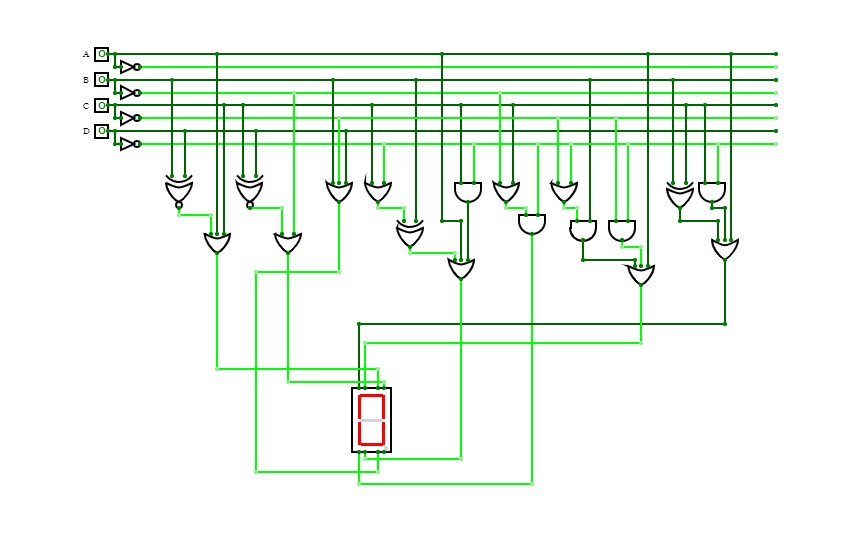

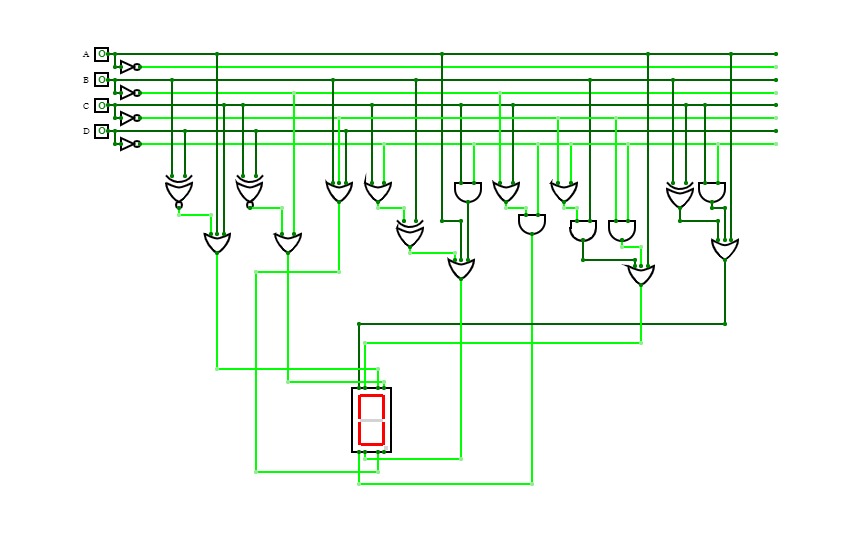

BCD to 7 SEGMENT DECODER

BCD to 7 SEGMENT DECODER

BCD to 7 SEGMENT DECODER

BCD to 7 SEGMENT DECODER

FULL SUBTRACTOR USING NOR GATES

FULL SUBTRACTOR USING NOR GATES

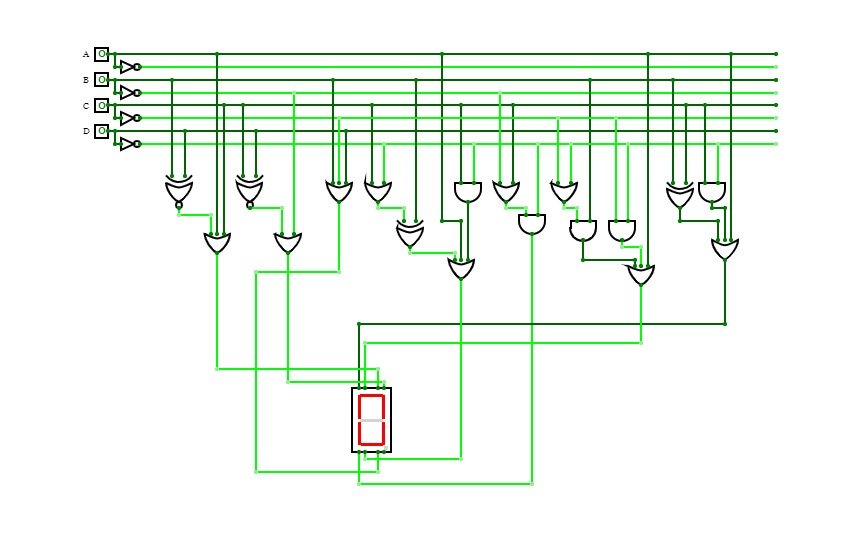

BCD to 7 SEGMENT DECODER

BCD to 7 SEGMENT DECODER

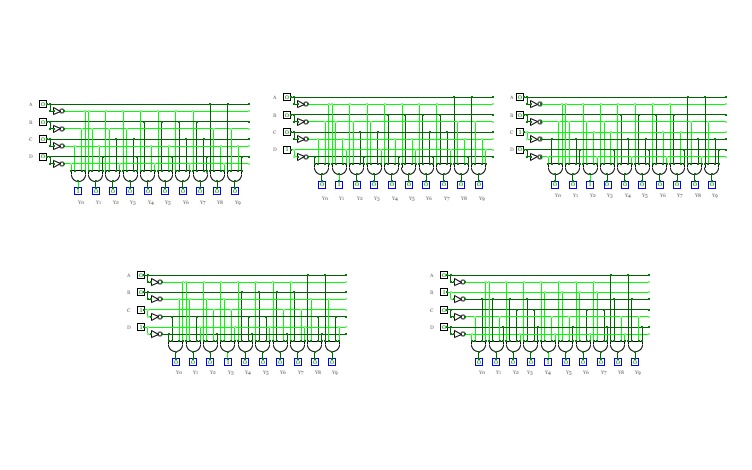

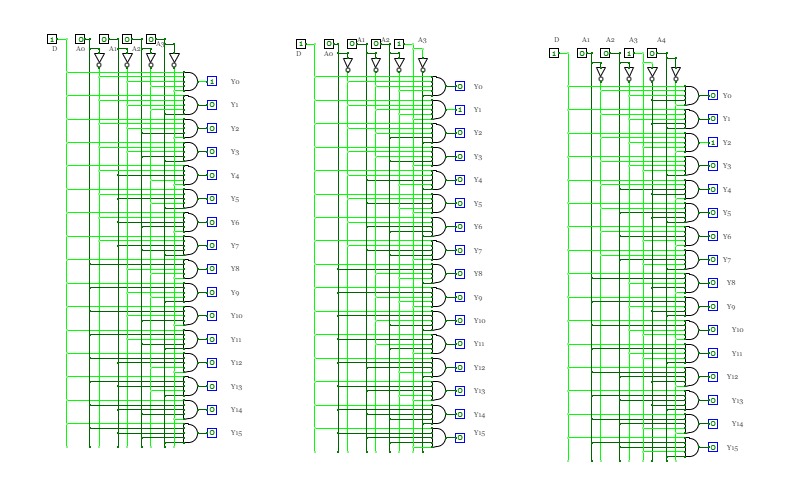

4 to 16 decoder

4 to 16 decoder

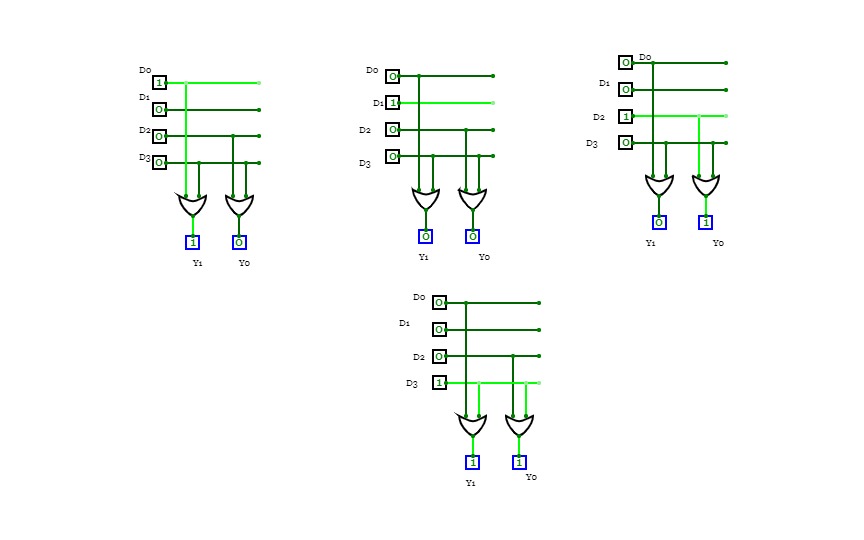

2 x 1 encoder

2 x 1 encoder

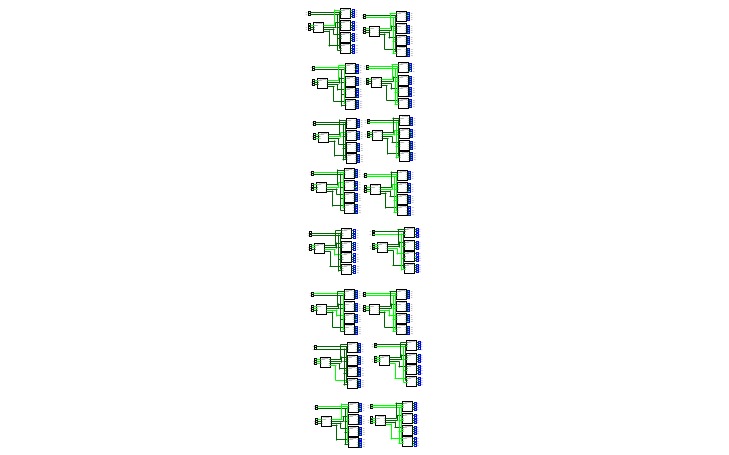

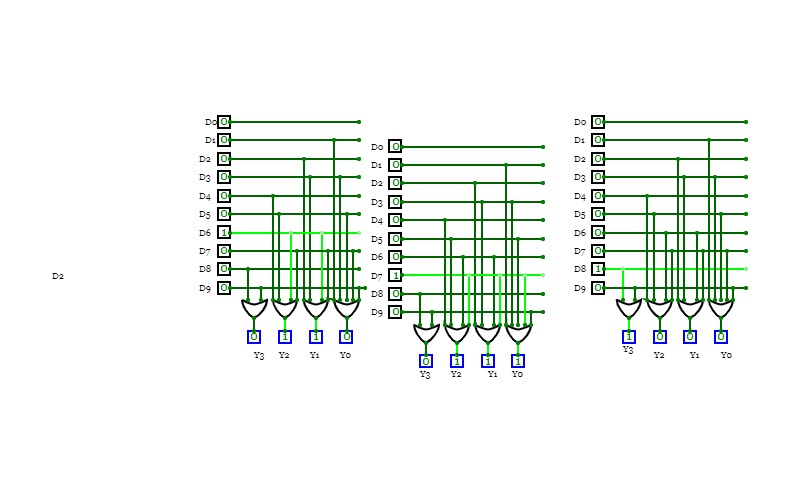

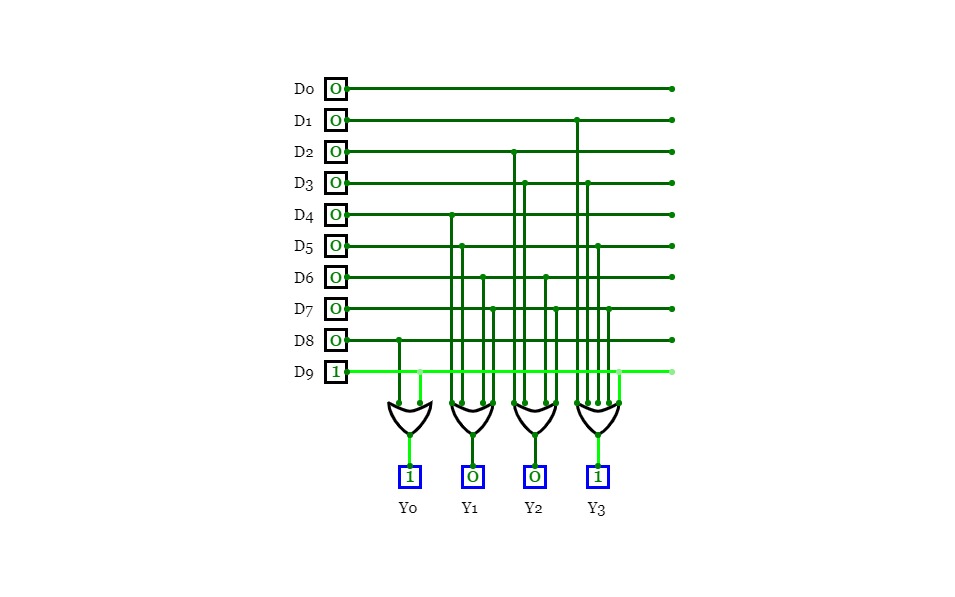

DECIMAL TO BCD ENCODER

DECIMAL TO BCD ENCODER

DECIMAL TO BCD ENCODER

DECIMAL TO BCD ENCODER

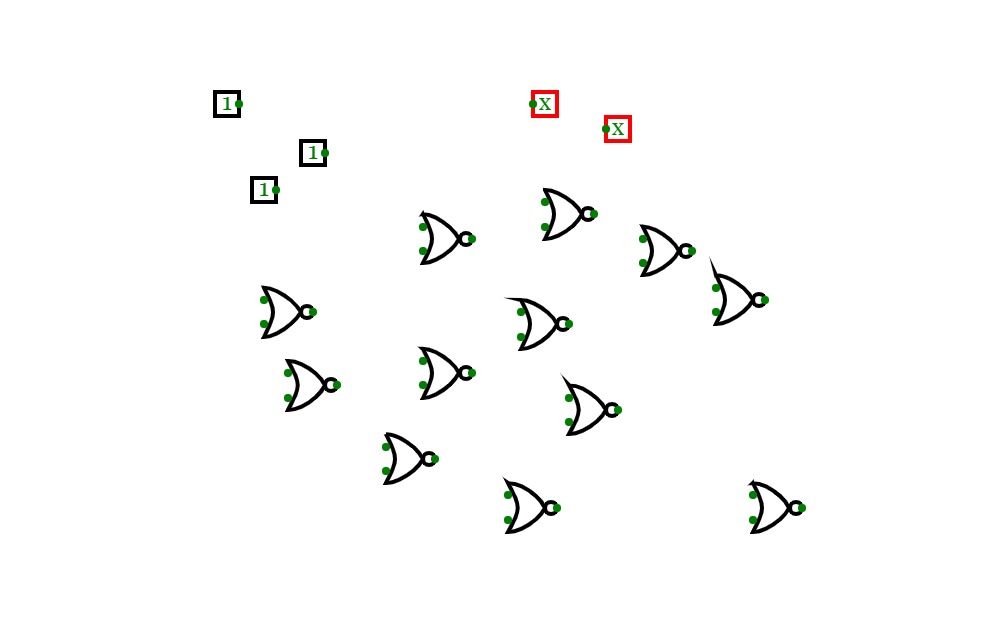

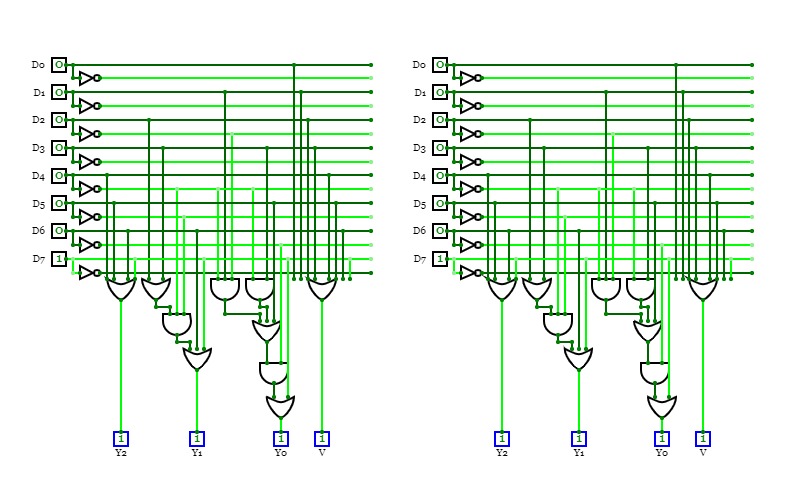

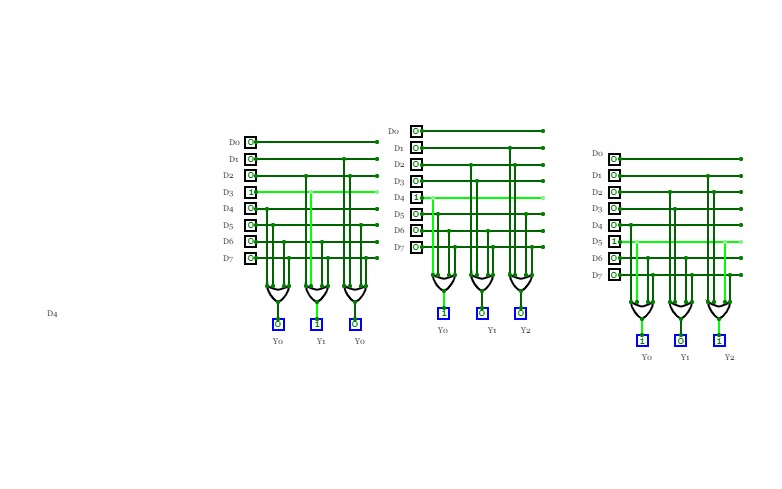

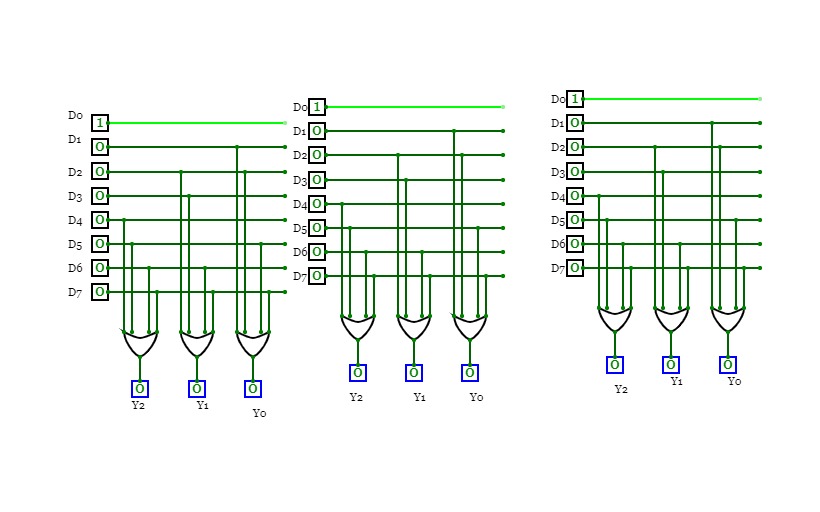

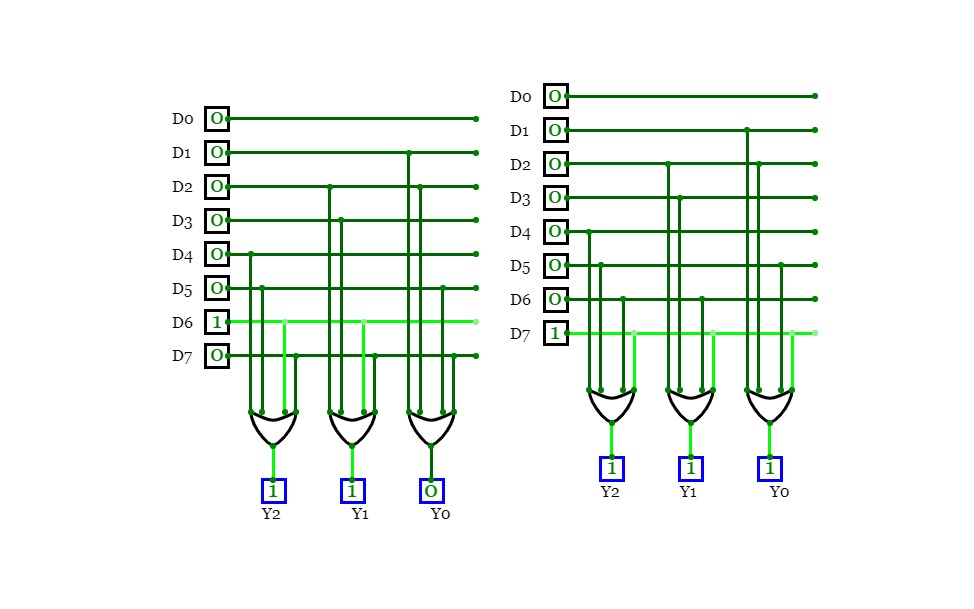

8 TO 3 PRIORITY ENCODER

8 TO 3 PRIORITY ENCODER

BCD to 7 SEGMENT DECODER

BCD to 7 SEGMENT DECODER

BCD TO DECIMAL DECODER

BCD TO DECIMAL DECODER

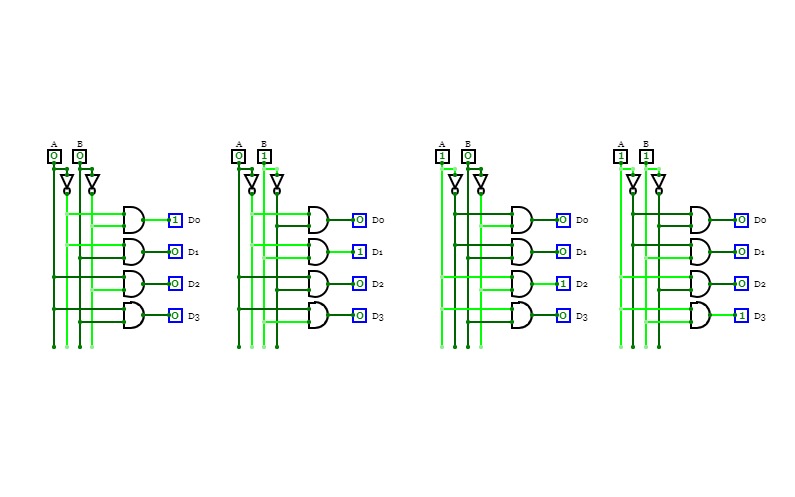

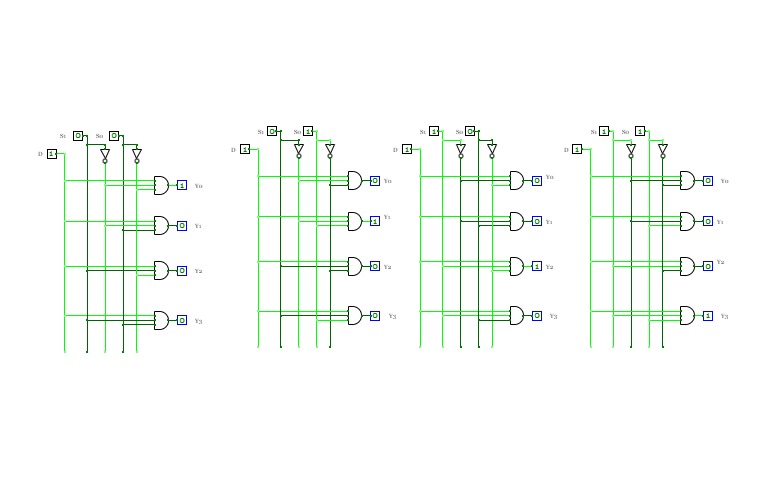

2 TO 4 DECODER

2 TO 4 DECODER

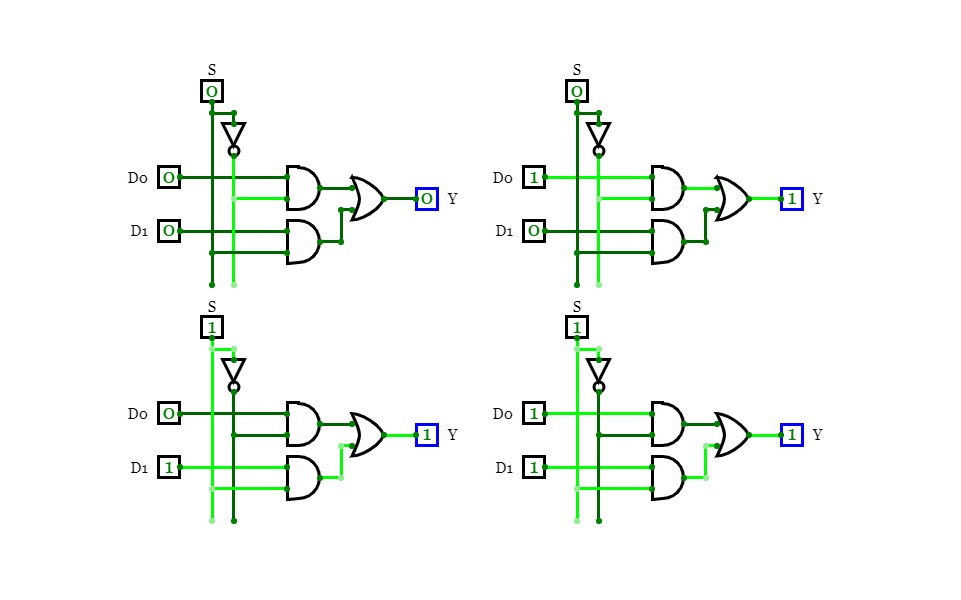

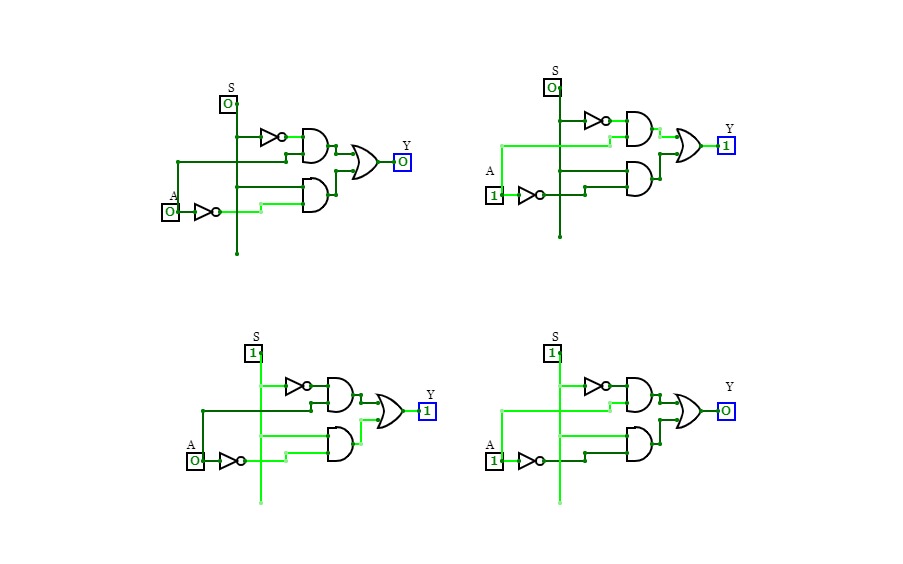

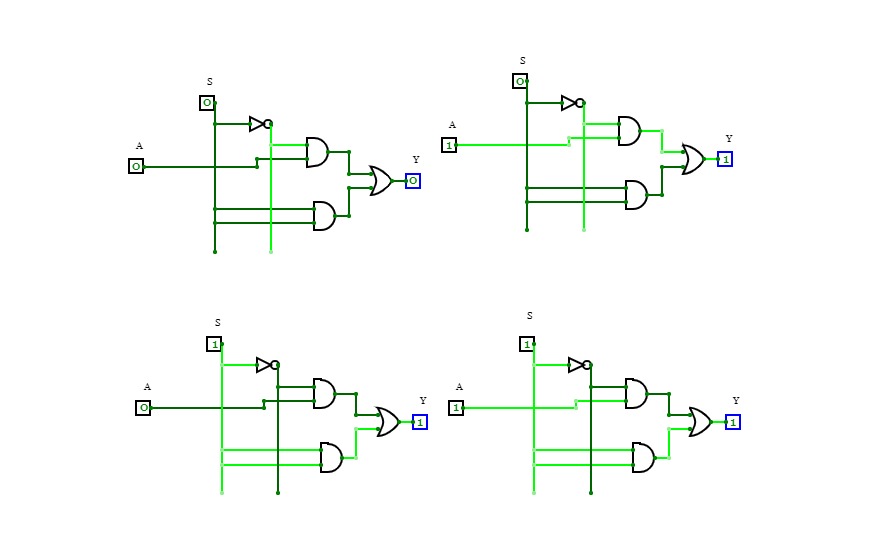

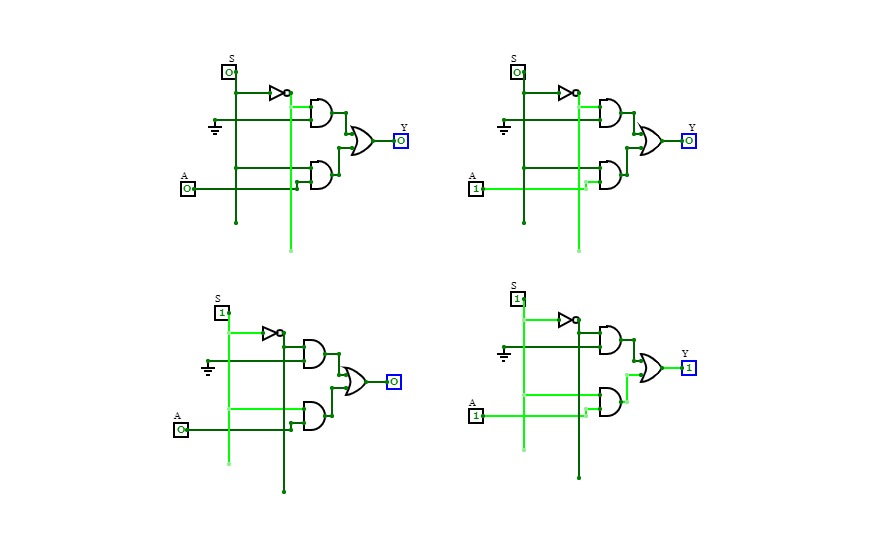

2 TO 1 MUX

2 TO 1 MUX

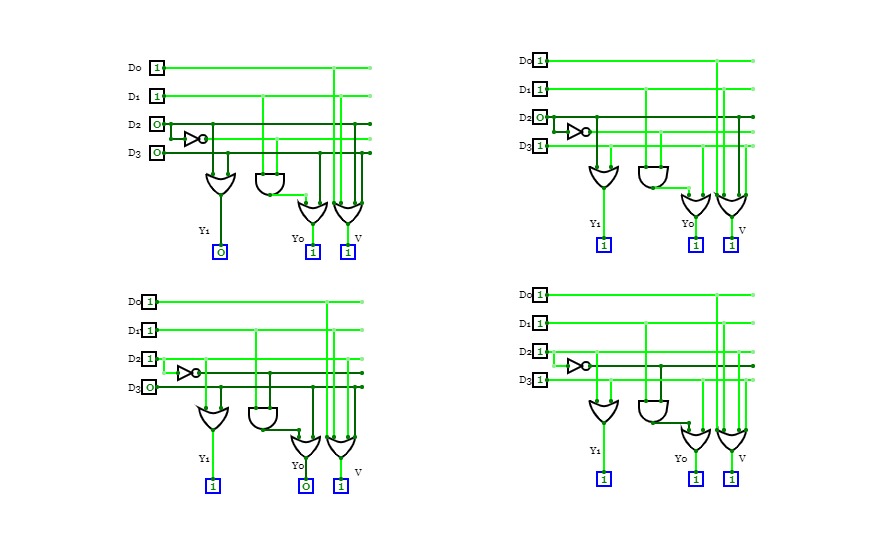

4 to 2 Priority Encoder

4 to 2 Priority Encoder

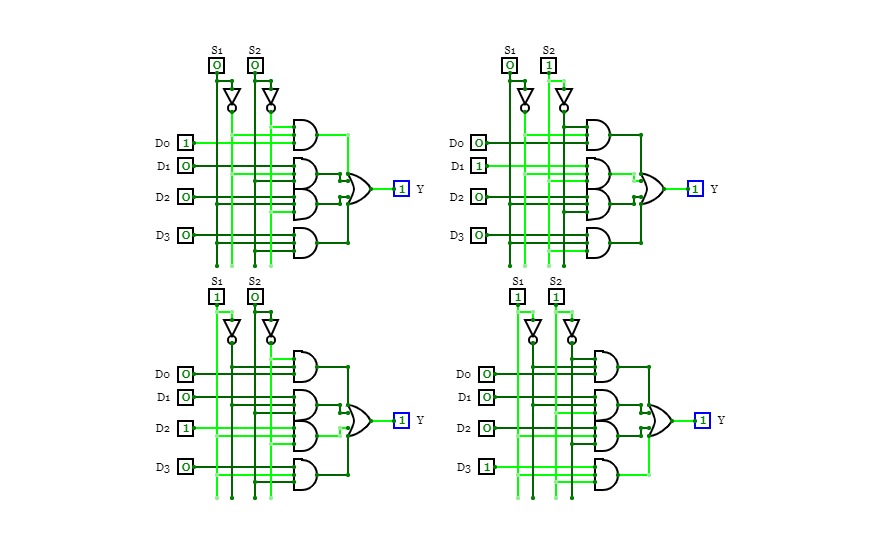

4 TO 1 MUX

4 TO 1 MUX

EXOR USING 2 TO 1 MUX

EXOR USING 2 TO 1 MUX

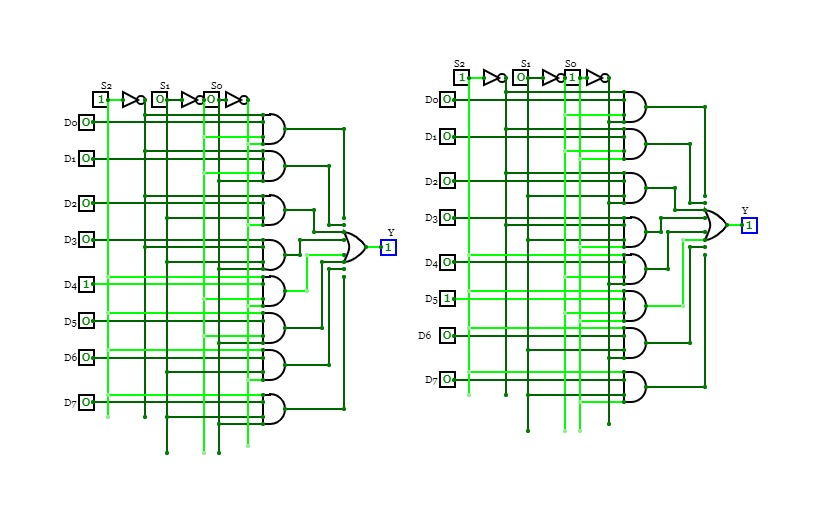

8 TO 1 MUX

8 TO 1 MUX

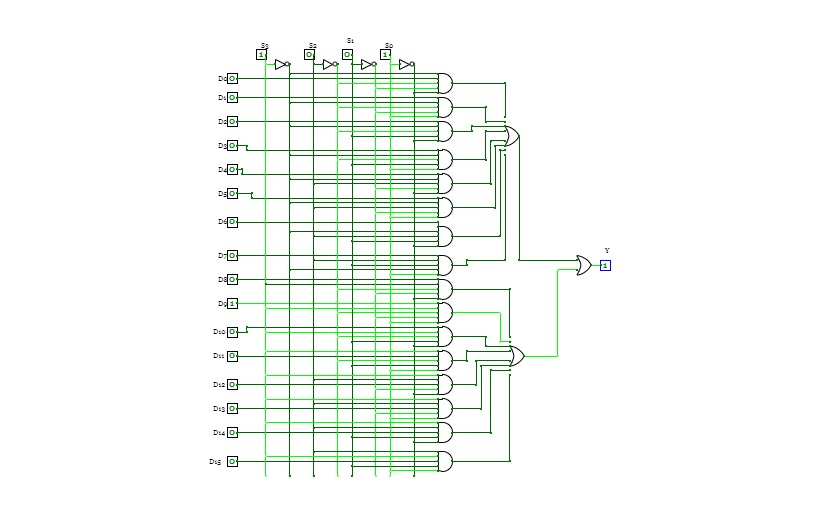

16 TO 1 MUX

16 TO 1 MUX

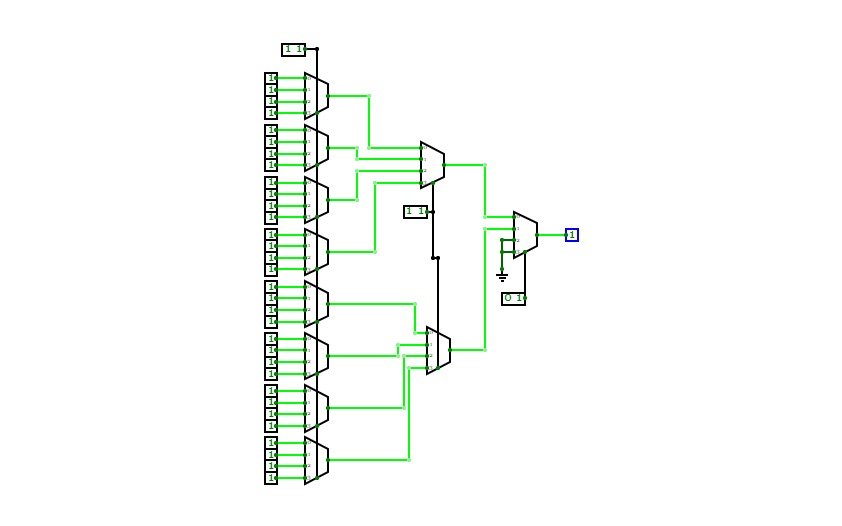

32:1 mux using 4:1 mux

32:1 mux using 4:1 mux

32 TO 1 MUX USING 4 TO 1 MUX

32 TO 1 MUX USING 4 TO 1 MUX

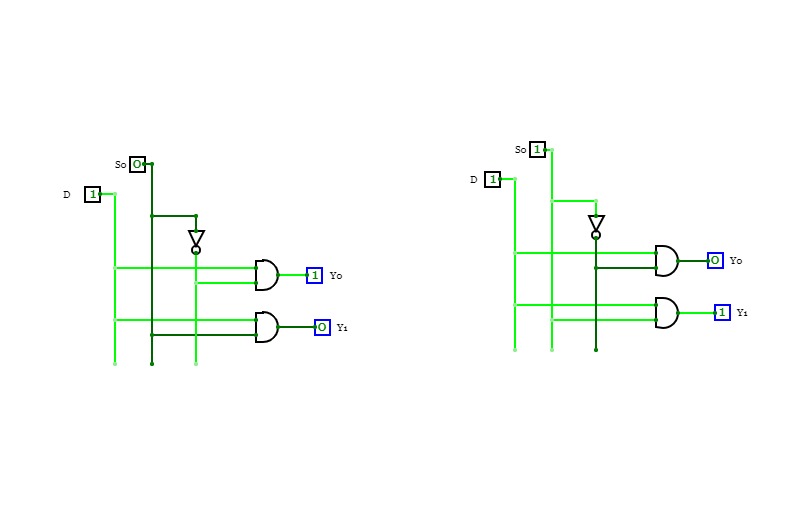

1 TO 2 DEMUX

1 TO 2 DEMUX

1 TO 4 DEMUX

1 TO 4 DEMUX

16 TO 1 MUX

16 TO 1 MUX

BCD to 7 SEGMENT DECODER

BCD to 7 SEGMENT DECODER

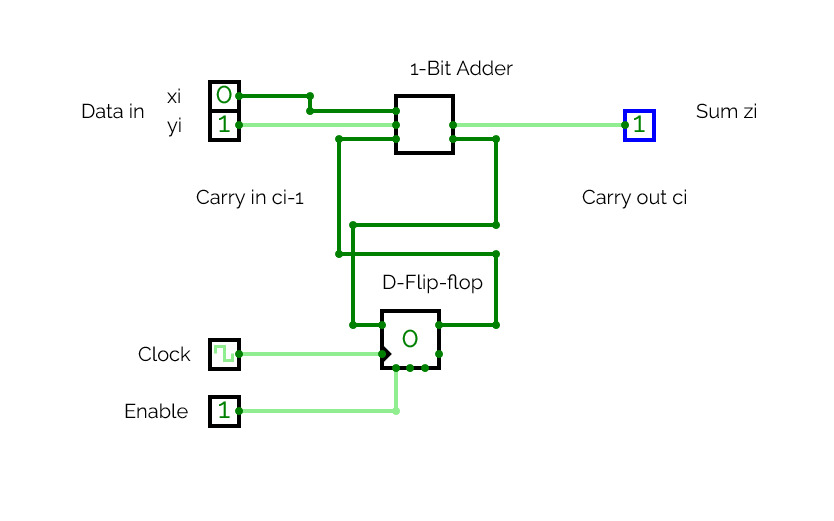

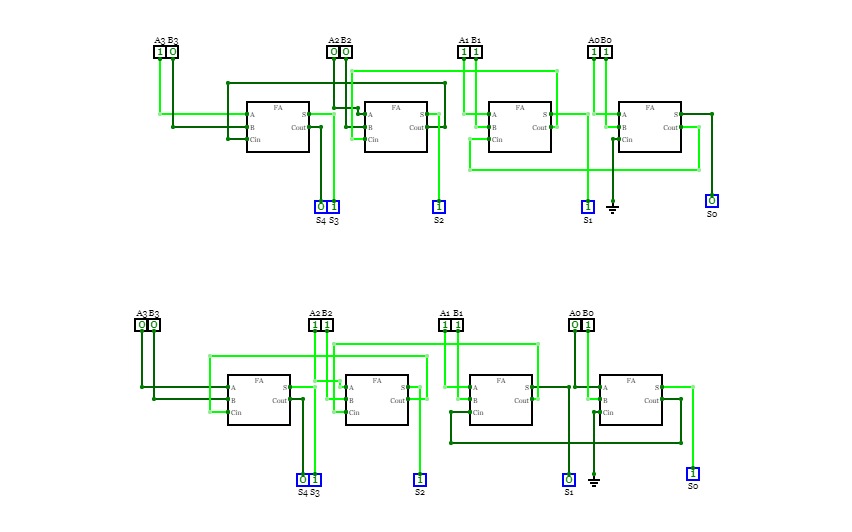

Ripple carry Adder

Ripple carry Adder

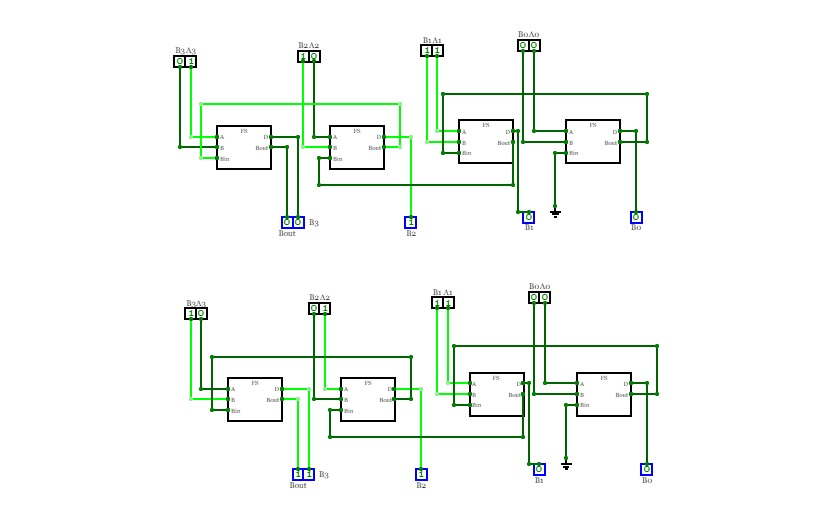

RIPPLE CARRY SUBTRACTOR

RIPPLE CARRY SUBTRACTOR

3 BIT PARALLEL MULTIPLIER

3 BIT PARALLEL MULTIPLIER

3 BIT PARALLEL MULTIPLIER

3 BIT PARALLEL MULTIPLIER

4 BIT ADDER /SUBTRACTOR

4 BIT ADDER /SUBTRACTOR

BCD to 7 SEGMENT DECODER

BCD to 7 SEGMENT DECODER

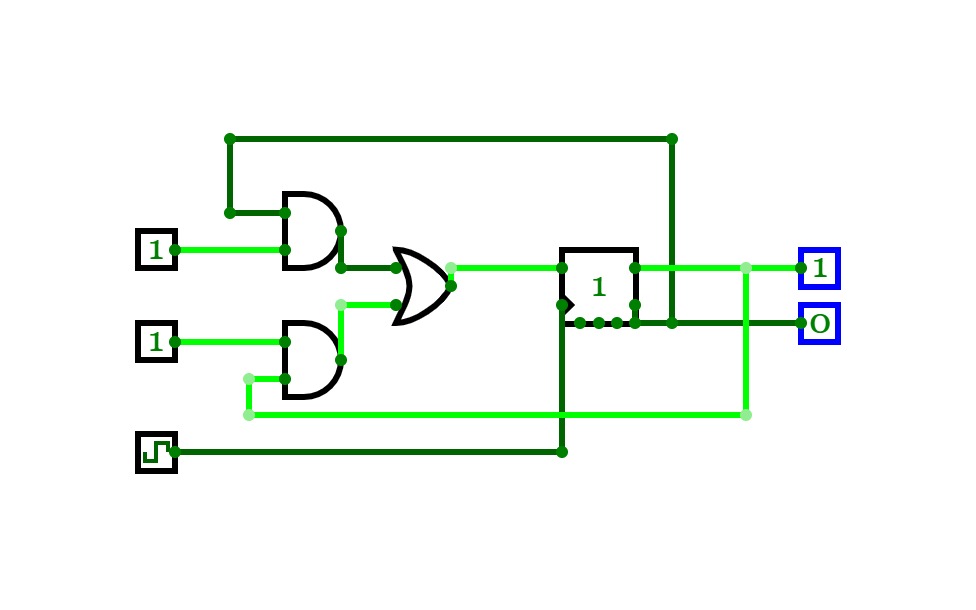

JK FLIPFLOP

JK FLIPFLOP

DFF USING JKFF

DFF USING JKFF

T FLIPFLOP

T FLIPFLOP

BCD to 7 segment decoder

BCD to 7 segment decoder

OCTAL TO BINARY ENCODER

OCTAL TO BINARY ENCODER

4 to 2 priority encoder

4 to 2 priority encoder

NOR USING 2 TO 1 MUX

NOR USING 2 TO 1 MUX

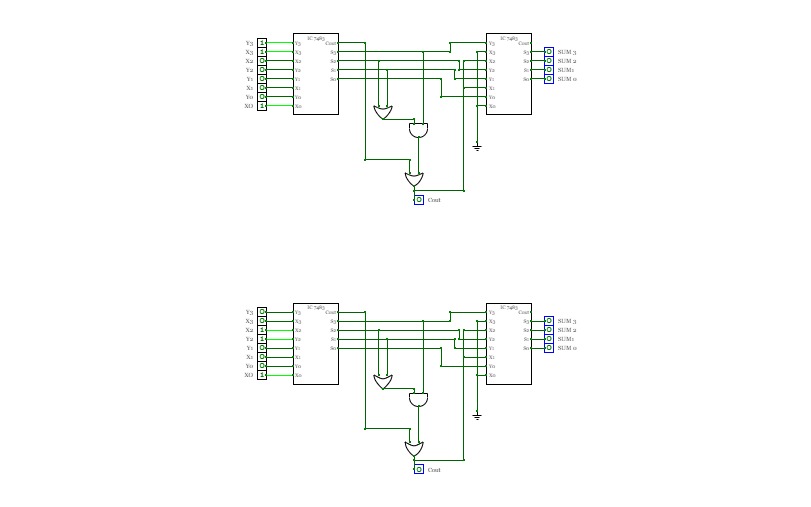

BCD ADDER

BCD ADDER

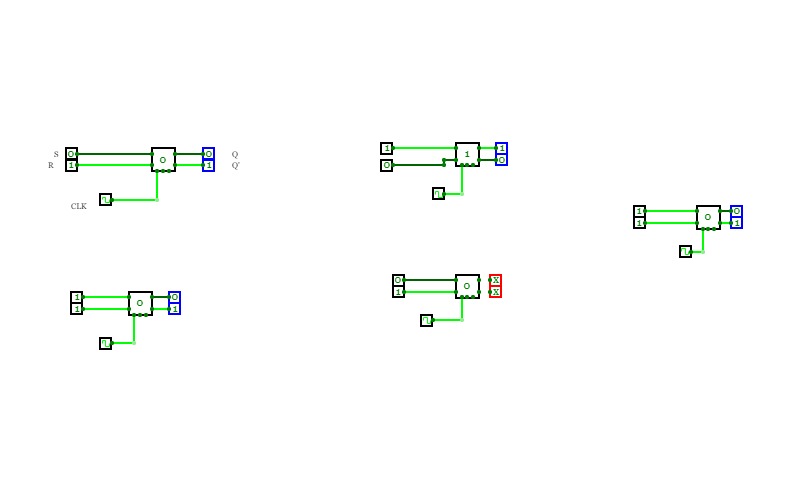

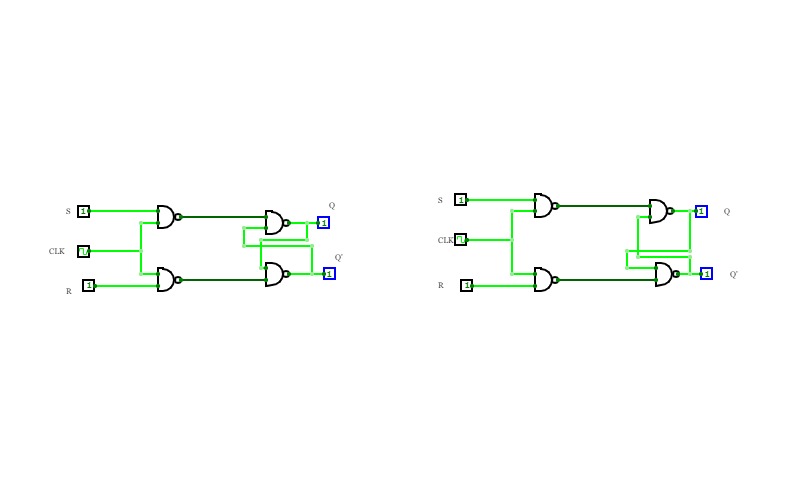

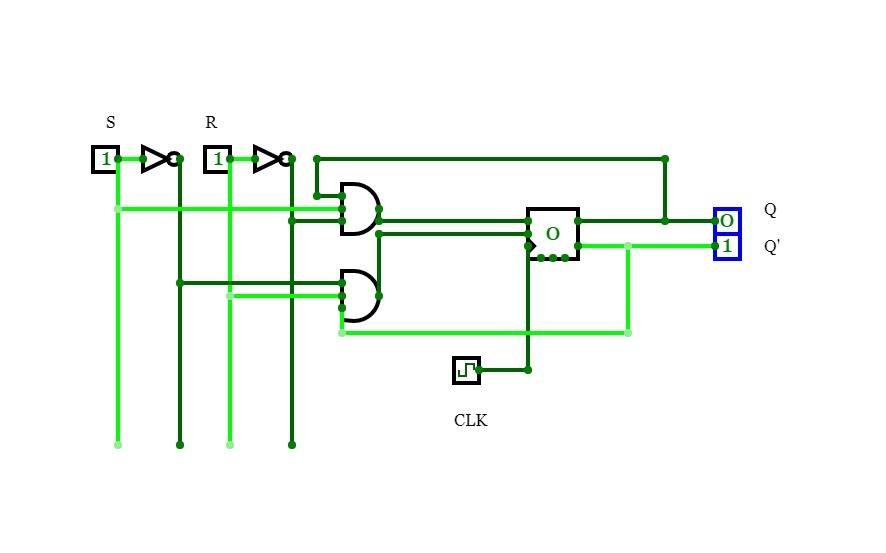

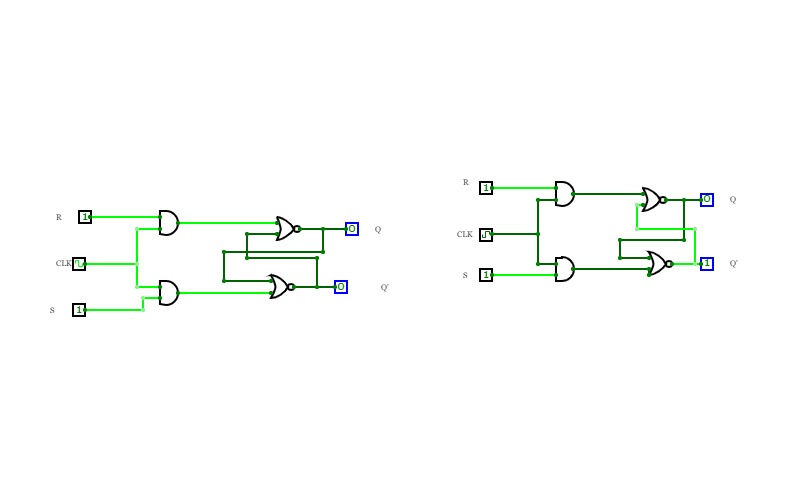

SR FLIPFLOP

SR FLIPFLOP

ASSIGNMENT 2

ASSIGNMENT 2

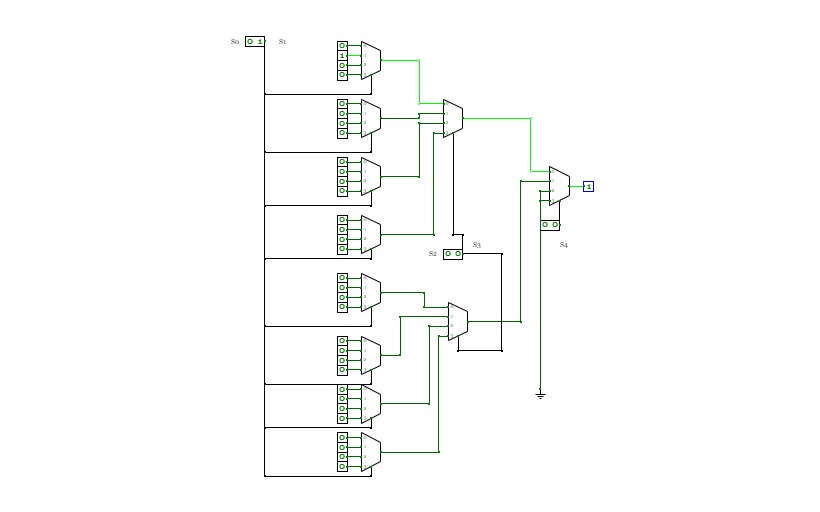

1 TO 16 DEMUX

1 TO 16 DEMUX

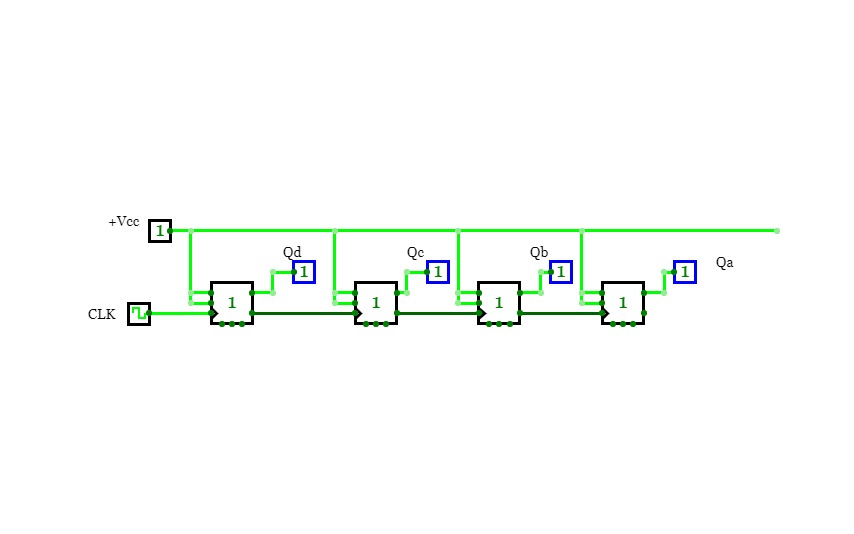

4 BIT RIPPLE COUNTER

4 BIT RIPPLE COUNTER

BCD to 7 SEGMENT DECODER

BCD to 7 SEGMENT DECODER

4 bit synchronous counter

4 bit synchronous counter

BCD to 7 SEGMENT DECODER

BCD to 7 SEGMENT DECODER

JKFF using SRFF

JKFF using SRFF

1 to 8 DEMUX

1 to 8 DEMUX

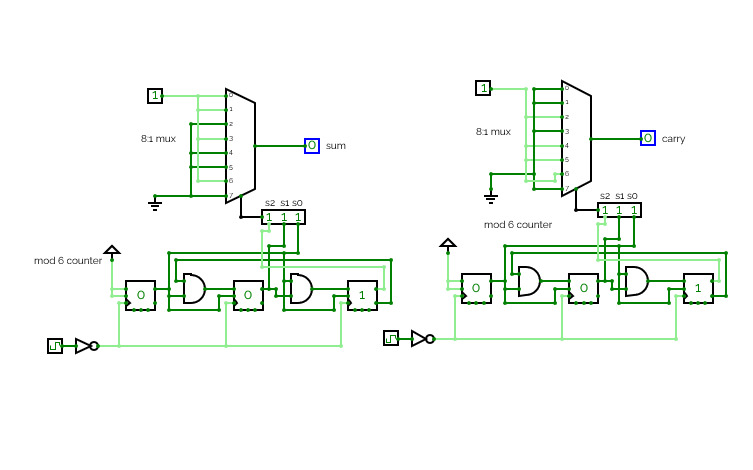

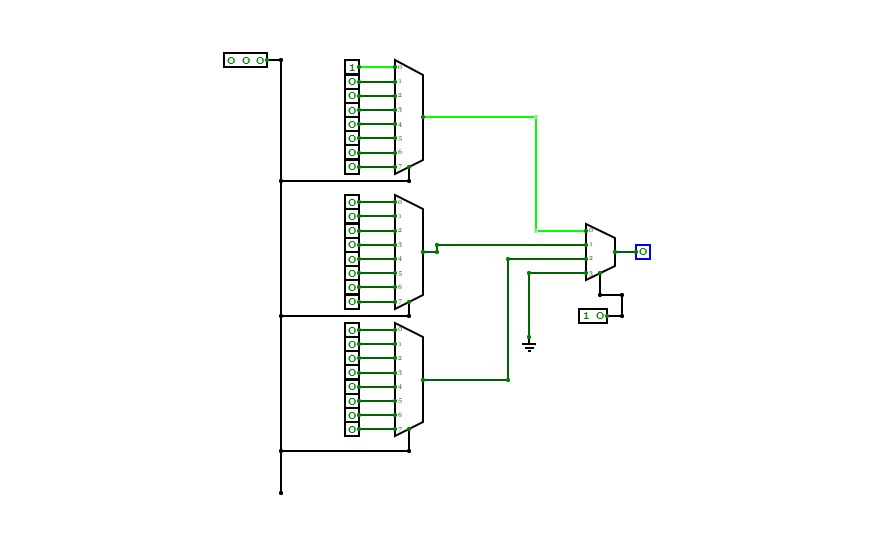

implementation of full adder with mux and counter

implementation of full adder with mux and counter

NAND BASED SR FLIPFLOP

NAND BASED SR FLIPFLOP

BCD to 7 SEGMENT DECODER

BCD to 7 SEGMENT DECODER

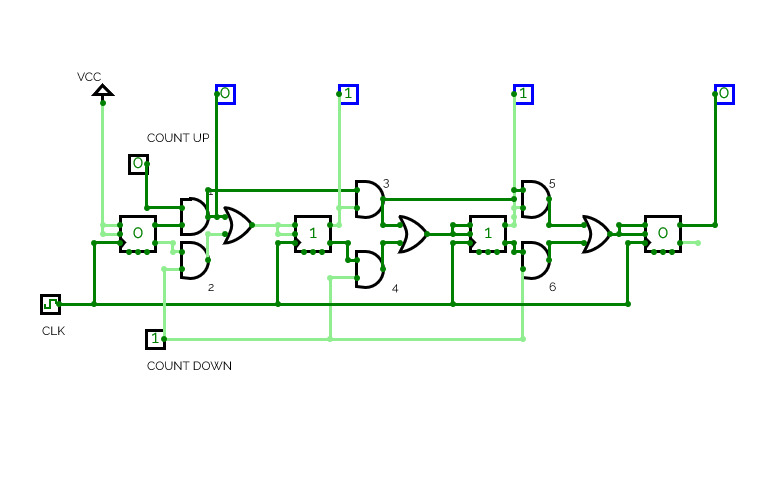

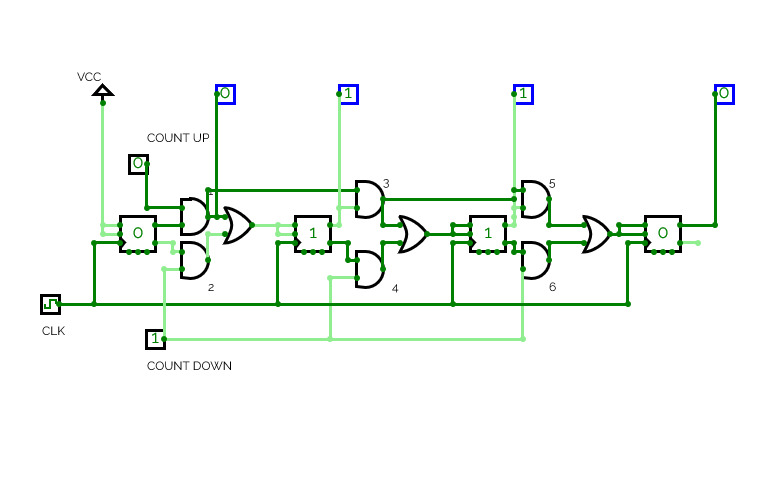

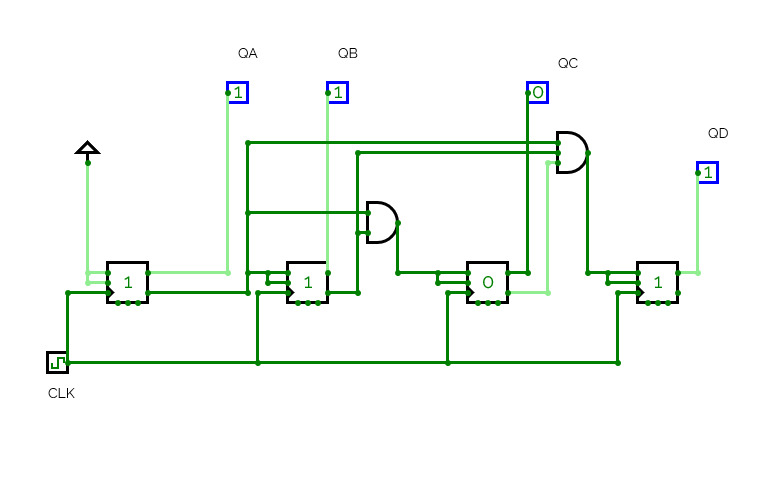

4 bit synchronous UP/DOWN counter

4 bit synchronous UP/DOWN counter

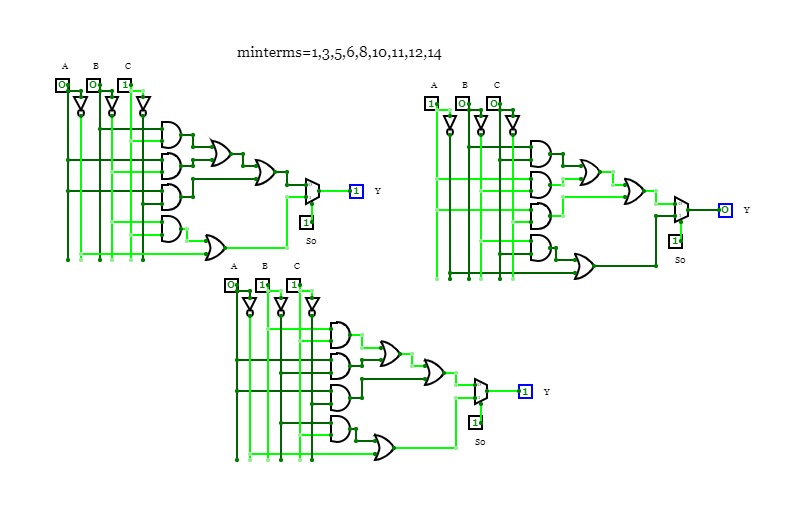

implementation using minterms with 2:1 MUX

implementation using minterms with 2:1 MUX

Untitled

Untitled

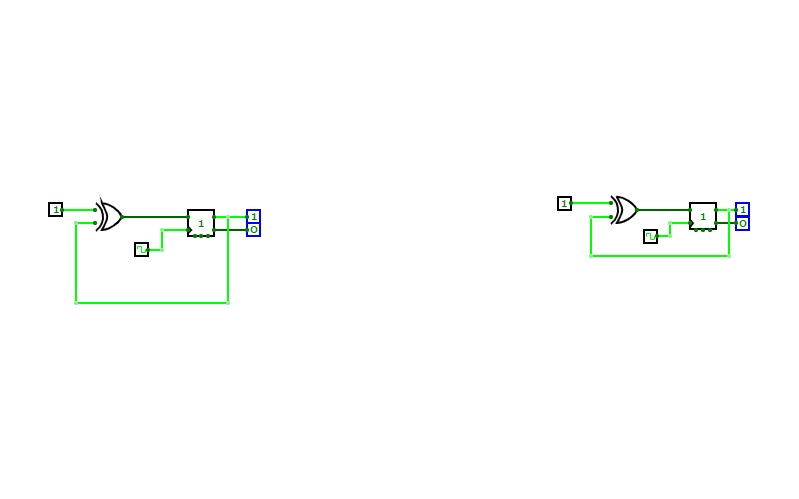

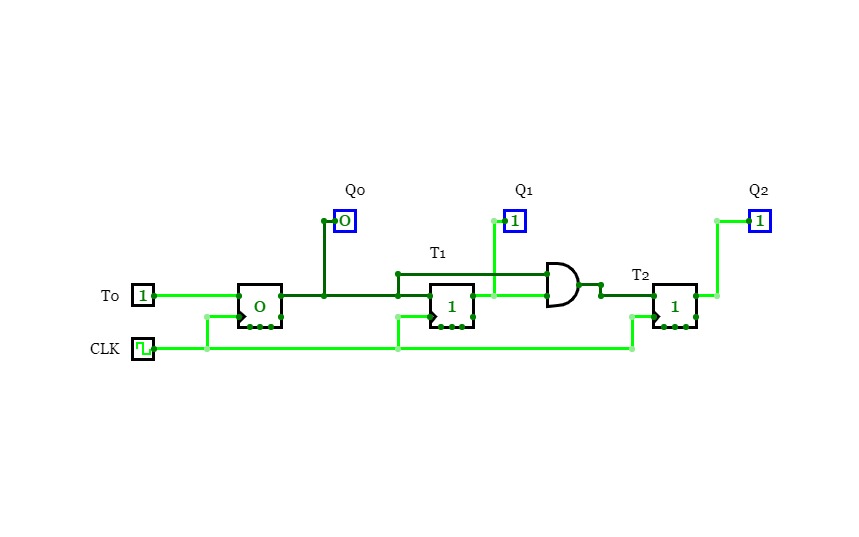

TFF

TFF

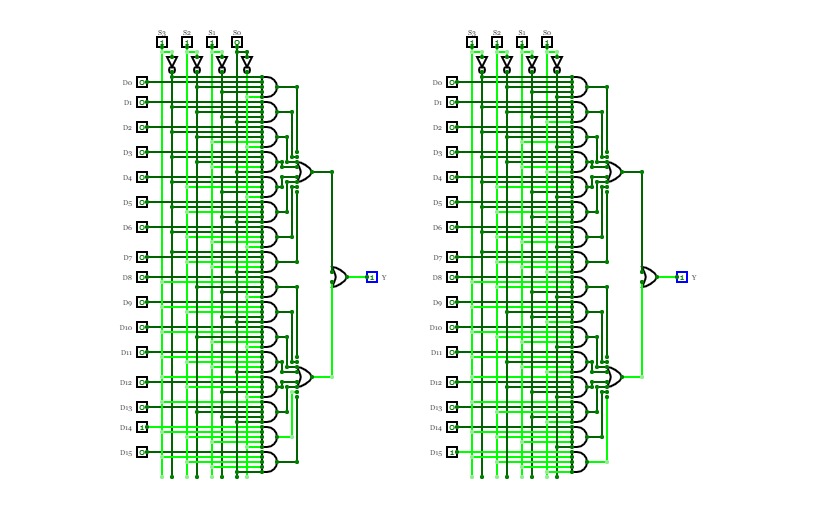

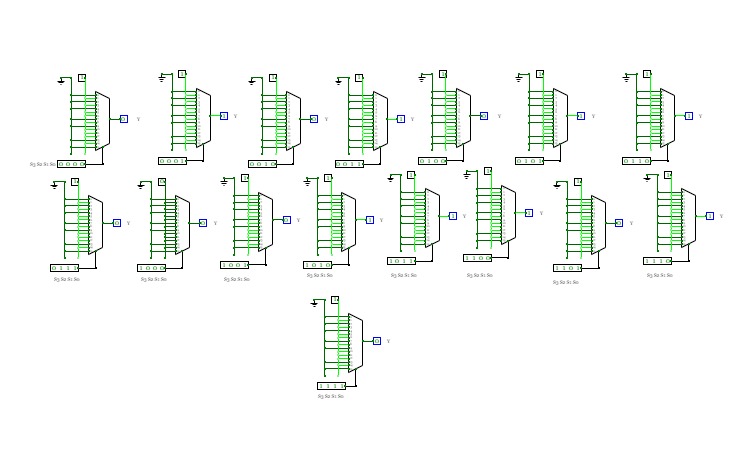

IMPLEMENTATION USING MINTERMS WITH 16:1 MUX

IMPLEMENTATION USING MINTERMS WITH 16:1 MUX

SRFF USING TFF

SRFF USING TFF

1 to 8 DEMUX

1 to 8 DEMUX

3 bit binary counter

3 bit binary counter

circuit that counts (0,2,4...14)when input is 1 and counts (1,3...15)when input is 0

circuit that counts (0,2,4...14)when input is 1 and counts (1,3...15)when input is 0

SRFF USING JKFF

SRFF USING JKFF

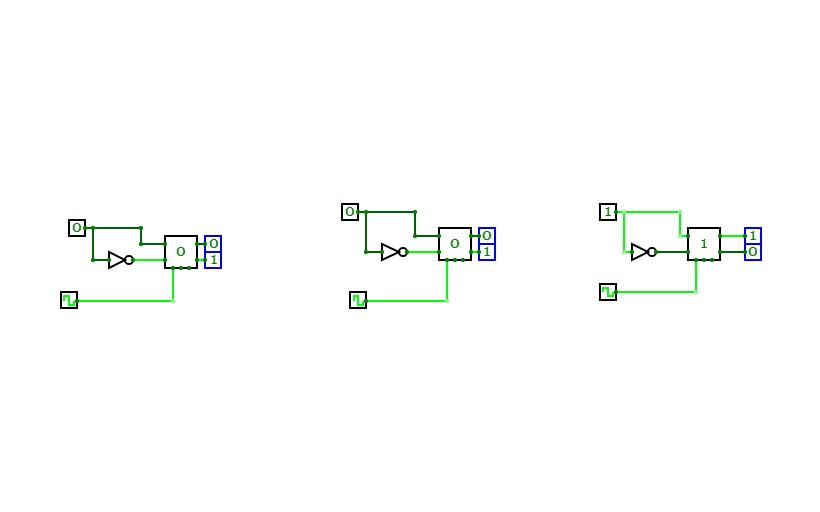

NOT USING 2 TO 1 MUX

NOT USING 2 TO 1 MUX

SISO

SISO

IMPLEMENTATION USING MINTERNS WITH 4:1 MUX

IMPLEMENTATION USING MINTERNS WITH 4:1 MUX

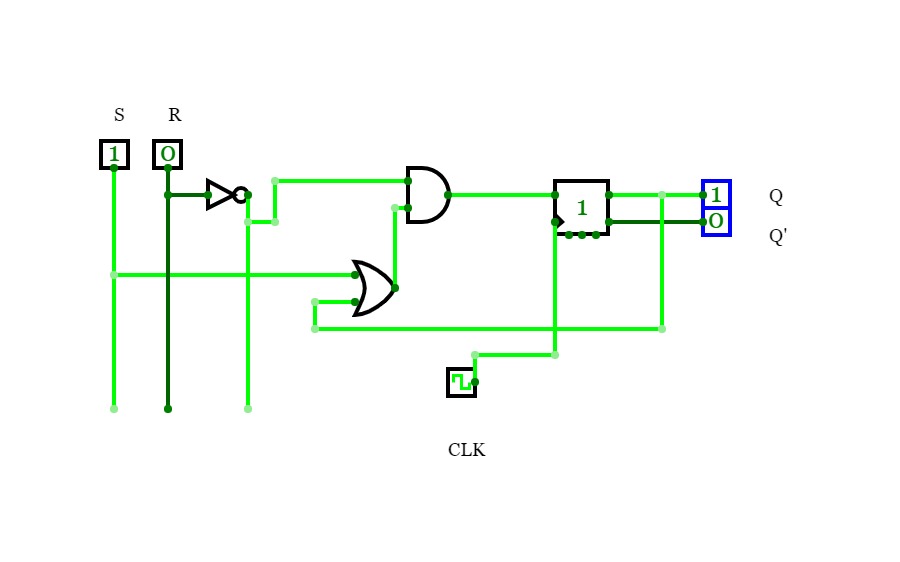

DFF USING SRFF

DFF USING SRFF

4 BIT RIPPLE DOWN COUNTER

4 BIT RIPPLE DOWN COUNTER

OCTAL TO BINARY ENCODER

OCTAL TO BINARY ENCODER

SRFF using DFF

SRFF using DFF

OCTAL TO BINARY ENCODER

OCTAL TO BINARY ENCODER

24 TO 1 MUX USING 8 TO 1 MUX

24 TO 1 MUX USING 8 TO 1 MUX

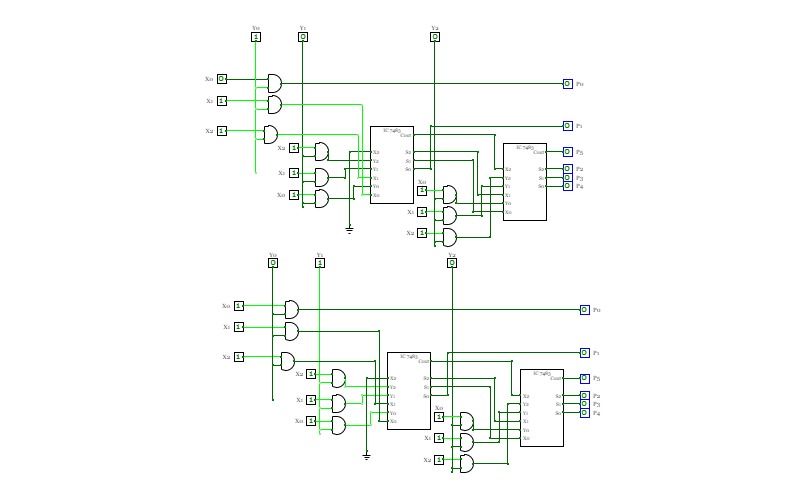

3 BIT PARALLEL MULTIPLIER

3 BIT PARALLEL MULTIPLIER

4 bit synchronous UP/DOWN counter

4 bit synchronous UP/DOWN counter

4 bit synchronous counter

4 bit synchronous counter

MOD 12 COUNTER

MOD 12 COUNTER

DFF USING TFF

DFF USING TFF

4 bit synchronous down counter

4 bit synchronous down counter

IMPLEMENTATION USING MINTERMS WITH 8:1 MUX

IMPLEMENTATION USING MINTERMS WITH 8:1 MUX

OR USING 2 TO 1 MUX

OR USING 2 TO 1 MUX

4 X 2 ENCODER

4 X 2 ENCODER

Untitled

Untitled

32 TO 1 MUX USING 4 TO 1 MUX

32 TO 1 MUX USING 4 TO 1 MUX

CONSENSUS THEOREM

CONSENSUS THEOREM

MOD 7 COUNTER

MOD 7 COUNTER

NOR USING 2 TO 1 MUX

NOR USING 2 TO 1 MUX

NOR BASED SR FLIPFLOP

NOR BASED SR FLIPFLOP

AND USING 2 TP 1 MUX

AND USING 2 TP 1 MUX

BCD to 7 SEGMENT DECODER

BCD to 7 SEGMENT DECODER