sarveshwaran.S

Member since: 4 years

Educational Institution: MEPCO SCHLENK ENGINNERING COLLEGE,SIVAKASI

Country: India

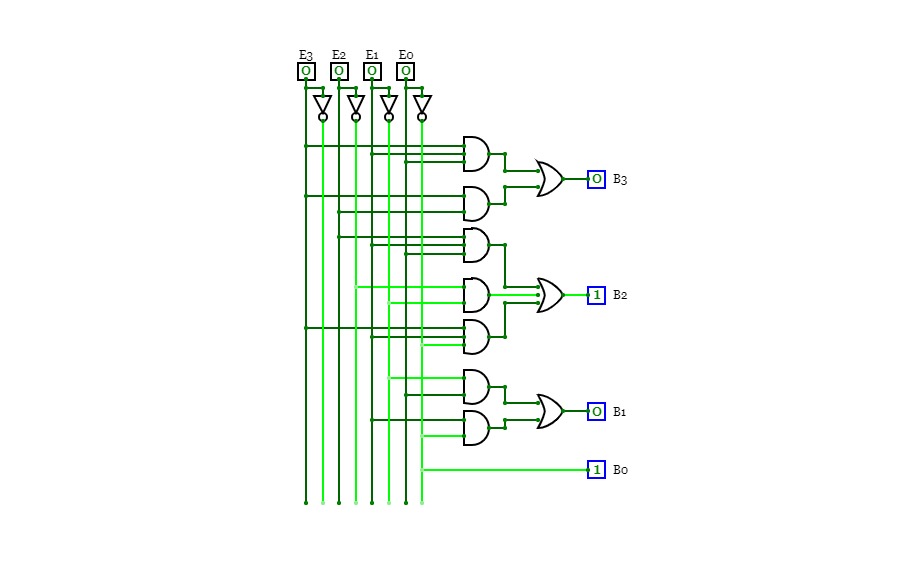

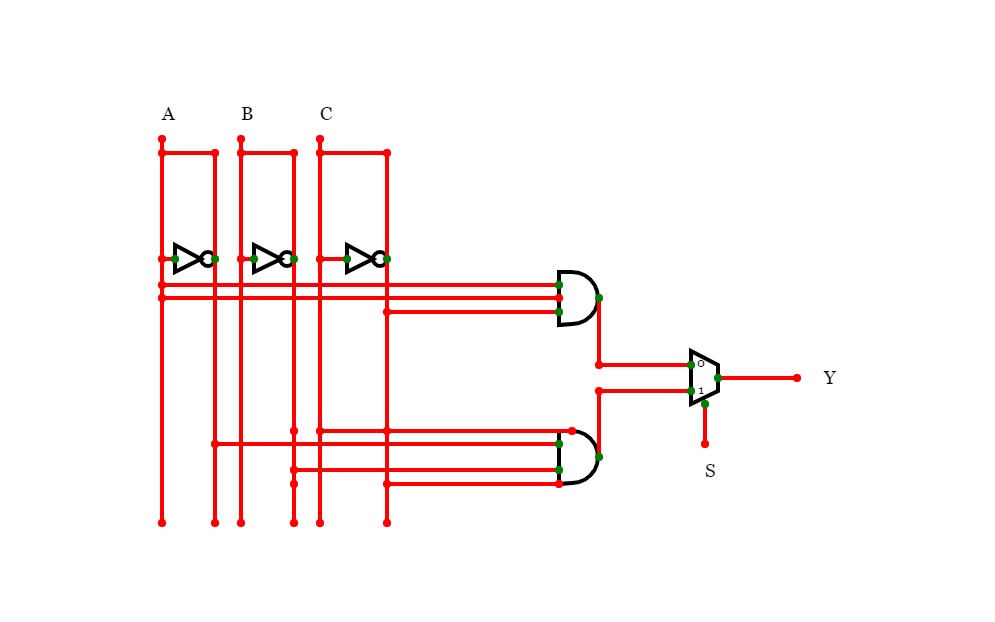

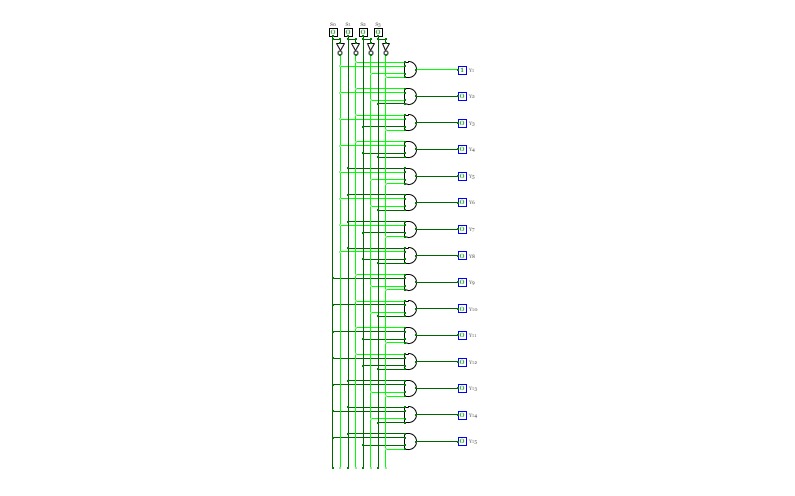

CODE CONVERTERS

CODE CONVERTERS

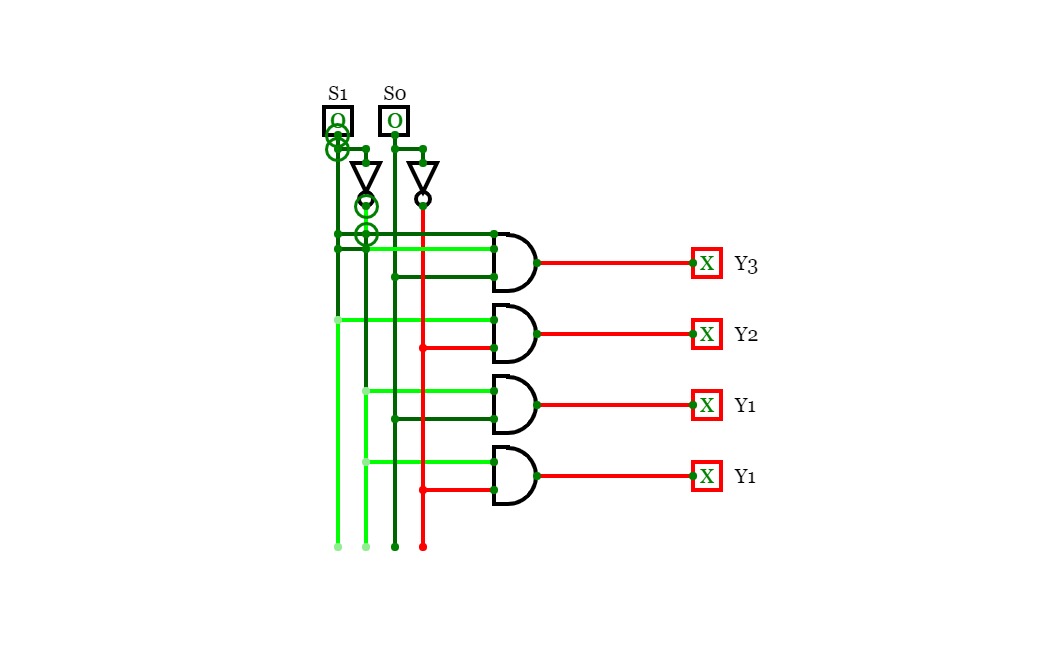

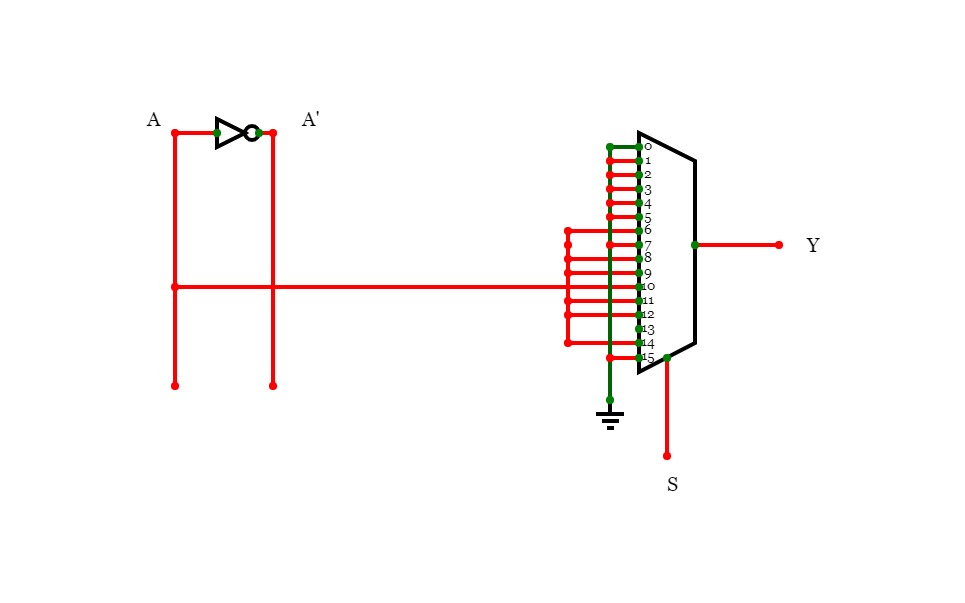

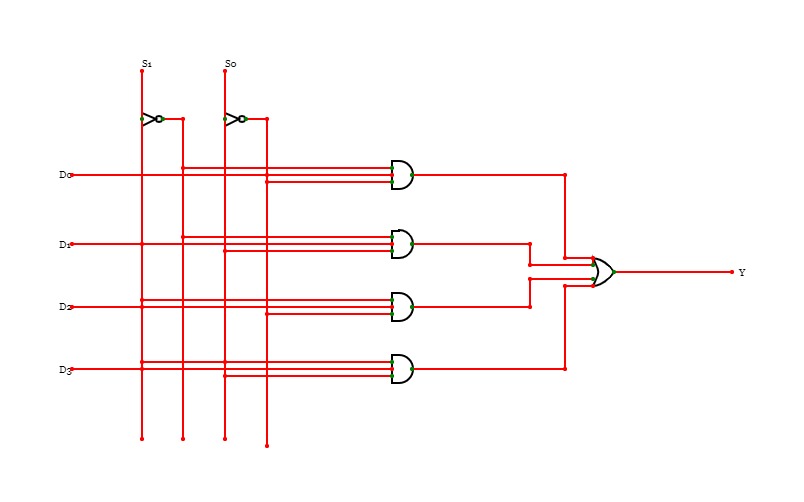

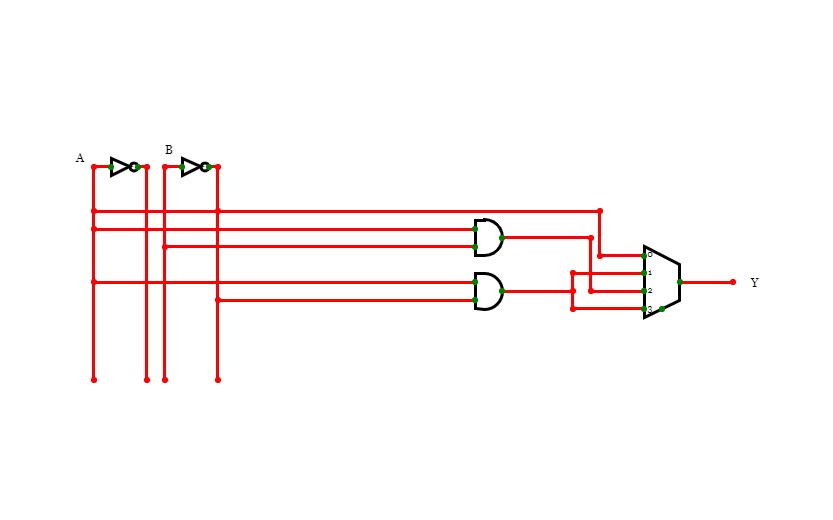

MUX AND DEMUX

MUX AND DEMUX

Untitled

Untitled

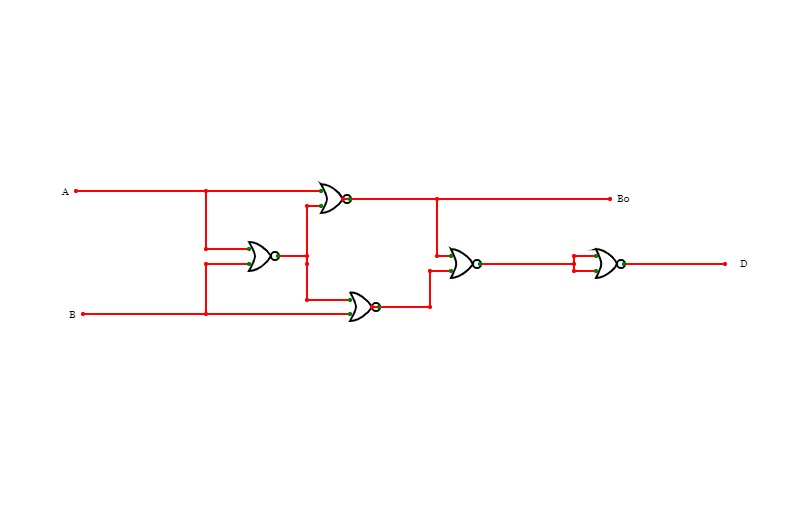

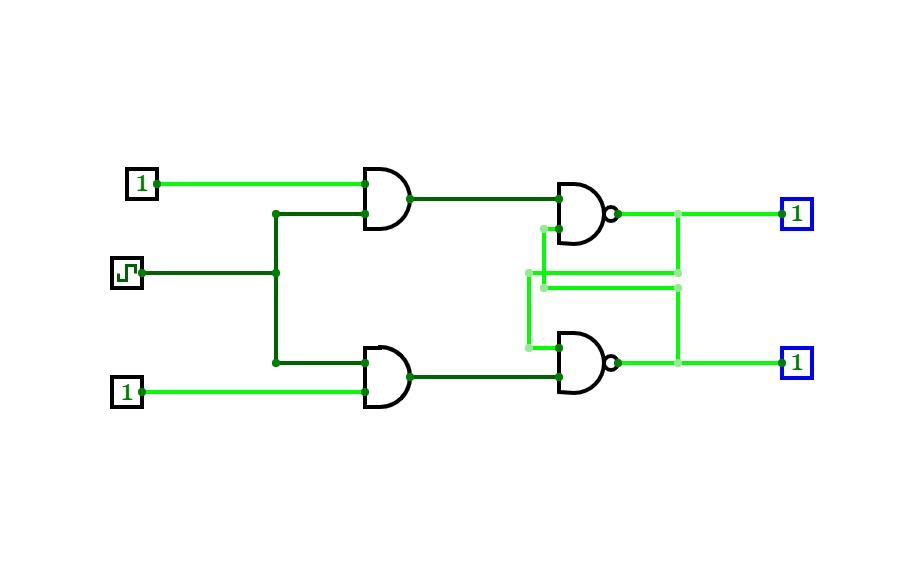

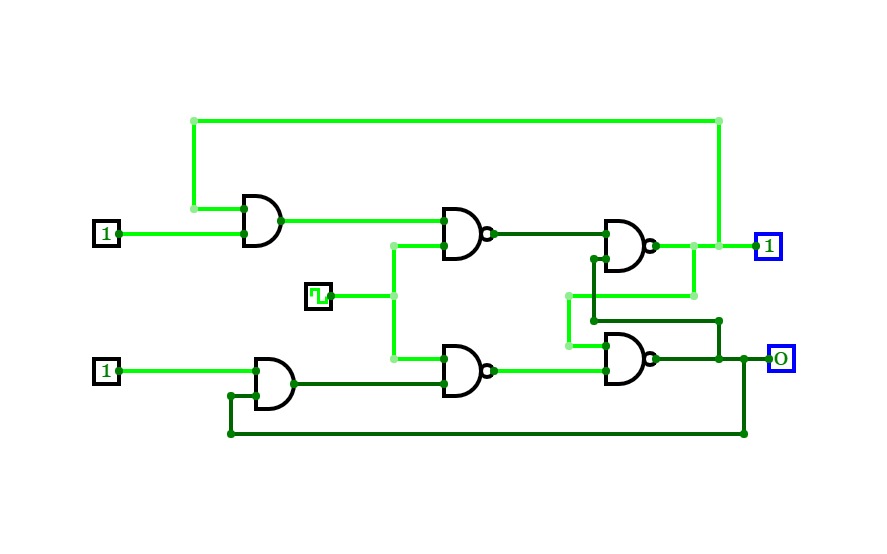

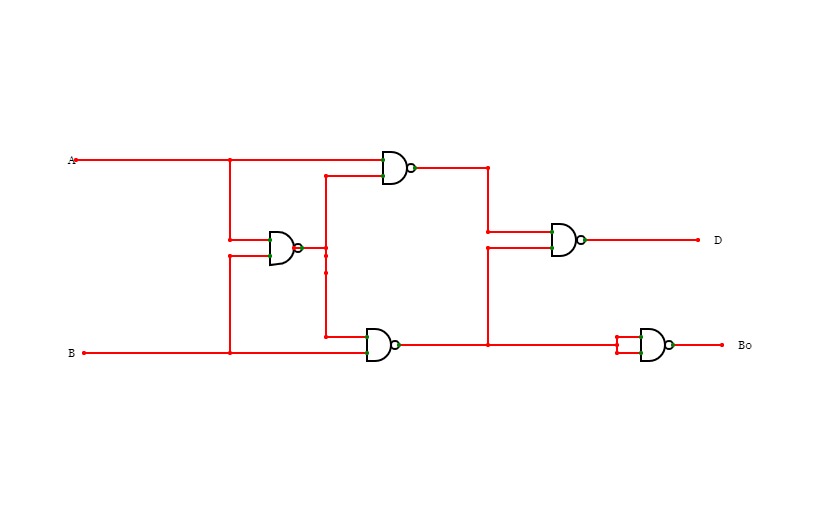

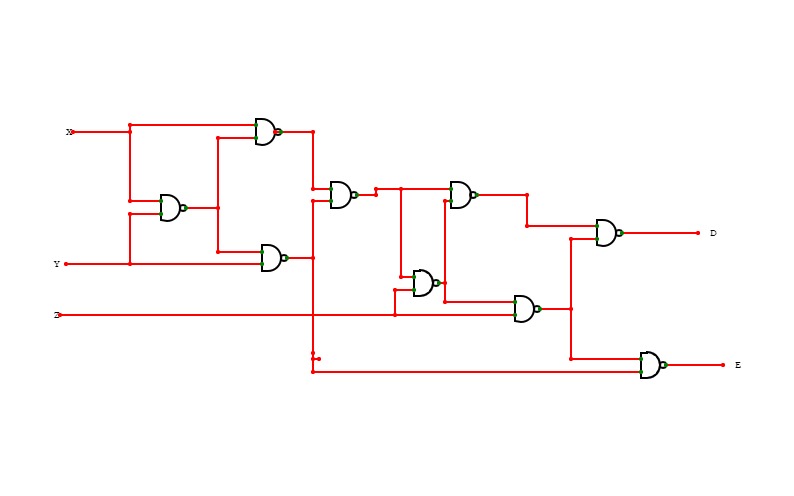

FULL SUBTRACTOR USING NAND GATES

FULL SUBTRACTOR USING NAND GATES

f6tyutyutyyruru

f6tyutyutyyruru

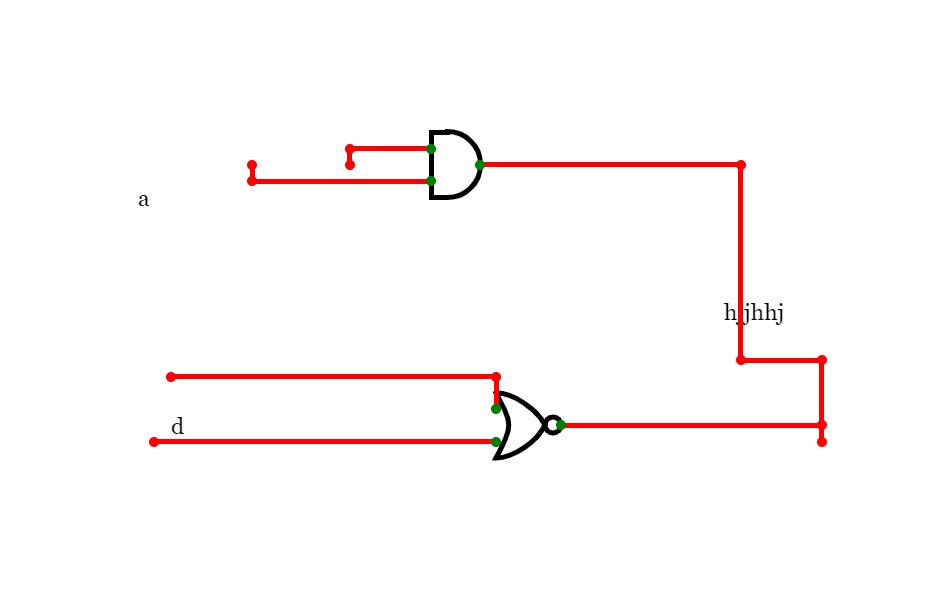

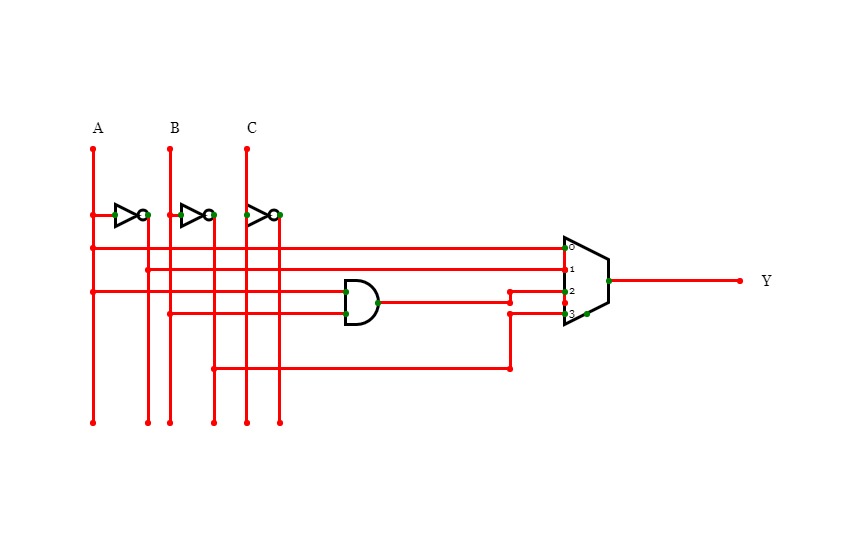

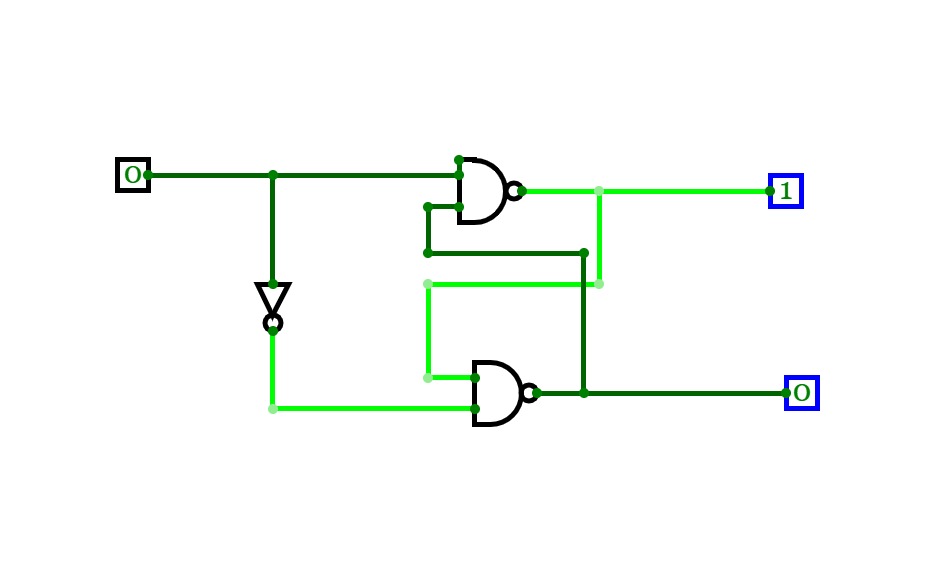

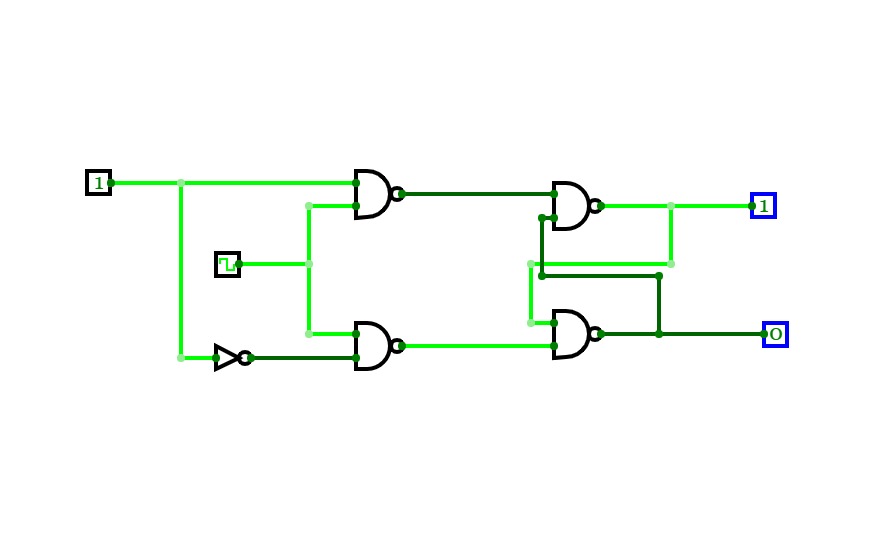

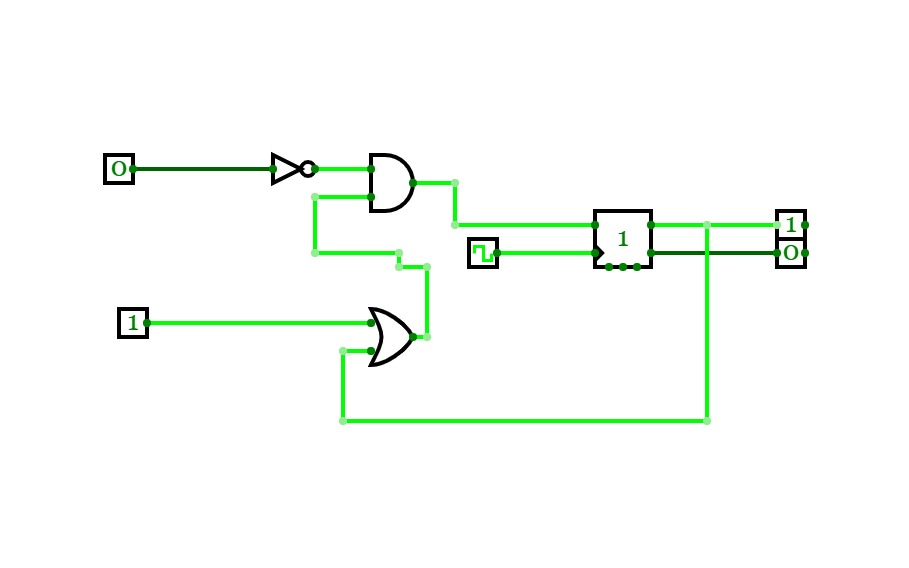

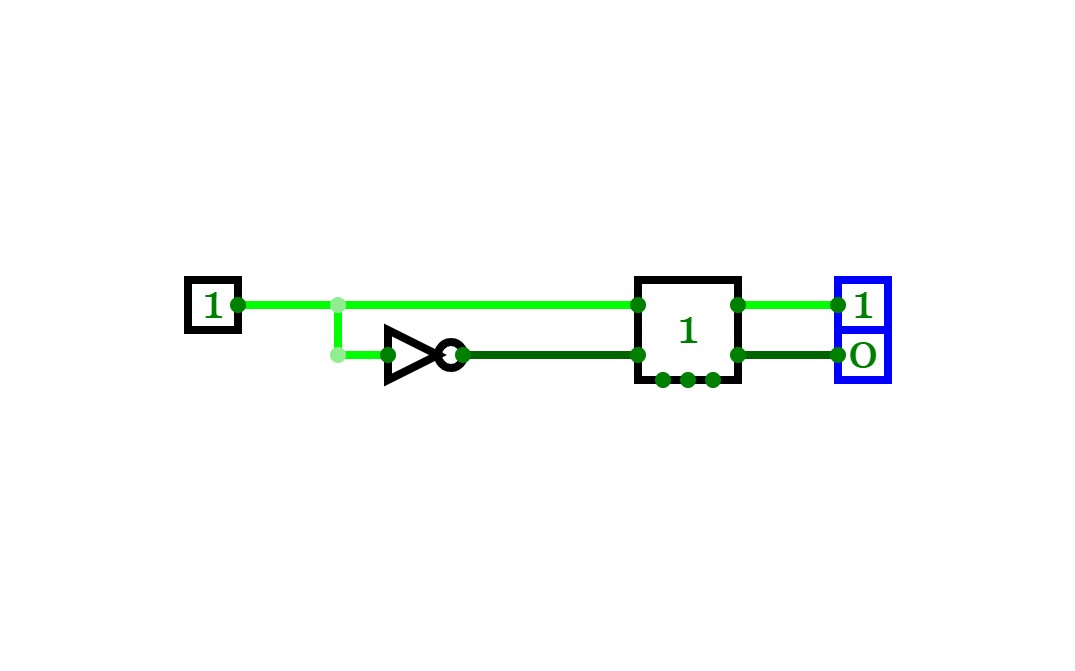

HALF SUBTRACTOR using XOR gate

HALF SUBTRACTOR using XOR gate

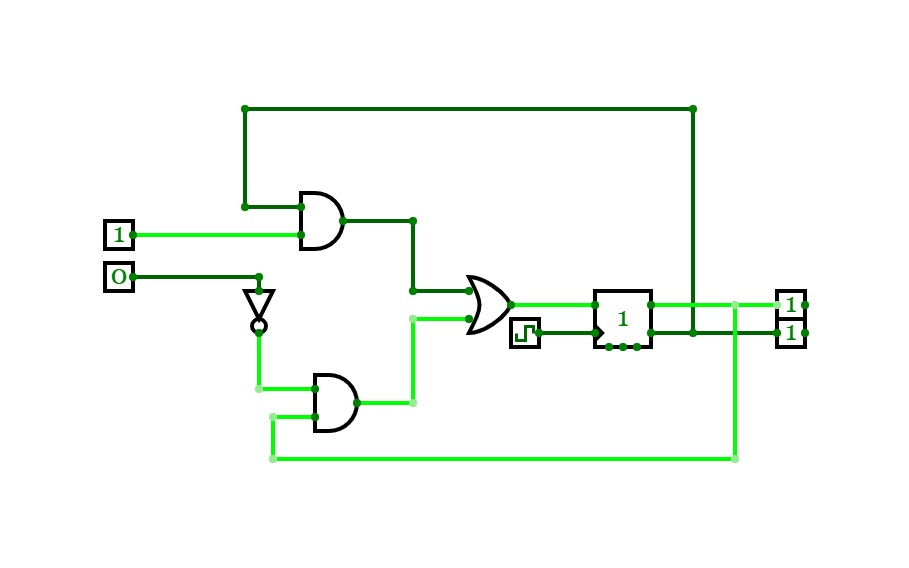

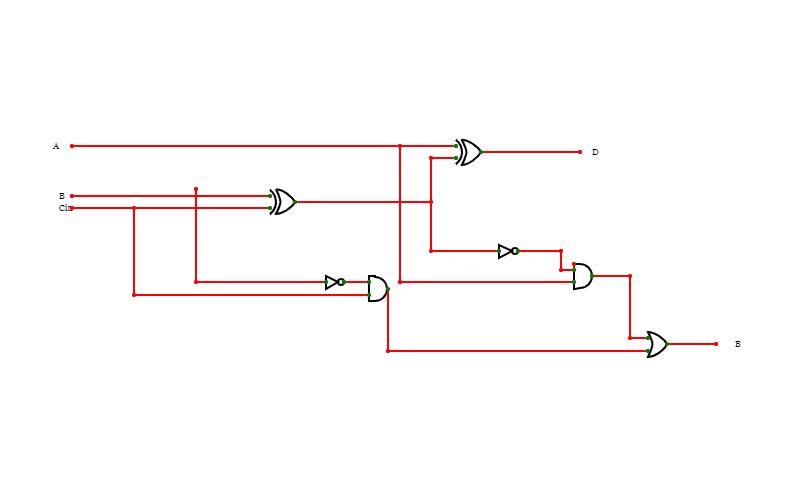

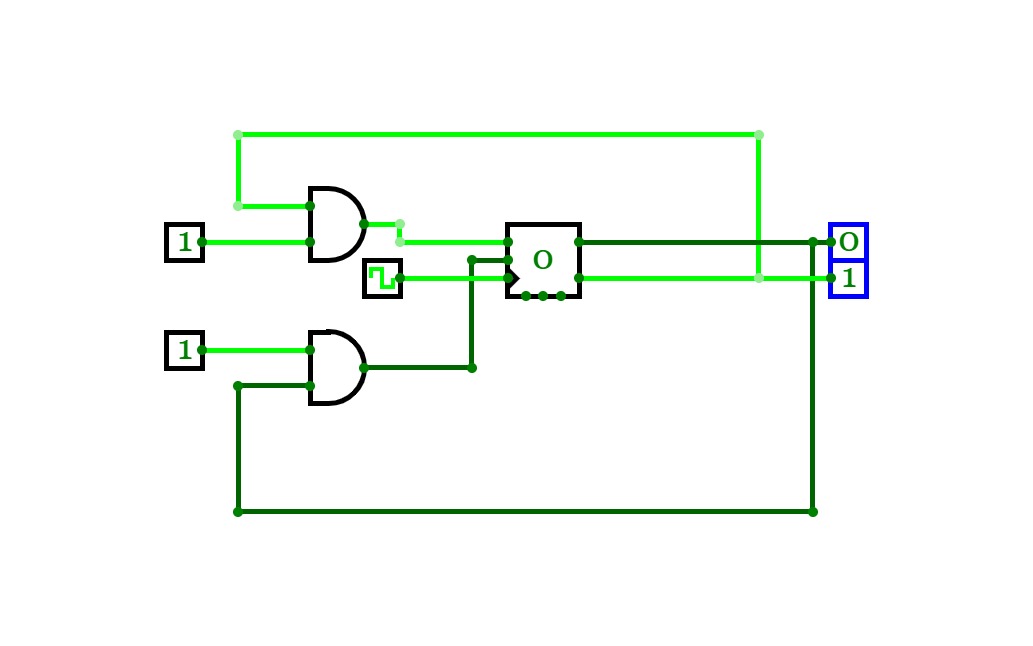

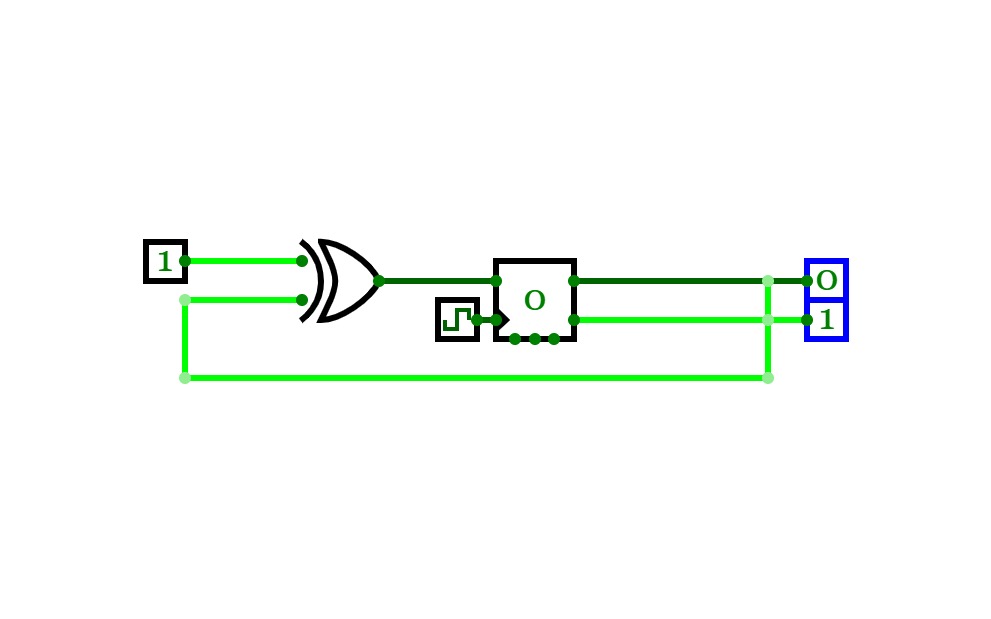

realisation of J-FF using D-FF

realisation of J-FF using D-FF

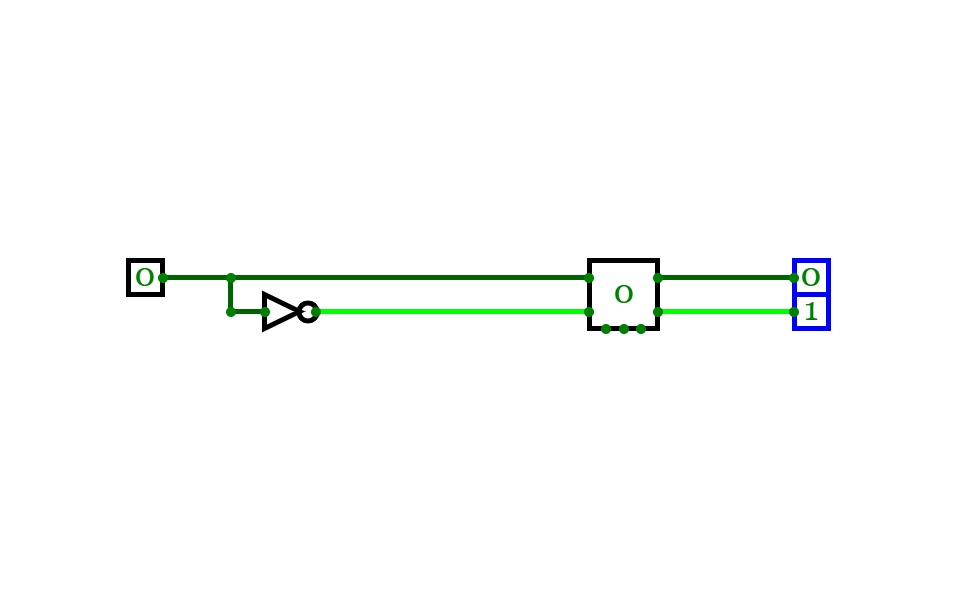

realisation of D-FF using JK-FF

realisation of D-FF using JK-FF

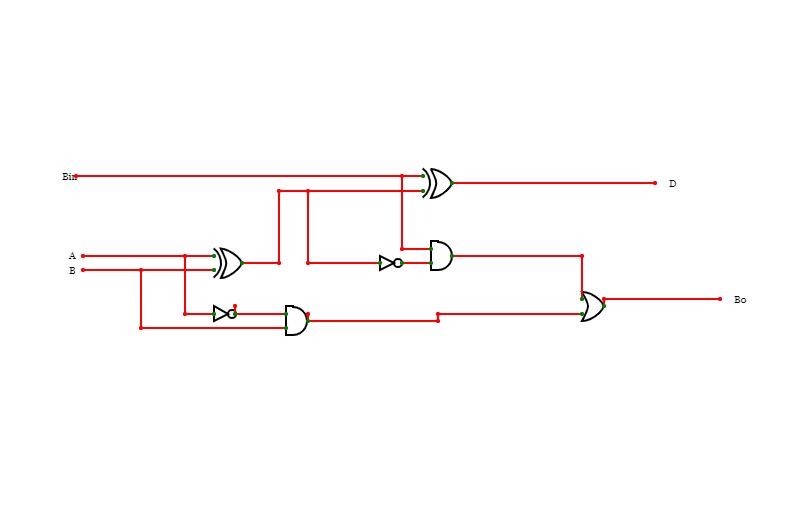

FULLSUBTRATOR using basic gates

FULLSUBTRATOR using basic gates

F(A,B,C,D)=Em(1,3,5,6,8,10,11,12,14)

F(A,B,C,D)=Em(1,3,5,6,8,10,11,12,14)

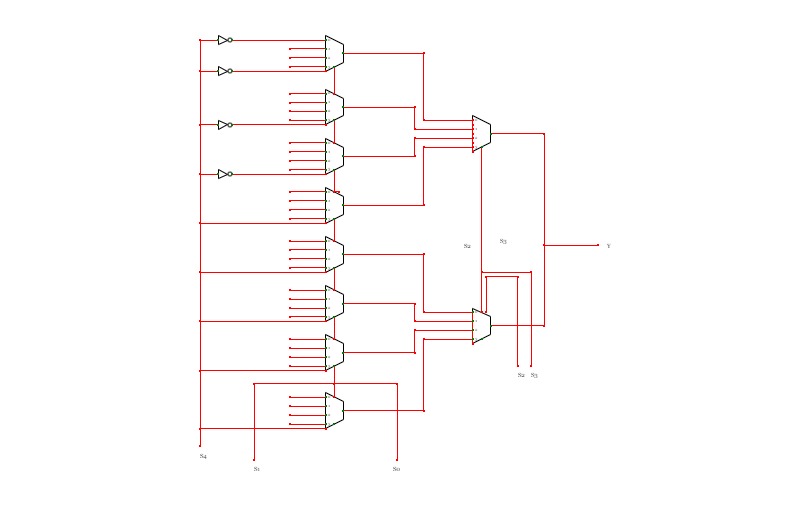

32 TO 1 USING 4 TO 1 MUX

32 TO 1 USING 4 TO 1 MUX

realisation of T-FF using SR-FF

realisation of T-FF using SR-FF

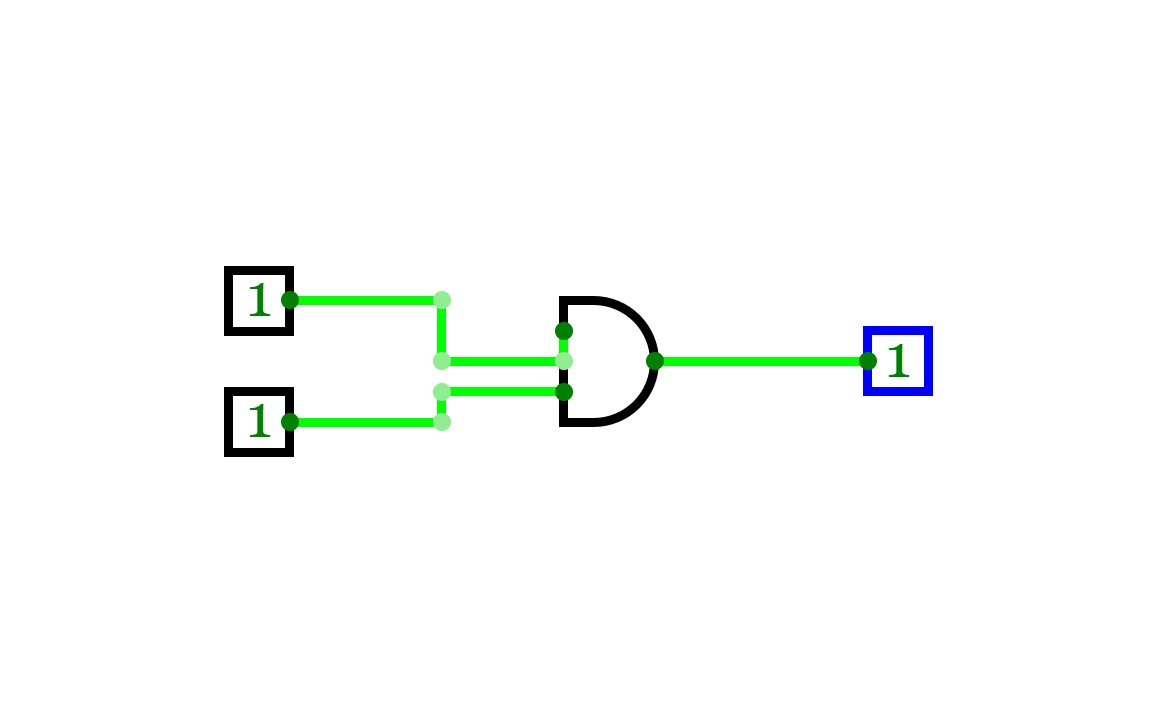

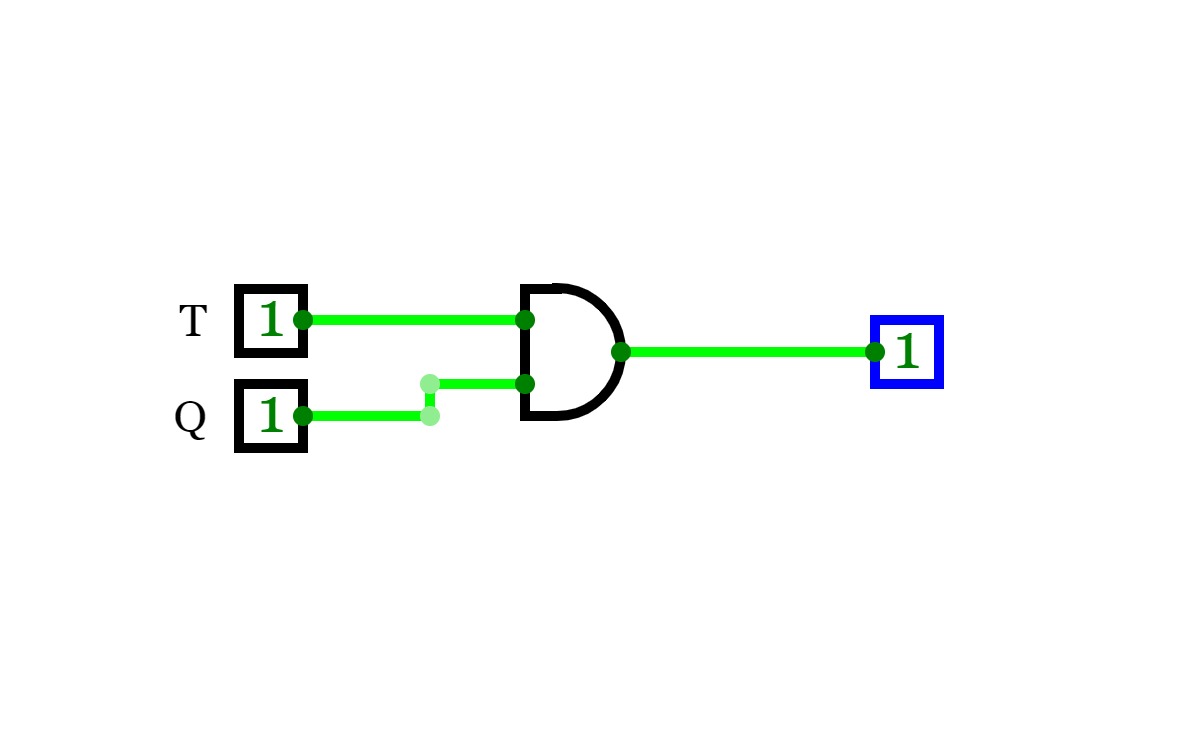

AND GATE

AND GATE

AND GATE

AND GATE

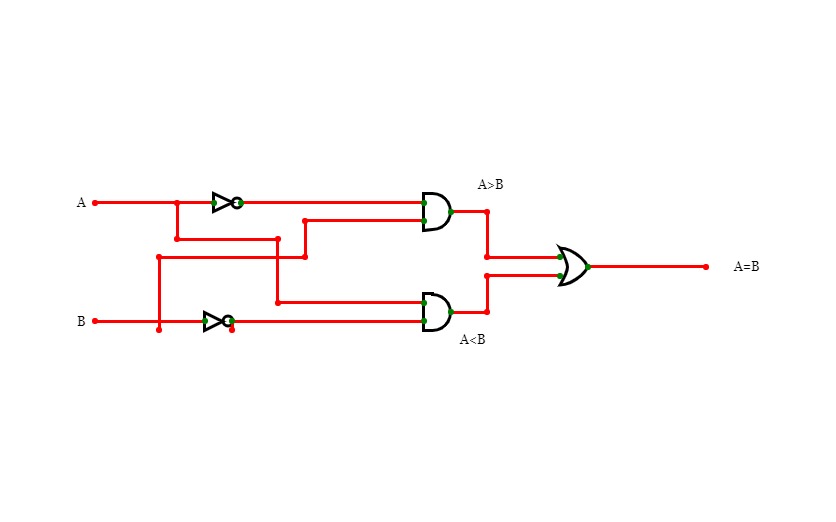

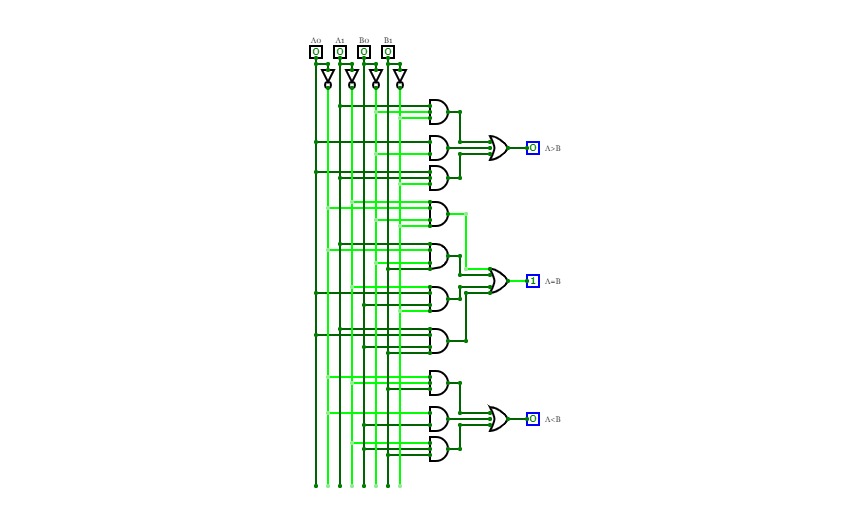

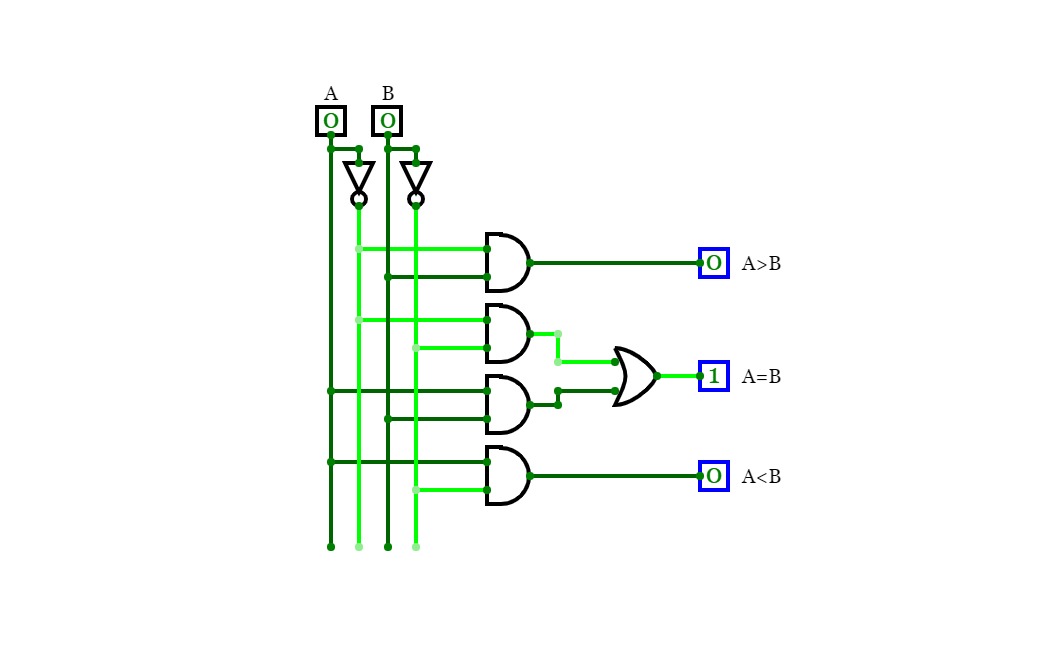

MAGNITUDE COMPARATOR AND PARITY CHECKER

MAGNITUDE COMPARATOR AND PARITY CHECKER

AND

AND

Untitled

Untitled

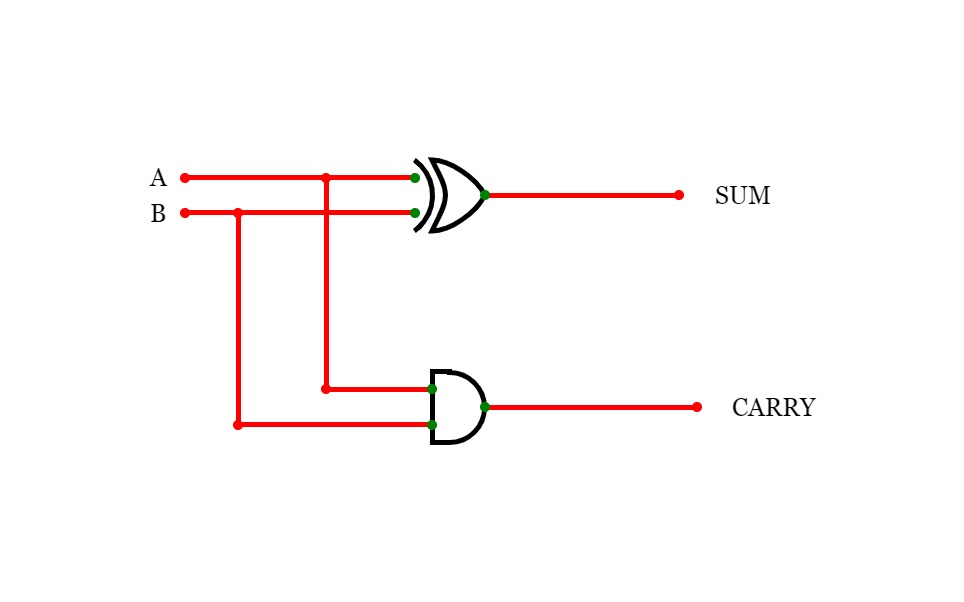

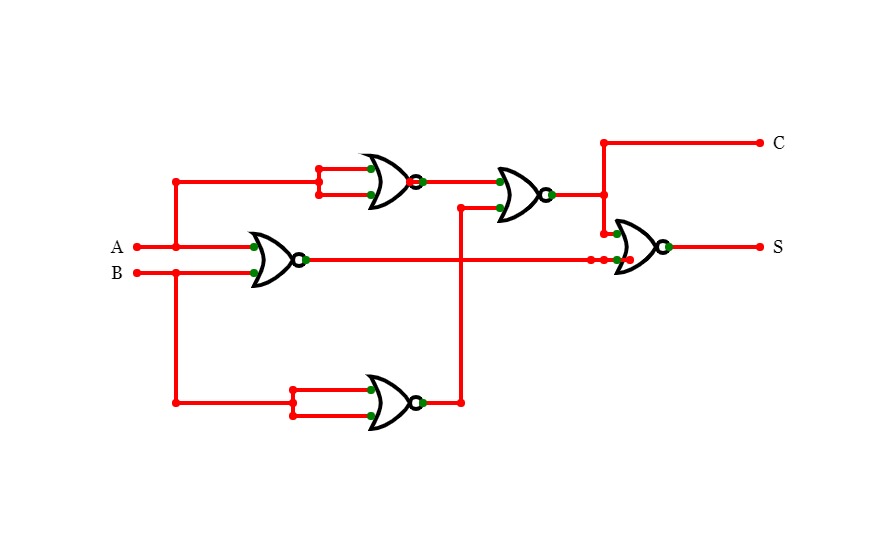

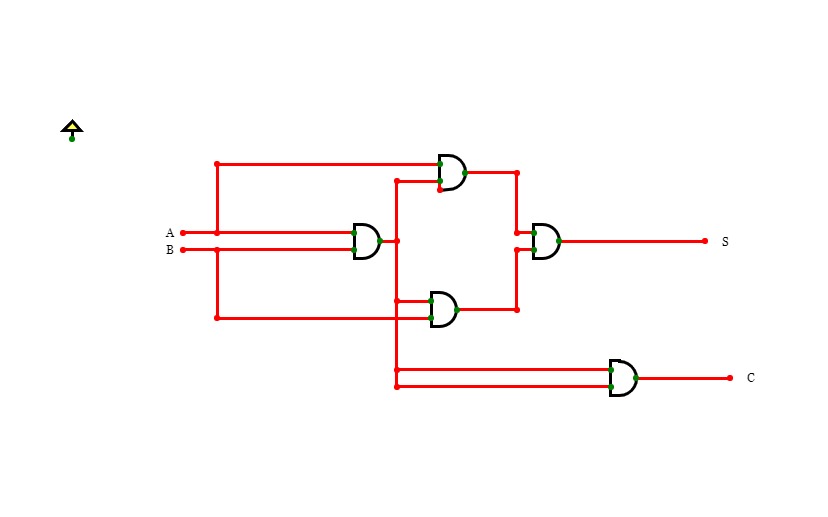

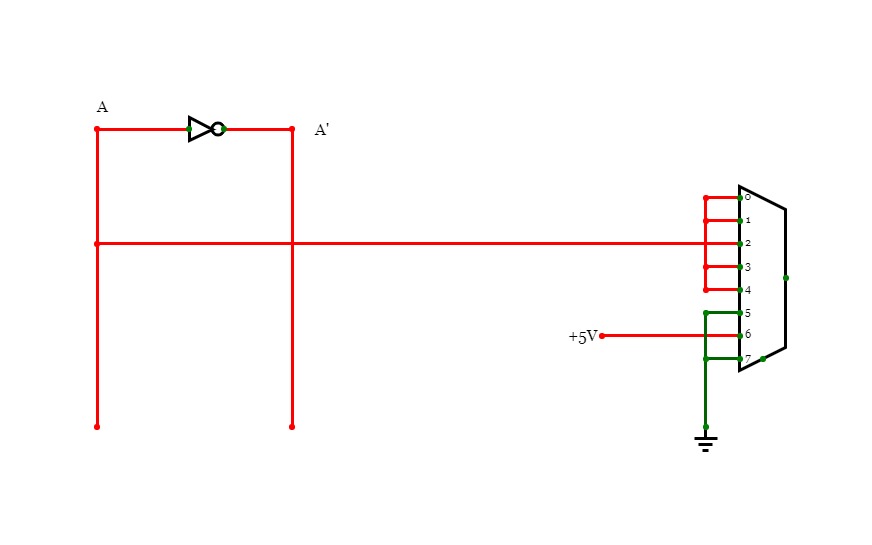

HALF ADDER using XOR gates

HALF ADDER using XOR gates

HALF SUBTRATOR using NOR gates

HALF SUBTRATOR using NOR gates

F(A,B,C,D)=Em(6,8,9,10,11,12,14)

F(A,B,C,D)=Em(6,8,9,10,11,12,14)

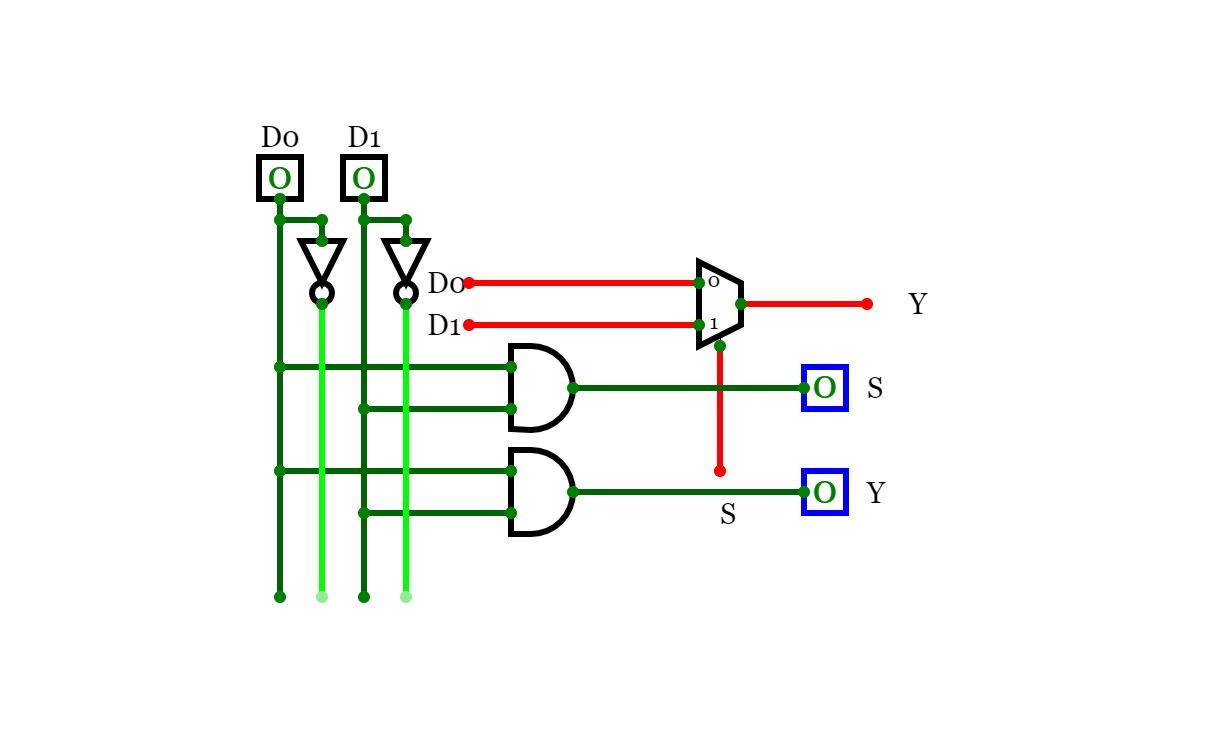

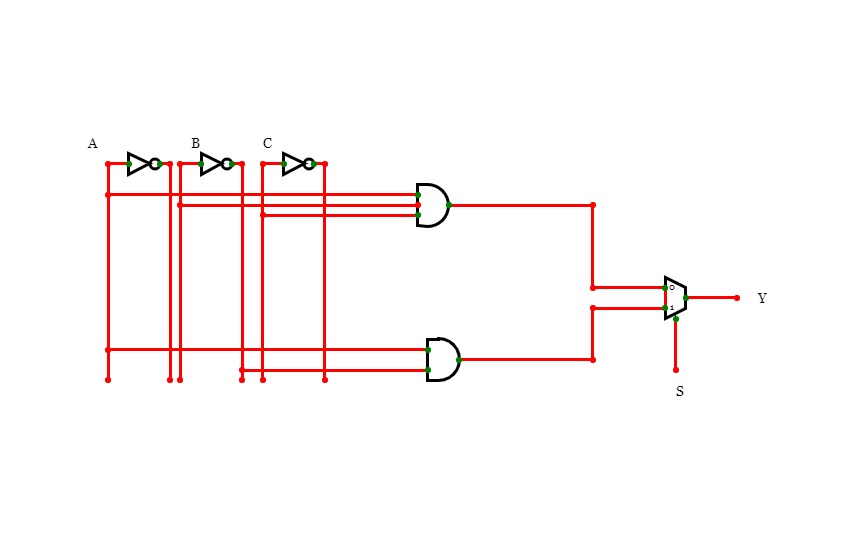

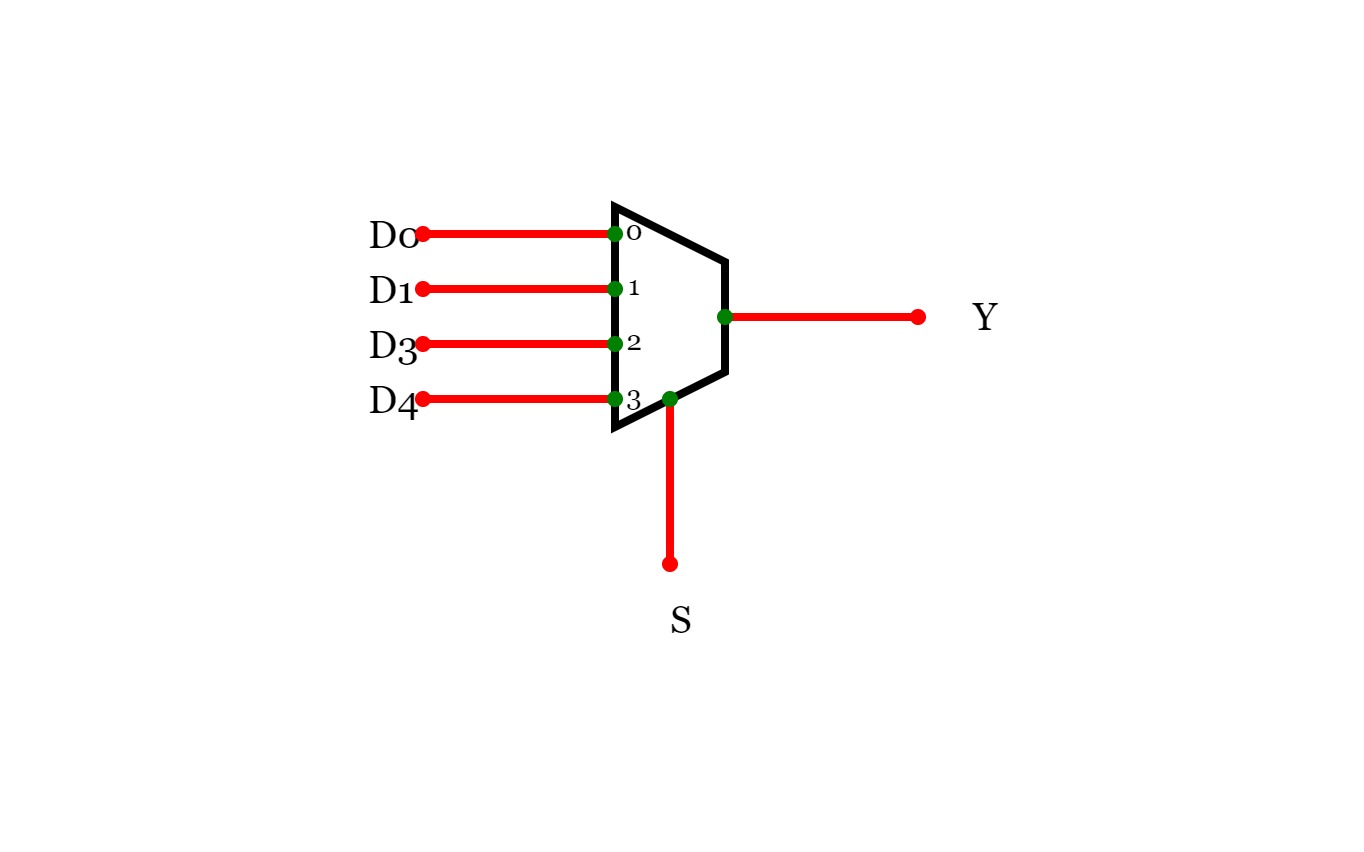

MUX AND DEMUX

MUX AND DEMUX

MUX AND DEMUX

MUX AND DEMUX

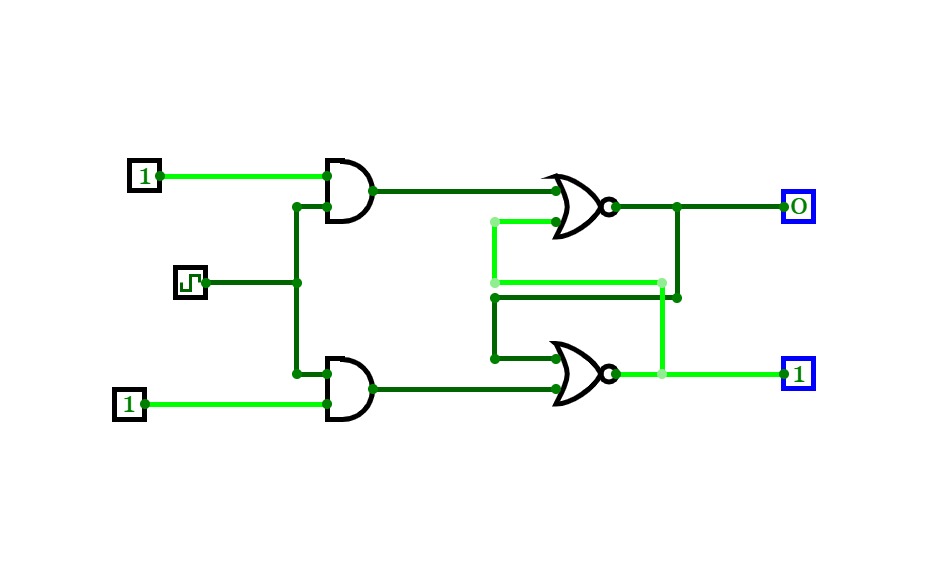

NAND based SR-FF

NAND based SR-FF

4 BIT EXESS TO BCD

4 BIT EXESS TO BCD

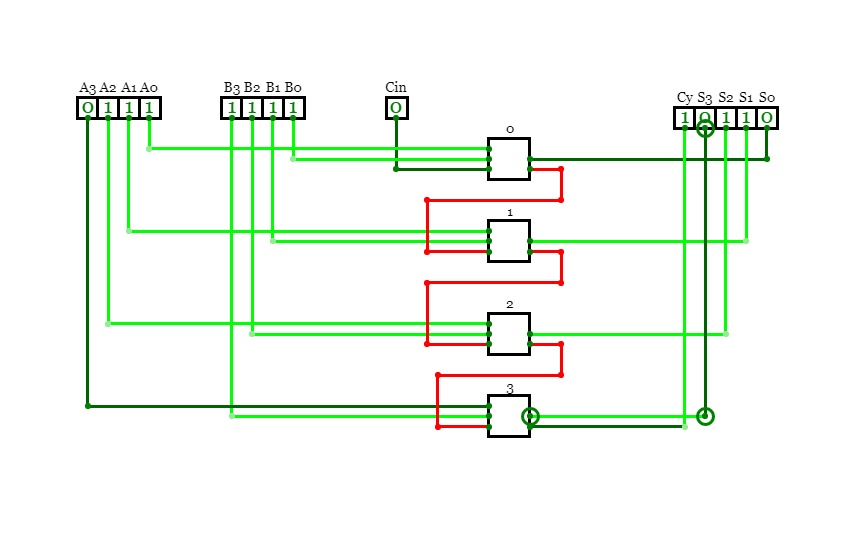

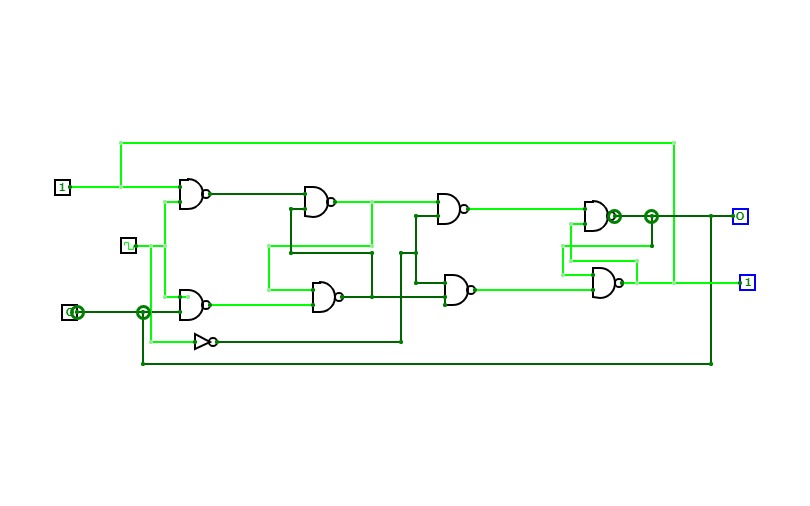

4 BIT RIPPLE CARRY ADDER

4 BIT RIPPLE CARRY ADDER

D-FF using NAND gate

D-FF using NAND gate

F(A,B,C,D)=Em(1,3,5,6,8,10,11,12,14)

F(A,B,C,D)=Em(1,3,5,6,8,10,11,12,14)

F(A,B,C,D)=Em(1,3,5,6,8,10,11,12,14)

F(A,B,C,D)=Em(1,3,5,6,8,10,11,12,14)

Toggle Flip Flop usinG NAND gate

Toggle Flip Flop usinG NAND gate

realisation ofJ-FF using SR-FF

realisation ofJ-FF using SR-FF

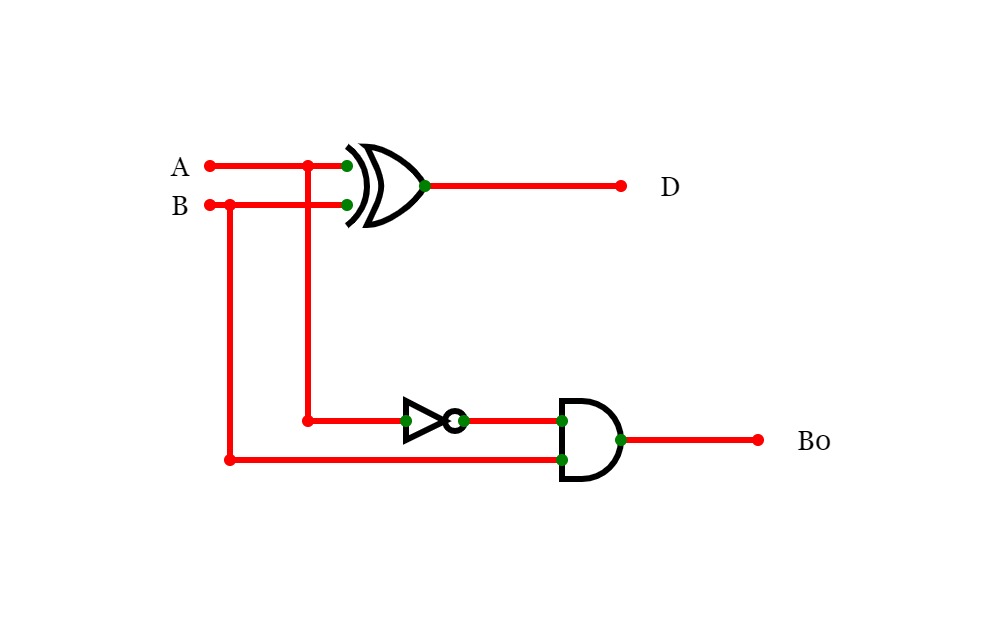

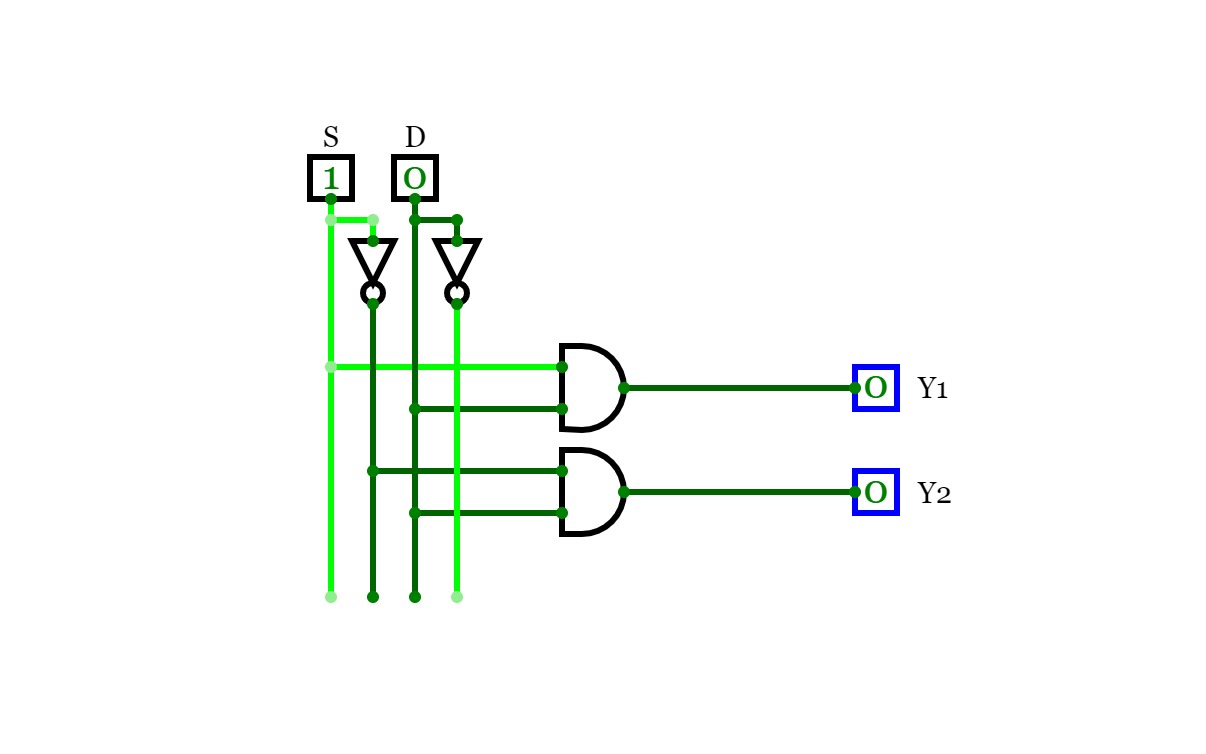

realisation of D-FF using SR-FF

realisation of D-FF using SR-FF

MUX AND DEMUX

MUX AND DEMUX

HALF SUBTRATOR using NAND gates only

HALF SUBTRATOR using NAND gates only

MUX AND DEMUX

MUX AND DEMUX

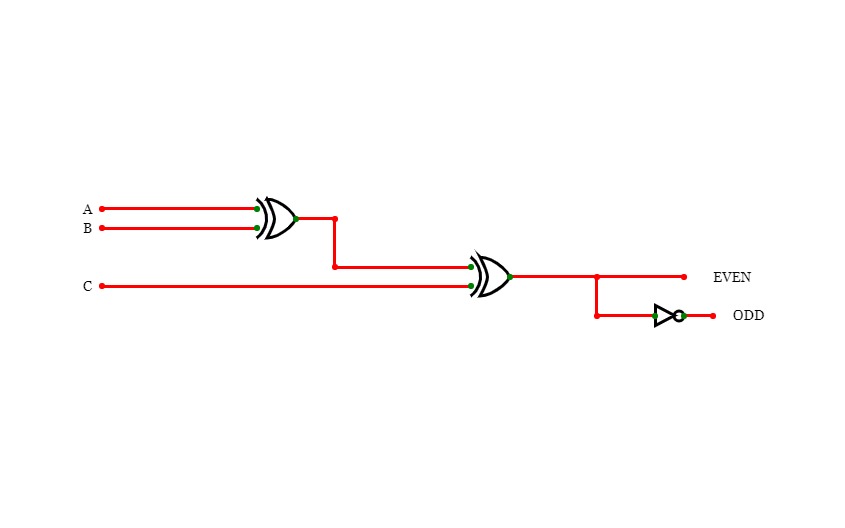

MAGNITUDE COMPARATOR AND PARITY CHECKER

MAGNITUDE COMPARATOR AND PARITY CHECKER

D-FF using NAND gate

D-FF using NAND gate

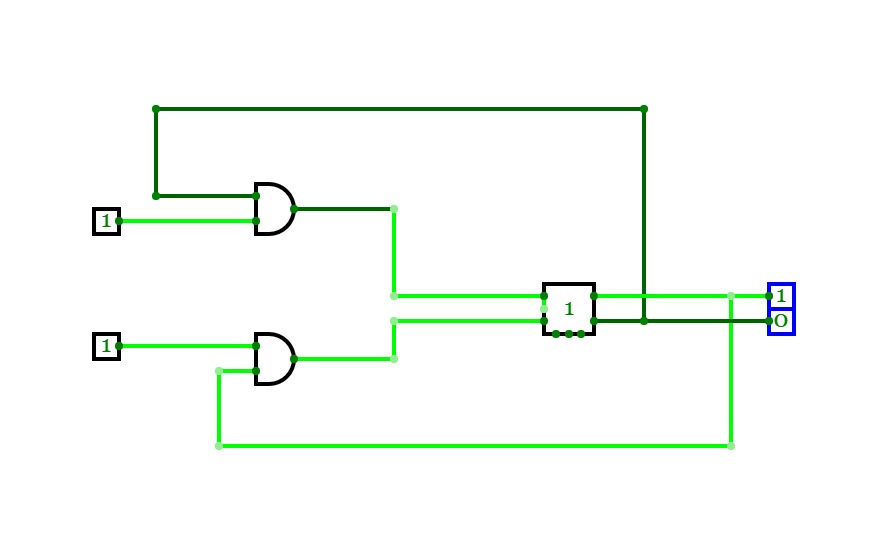

realisation of SR-FF using D-FF

realisation of SR-FF using D-FF

MAGNITUDE COMPARATOR AND PARITY CHECKER

MAGNITUDE COMPARATOR AND PARITY CHECKER

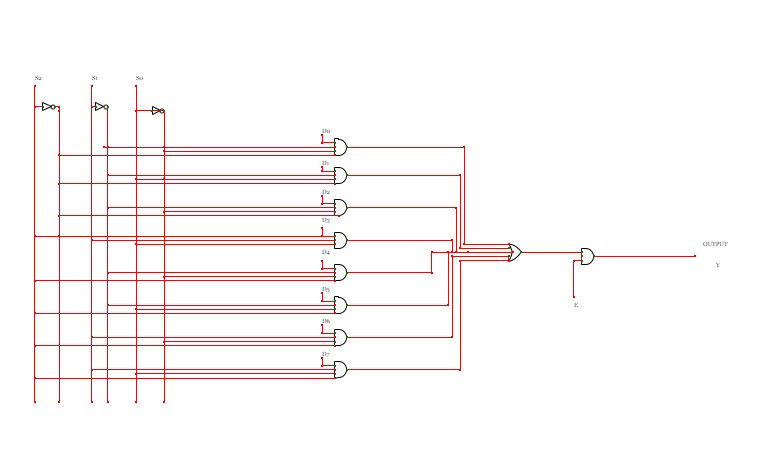

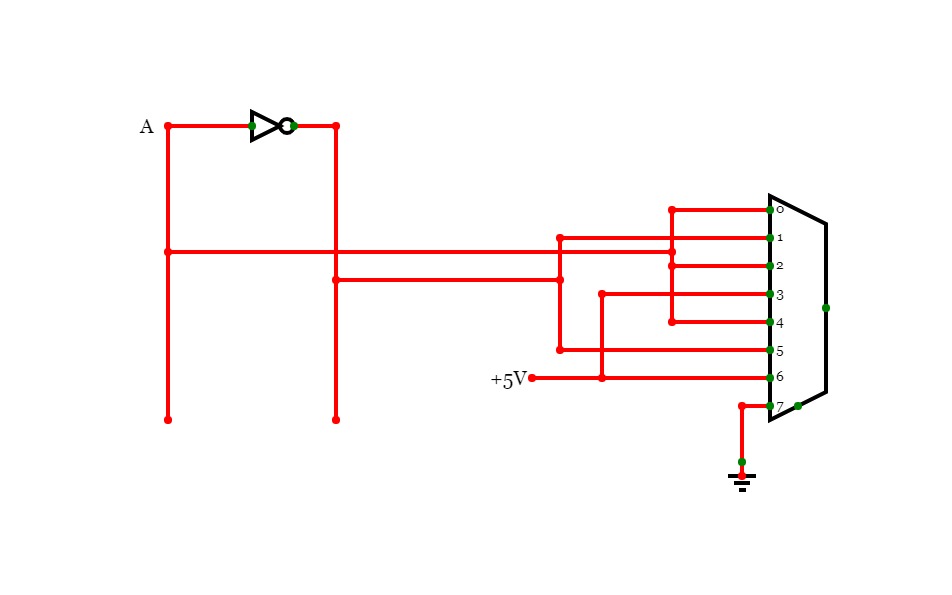

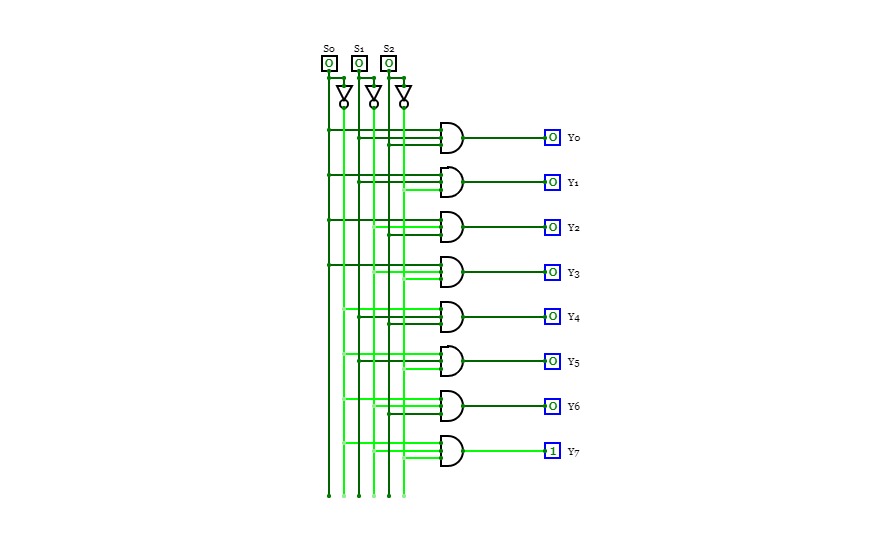

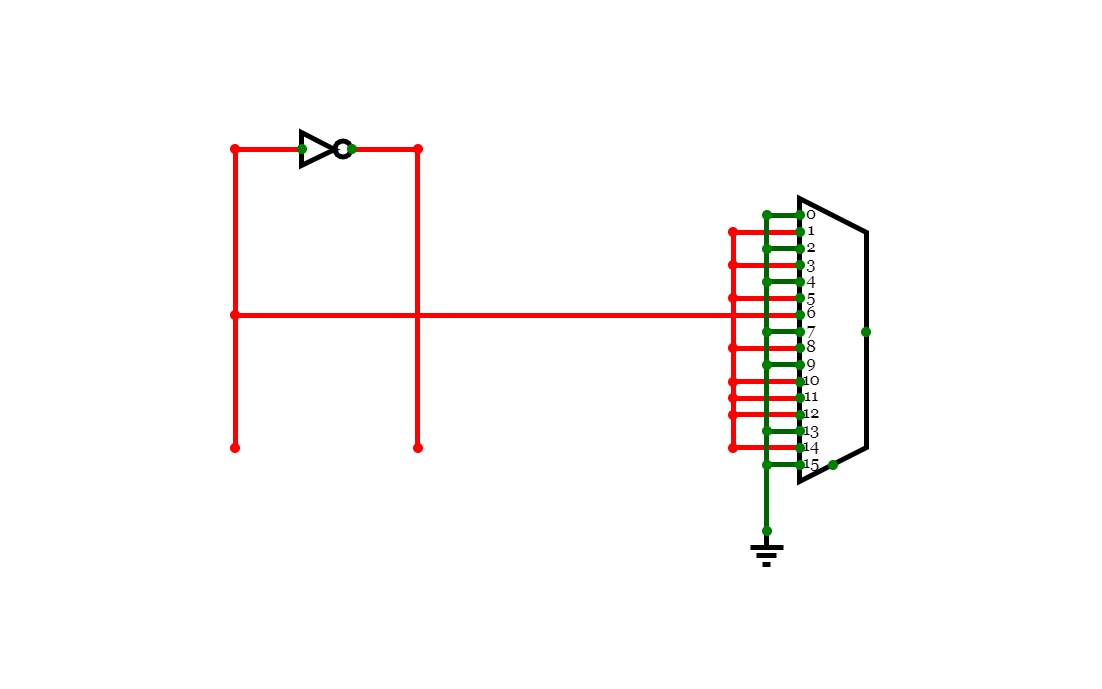

8 TO 1 DEMUX

8 TO 1 DEMUX

JK-FF using NAND gate

JK-FF using NAND gate

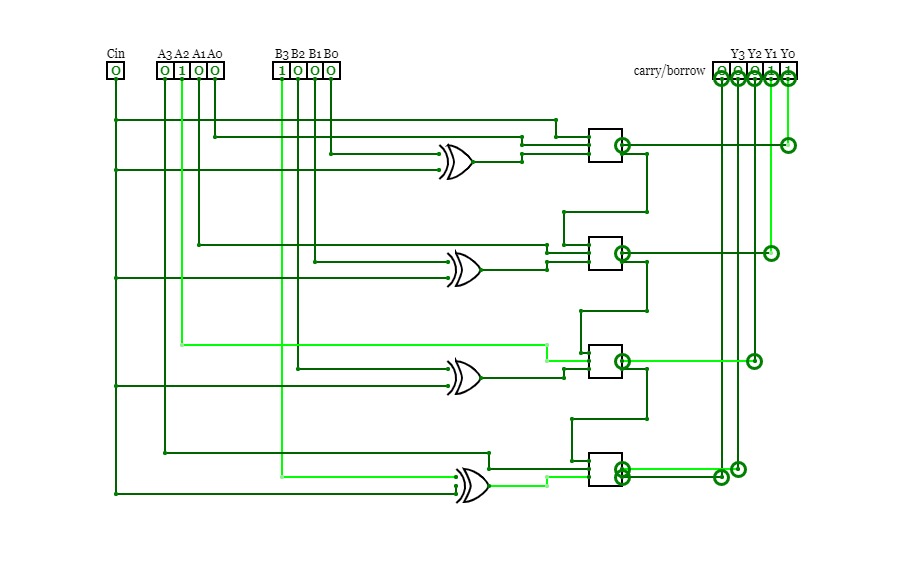

4 BIT ADDER/SUBTRACTOR

4 BIT ADDER/SUBTRACTOR

MAGNITUDE COMPARATOR AND PARITY CHECKER

MAGNITUDE COMPARATOR AND PARITY CHECKER

4 BIT RIPPLE CAFRY SUBTRACTOR

4 BIT RIPPLE CAFRY SUBTRACTOR

MAGNITUDE COMPARATOR AND PARITY CHECKER

MAGNITUDE COMPARATOR AND PARITY CHECKER

HALF ADDER using NOR gates

HALF ADDER using NOR gates

BCD AADER

BCD AADER

FULLSUBTRATROR using XOR gates

FULLSUBTRATROR using XOR gates

NOR -based SR-FF

NOR -based SR-FF

4 BIT BCD TO EXCESS 3

4 BIT BCD TO EXCESS 3

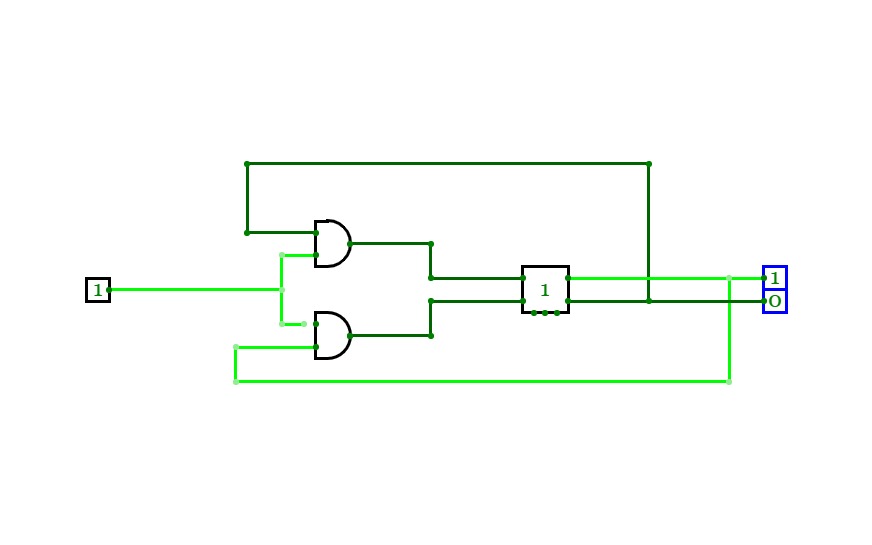

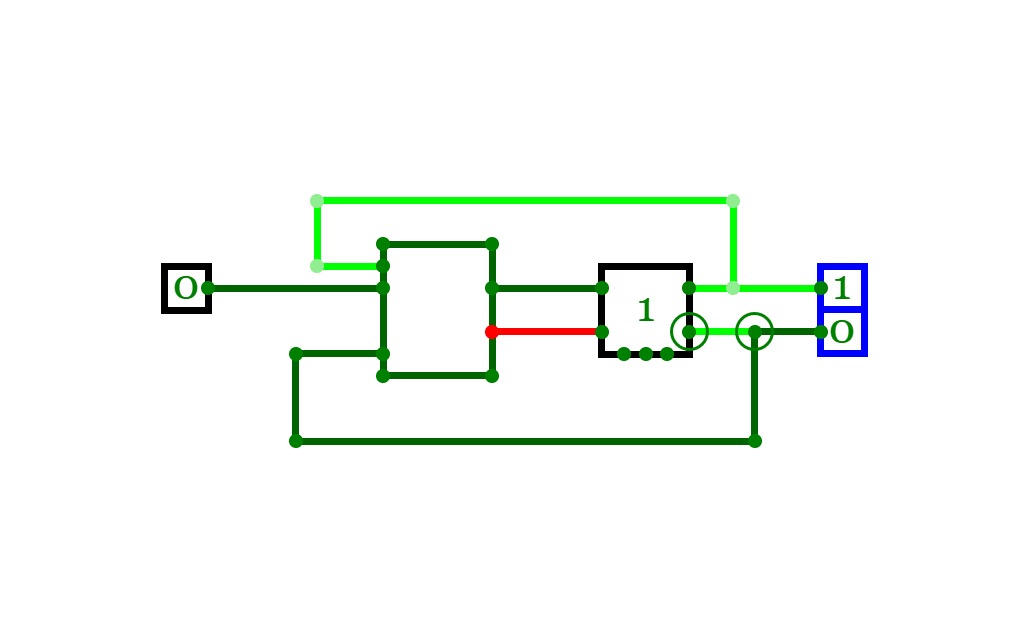

realisation of T-FF using D-FF

realisation of T-FF using D-FF

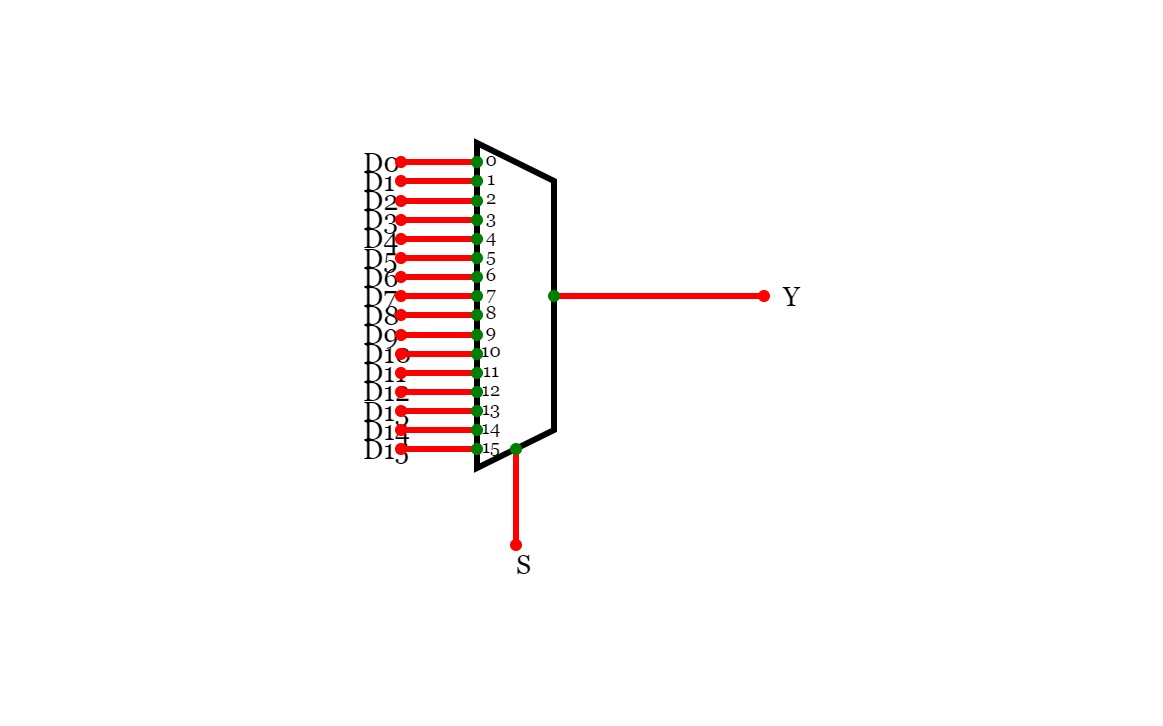

MUX AND DEMUX

MUX AND DEMUX

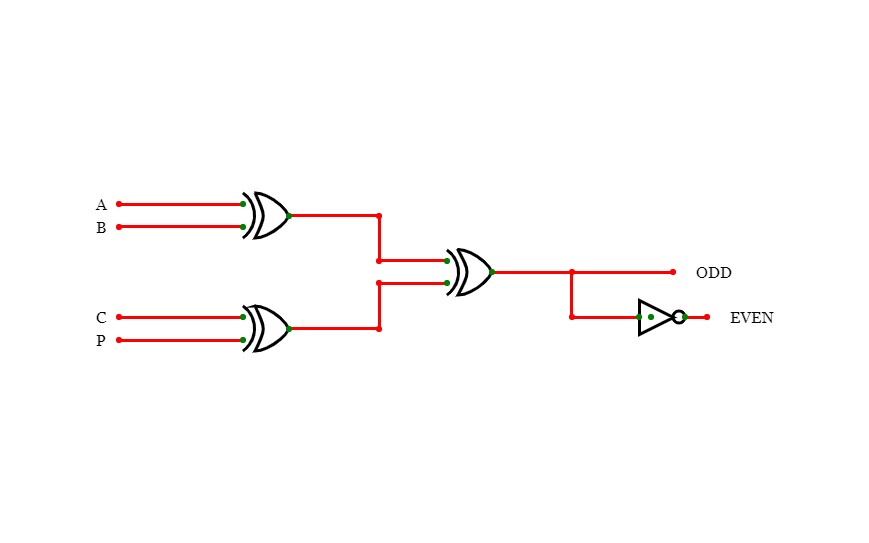

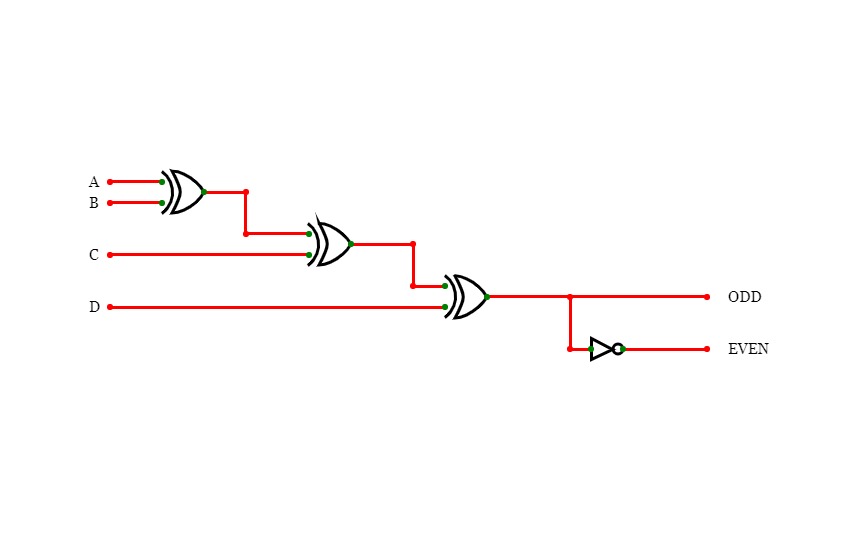

MAGNITUDE COMPARATOR AND PARITY CHECKER

MAGNITUDE COMPARATOR AND PARITY CHECKER

realisation of D-FF using SR-FF

realisation of D-FF using SR-FF

F(A,B,C,D)=Em(6,8,9,10,11,12,14)

F(A,B,C,D)=Em(6,8,9,10,11,12,14)

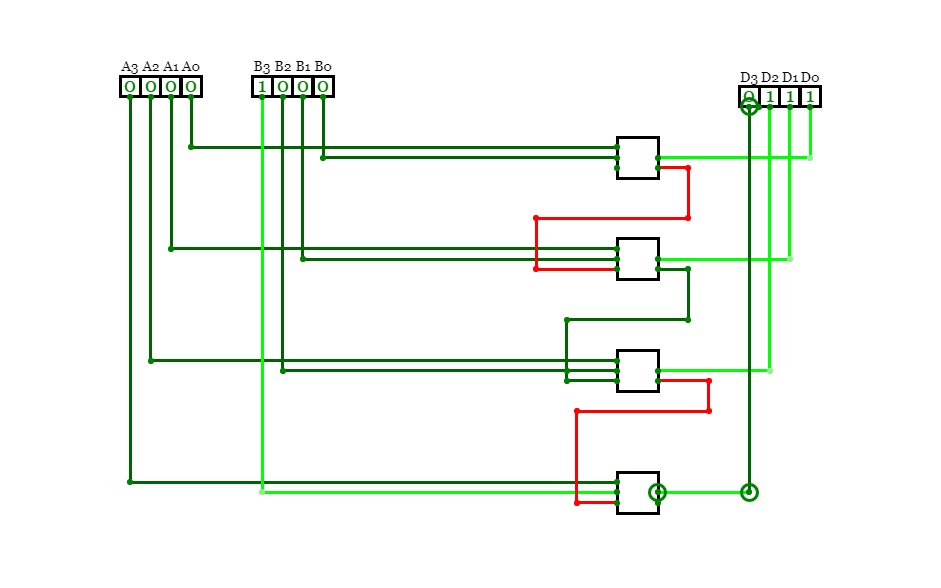

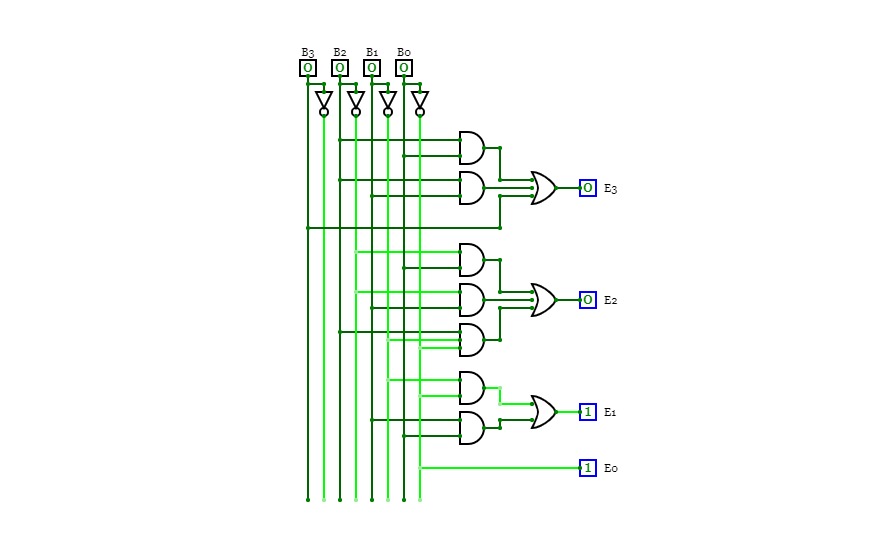

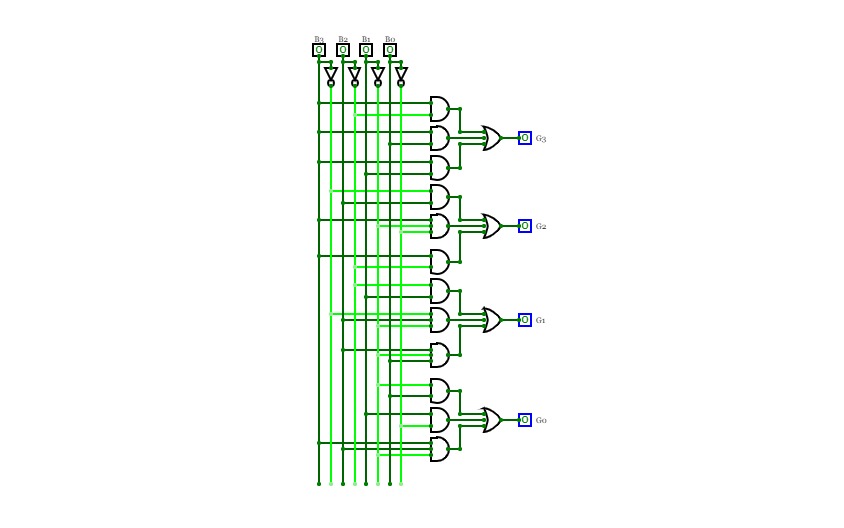

4 BIT BINARY TO GRAY

4 BIT BINARY TO GRAY

FULL SUBTRACTOR USING NAND GATES

FULL SUBTRACTOR USING NAND GATES

MUX AND DEMUX

MUX AND DEMUX

F(A,B,C,D)=Em(1,3,5,6,8,10,11,12,14)

F(A,B,C,D)=Em(1,3,5,6,8,10,11,12,14)

F(A,B,C,D)=Em(6,8,9,10,11,12,14)

F(A,B,C,D)=Em(6,8,9,10,11,12,14)

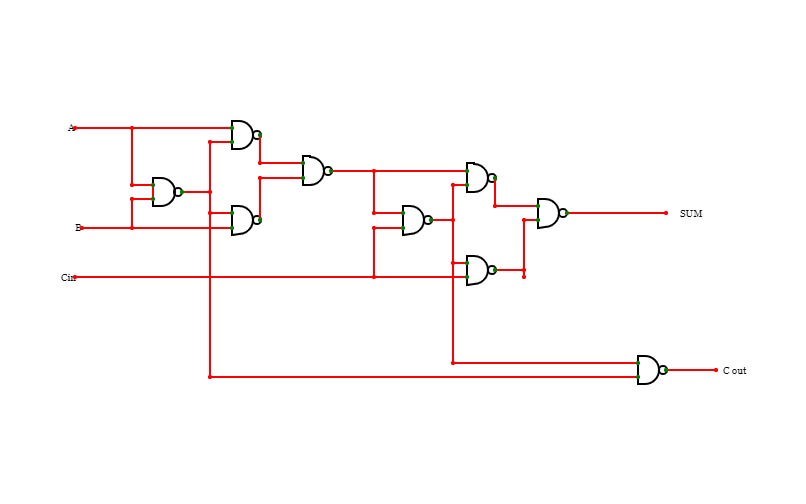

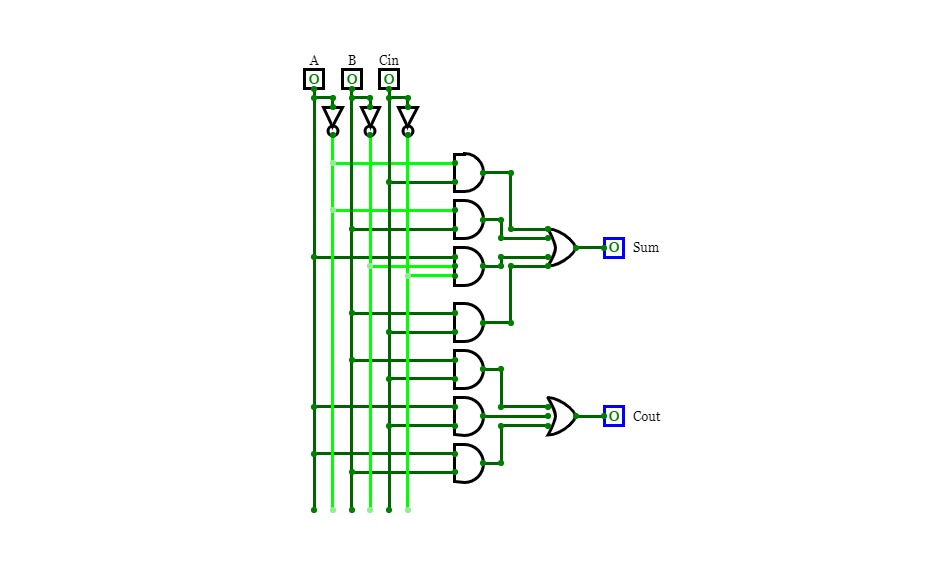

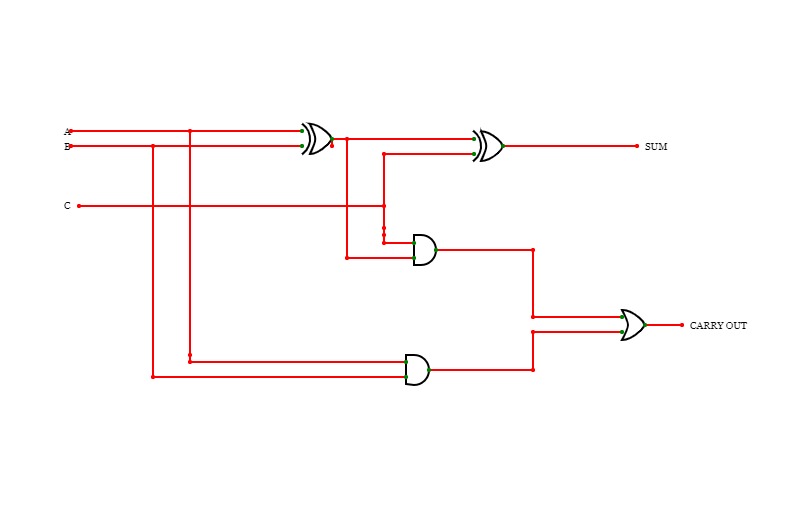

full adder using basic gates

full adder using basic gates

HALF ADDER using NAND logic

HALF ADDER using NAND logic

MASTER SLAVE -FF using NAND gate

MASTER SLAVE -FF using NAND gate

MUX AND DEMUX

MUX AND DEMUX

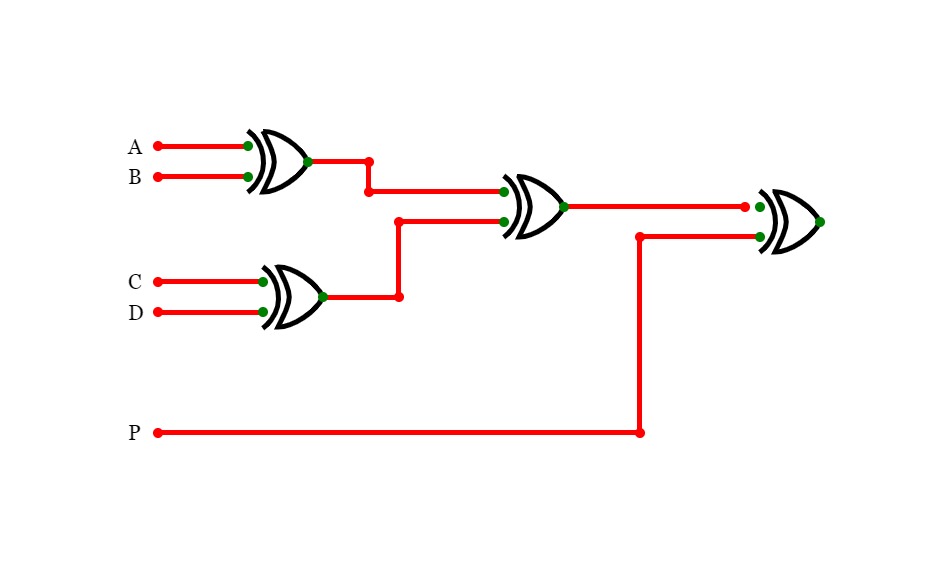

MAGNITUDE COMPARATOR AND PARITY CHECKER

MAGNITUDE COMPARATOR AND PARITY CHECKER

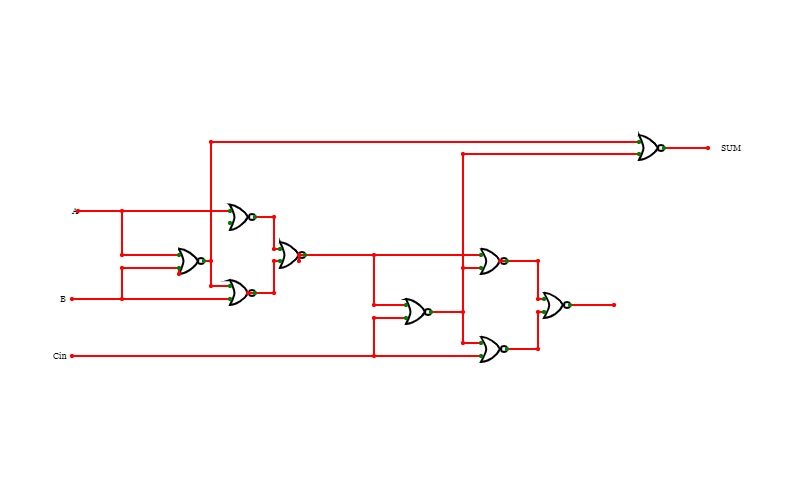

FULLADDER using XOR

FULLADDER using XOR

F(A,B,C,D)=Em(6,8,9,10,11,12,14)

F(A,B,C,D)=Em(6,8,9,10,11,12,14)

Full adder using NAND gates

Full adder using NAND gates