Rupashi

Member since: 4 years

Educational Institution: University of Enginnering and Management, Kolkata

Country: India

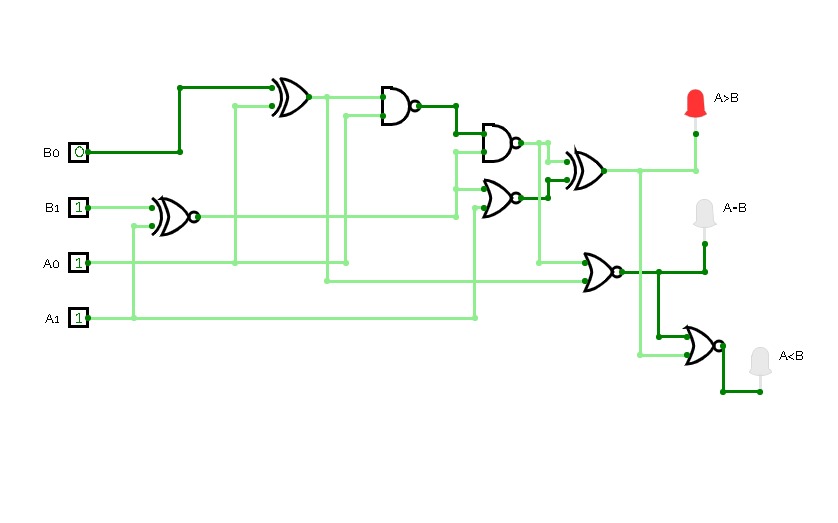

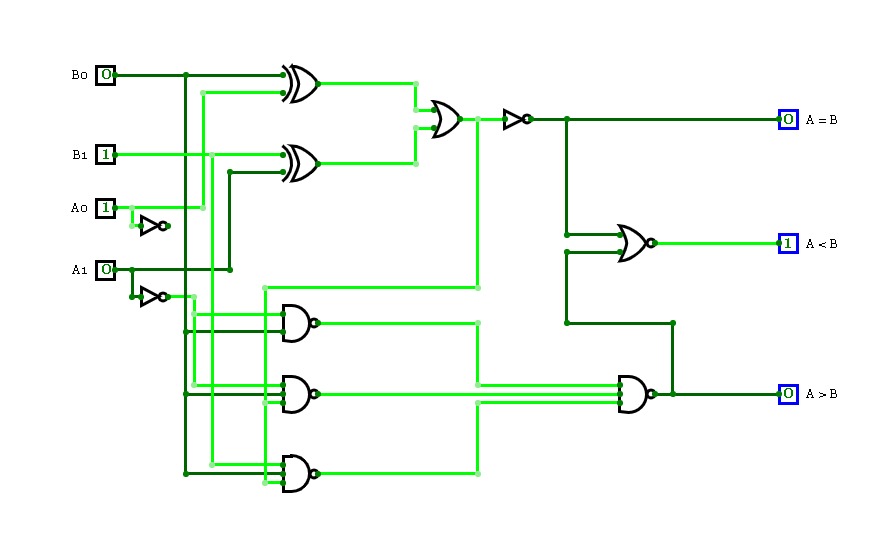

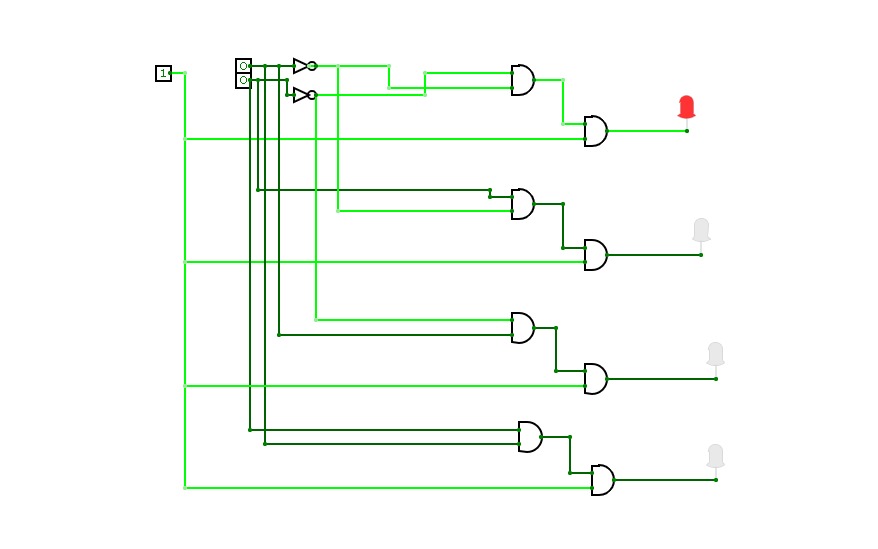

2-bit comparator

2-bit comparator

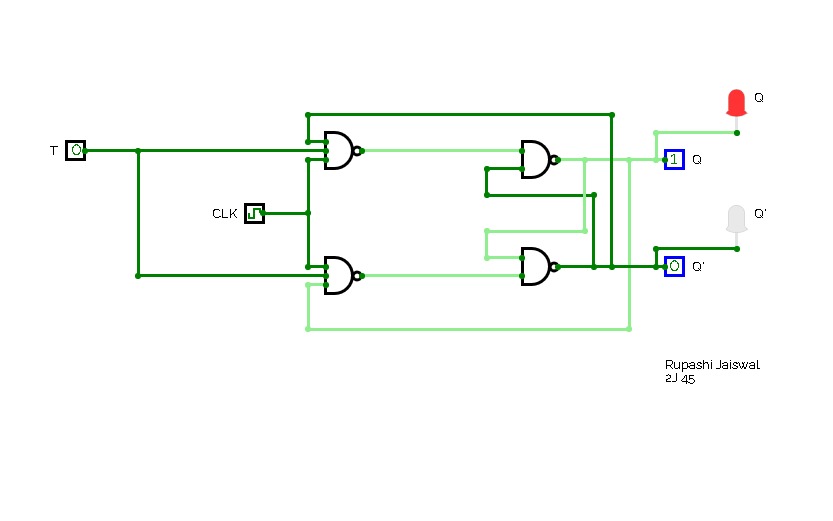

T Flip-Flop

T Flip-Flop

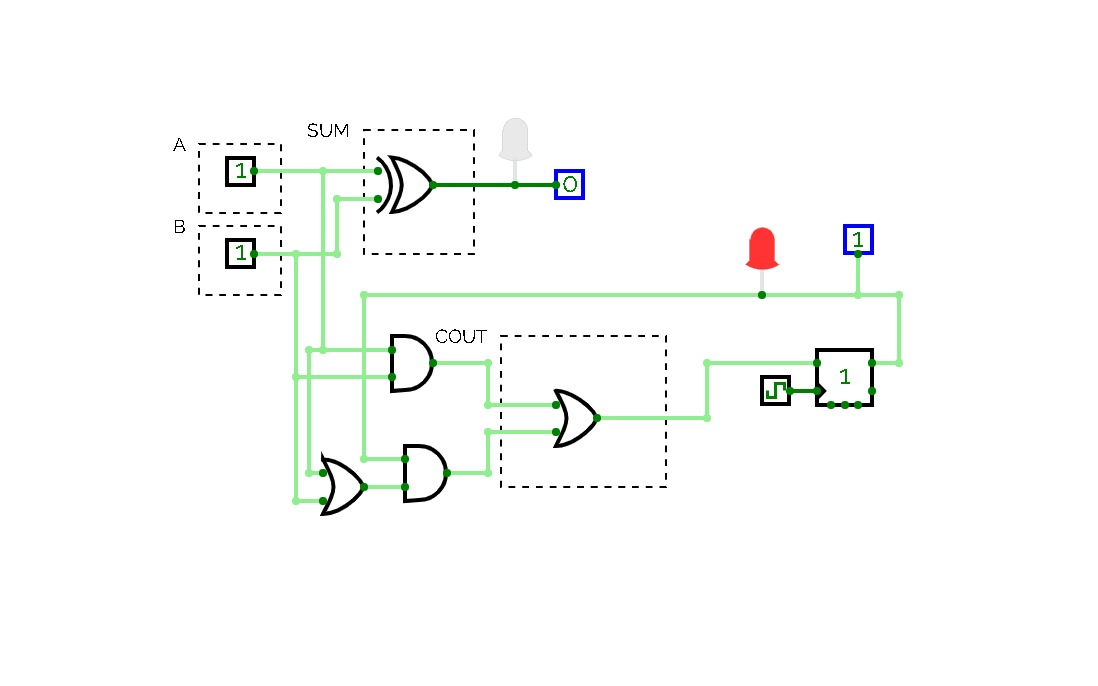

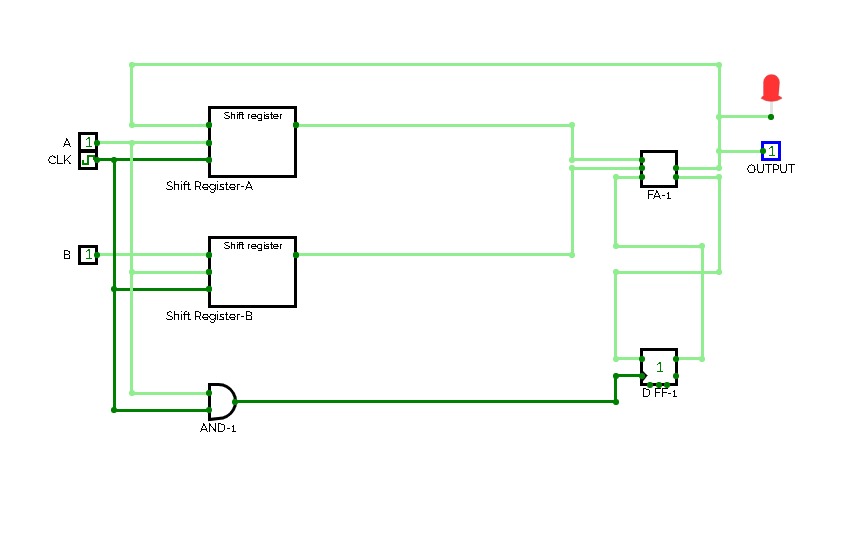

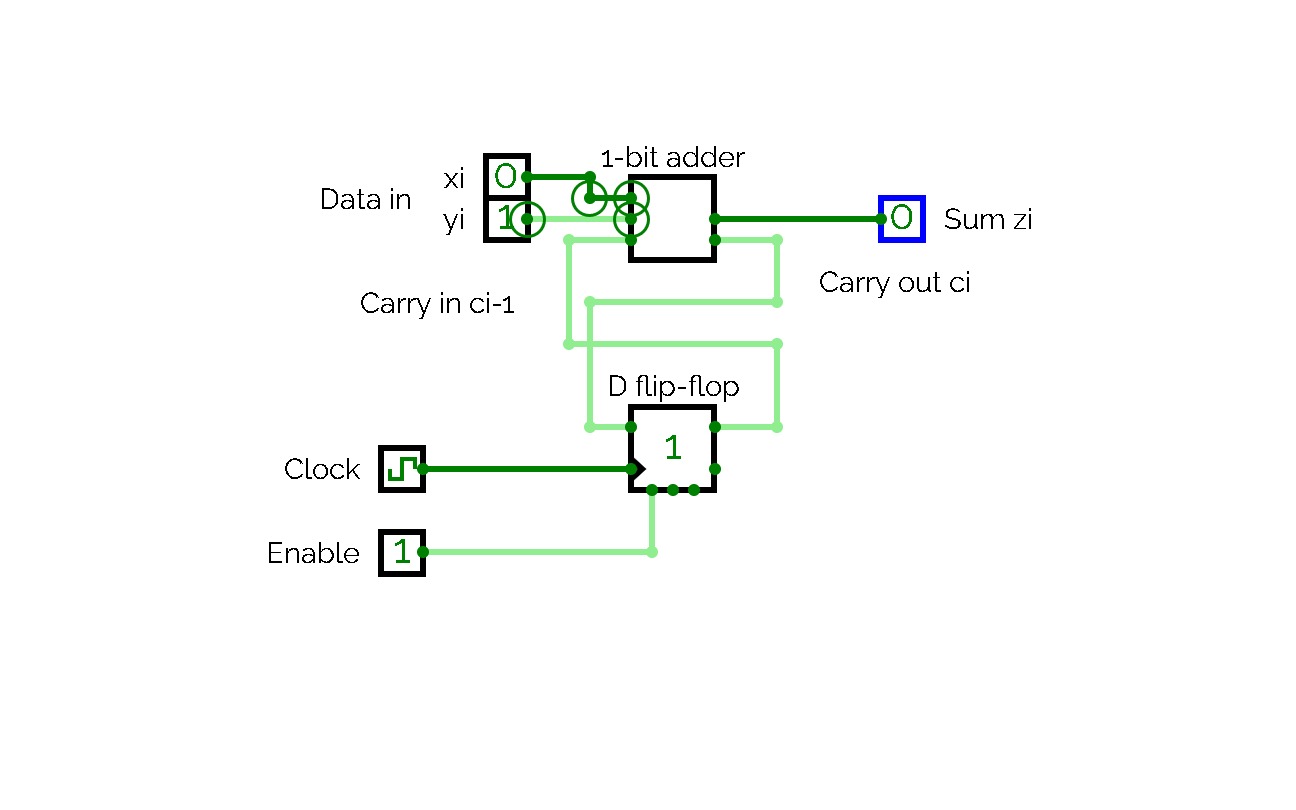

1-bit Serial Adder

1-bit Serial Adder

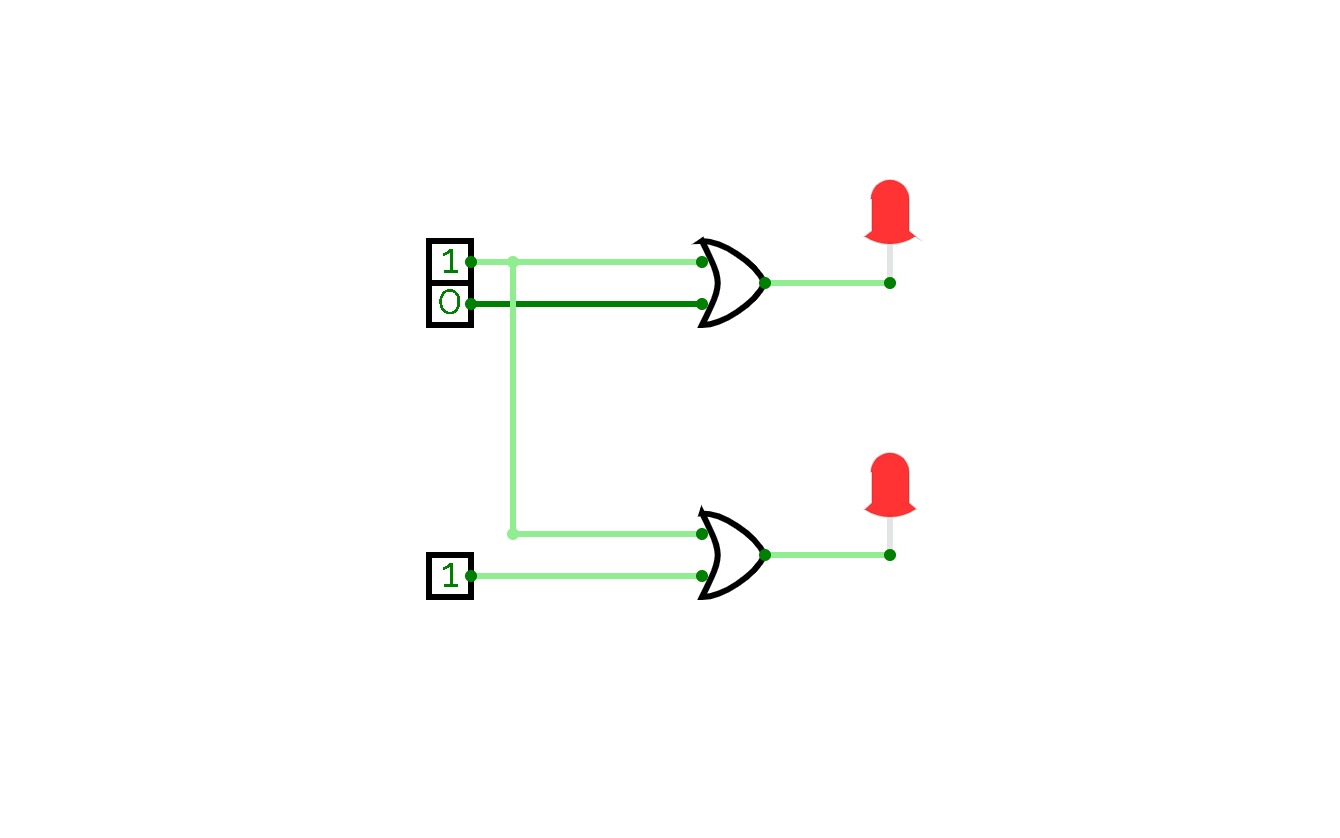

4:2 Encoder

4:2 Encoder

4-bit Serial Adder

4-bit Serial Adder

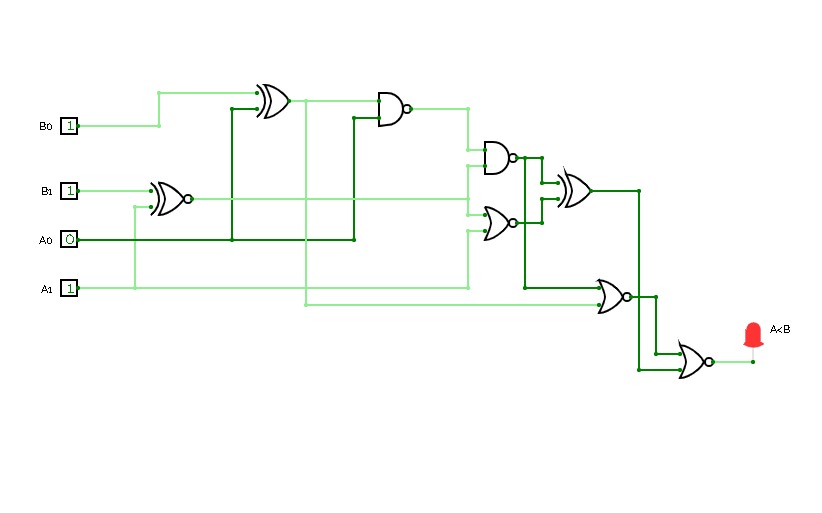

2-Bit comparator(less than operation)

2-Bit comparator(less than operation)

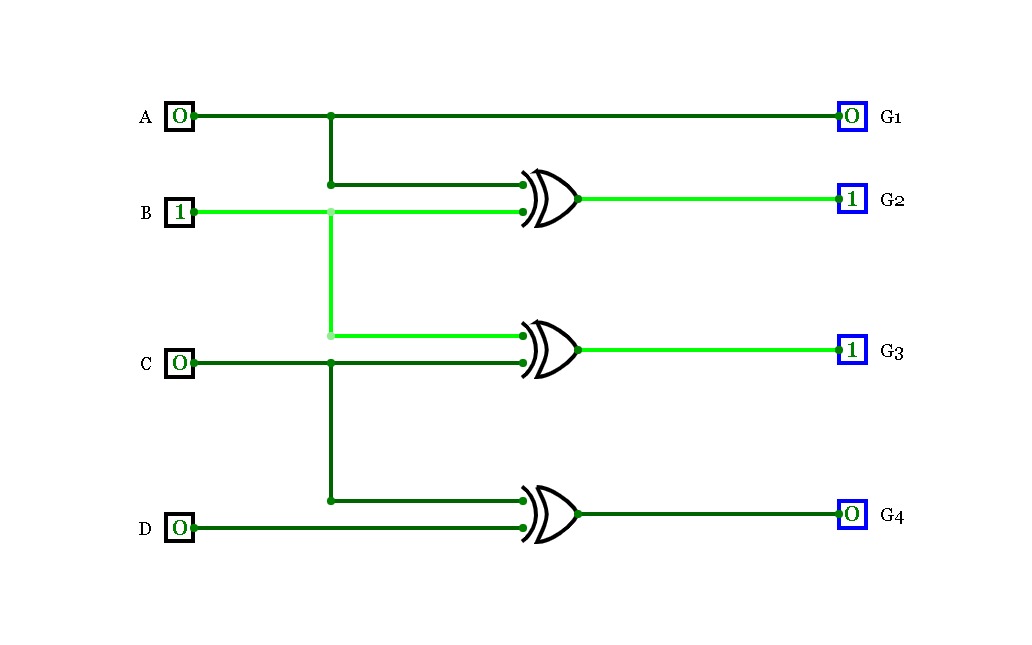

4bit Binary to 4bit Gray Code

4bit Binary to 4bit Gray Code

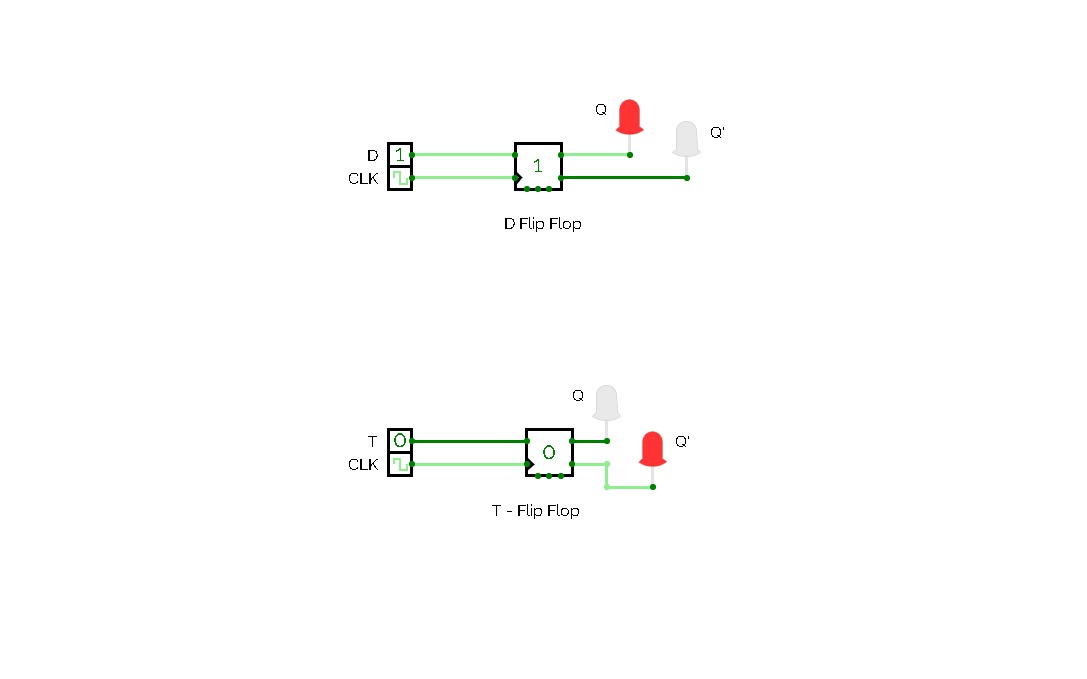

D flip flop and T flip flop

D flip flop and T flip flop

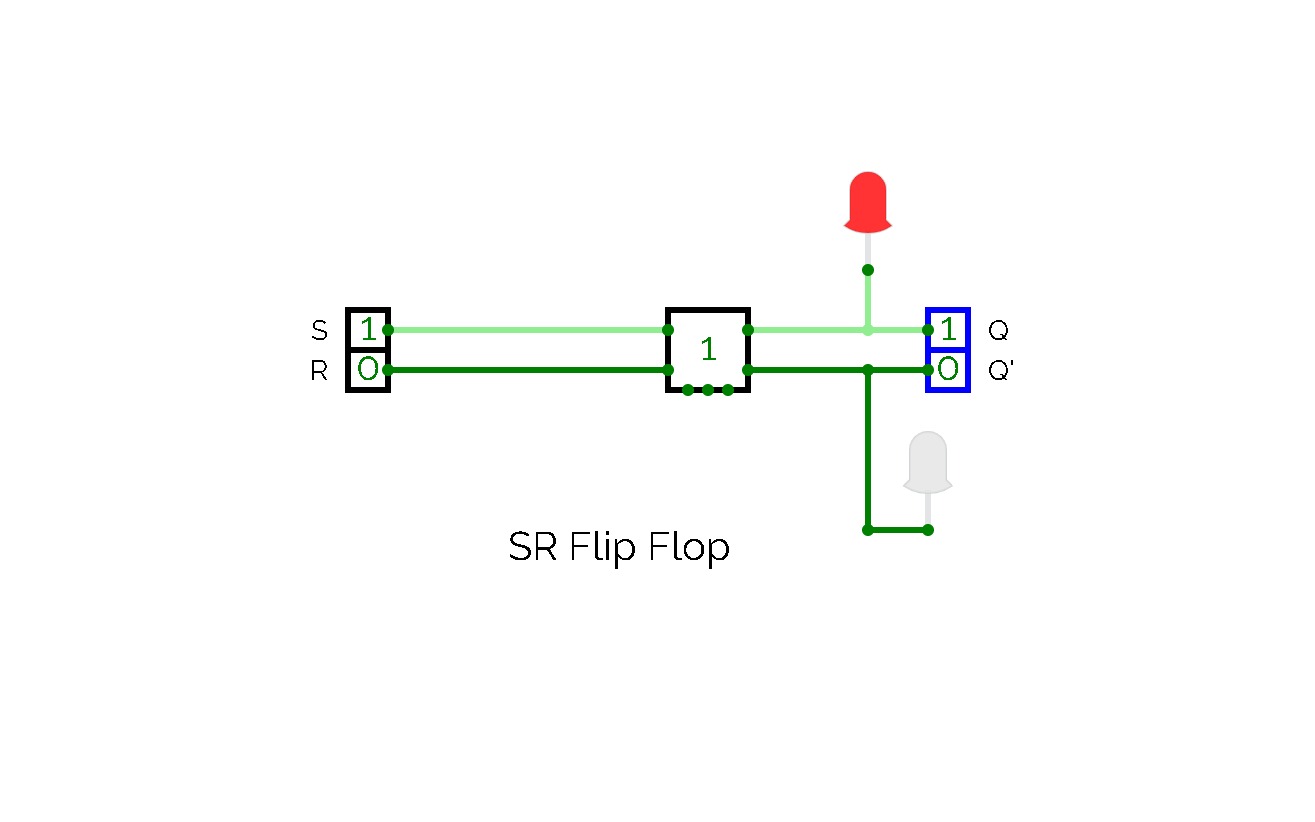

SR Flip Flop

SR Flip Flop

2 bit Comparator

2 bit Comparator

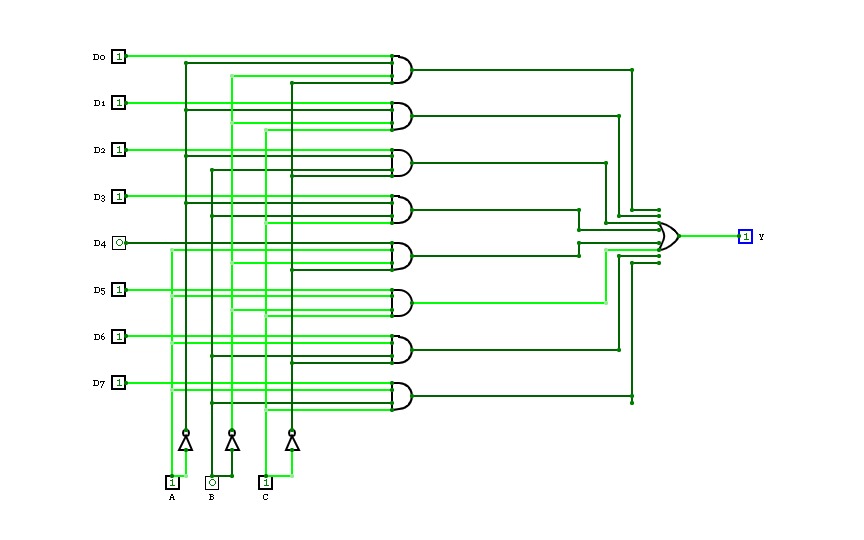

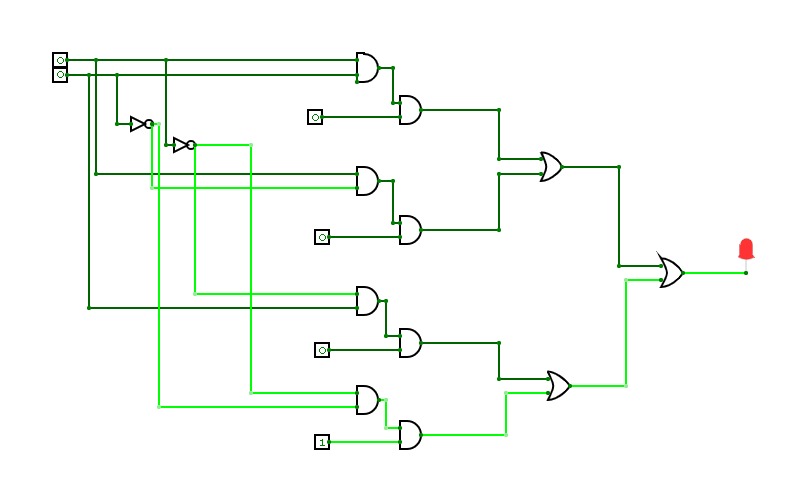

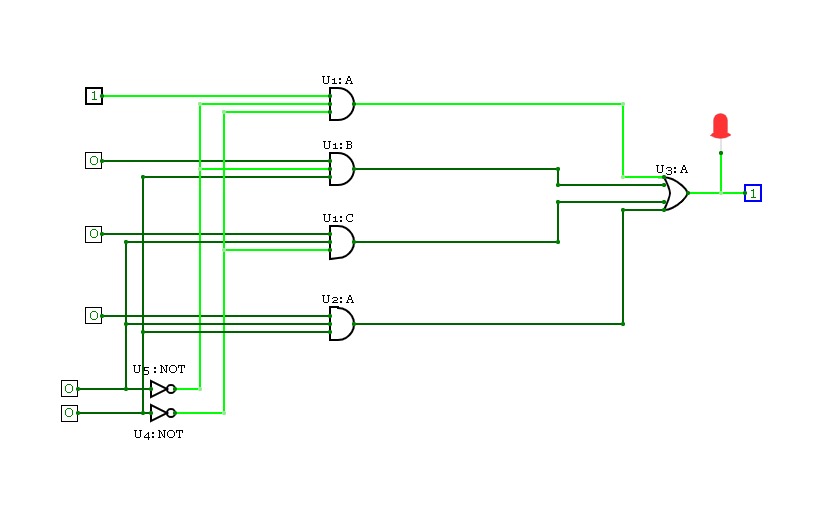

8:1 MUX using Logic Gates

8:1 MUX using Logic Gates

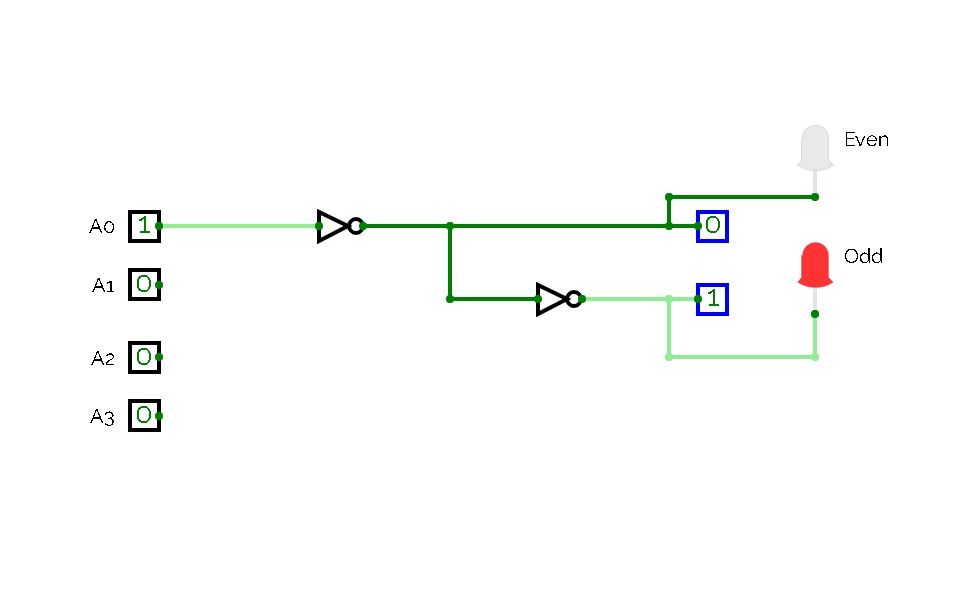

4-bit Odd/Even

4-bit Odd/Even

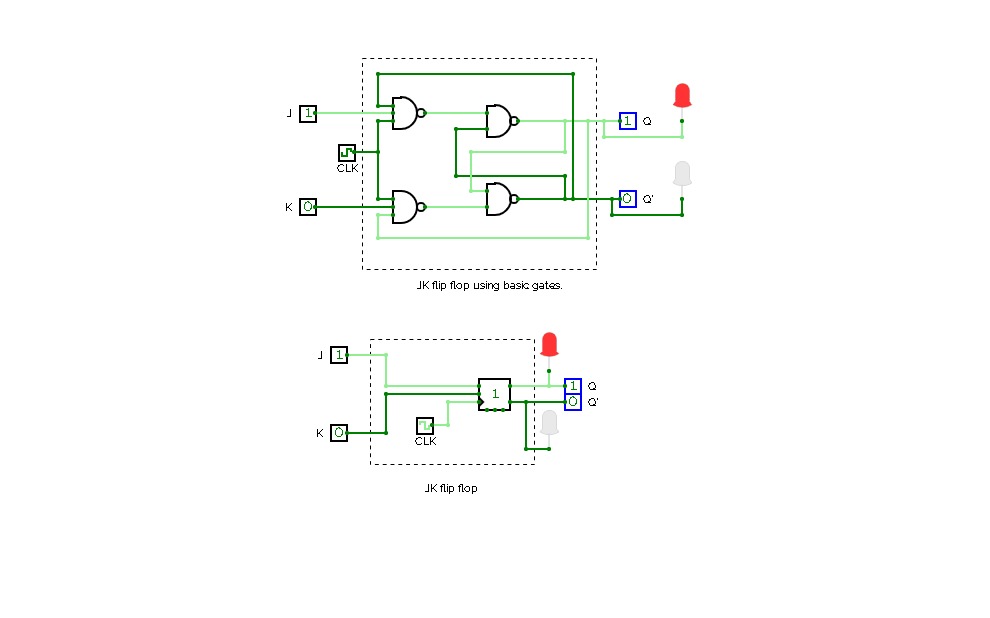

JK Flip Flop

JK Flip Flop

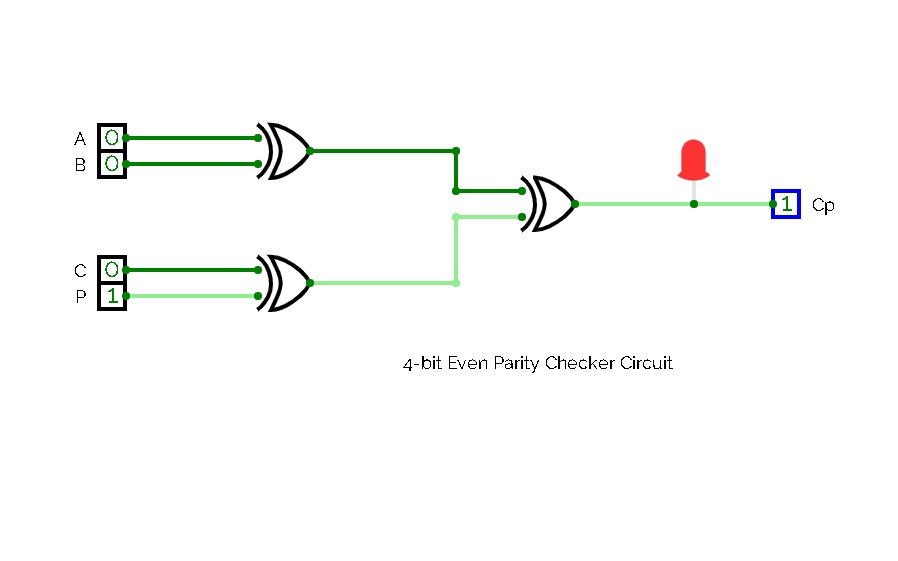

4 bit Even Parity Checker circuit

4 bit Even Parity Checker circuit

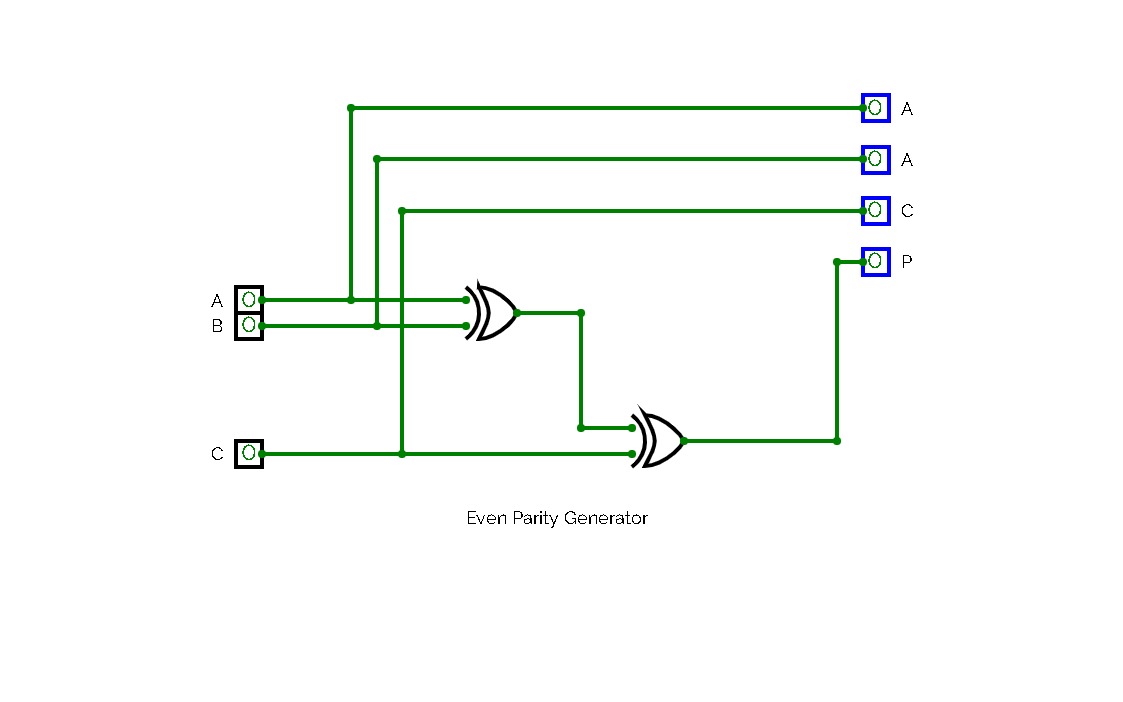

Even parity generator

Even parity generator

4*1 MUX

4*1 MUX

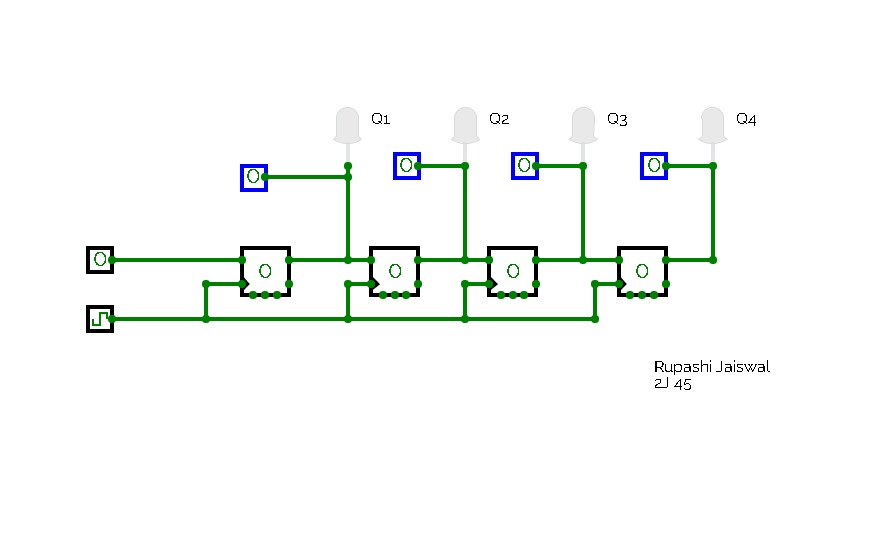

SIPO Shift Register

SIPO Shift Register

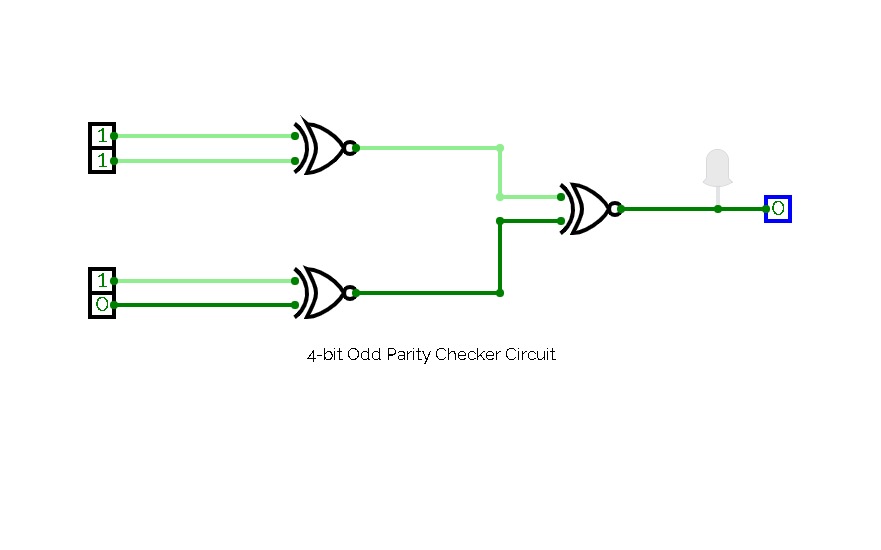

4-bit Odd Parity Checker

4-bit Odd Parity Checker

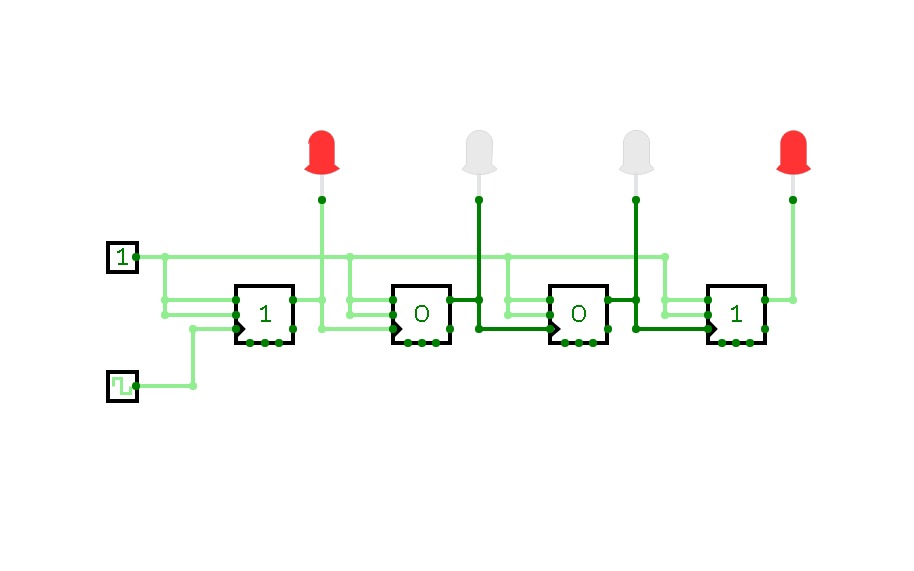

4-bit Asynchronous Up counter

4-bit Asynchronous Up counter

4- bit EP Checker circuit

4- bit EP Checker circuit

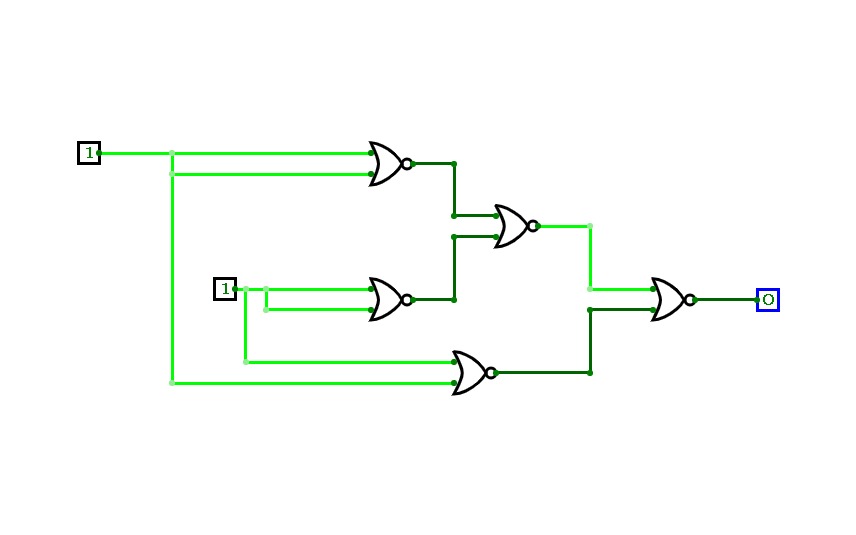

XOR using NOR gates

XOR using NOR gates

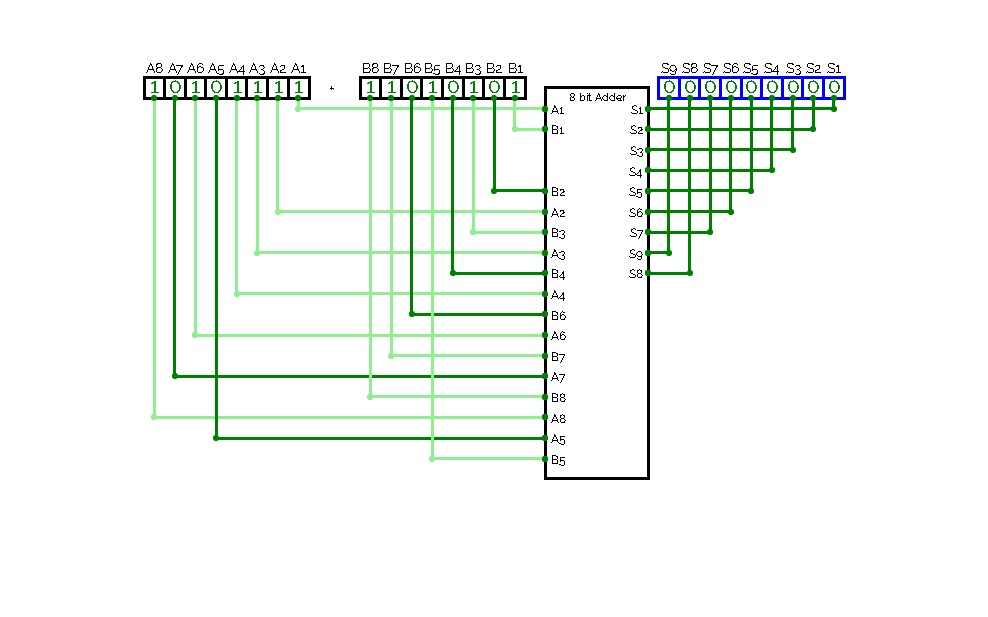

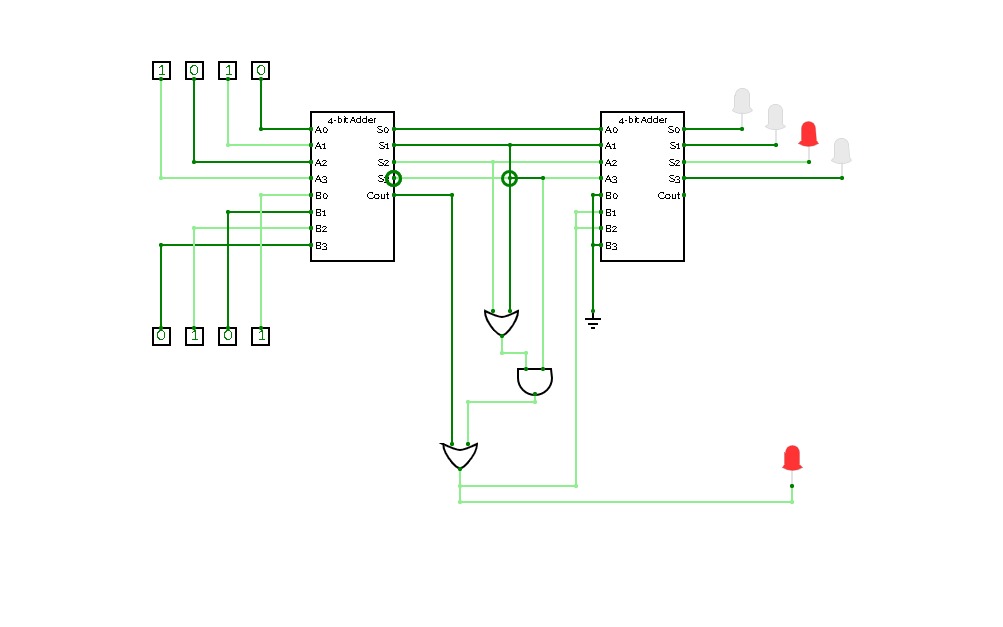

8-bit parallel Adder

8-bit parallel Adder

4-bit Asynchronous Down counter

4-bit Asynchronous Down counter

4:1 Mux using Logic Gates

4:1 Mux using Logic Gates

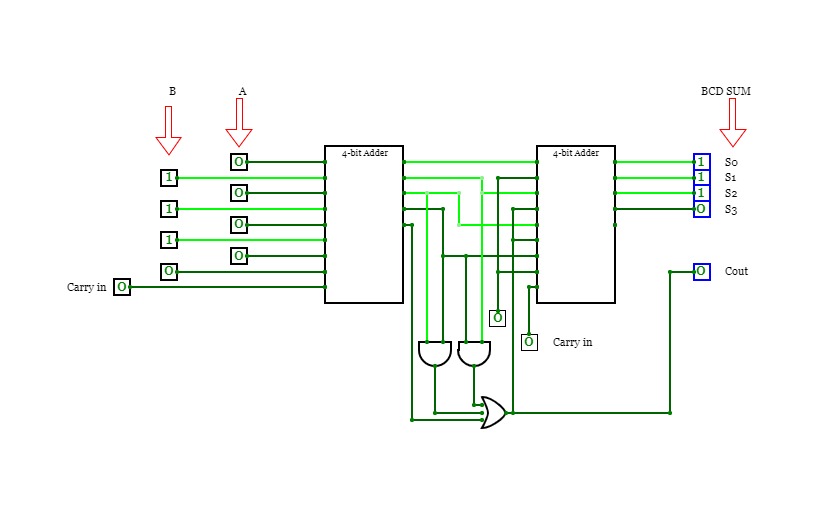

4- BCD ADDER

4- BCD ADDER

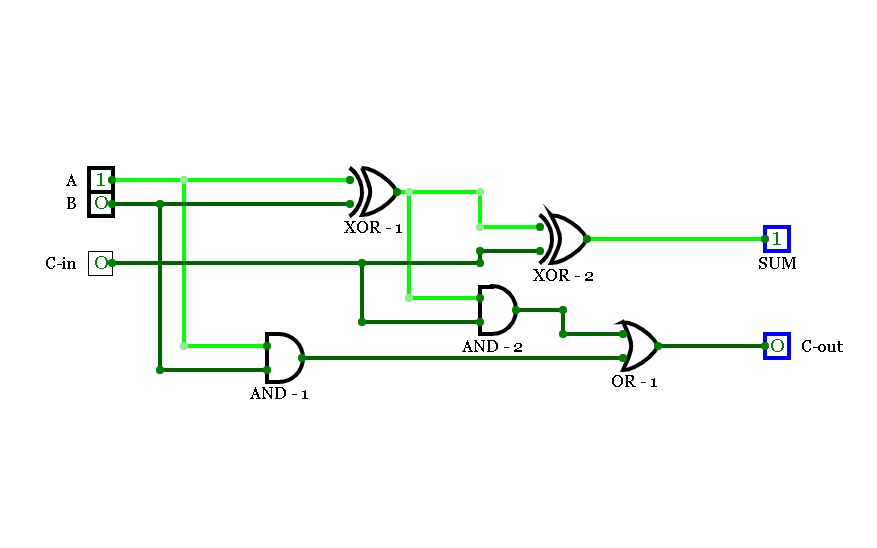

Full Adder using Logic Gates

Full Adder using Logic Gates

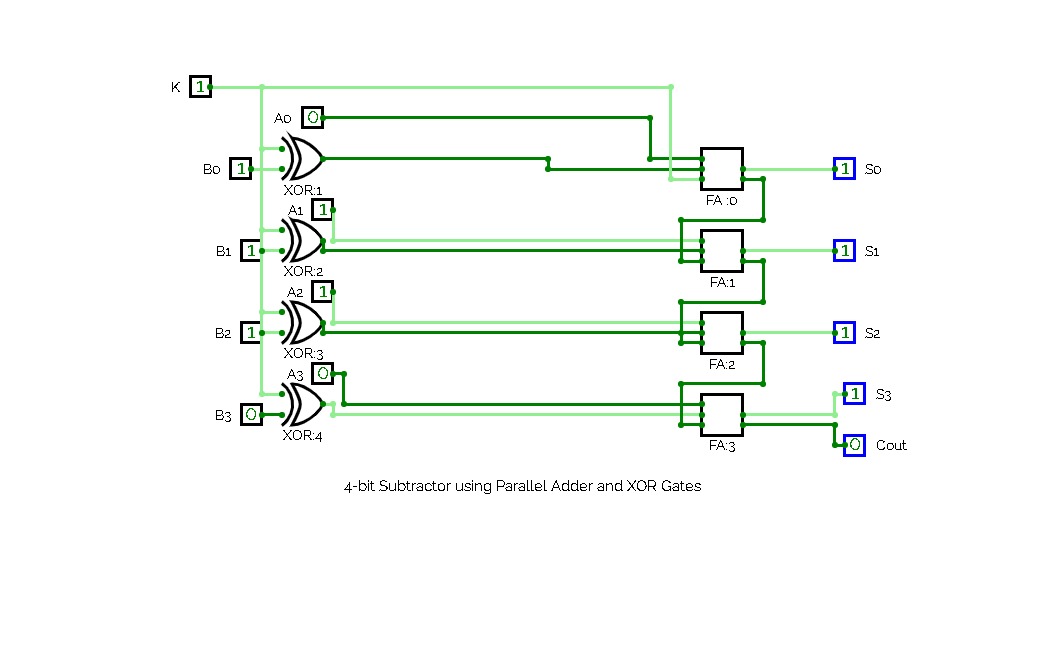

4-bit Subtractor using Parallel Adder and XOR Gates

4-bit Subtractor using Parallel Adder and XOR Gates

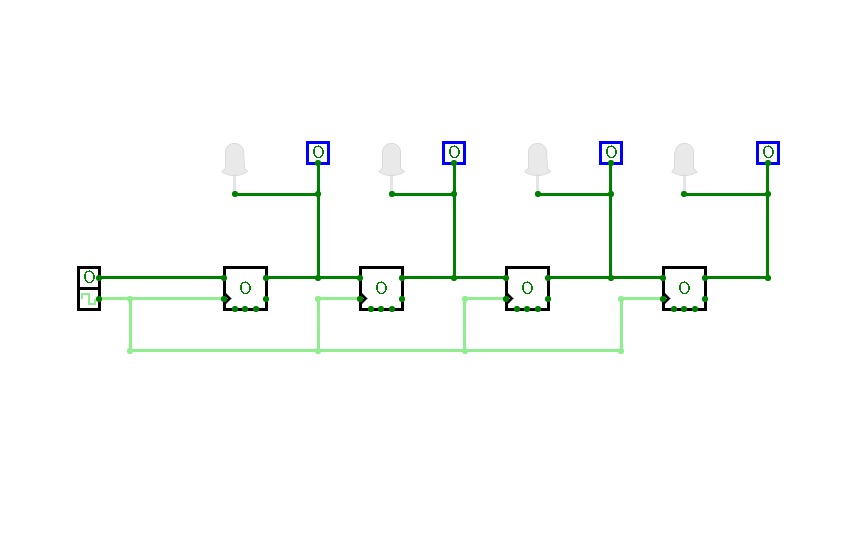

Right Shift Register [SIPO]

Right Shift Register [SIPO]

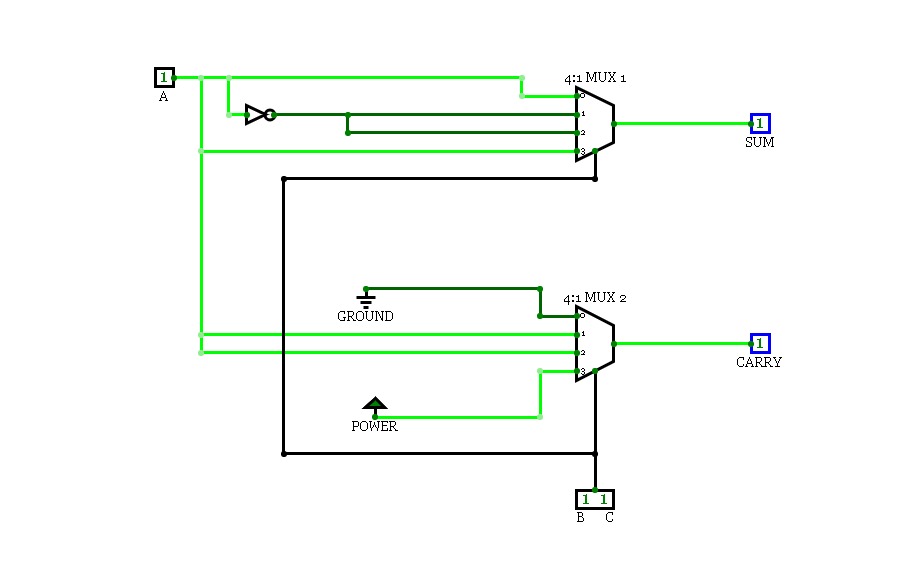

Full Adder using 2, 4*1 MUX

Full Adder using 2, 4*1 MUX

1x4 Demultiplexer

1x4 Demultiplexer

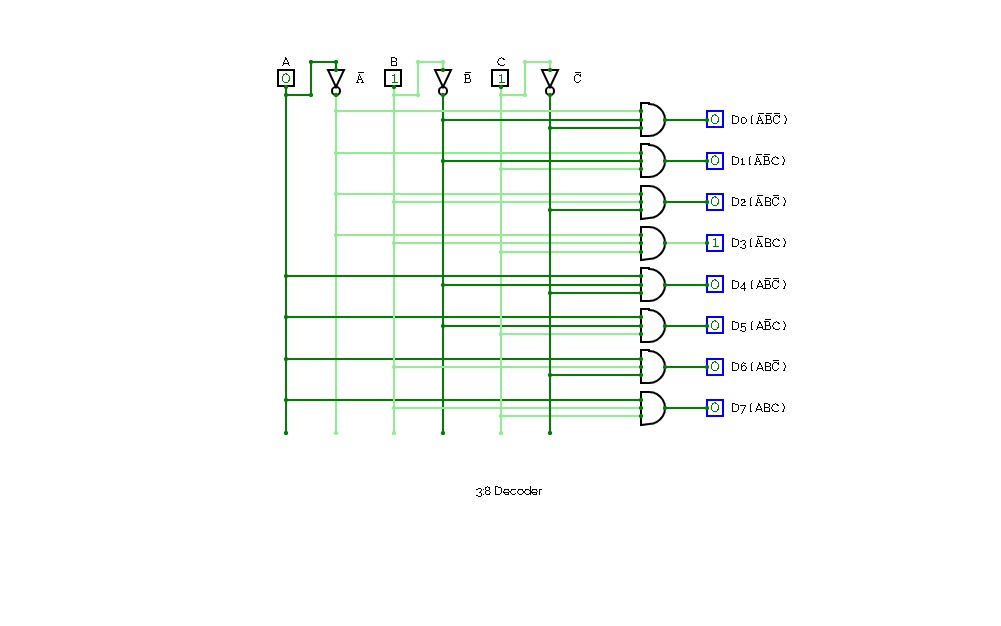

3 to 8 Line Decoder

3 to 8 Line Decoder

4-Bit BCD Adder

4-Bit BCD Adder

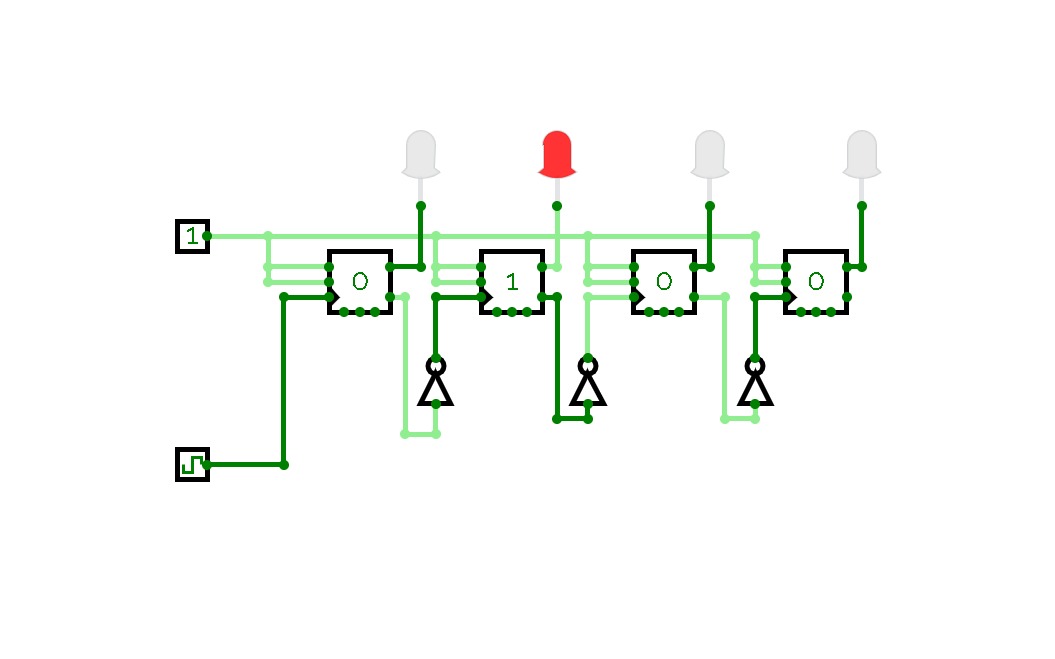

Figure 4.2 A serial binary adder

Figure 4.2 A serial binary adder

Shift Register - SIPO mode

Shift Register - SIPO mode

74HC161

74HC161