Prakhar

Member since: 3 years

Educational Institution: Not Entered

Country: Not Entered

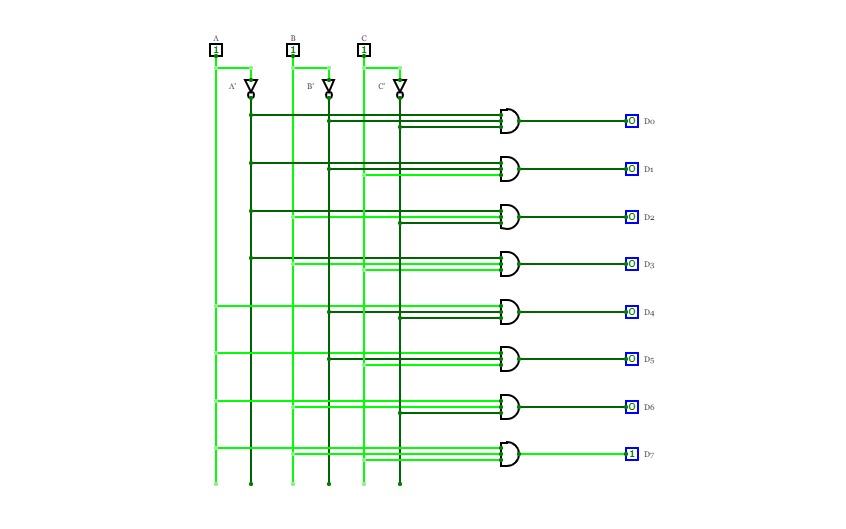

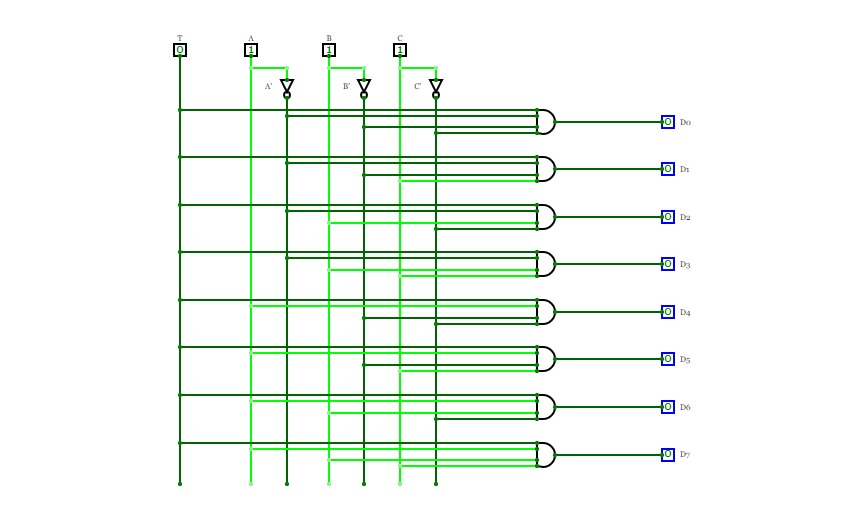

3*8 Decoder(EXP8)

3*8 Decoder(EXP8)

EXP-14B

EXP-14B

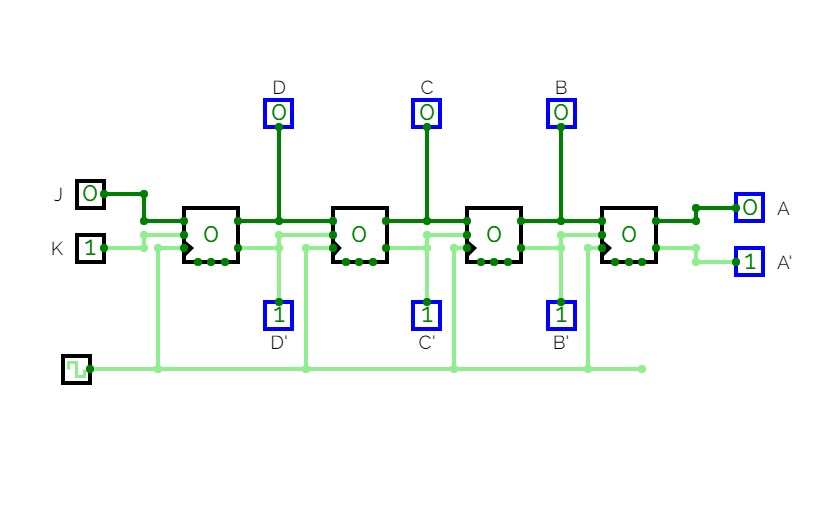

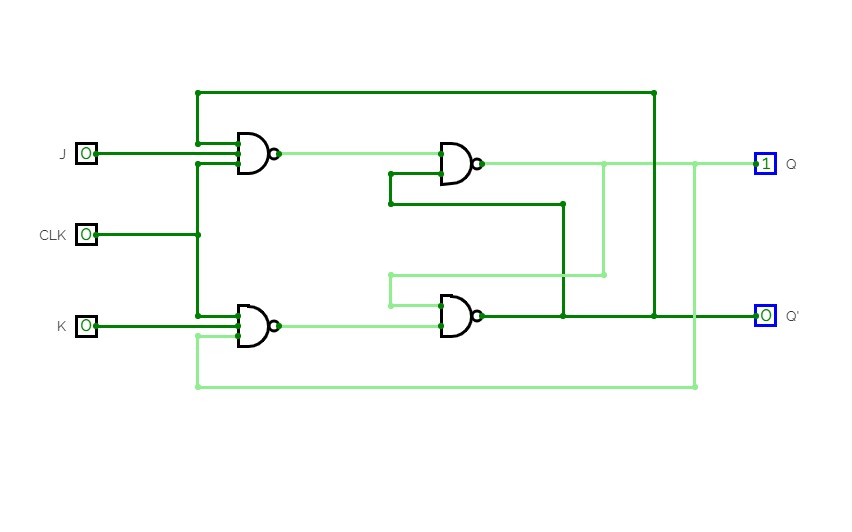

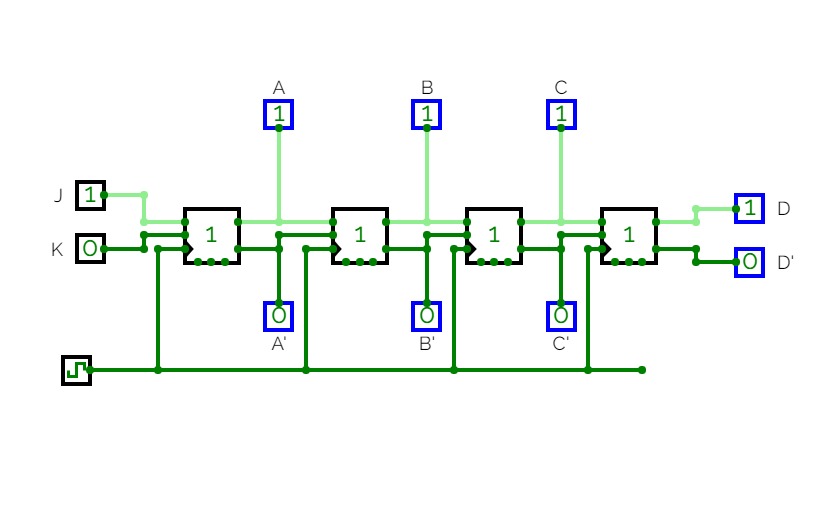

Right shift using JK

Right shift using JK

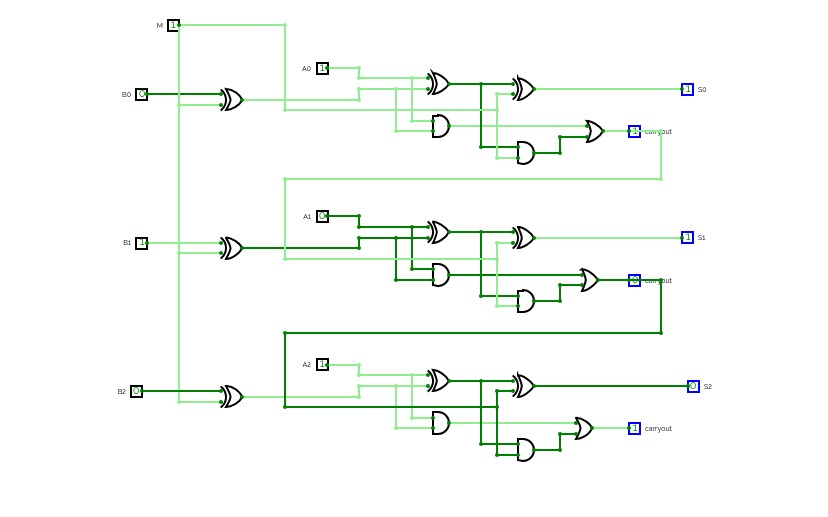

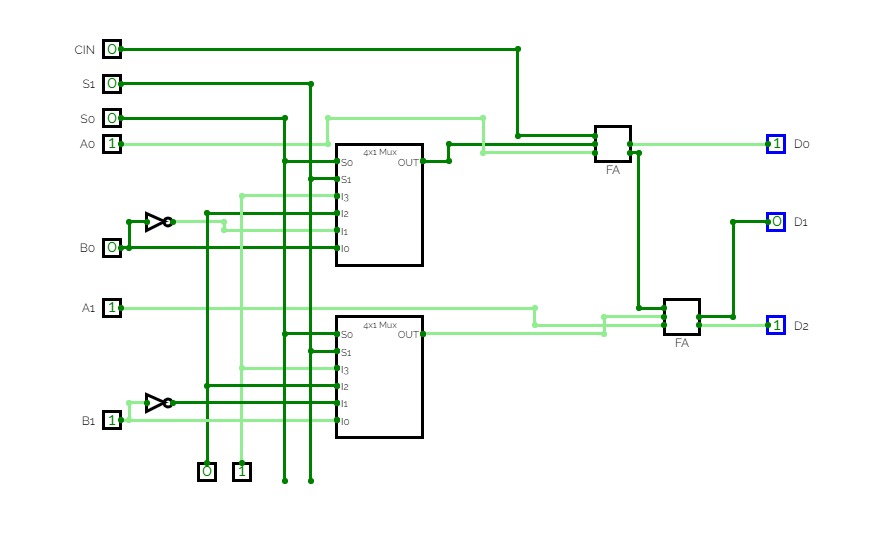

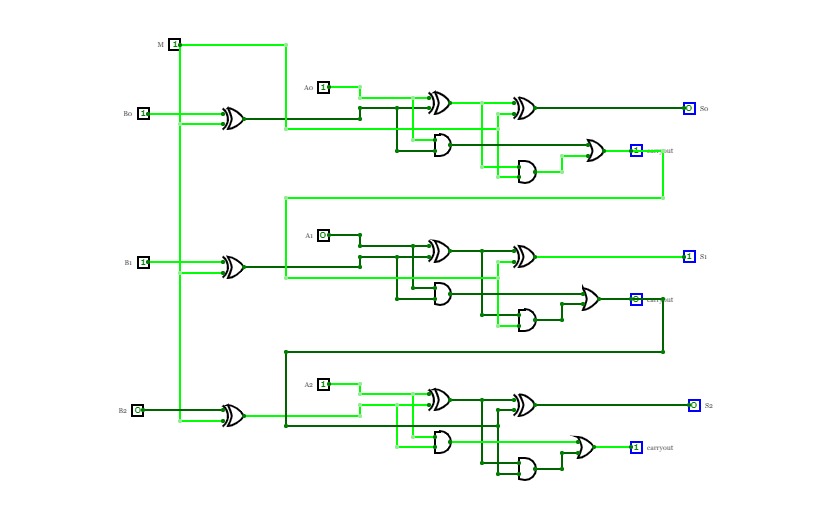

binary parallel adder-subtractor(EXTERNAL EXAM)

binary parallel adder-subtractor(EXTERNAL EXAM)

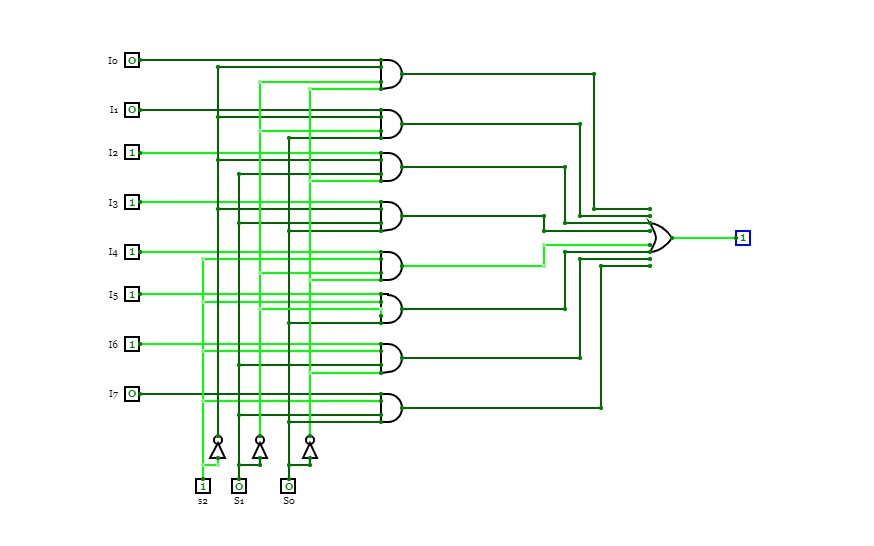

Exp 9 (8*1 Multiplexer)

Exp 9 (8*1 Multiplexer)

EXP_7

EXP_7

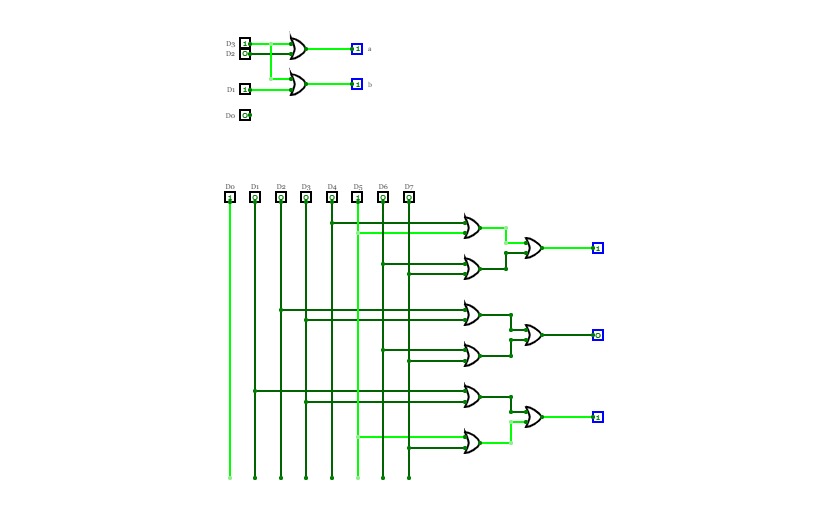

2*4 Decoder(exp8)

2*4 Decoder(exp8)

3*8 Decoder(EXP8 Enable)

3*8 Decoder(EXP8 Enable)

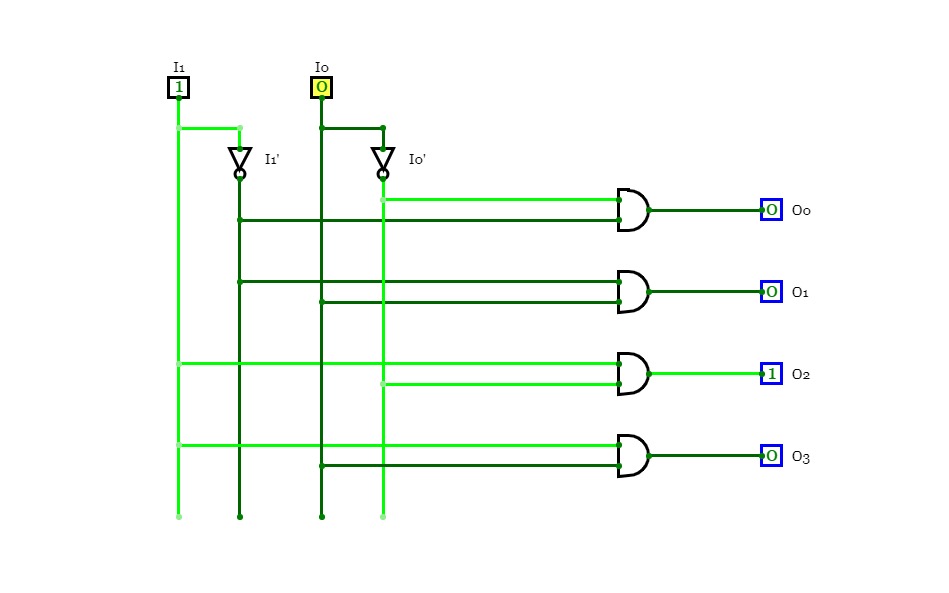

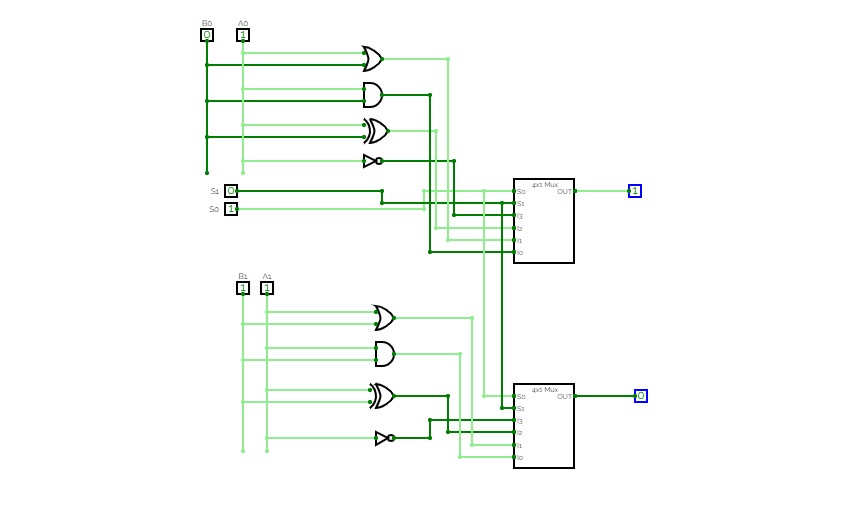

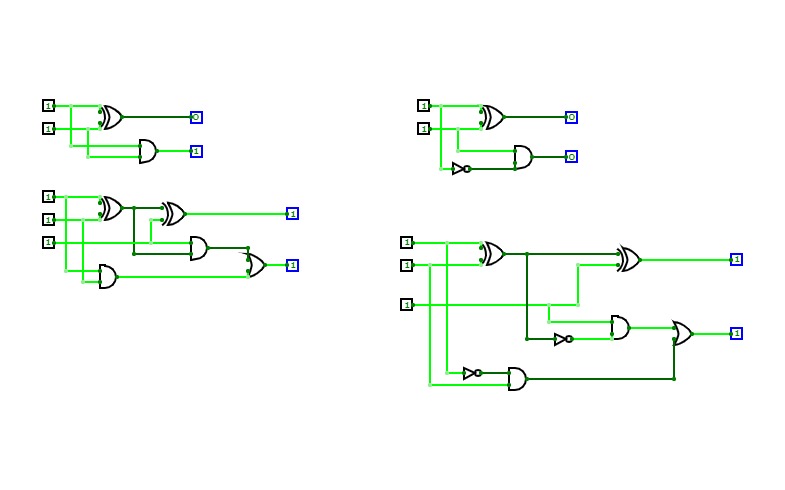

Exp-15A( 2 bit Arithimetic)

Exp-15A( 2 bit Arithimetic)

Exp-15B

Exp-15B

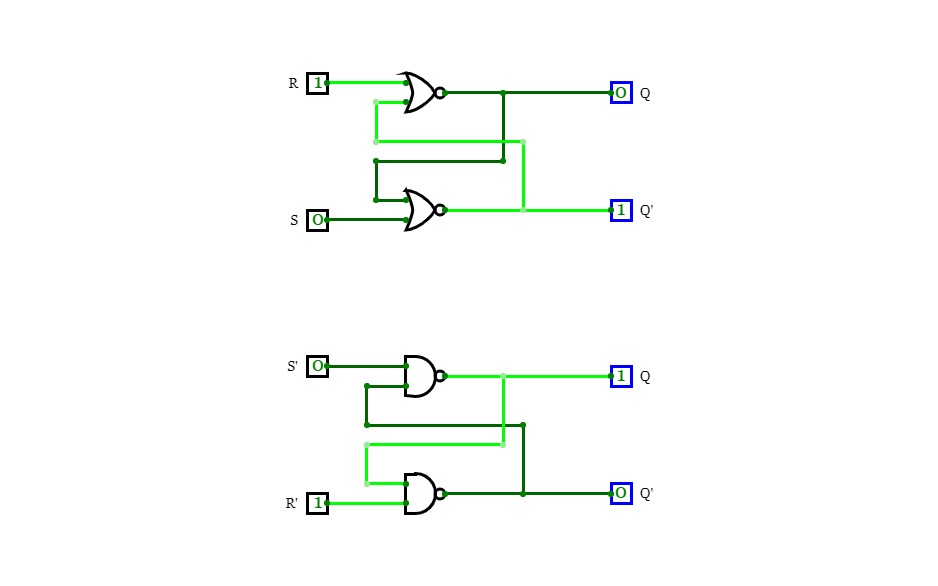

S-R Latch

S-R Latch

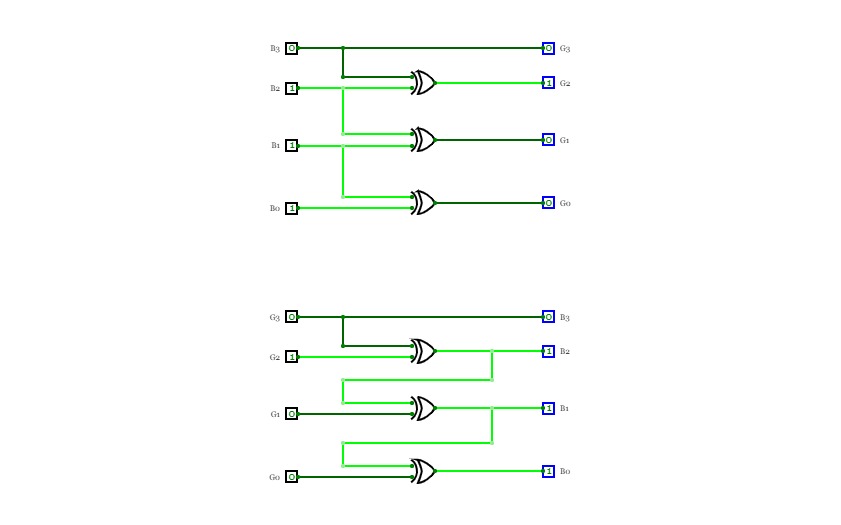

Gray code

Gray code

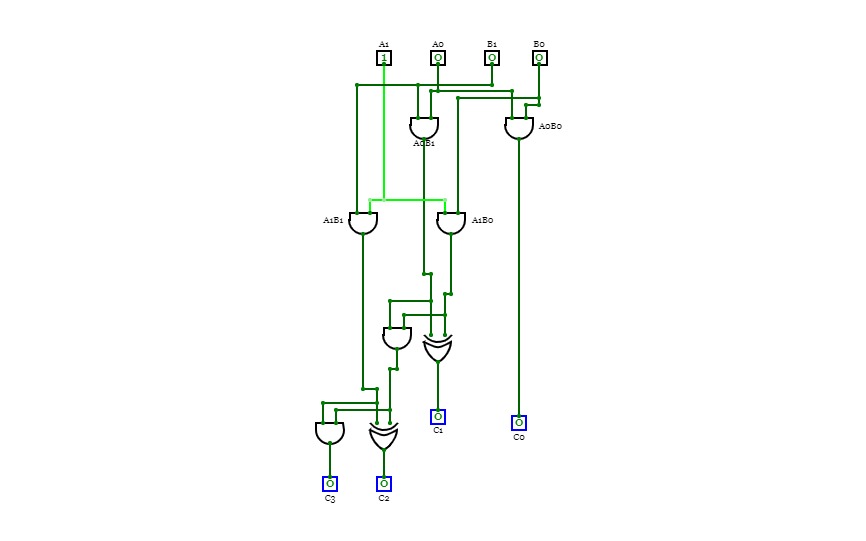

array_multiplier(2*2)

array_multiplier(2*2)

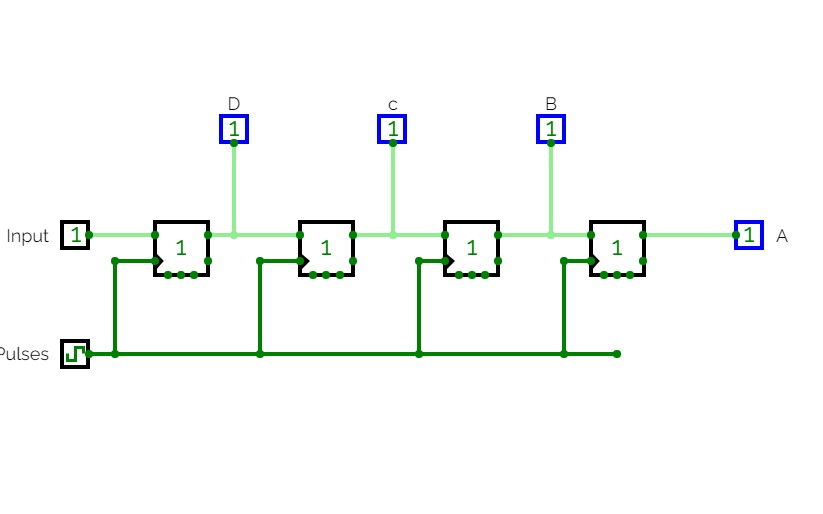

EXP-17 Shift Right using D

EXP-17 Shift Right using D

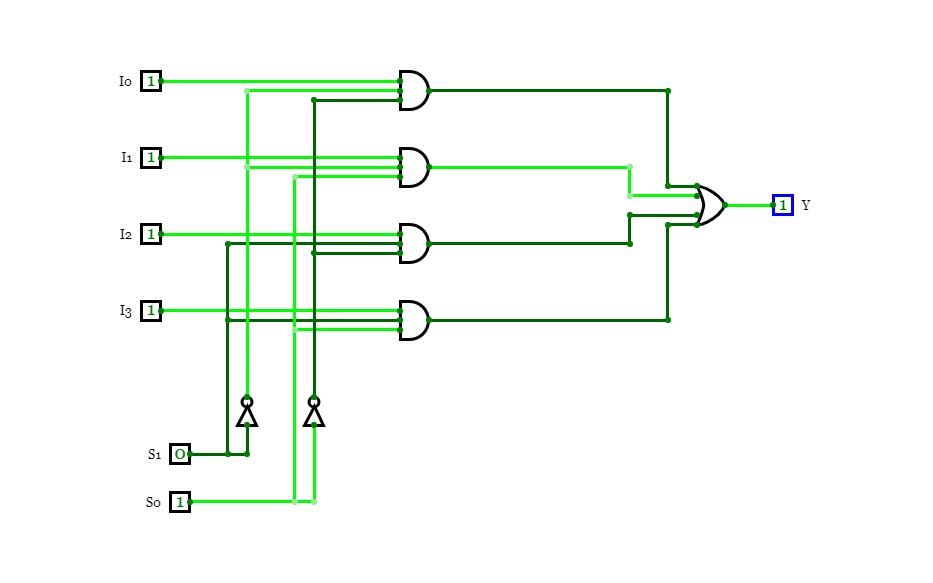

EXP 9(4*1 Multiplexer)

EXP 9(4*1 Multiplexer)

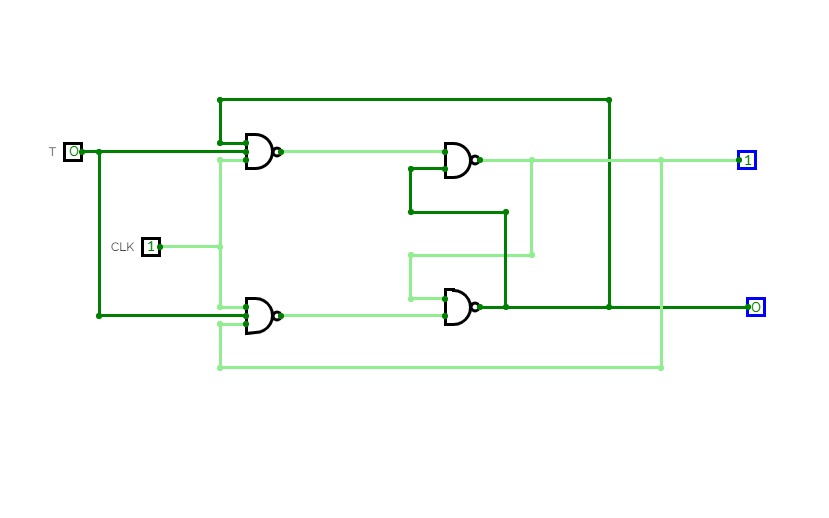

T Flip Flop

T Flip Flop

Modified SR Circuit

Modified SR Circuit

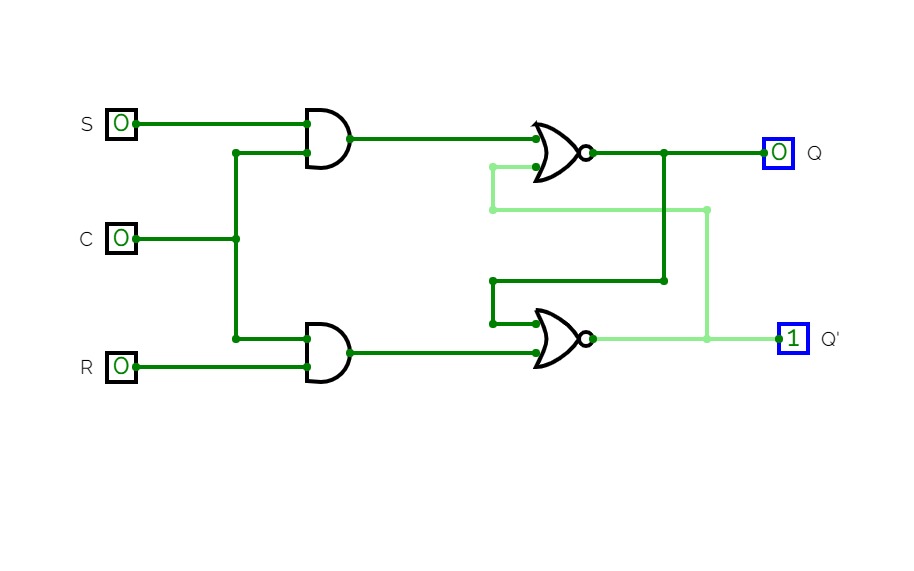

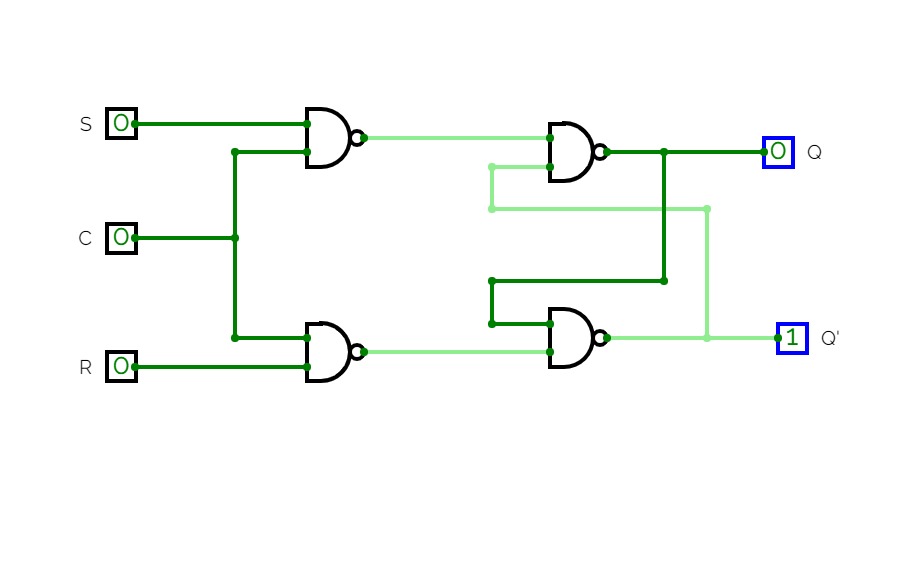

Clocked SR using NOR

Clocked SR using NOR

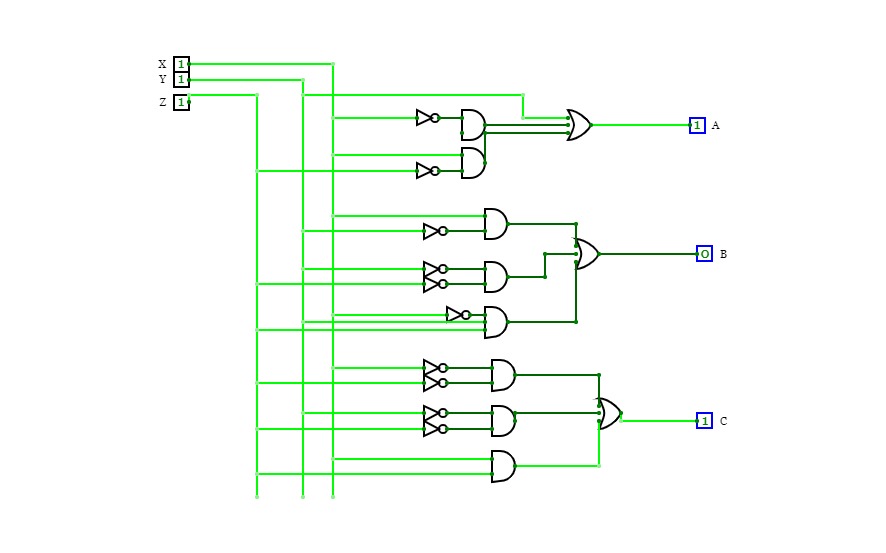

k map

k map

Shift Left using JK

Shift Left using JK

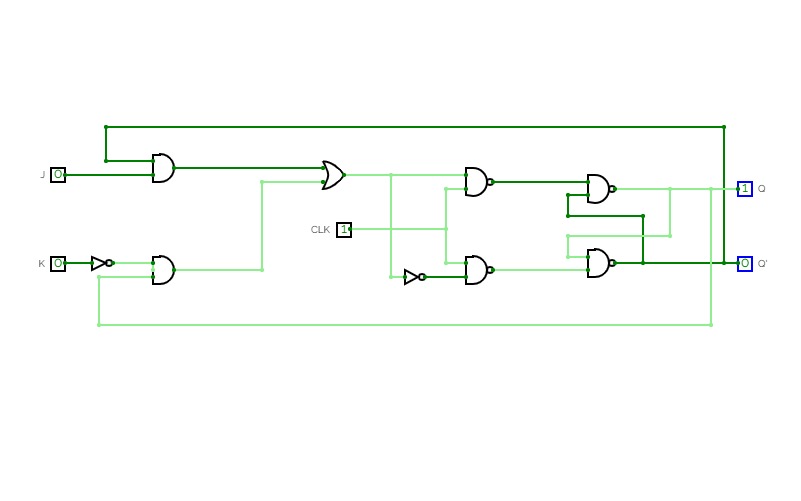

JK Flip flop using D Flip flop(EDV)

JK Flip flop using D Flip flop(EDV)

Clocked SR using NAND

Clocked SR using NAND

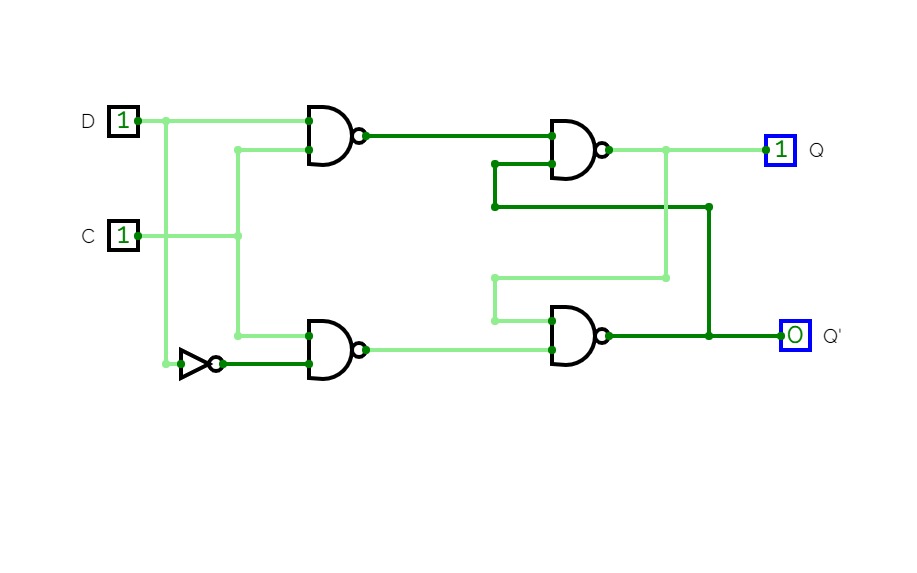

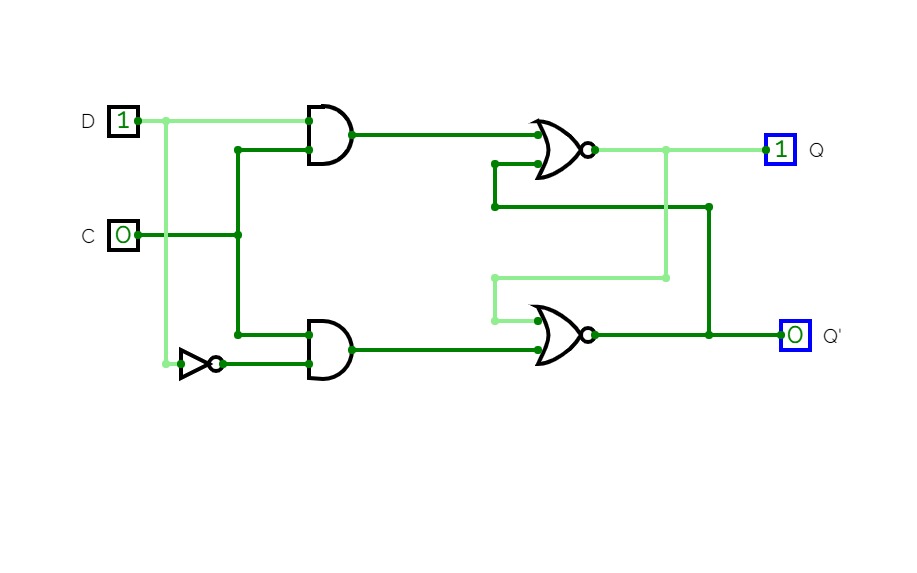

D Latch using NAND

D Latch using NAND

D Latch using NOR

D Latch using NOR

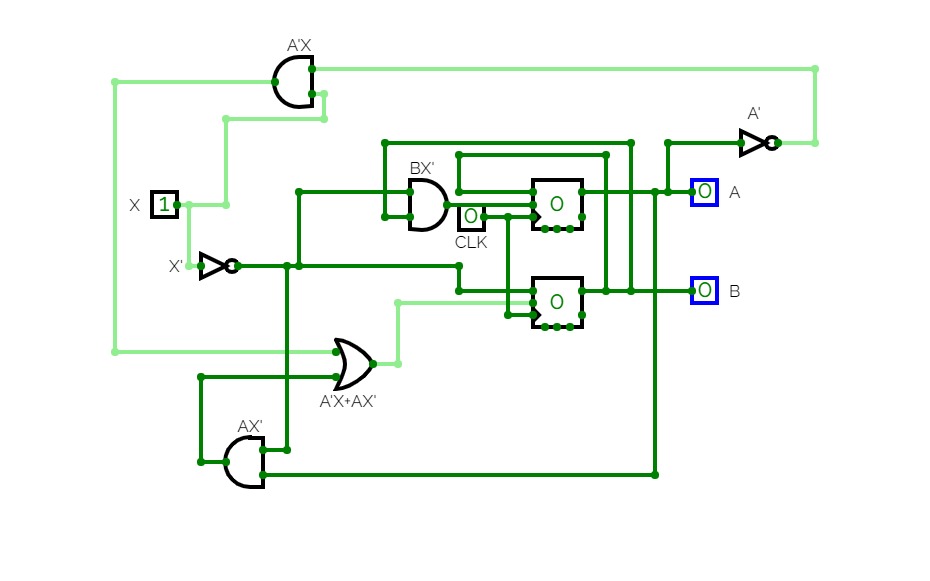

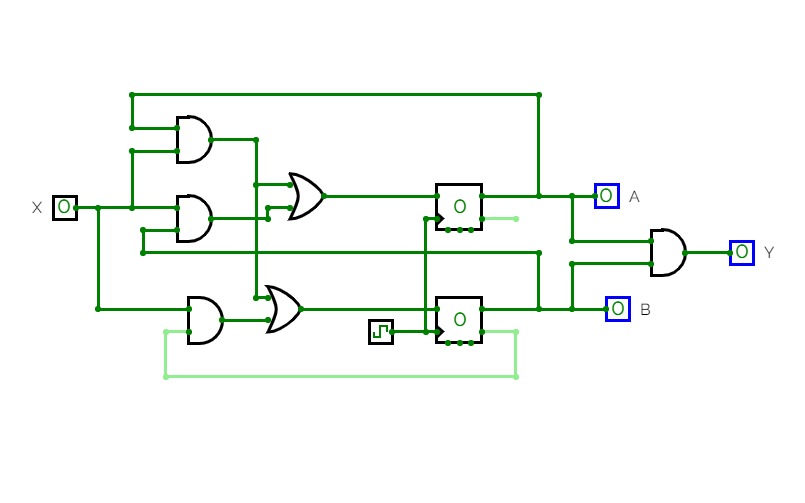

Exp -16 (Determine 3 consecutive 1s)

Exp -16 (Determine 3 consecutive 1s)

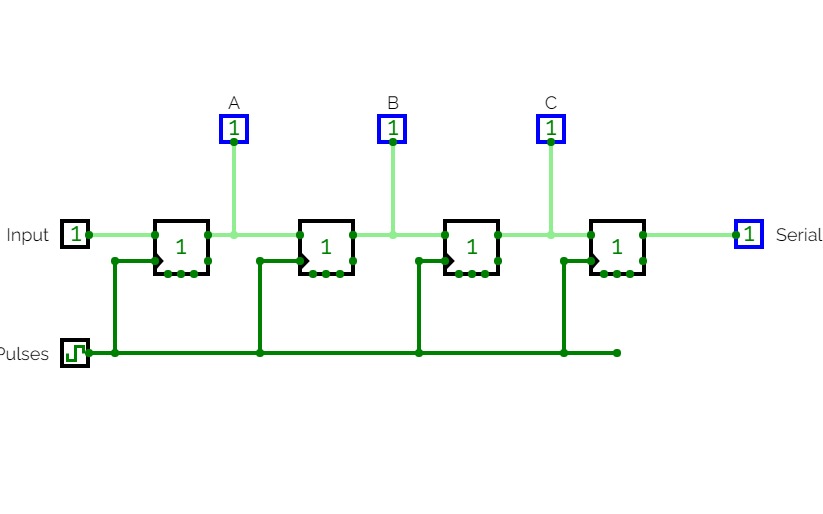

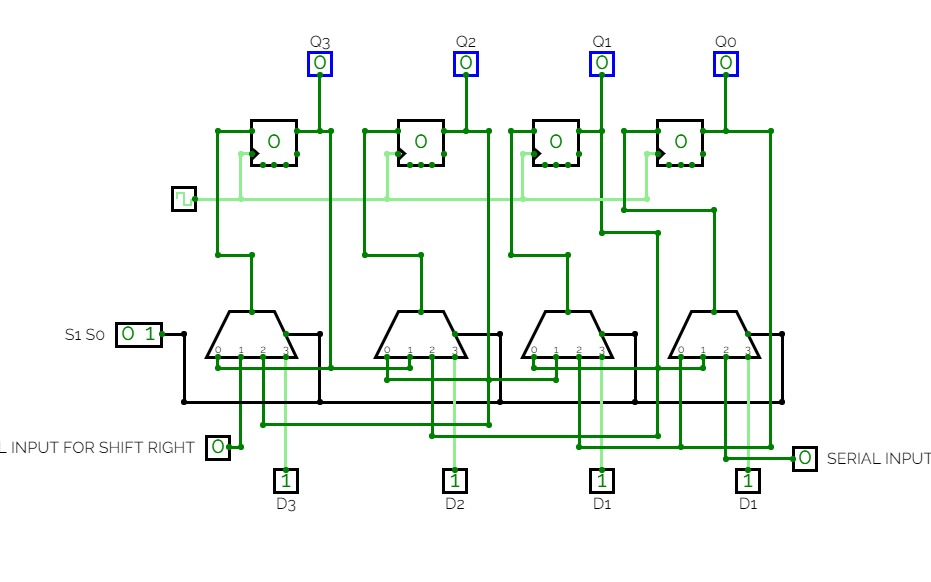

Universal Register

Universal Register

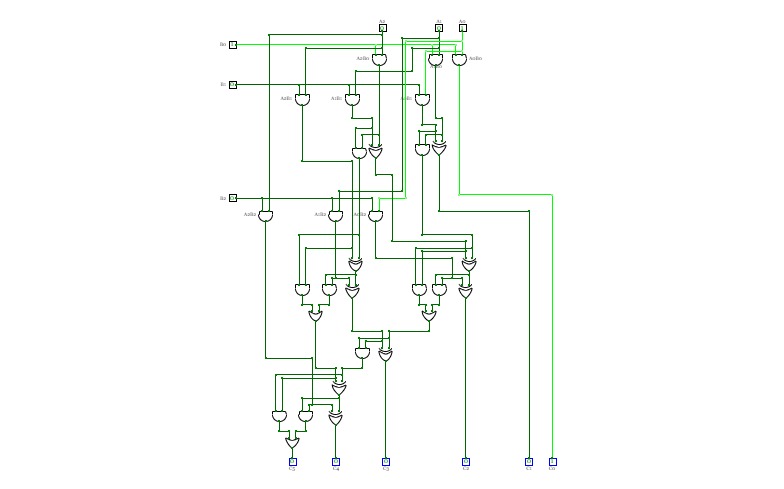

array_multiplier(3*3)

array_multiplier(3*3)

add_sub

add_sub

Full adder using XOR

Full adder using XOR

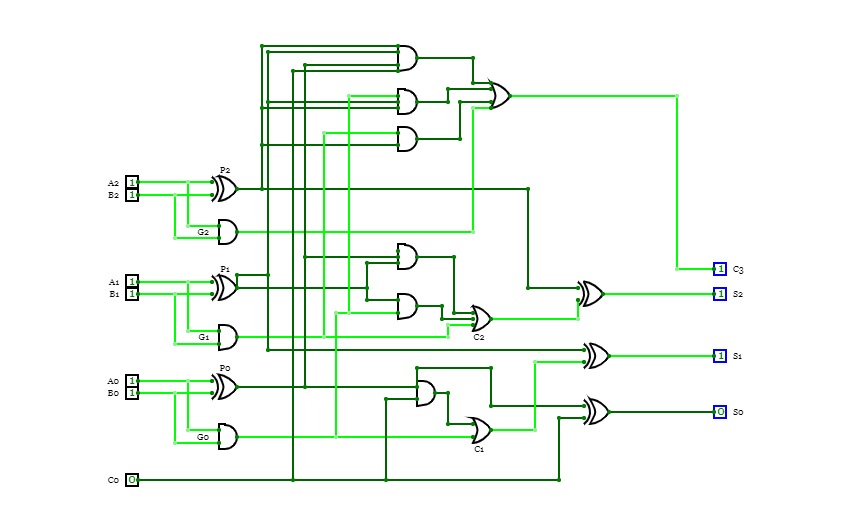

carry adder

carry adder

array_multiplier(3*3)

array_multiplier(3*3)

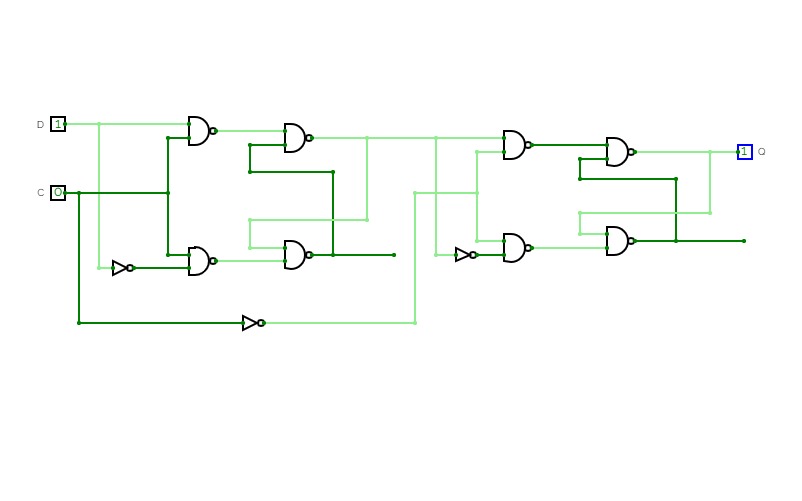

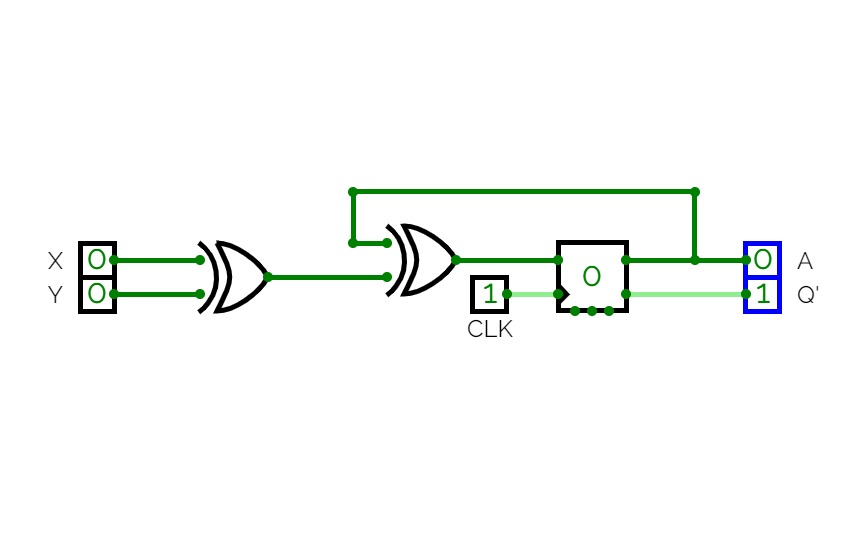

Edge Trigerred Flip Flop (Master-slave)

Edge Trigerred Flip Flop (Master-slave)

EXP 14 A (using internal D Flip Flop)

EXP 14 A (using internal D Flip Flop)

Exp-17 Shift Left using D

Exp-17 Shift Left using D