Kunal Singh

Member since: 4 years

Educational Institution: Not Entered

Country: Not Entered

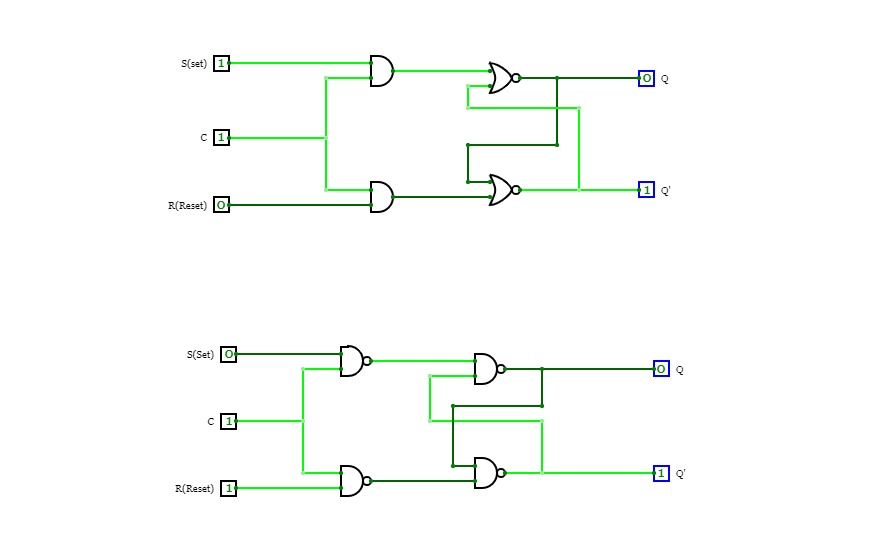

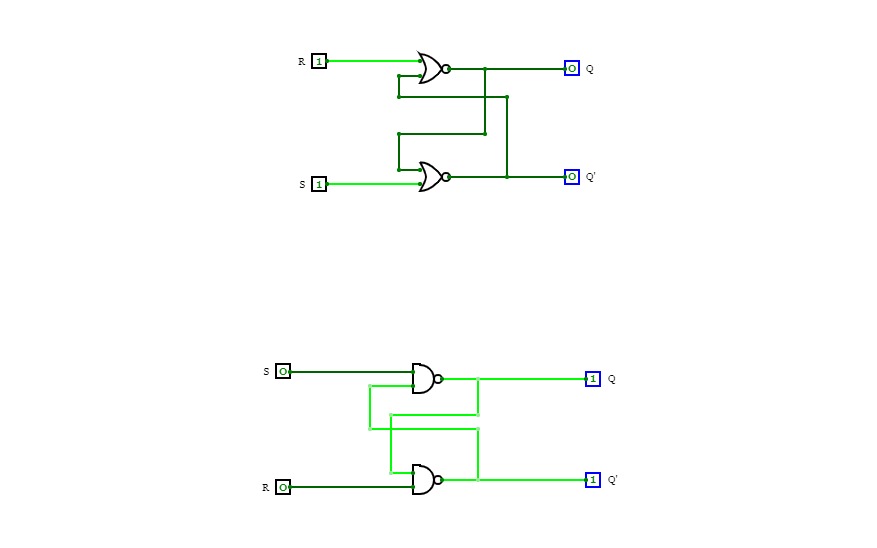

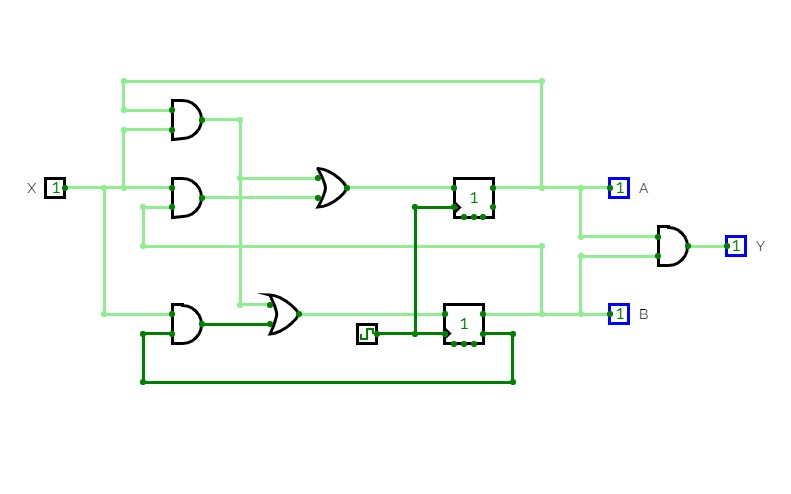

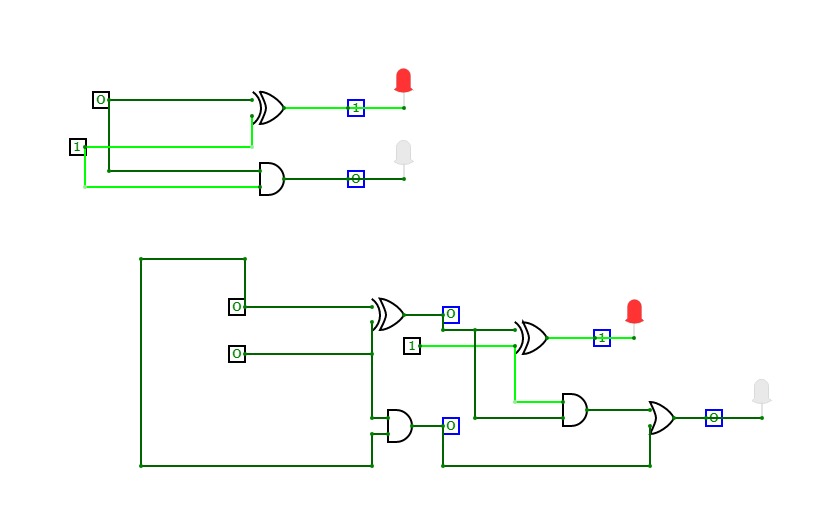

Clocked SR latch using NOR & NAND gate

Clocked SR latch using NOR & NAND gate

Exp-12

Exp-12

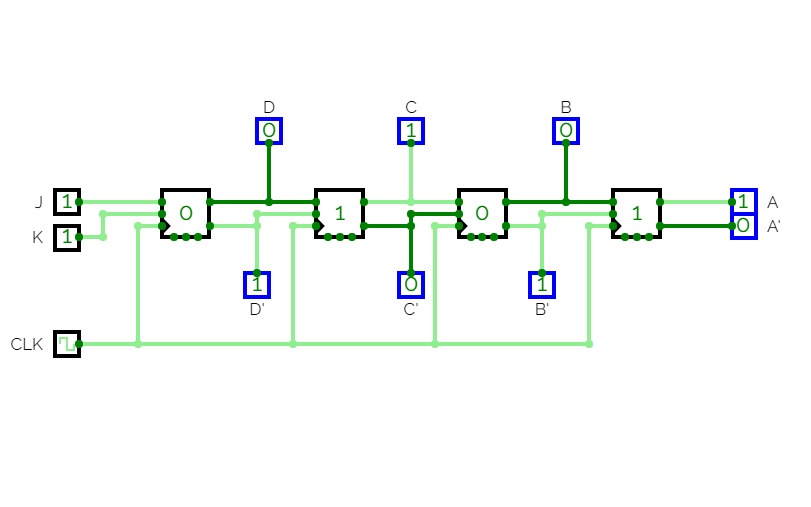

Exp 17a ii (shift left using JK)

Exp 17a ii (shift left using JK)

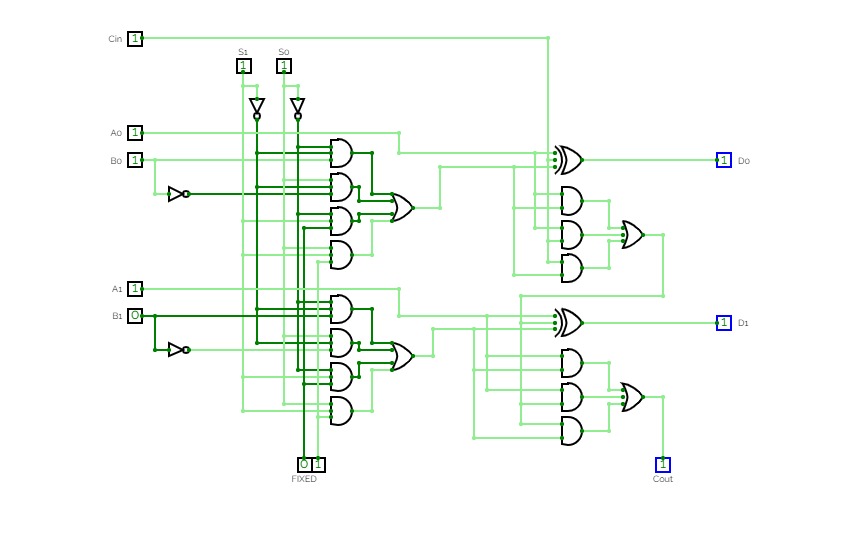

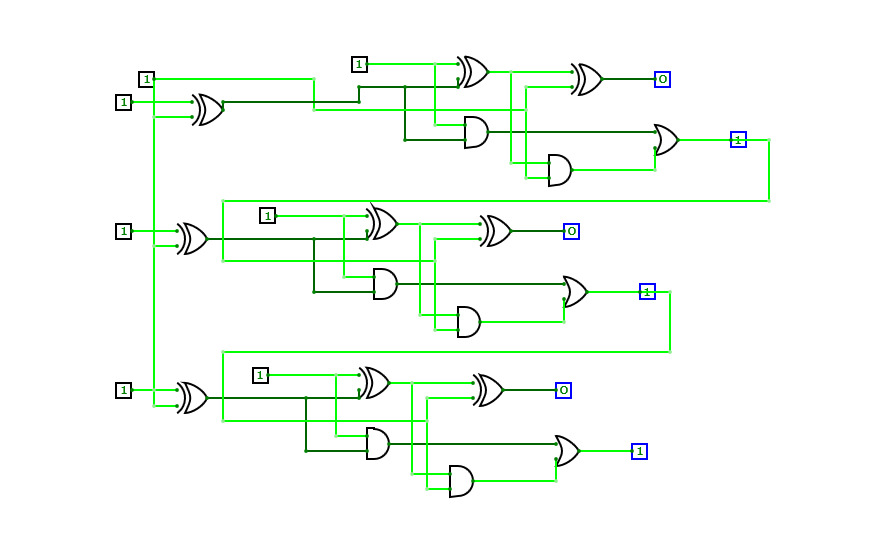

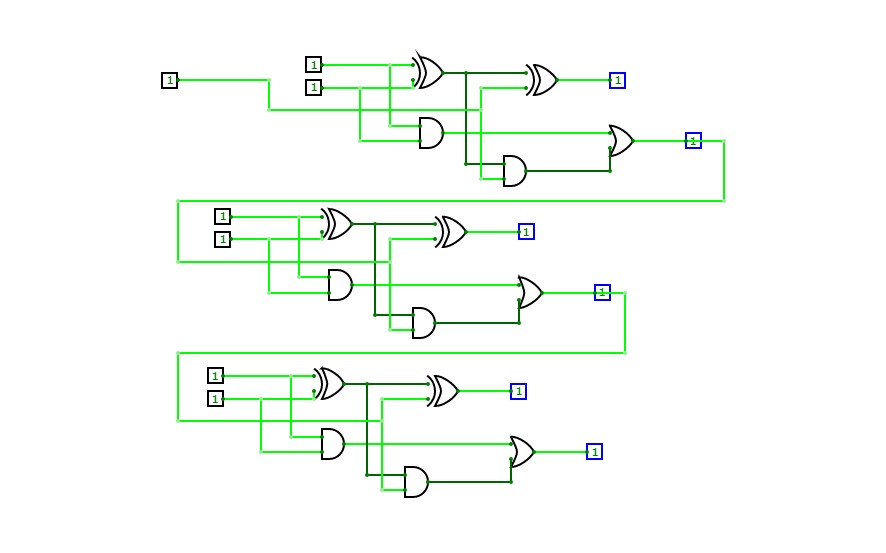

Exp 15-a (2 bit arithmetic)

Exp 15-a (2 bit arithmetic)

23/09/2020

23/09/2020

Exp.6 (1)

Exp.6 (1)

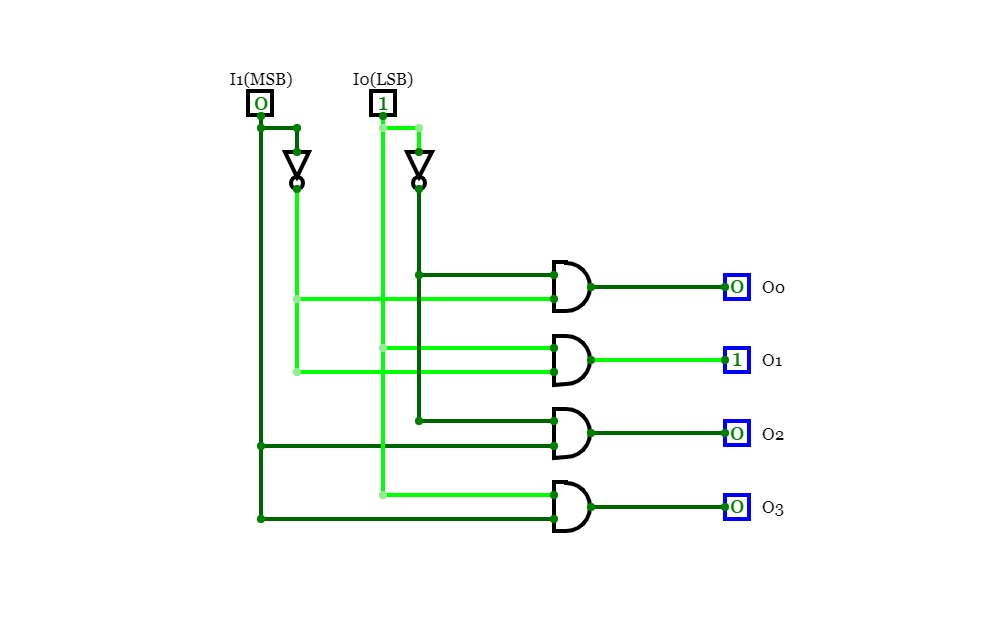

2x4 decoder

2x4 decoder

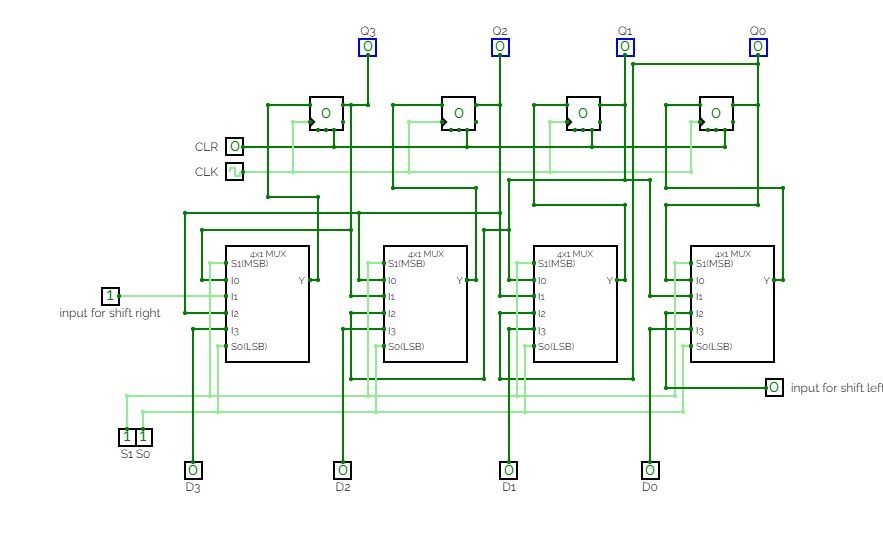

Exp 17c (universal shift register)

Exp 17c (universal shift register)

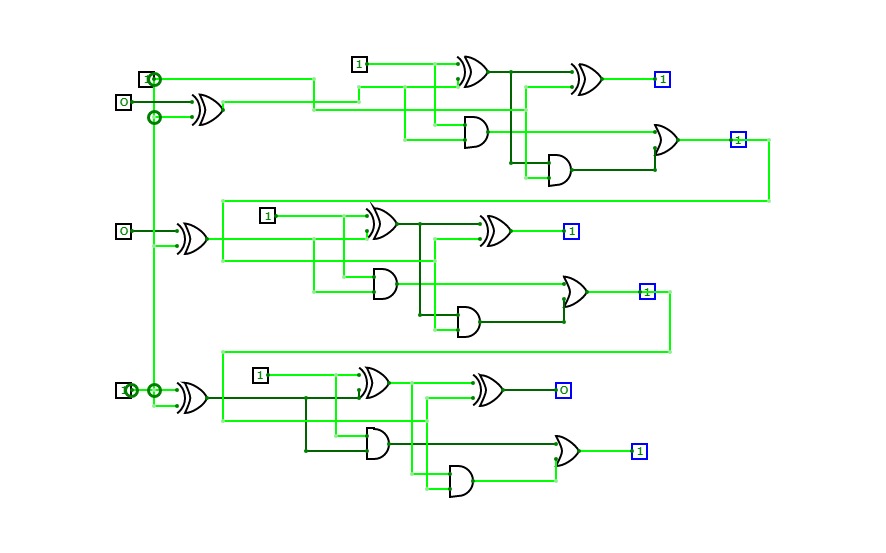

Exp 15-b (logic diagram)

Exp 15-b (logic diagram)

Lab 3

Lab 3

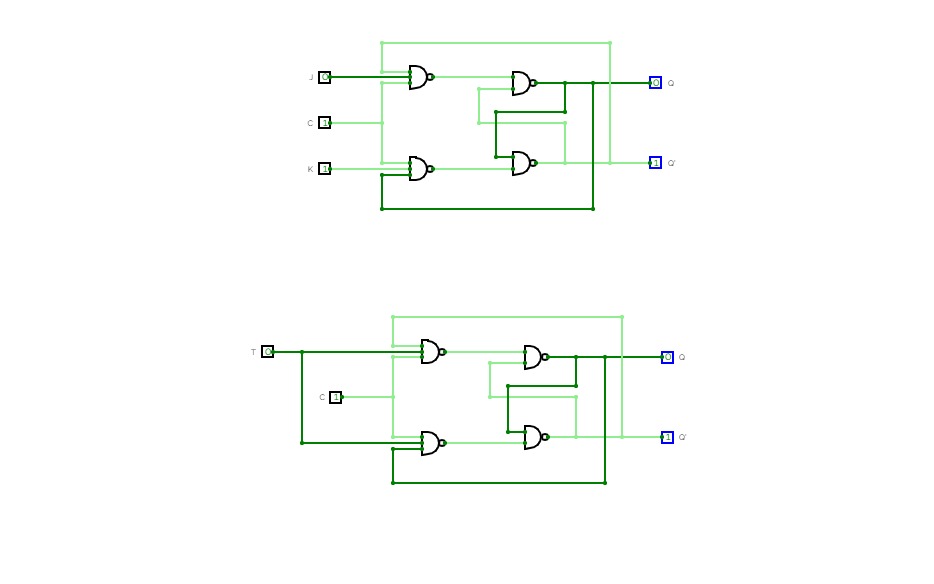

Exp-11

Exp-11

Exp 17 b2 (shift right using JK)

Exp 17 b2 (shift right using JK)

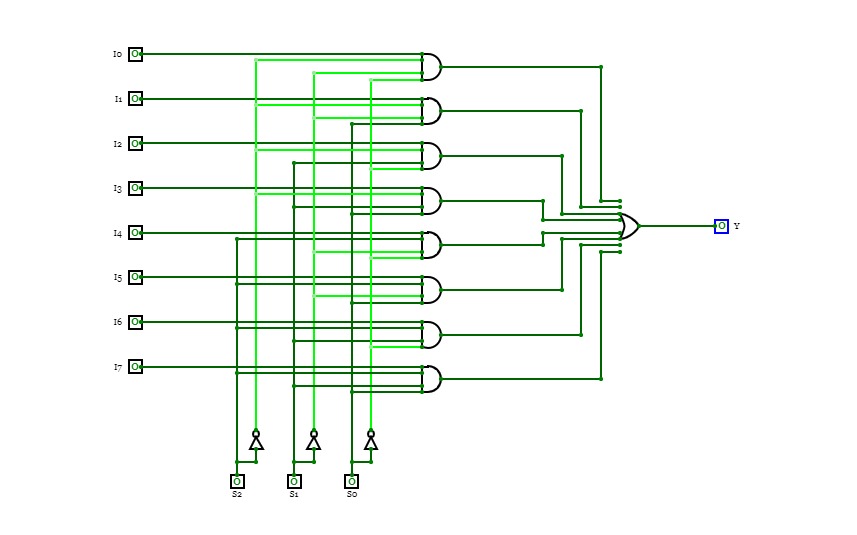

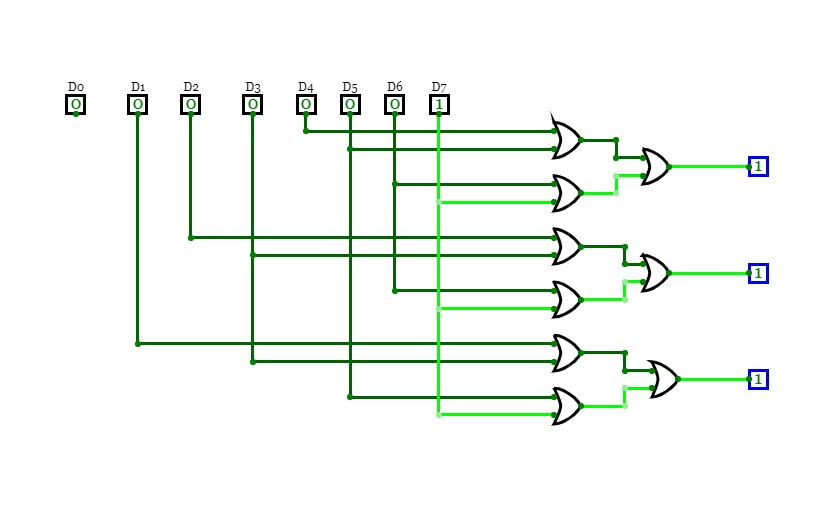

8x1 MULTIPLEXER

8x1 MULTIPLEXER

Exp 16

Exp 16

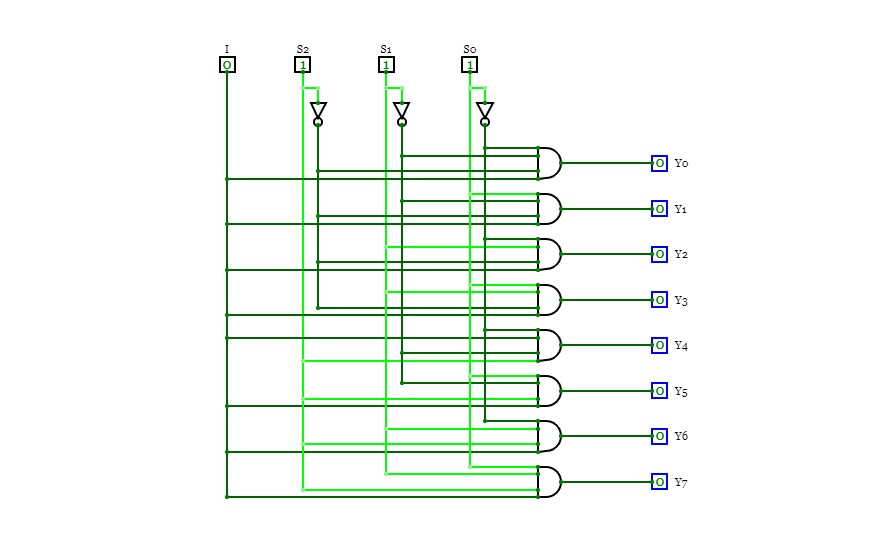

1x8 DeMultiplexer

1x8 DeMultiplexer

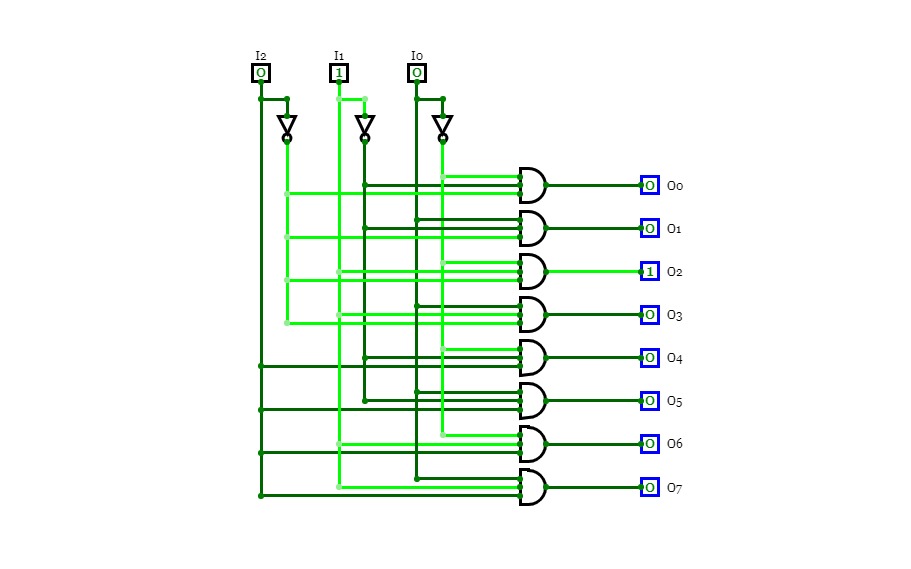

Decoder 3x8

Decoder 3x8

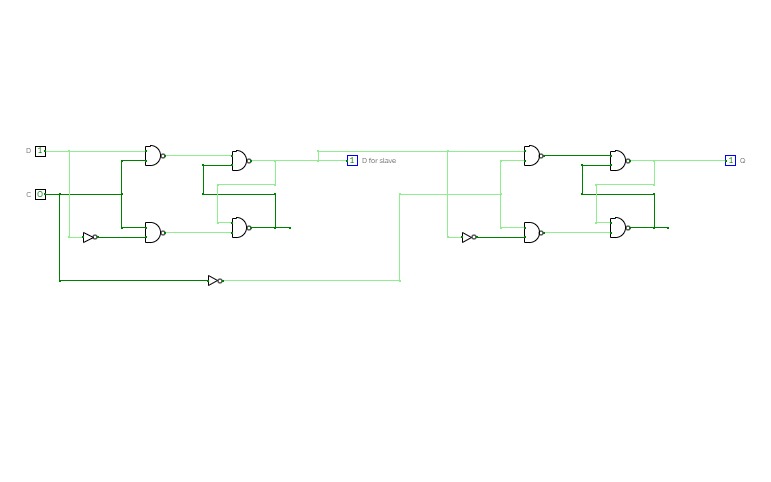

Master Slave Exp-13

Master Slave Exp-13

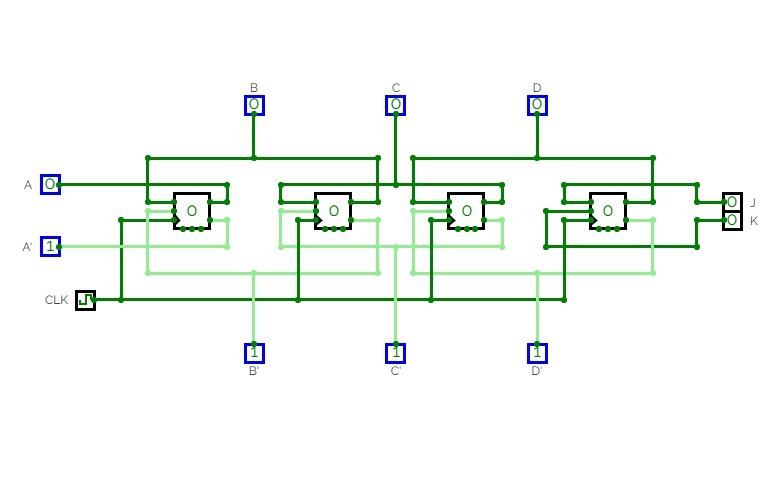

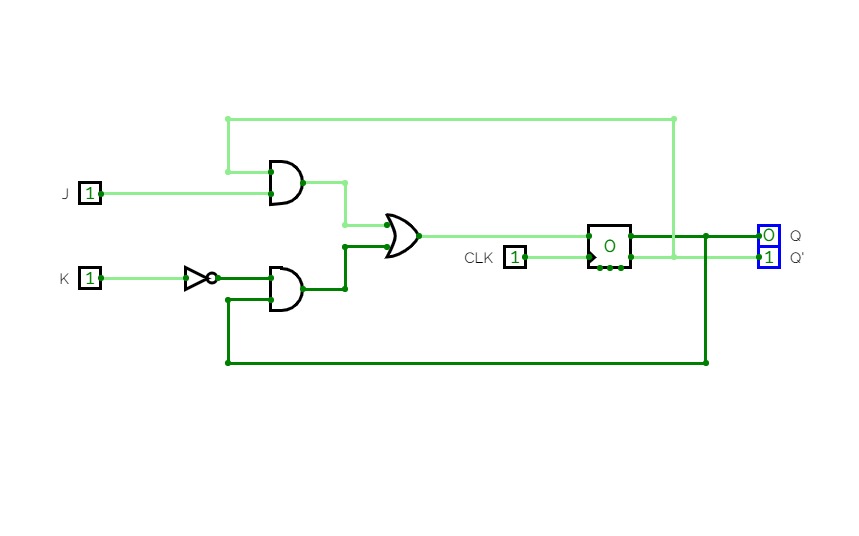

JK Flip Flop Exp-13

JK Flip Flop Exp-13

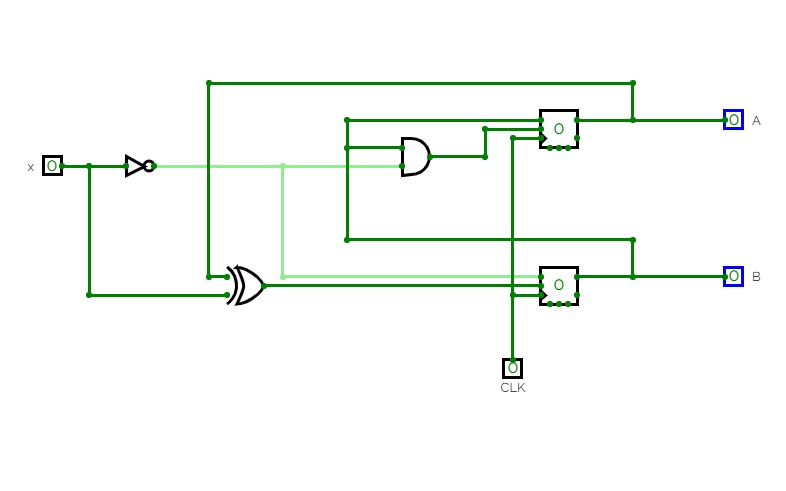

Exp 14-b

Exp 14-b

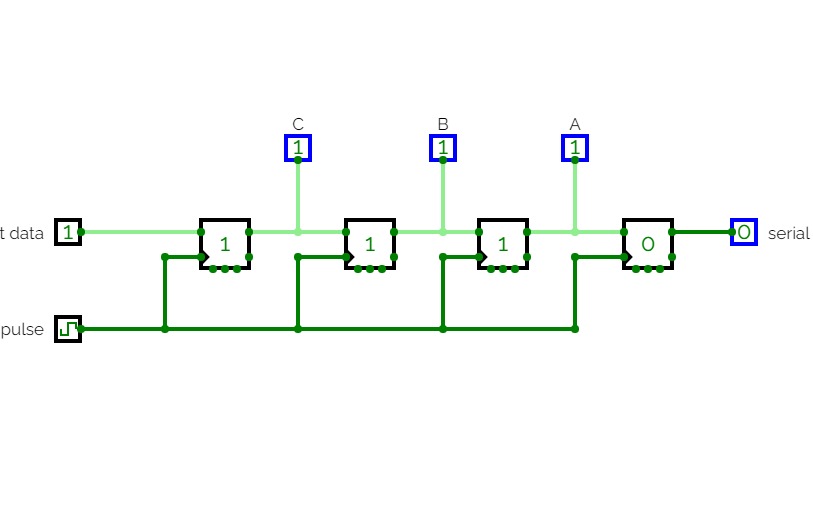

Exp 17 b1 (Shift right using D)

Exp 17 b1 (Shift right using D)

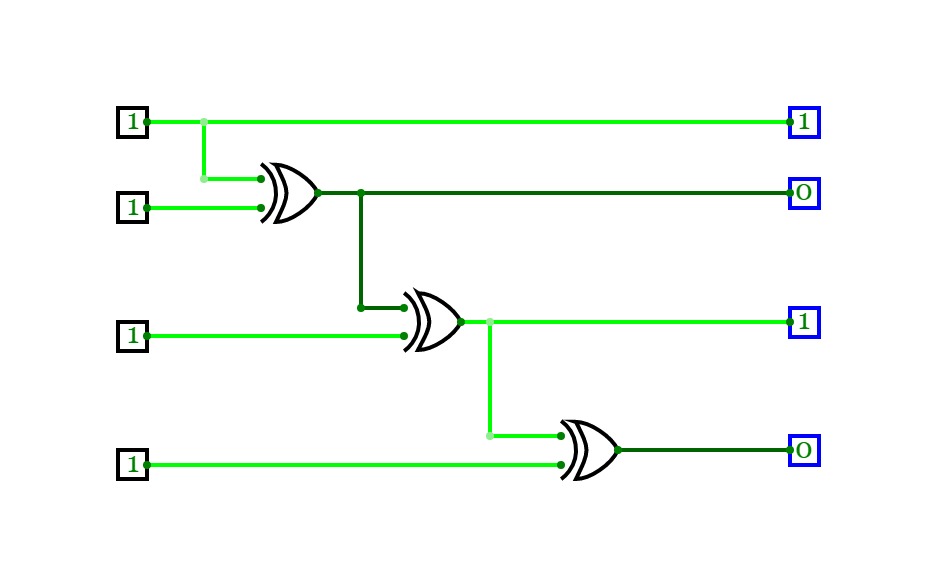

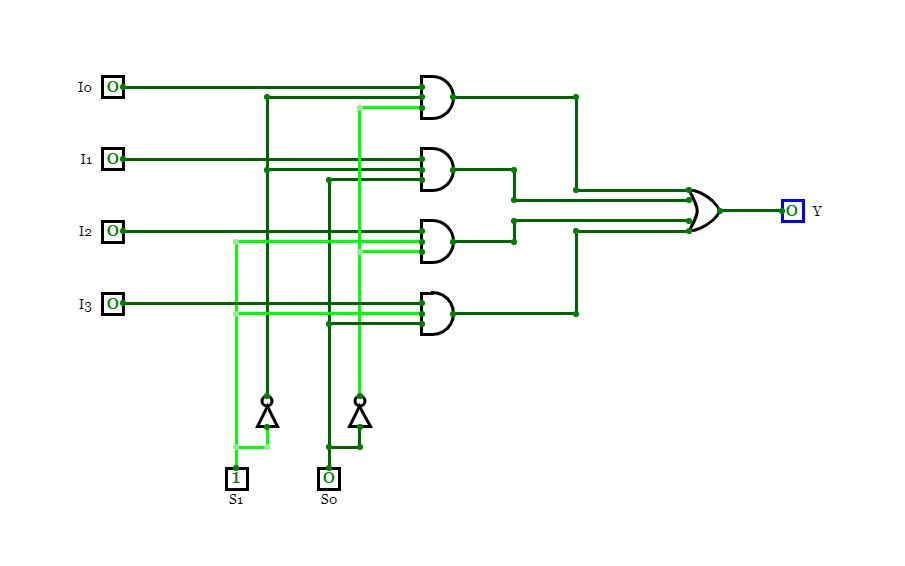

4x1 MULTIPLEXER

4x1 MULTIPLEXER

26/08/12

26/08/12

Untitled

Untitled

Lab 3

Lab 3

Exp.6 (2)

Exp.6 (2)

Untitled

Untitled

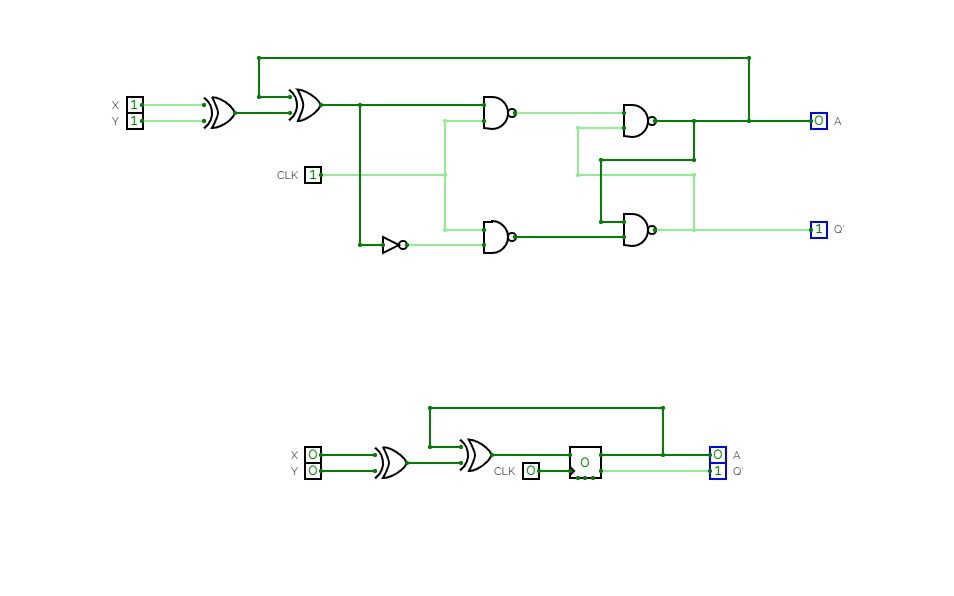

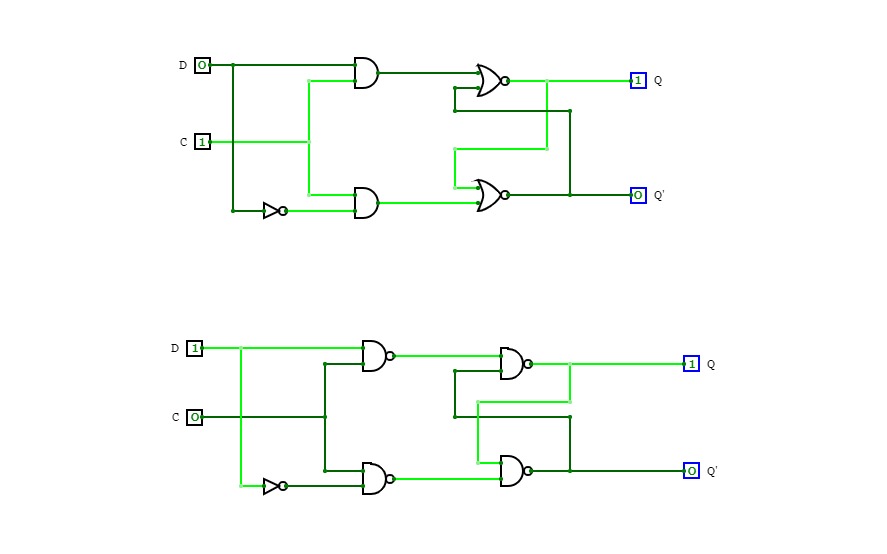

D latch NOR and NAND gate

D latch NOR and NAND gate

Lab 2

Lab 2

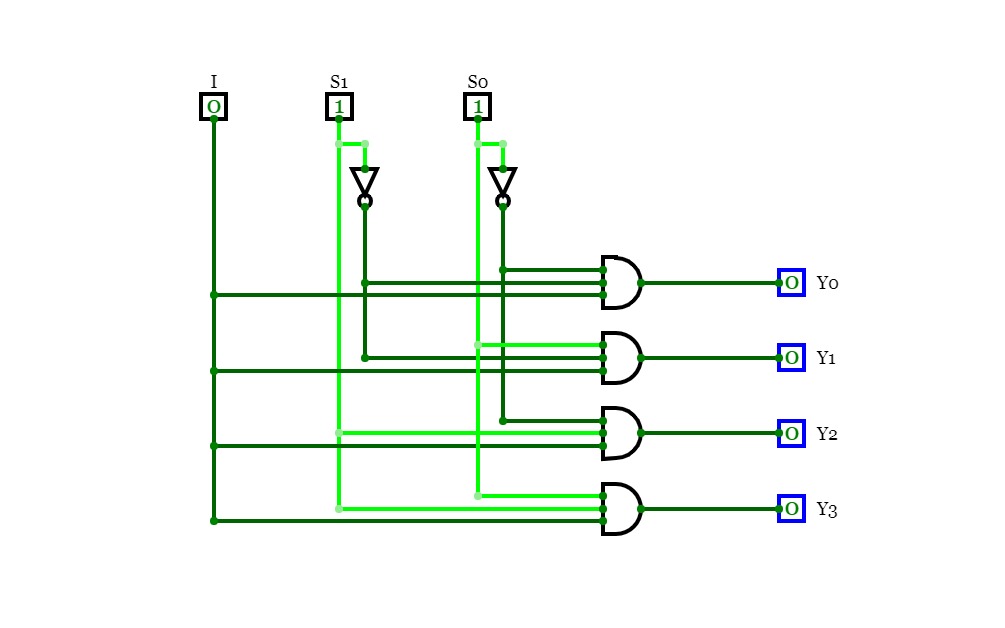

1x4 DeMultiplexer

1x4 DeMultiplexer

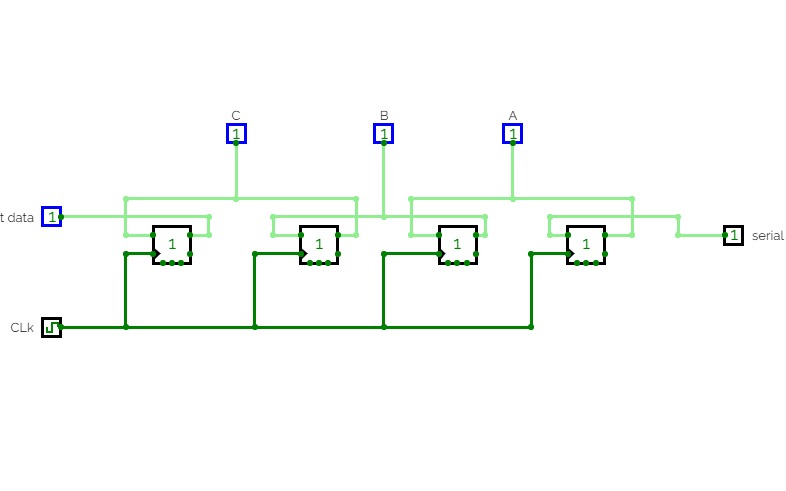

Exp 17a i (shift left using D)

Exp 17a i (shift left using D)

Logic Gates

Logic Gates

Exp. 7(1)

Exp. 7(1)

2/9/2020

2/9/2020

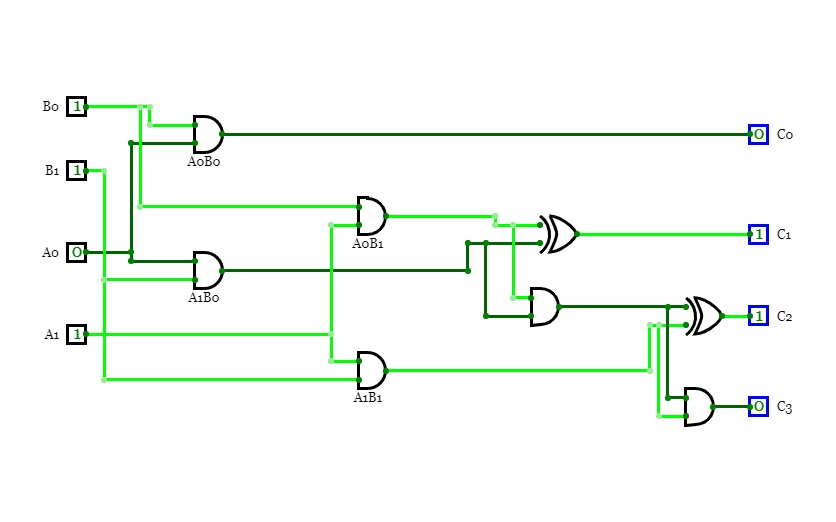

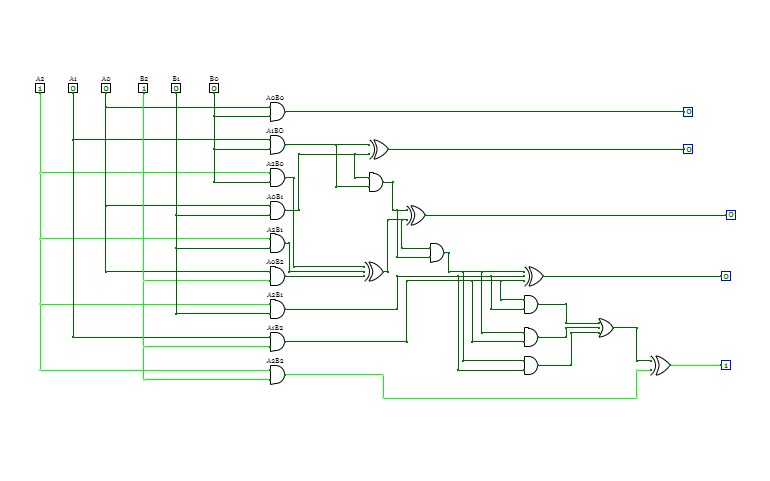

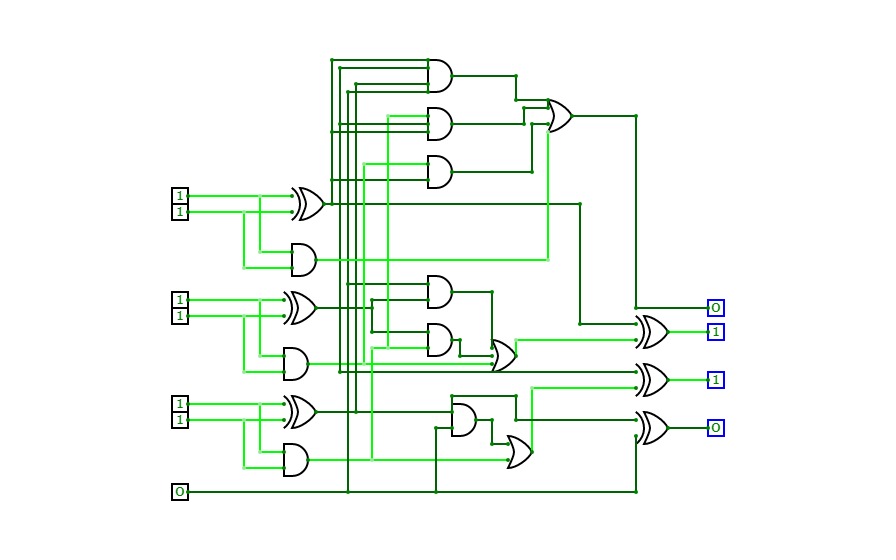

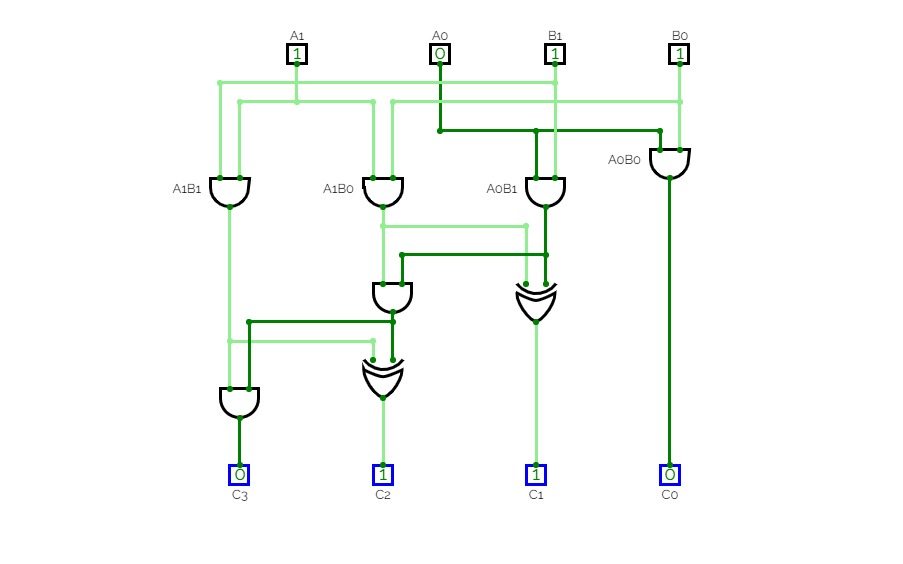

2x2 multiplier LAB Assignment

2x2 multiplier LAB Assignment

Exp 14-a

Exp 14-a